Timekeeping Redundancy Strategies Using Distributed CSAC Arrays

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

CSAC Technology Background and Objectives

Chip-Scale Atomic Clocks (CSACs) represent a revolutionary advancement in precision timekeeping technology, miniaturizing atomic clock capabilities into semiconductor-sized packages. Developed initially through DARPA funding in the early 2000s, CSACs have evolved from laboratory curiosities to commercially viable products that deliver remarkable timing stability in compact form factors. These devices leverage the quantum properties of alkali metal atoms, typically cesium or rubidium, to create highly stable frequency references that are orders of magnitude more precise than traditional quartz oscillators.

The evolution of CSAC technology has been driven by increasing demands for precise timing in distributed systems operating in GPS-denied environments. Traditional timing solutions either lack the necessary precision or require prohibitively large equipment, creating a technological gap that CSACs effectively address. The miniaturization breakthrough came through innovative physics package designs and low-power electronics that maintain atomic resonance conditions while dramatically reducing size, weight, and power requirements.

Current generation CSACs typically achieve stability performance of 10^-11 to 10^-12 over one day, while consuming only 100-150 mW of power in packages smaller than 20 cubic centimeters. This represents a transformative capability for applications requiring autonomous precision timing, though still falls short of the performance achieved by larger atomic clock systems.

The primary objective of distributed CSAC array research is to develop redundant timekeeping architectures that leverage the collective performance of multiple synchronized CSACs to achieve higher levels of accuracy, reliability, and resilience than individual units can provide. By implementing sophisticated synchronization algorithms and fault-tolerance mechanisms, these arrays aim to approach the performance of larger, more expensive atomic clock systems while maintaining the deployment advantages of chip-scale devices.

Additional technical goals include developing methods to characterize and compensate for individual CSAC error sources, creating optimal data fusion algorithms for multiple time sources, and designing network protocols that can maintain synchronization across distributed nodes even when external reference signals are unavailable. The ultimate aim is to create self-healing timing networks that can maintain critical infrastructure operations during GPS outages or jamming scenarios.

The technology trajectory suggests continued improvements in CSAC stability, size reduction, and power efficiency, with emerging research focused on alternative atomic species, optical rather than microwave transitions, and integration with other miniaturized quantum sensors to create comprehensive timing and navigation solutions.

The evolution of CSAC technology has been driven by increasing demands for precise timing in distributed systems operating in GPS-denied environments. Traditional timing solutions either lack the necessary precision or require prohibitively large equipment, creating a technological gap that CSACs effectively address. The miniaturization breakthrough came through innovative physics package designs and low-power electronics that maintain atomic resonance conditions while dramatically reducing size, weight, and power requirements.

Current generation CSACs typically achieve stability performance of 10^-11 to 10^-12 over one day, while consuming only 100-150 mW of power in packages smaller than 20 cubic centimeters. This represents a transformative capability for applications requiring autonomous precision timing, though still falls short of the performance achieved by larger atomic clock systems.

The primary objective of distributed CSAC array research is to develop redundant timekeeping architectures that leverage the collective performance of multiple synchronized CSACs to achieve higher levels of accuracy, reliability, and resilience than individual units can provide. By implementing sophisticated synchronization algorithms and fault-tolerance mechanisms, these arrays aim to approach the performance of larger, more expensive atomic clock systems while maintaining the deployment advantages of chip-scale devices.

Additional technical goals include developing methods to characterize and compensate for individual CSAC error sources, creating optimal data fusion algorithms for multiple time sources, and designing network protocols that can maintain synchronization across distributed nodes even when external reference signals are unavailable. The ultimate aim is to create self-healing timing networks that can maintain critical infrastructure operations during GPS outages or jamming scenarios.

The technology trajectory suggests continued improvements in CSAC stability, size reduction, and power efficiency, with emerging research focused on alternative atomic species, optical rather than microwave transitions, and integration with other miniaturized quantum sensors to create comprehensive timing and navigation solutions.

Market Demand Analysis for Precision Timekeeping

The precision timekeeping market is experiencing unprecedented growth driven by the increasing reliance on synchronized systems across multiple industries. The global market for precision timing devices was valued at approximately $6.3 billion in 2022 and is projected to reach $8.9 billion by 2027, representing a compound annual growth rate of 7.2%. This growth trajectory is primarily fueled by the expanding telecommunications sector, defense applications, and the emergence of autonomous systems that require ultra-precise synchronization.

Within this broader market, Chip-Scale Atomic Clocks (CSACs) represent a rapidly growing segment due to their unique combination of high precision and relatively small form factor. The CSAC market specifically is expected to grow from $325 million in 2022 to over $550 million by 2028, with distributed CSAC arrays emerging as a particularly promising application area.

The demand for redundant timekeeping solutions using distributed CSAC arrays is being driven by several key factors. First, critical infrastructure protection has become a national security priority for many countries, with GPS-timing vulnerabilities increasingly recognized as a significant risk factor. The 2018 U.S. Presidential Executive Order on Strengthening National Resilience through Responsible Use of Positioning, Navigation, and Timing Services highlighted the need for backup systems to GPS timing.

Telecommunications networks, particularly with the rollout of 5G and future 6G technologies, require timing synchronization accuracy in the sub-microsecond to nanosecond range. The market for telecom timing solutions alone is projected to exceed $1.2 billion by 2026, with distributed timing architectures gaining significant traction.

Financial markets represent another major demand driver, with high-frequency trading operations requiring timestamp accuracies in the microsecond range to comply with regulations such as MiFID II in Europe and similar frameworks in other jurisdictions. The financial sector's spending on precision timing solutions has increased by approximately 15% annually since 2019.

Defense and aerospace applications continue to be substantial market segments, with military communications, radar systems, and electronic warfare all requiring highly reliable, jam-resistant timing solutions. The defense market for precision timing is estimated at $1.8 billion globally, with distributed redundant systems capturing an increasing share.

Emerging applications in autonomous vehicles, smart grid infrastructure, and industrial IoT are creating new market opportunities. These sectors value the resilience offered by distributed timing architectures, with the industrial timing market expected to grow at 9.3% CAGR through 2028.

Within this broader market, Chip-Scale Atomic Clocks (CSACs) represent a rapidly growing segment due to their unique combination of high precision and relatively small form factor. The CSAC market specifically is expected to grow from $325 million in 2022 to over $550 million by 2028, with distributed CSAC arrays emerging as a particularly promising application area.

The demand for redundant timekeeping solutions using distributed CSAC arrays is being driven by several key factors. First, critical infrastructure protection has become a national security priority for many countries, with GPS-timing vulnerabilities increasingly recognized as a significant risk factor. The 2018 U.S. Presidential Executive Order on Strengthening National Resilience through Responsible Use of Positioning, Navigation, and Timing Services highlighted the need for backup systems to GPS timing.

Telecommunications networks, particularly with the rollout of 5G and future 6G technologies, require timing synchronization accuracy in the sub-microsecond to nanosecond range. The market for telecom timing solutions alone is projected to exceed $1.2 billion by 2026, with distributed timing architectures gaining significant traction.

Financial markets represent another major demand driver, with high-frequency trading operations requiring timestamp accuracies in the microsecond range to comply with regulations such as MiFID II in Europe and similar frameworks in other jurisdictions. The financial sector's spending on precision timing solutions has increased by approximately 15% annually since 2019.

Defense and aerospace applications continue to be substantial market segments, with military communications, radar systems, and electronic warfare all requiring highly reliable, jam-resistant timing solutions. The defense market for precision timing is estimated at $1.8 billion globally, with distributed redundant systems capturing an increasing share.

Emerging applications in autonomous vehicles, smart grid infrastructure, and industrial IoT are creating new market opportunities. These sectors value the resilience offered by distributed timing architectures, with the industrial timing market expected to grow at 9.3% CAGR through 2028.

Current State and Challenges of Distributed CSAC Systems

Distributed Chip-Scale Atomic Clock (CSAC) systems represent a significant advancement in precision timekeeping technology, offering unprecedented opportunities for robust time synchronization across distributed networks. Currently, these systems have reached a maturity level where commercial deployment is feasible, with several manufacturers producing CSAC units that achieve stability levels of approximately 10^-11 over one hour of operation while consuming only 120-150 mW of power. This remarkable power efficiency, combined with their compact form factor (typically under 17 cm³), makes them suitable for deployment in resource-constrained environments.

Despite these advancements, distributed CSAC systems face several critical challenges. Frequency drift remains a persistent issue, with typical drift rates of 3×10^-10 per month necessitating regular synchronization with more stable reference sources. This drift characteristic limits the autonomous operation period of CSAC arrays without external calibration. Environmental sensitivity also poses significant challenges, as CSACs exhibit temperature coefficients of approximately 5×10^-10 per °C, requiring sophisticated temperature compensation mechanisms for optimal performance in variable environments.

The synchronization of distributed CSAC arrays presents another major technical hurdle. Current synchronization protocols struggle to maintain sub-nanosecond accuracy across geographically dispersed nodes, particularly in environments with variable network latency or intermittent connectivity. The absence of standardized protocols specifically designed for CSAC array synchronization further complicates system integration and interoperability between different manufacturers' components.

From a geographical perspective, CSAC technology development remains concentrated primarily in North America and Europe, with emerging capabilities in Asia. The United States maintains leadership in both research and commercial production, with companies like Microsemi and Frequency Electronics dominating the market. European research institutions have made significant contributions to miniaturization techniques, while Chinese and Japanese entities are rapidly advancing their capabilities in mass production and system integration.

Resource constraints continue to limit wider adoption of distributed CSAC systems. The current unit cost of approximately $1,500-5,000 per CSAC device restricts deployment to high-value applications where precise timing is mission-critical. Additionally, the specialized expertise required for system integration and maintenance creates barriers to entry for many potential users.

Cybersecurity vulnerabilities represent an emerging concern for distributed timing systems. As these systems become more networked, they face increased exposure to spoofing, jamming, and other forms of interference. Current security measures for distributed CSAC systems remain largely ad hoc, lacking comprehensive standards and protocols specifically designed to address the unique security requirements of precision timing networks.

Despite these advancements, distributed CSAC systems face several critical challenges. Frequency drift remains a persistent issue, with typical drift rates of 3×10^-10 per month necessitating regular synchronization with more stable reference sources. This drift characteristic limits the autonomous operation period of CSAC arrays without external calibration. Environmental sensitivity also poses significant challenges, as CSACs exhibit temperature coefficients of approximately 5×10^-10 per °C, requiring sophisticated temperature compensation mechanisms for optimal performance in variable environments.

The synchronization of distributed CSAC arrays presents another major technical hurdle. Current synchronization protocols struggle to maintain sub-nanosecond accuracy across geographically dispersed nodes, particularly in environments with variable network latency or intermittent connectivity. The absence of standardized protocols specifically designed for CSAC array synchronization further complicates system integration and interoperability between different manufacturers' components.

From a geographical perspective, CSAC technology development remains concentrated primarily in North America and Europe, with emerging capabilities in Asia. The United States maintains leadership in both research and commercial production, with companies like Microsemi and Frequency Electronics dominating the market. European research institutions have made significant contributions to miniaturization techniques, while Chinese and Japanese entities are rapidly advancing their capabilities in mass production and system integration.

Resource constraints continue to limit wider adoption of distributed CSAC systems. The current unit cost of approximately $1,500-5,000 per CSAC device restricts deployment to high-value applications where precise timing is mission-critical. Additionally, the specialized expertise required for system integration and maintenance creates barriers to entry for many potential users.

Cybersecurity vulnerabilities represent an emerging concern for distributed timing systems. As these systems become more networked, they face increased exposure to spoofing, jamming, and other forms of interference. Current security measures for distributed CSAC systems remain largely ad hoc, lacking comprehensive standards and protocols specifically designed to address the unique security requirements of precision timing networks.

Current Redundancy Strategies for Distributed Timing Systems

01 Distributed CSAC array architecture for enhanced timekeeping redundancy

Distributed Chip-Scale Atomic Clock (CSAC) arrays can be designed to provide enhanced timekeeping redundancy by distributing multiple atomic clock units across a system. This architecture allows for continued operation even if individual clock units fail, as the system can switch to functioning units. The distributed nature of these arrays enables fault tolerance and improved reliability in critical timing applications, with synchronization mechanisms ensuring consistent timekeeping across all nodes.- Distributed CSAC array architecture for redundant timekeeping: Distributed Chip-Scale Atomic Clock (CSAC) arrays can be designed to provide redundant timekeeping capabilities across multiple nodes. This architecture allows for fault tolerance by distributing timing responsibilities across multiple atomic clocks, ensuring that if one clock fails, others can maintain accurate time. The system can employ voting mechanisms to identify and isolate faulty clocks while maintaining overall system timing integrity.

- Synchronization methods for distributed timing systems: Various synchronization methods can be implemented in distributed CSAC arrays to maintain coherent timekeeping across the network. These methods include master-slave configurations, peer-to-peer synchronization protocols, and consensus algorithms that allow multiple atomic clocks to agree on a common time reference. Advanced synchronization techniques can compensate for communication delays and environmental factors that might affect individual clock accuracy.

- Fault detection and recovery in redundant timing systems: Redundant CSAC arrays incorporate sophisticated fault detection mechanisms to identify when a clock is drifting or has failed. The system can automatically switch to backup clocks when failures are detected, ensuring continuous operation. Some implementations include self-healing capabilities where the system can reconfigure itself after detecting faults, adjusting the weighting of different clocks in the timing consensus based on their reliability and performance metrics.

- Memory management for distributed timing data: Efficient memory management is crucial for distributed CSAC arrays to store and process timing data across the network. These systems employ specialized memory architectures that can quickly access and update timing information while maintaining data integrity. Some implementations use distributed memory systems with redundant storage to prevent data loss, while others implement hierarchical memory structures to optimize access to critical timing parameters.

- Network communication protocols for time distribution: Specialized communication protocols are essential for maintaining accurate time distribution across CSAC arrays. These protocols are designed to minimize latency and jitter while providing secure and reliable transmission of timing information. Some implementations use deterministic networking approaches to ensure predictable timing behavior, while others employ adaptive protocols that can adjust to changing network conditions while maintaining the integrity of the distributed timing system.

02 Synchronization methods for distributed clock systems

Various synchronization methods are employed in distributed CSAC arrays to maintain accurate timekeeping across multiple clock units. These methods include master-slave configurations, consensus algorithms, and network time protocols adapted for atomic clock precision. Synchronization techniques ensure that all clocks in the array maintain coherent time references despite physical separation, environmental variations, or communication delays, which is essential for applications requiring precise timing coordination.Expand Specific Solutions03 Fault detection and recovery mechanisms in redundant timing systems

Redundant CSAC arrays implement sophisticated fault detection and recovery mechanisms to identify malfunctioning clock units and seamlessly transition to backup units. These systems continuously monitor clock performance parameters such as drift, stability, and signal quality to detect anomalies. When faults are detected, automated recovery procedures redirect timing functions to operational units, maintaining system integrity and preventing timing discontinuities in critical applications.Expand Specific Solutions04 Memory and storage architectures for distributed timing systems

Specialized memory and storage architectures support distributed CSAC arrays by providing efficient data structures for timestamp management, clock state information, and synchronization parameters. These architectures include redundant storage systems, distributed databases for timing information, and memory management techniques optimized for real-time clock data. The storage systems are designed to maintain timing coherence across distributed nodes while minimizing access latency for time-critical operations.Expand Specific Solutions05 Network communication protocols for time distribution

Custom network communication protocols enable precise time distribution across distributed CSAC arrays. These protocols are optimized for minimal latency, deterministic behavior, and resistance to network jitter. They include mechanisms for timestamp exchange, clock drift compensation, and secure time transfer between nodes. The protocols support various network topologies and can adapt to changing network conditions while maintaining the high precision required for atomic clock synchronization in distributed environments.Expand Specific Solutions

Major Players in CSAC and Precision Timing Industry

The distributed CSAC (Chip-Scale Atomic Clock) arrays market is in its growth phase, characterized by increasing adoption across telecommunications, defense, and critical infrastructure sectors. The global market for precision timing solutions is projected to reach approximately $6-8 billion by 2025, with redundancy strategies becoming essential for mission-critical applications. Technologically, the field is maturing rapidly with companies like Huawei, IBM, and Microsemi (acquired by Microchip) leading innovation. Huawei and ZTE are advancing telecom-focused implementations, while Western Digital and Marvell focus on data center applications. Defense applications are championed by Siemens and TTTech. Academic-industry partnerships, particularly involving Tsinghua University and Chongqing University of Posts & Telecommunications, are accelerating development of fault-tolerant distributed timing architectures, with emerging players like Chengdu Spaceon Electronics specializing in atomic clock technologies for redundant timing systems.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed an innovative approach to timekeeping redundancy using distributed CSAC arrays for telecommunications infrastructure. Their solution, known as "Distributed Precision Time Protocol" (DPTP), deploys multiple Chip-Scale Atomic Clocks across network nodes to maintain synchronization even during network partitions or GNSS outages. The system employs a hierarchical architecture where primary and secondary timing sources automatically negotiate roles based on stability metrics and connection quality. Huawei's implementation includes machine learning algorithms that continuously analyze clock behavior to predict drift patterns and preemptively adjust synchronization parameters. The technology achieves sub-100 nanosecond accuracy across geographically distributed networks and incorporates security mechanisms to detect and mitigate timing attacks. This solution has been deployed in 5G base stations and critical communications infrastructure where precise timing is essential for network operation.

Strengths: Exceptional synchronization performance across large-scale networks; advanced machine learning capabilities for predictive clock management; proven deployment in telecommunications infrastructure. Weaknesses: Complex implementation requiring specialized expertise; higher power consumption compared to non-redundant solutions; proprietary elements limiting interoperability with some third-party systems.

TTTech Computertechnik AG

Technical Solution: TTTech has developed advanced Timekeeping Redundancy Strategies using Distributed CSAC (Chip-Scale Atomic Clock) Arrays for mission-critical systems. Their solution implements a hierarchical time synchronization architecture where multiple CSACs are distributed across a network, creating a fault-tolerant time reference system. The technology employs sophisticated algorithms for clock drift compensation and detection of faulty atomic clocks. TTTech's implementation includes a distributed consensus protocol that allows the system to maintain sub-microsecond synchronization accuracy even when individual CSACs fail. Their solution integrates with time-triggered networks, providing deterministic communication with precise time guarantees for safety-critical applications in aerospace, automotive, and industrial automation sectors.

Strengths: Exceptional fault tolerance through distributed redundancy; proven implementation in safety-critical systems; integration with time-triggered networks for deterministic performance. Weaknesses: Higher implementation complexity and cost compared to centralized solutions; requires specialized expertise for deployment and maintenance.

Key Technical Innovations in CSAC Array Synchronization

Molecular clock

PatentActiveUS20190235445A1

Innovation

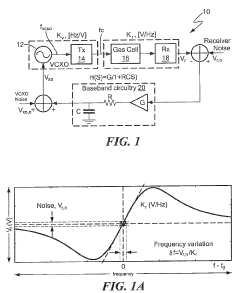

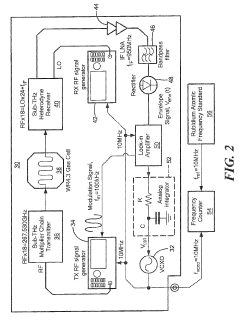

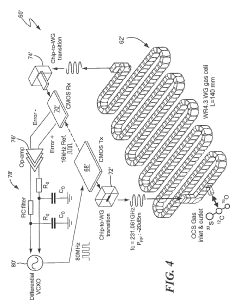

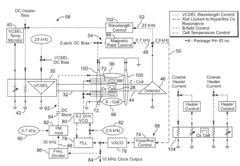

- A molecular clock utilizing rotational-state transitions of gaseous polar molecules in the sub-THz region, integrated with CMOS technology, providing a compact, low-power, and robust frequency reference with enhanced stability and instant start-up capabilities.

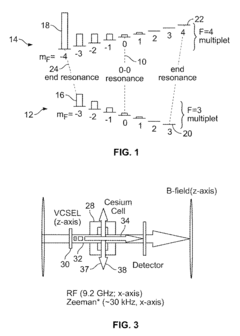

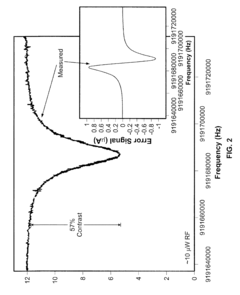

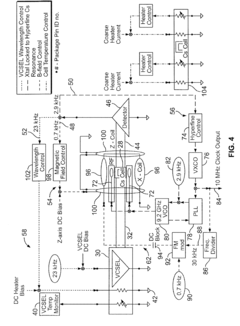

Batch-fabricated, RF-interrogated, end transition, chip-scale atomic clock

PatentActiveUS7852163B2

Innovation

- A chip-scale atomic clock employing direct RF-interrogation on an end-state transition using an alkali vapor cell, a laser source, photodetector, RF excitation coils, bias coils, and Zeeman coils, with feedback loops for maintaining stable magnetic and optical conditions, allowing for compact and low-power operation without bulky microwave cavities.

Reliability Metrics and Performance Standards

The reliability of Chip-Scale Atomic Clock (CSAC) arrays in distributed timekeeping systems must be evaluated against rigorous metrics and standards to ensure mission-critical performance. Industry standards such as IEEE 1588 Precision Time Protocol (PTP) establish baseline requirements for time synchronization accuracy, typically demanding sub-microsecond precision in telecommunications and sub-nanosecond precision in advanced scientific applications. For CSAC arrays, Allan Deviation serves as a fundamental metric, measuring frequency stability over various time intervals, with high-performance systems achieving values below 1×10^-11 at 1-second averaging times.

Mean Time Between Failures (MTBF) represents another critical reliability parameter, with modern CSAC units demonstrating MTBF values exceeding 100,000 hours under standard operating conditions. However, when deployed in distributed arrays, system-level MTBF calculations must account for network topology and redundancy architecture. Fault tolerance metrics, including N+1 and N+2 redundancy configurations, provide quantitative measures of system resilience against individual clock failures.

Time Error Tolerance (TET) standards define acceptable deviation limits before system performance degradation occurs. In telecommunications networks, TET typically ranges from 1.5 to 5 microseconds, while financial trading systems may require stricter tolerances below 100 nanoseconds. The Holdover Performance metric evaluates how long a system can maintain acceptable timing accuracy when external synchronization sources become unavailable, with distributed CSAC arrays typically achieving 24-72 hour holdover periods while maintaining microsecond-level accuracy.

Environmental performance standards establish operational parameters across temperature ranges (-40°C to +85°C for military-grade applications), vibration profiles (MIL-STD-810G compliance), and radiation tolerance (particularly relevant for space-based applications). Recovery Time Objective (RTO) metrics specify the maximum acceptable time to restore normal timing operations following a disruption, typically ranging from milliseconds in telecommunications to seconds in less time-critical applications.

Synchronization Accuracy Deviation (SAD) measures the statistical distribution of timing errors across the distributed array, with well-designed systems maintaining 95% of measurements within ±50 nanoseconds of the reference. Power consumption efficiency standards have also emerged as important reliability indicators, with modern CSACs operating at 120-150 mW during normal operation and implementing power-saving modes that can reduce consumption to below 30 mW during standby periods while maintaining rapid recovery capabilities.

Certification requirements vary by application domain, with telecommunications systems typically requiring ITU-T G.8272 compliance, aviation systems adhering to DO-178C software standards, and military applications following MIL-STD-1547 for space systems. These comprehensive reliability metrics and performance standards provide the framework for evaluating and validating distributed CSAC array implementations across diverse operational environments.

Mean Time Between Failures (MTBF) represents another critical reliability parameter, with modern CSAC units demonstrating MTBF values exceeding 100,000 hours under standard operating conditions. However, when deployed in distributed arrays, system-level MTBF calculations must account for network topology and redundancy architecture. Fault tolerance metrics, including N+1 and N+2 redundancy configurations, provide quantitative measures of system resilience against individual clock failures.

Time Error Tolerance (TET) standards define acceptable deviation limits before system performance degradation occurs. In telecommunications networks, TET typically ranges from 1.5 to 5 microseconds, while financial trading systems may require stricter tolerances below 100 nanoseconds. The Holdover Performance metric evaluates how long a system can maintain acceptable timing accuracy when external synchronization sources become unavailable, with distributed CSAC arrays typically achieving 24-72 hour holdover periods while maintaining microsecond-level accuracy.

Environmental performance standards establish operational parameters across temperature ranges (-40°C to +85°C for military-grade applications), vibration profiles (MIL-STD-810G compliance), and radiation tolerance (particularly relevant for space-based applications). Recovery Time Objective (RTO) metrics specify the maximum acceptable time to restore normal timing operations following a disruption, typically ranging from milliseconds in telecommunications to seconds in less time-critical applications.

Synchronization Accuracy Deviation (SAD) measures the statistical distribution of timing errors across the distributed array, with well-designed systems maintaining 95% of measurements within ±50 nanoseconds of the reference. Power consumption efficiency standards have also emerged as important reliability indicators, with modern CSACs operating at 120-150 mW during normal operation and implementing power-saving modes that can reduce consumption to below 30 mW during standby periods while maintaining rapid recovery capabilities.

Certification requirements vary by application domain, with telecommunications systems typically requiring ITU-T G.8272 compliance, aviation systems adhering to DO-178C software standards, and military applications following MIL-STD-1547 for space systems. These comprehensive reliability metrics and performance standards provide the framework for evaluating and validating distributed CSAC array implementations across diverse operational environments.

Security Considerations for Distributed Timing Infrastructure

The security landscape of distributed timing infrastructure presents unique challenges when implementing CSAC (Chip-Scale Atomic Clock) arrays for redundancy. As timing systems become increasingly decentralized, they face sophisticated threats including signal jamming, spoofing attacks, and physical tampering. These vulnerabilities are particularly concerning for critical infrastructure sectors where precise timing synchronization is essential for operations.

Distributed CSAC arrays must implement robust authentication mechanisms to verify the legitimacy of timing signals. Cryptographic techniques such as digital signatures and secure hash algorithms can validate timing data integrity, while encrypted communication channels protect against man-in-the-middle attacks. The implementation of zero-trust architecture principles is advisable, where each timing node must authenticate before participating in the network.

Physical security measures remain equally important for protecting CSAC hardware components. Tamper-evident enclosures, secure installation locations, and continuous environmental monitoring help detect unauthorized access attempts. For highly sensitive applications, implementing physical isolation through air-gapping may be necessary to prevent remote exploitation.

Network segmentation strategies should be employed to contain potential security breaches within distributed timing systems. By creating separate timing domains with controlled interfaces between them, organizations can limit the impact of compromised nodes. Additionally, implementing timing diversity through multiple synchronization sources with different technologies provides resilience against targeted attacks on specific timing protocols.

Continuous security monitoring is essential for maintaining the integrity of distributed CSAC arrays. Real-time anomaly detection systems can identify unusual timing patterns that may indicate manipulation attempts. Establishing baseline timing behaviors enables quick identification of deviations that could signal security incidents. Regular security audits and penetration testing should be conducted to identify vulnerabilities before they can be exploited.

Regulatory compliance and industry standards provide important frameworks for securing timing infrastructure. Standards such as IEEE 1588 PTP Security, IEC 62351, and NIST Cybersecurity Framework offer guidelines specifically addressing timing security concerns. Organizations should incorporate these standards into their security policies while maintaining awareness of emerging threats through participation in information sharing communities focused on timing security.

Distributed CSAC arrays must implement robust authentication mechanisms to verify the legitimacy of timing signals. Cryptographic techniques such as digital signatures and secure hash algorithms can validate timing data integrity, while encrypted communication channels protect against man-in-the-middle attacks. The implementation of zero-trust architecture principles is advisable, where each timing node must authenticate before participating in the network.

Physical security measures remain equally important for protecting CSAC hardware components. Tamper-evident enclosures, secure installation locations, and continuous environmental monitoring help detect unauthorized access attempts. For highly sensitive applications, implementing physical isolation through air-gapping may be necessary to prevent remote exploitation.

Network segmentation strategies should be employed to contain potential security breaches within distributed timing systems. By creating separate timing domains with controlled interfaces between them, organizations can limit the impact of compromised nodes. Additionally, implementing timing diversity through multiple synchronization sources with different technologies provides resilience against targeted attacks on specific timing protocols.

Continuous security monitoring is essential for maintaining the integrity of distributed CSAC arrays. Real-time anomaly detection systems can identify unusual timing patterns that may indicate manipulation attempts. Establishing baseline timing behaviors enables quick identification of deviations that could signal security incidents. Regular security audits and penetration testing should be conducted to identify vulnerabilities before they can be exploited.

Regulatory compliance and industry standards provide important frameworks for securing timing infrastructure. Standards such as IEEE 1588 PTP Security, IEC 62351, and NIST Cybersecurity Framework offer guidelines specifically addressing timing security concerns. Organizations should incorporate these standards into their security policies while maintaining awareness of emerging threats through participation in information sharing communities focused on timing security.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!