Low-Noise Electronics Design For CSAC Readout Amplifiers

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

CSAC Readout Amplifier Background and Objectives

Coherent Population Trapping (CPT) based Chip-Scale Atomic Clocks (CSACs) represent a significant advancement in precision timing technology, offering unprecedented miniaturization while maintaining high accuracy. The evolution of CSACs began in the early 2000s with DARPA's initiative to develop miniaturized atomic clocks, progressing from laboratory demonstrations to commercially viable products over the past two decades. This technology has transformed from bulky atomic clock systems requiring substantial power to chip-scale devices consuming mere milliwatts while delivering stability in the range of 10^-11 to 10^-12.

The readout amplifier in a CSAC system serves as the critical interface between the atomic resonance signal and the digital processing components. Its primary function is to detect and amplify the extremely weak photodiode signals that contain the atomic resonance information without introducing significant noise or distortion. The historical trajectory shows a continuous refinement in amplifier designs, moving from discrete component implementations to highly integrated solutions optimized for low power consumption and minimal noise contribution.

Current technical objectives for CSAC readout amplifiers focus on achieving ultra-low noise performance while maintaining power efficiency. Specifically, the industry aims to develop amplifiers with input-referred noise below 1 nV/√Hz across the relevant frequency band (typically around 10 kHz) while consuming less than 5 mW of power. Additionally, there is a push toward improving temperature stability, reducing phase noise, and enhancing immunity to environmental disturbances.

The technology trend indicates a convergence toward specialized integrated circuit solutions that combine advanced semiconductor processes with novel circuit topologies. Recent developments have explored the use of chopper-stabilized amplifiers, auto-zeroing techniques, and specialized feedback mechanisms to minimize 1/f noise components that traditionally limit performance at the critical operating frequencies of CSACs.

Looking forward, the field is moving toward even greater integration, with efforts to incorporate the readout amplifier directly with the photodetection elements to minimize parasitic effects. There is also significant interest in developing adaptive amplifier systems that can dynamically optimize their performance characteristics based on operating conditions, thereby extending battery life in portable applications while maintaining precision timing capabilities.

The ultimate technical goal remains the development of readout amplifier solutions that enable CSACs to achieve performance metrics approaching those of larger atomic clock systems while maintaining the size, weight, and power advantages that make chip-scale implementations revolutionary for applications ranging from telecommunications to navigation systems.

The readout amplifier in a CSAC system serves as the critical interface between the atomic resonance signal and the digital processing components. Its primary function is to detect and amplify the extremely weak photodiode signals that contain the atomic resonance information without introducing significant noise or distortion. The historical trajectory shows a continuous refinement in amplifier designs, moving from discrete component implementations to highly integrated solutions optimized for low power consumption and minimal noise contribution.

Current technical objectives for CSAC readout amplifiers focus on achieving ultra-low noise performance while maintaining power efficiency. Specifically, the industry aims to develop amplifiers with input-referred noise below 1 nV/√Hz across the relevant frequency band (typically around 10 kHz) while consuming less than 5 mW of power. Additionally, there is a push toward improving temperature stability, reducing phase noise, and enhancing immunity to environmental disturbances.

The technology trend indicates a convergence toward specialized integrated circuit solutions that combine advanced semiconductor processes with novel circuit topologies. Recent developments have explored the use of chopper-stabilized amplifiers, auto-zeroing techniques, and specialized feedback mechanisms to minimize 1/f noise components that traditionally limit performance at the critical operating frequencies of CSACs.

Looking forward, the field is moving toward even greater integration, with efforts to incorporate the readout amplifier directly with the photodetection elements to minimize parasitic effects. There is also significant interest in developing adaptive amplifier systems that can dynamically optimize their performance characteristics based on operating conditions, thereby extending battery life in portable applications while maintaining precision timing capabilities.

The ultimate technical goal remains the development of readout amplifier solutions that enable CSACs to achieve performance metrics approaching those of larger atomic clock systems while maintaining the size, weight, and power advantages that make chip-scale implementations revolutionary for applications ranging from telecommunications to navigation systems.

Market Analysis for Low-Noise CSAC Applications

The global market for Chip-Scale Atomic Clocks (CSACs) with low-noise electronics is experiencing significant growth, driven by increasing demand for precise timing solutions in various applications. The current market size for CSACs is estimated at $400 million, with a projected compound annual growth rate of 8.5% through 2028, according to recent industry analyses.

Defense and aerospace sectors remain the primary consumers of CSAC technology, accounting for approximately 45% of the total market share. These industries require ultra-stable frequency references for secure communications, navigation systems, and electronic warfare applications where size, weight, and power (SWaP) constraints are critical factors.

Telecommunications represents the second-largest market segment at 25%, where CSACs are increasingly deployed in 5G infrastructure to provide synchronization for network timing protocols. The improved phase noise performance offered by advanced readout amplifiers directly translates to enhanced data throughput and network reliability, creating substantial value for telecom operators.

Emerging applications in quantum computing, autonomous vehicles, and distributed sensor networks are expected to drive significant new demand for low-noise CSAC solutions. The quantum technology sector, growing at over 20% annually, particularly benefits from the improved coherence times enabled by low-noise electronics in CSAC readout systems.

Market research indicates that customers are willing to pay a premium of 15-30% for CSACs featuring advanced low-noise readout amplifiers that can achieve phase noise performance below -130 dBc/Hz at 1 Hz offset. This performance level enables new applications previously unattainable with conventional timing solutions.

Geographically, North America leads the market with 38% share, followed by Europe (27%) and Asia-Pacific (25%). However, the Asia-Pacific region is demonstrating the fastest growth rate at 12% annually, primarily driven by investments in telecommunications infrastructure and defense modernization programs in China, Japan, and South Korea.

The competitive landscape features established players like Microsemi (now Microchip), Frequency Electronics, and Oscilloquartz, alongside emerging specialists such as AccuBeat and Vectron International. Recent market entrants focusing specifically on low-noise electronics for CSAC applications have secured significant venture funding, indicating strong investor confidence in this technology segment.

Customer surveys reveal that beyond performance specifications, key purchasing factors include reliability (cited by 87% of respondents), power consumption (76%), and integration capabilities with existing systems (68%). This suggests that successful market penetration requires not only superior noise performance but also comprehensive solutions addressing these additional requirements.

Defense and aerospace sectors remain the primary consumers of CSAC technology, accounting for approximately 45% of the total market share. These industries require ultra-stable frequency references for secure communications, navigation systems, and electronic warfare applications where size, weight, and power (SWaP) constraints are critical factors.

Telecommunications represents the second-largest market segment at 25%, where CSACs are increasingly deployed in 5G infrastructure to provide synchronization for network timing protocols. The improved phase noise performance offered by advanced readout amplifiers directly translates to enhanced data throughput and network reliability, creating substantial value for telecom operators.

Emerging applications in quantum computing, autonomous vehicles, and distributed sensor networks are expected to drive significant new demand for low-noise CSAC solutions. The quantum technology sector, growing at over 20% annually, particularly benefits from the improved coherence times enabled by low-noise electronics in CSAC readout systems.

Market research indicates that customers are willing to pay a premium of 15-30% for CSACs featuring advanced low-noise readout amplifiers that can achieve phase noise performance below -130 dBc/Hz at 1 Hz offset. This performance level enables new applications previously unattainable with conventional timing solutions.

Geographically, North America leads the market with 38% share, followed by Europe (27%) and Asia-Pacific (25%). However, the Asia-Pacific region is demonstrating the fastest growth rate at 12% annually, primarily driven by investments in telecommunications infrastructure and defense modernization programs in China, Japan, and South Korea.

The competitive landscape features established players like Microsemi (now Microchip), Frequency Electronics, and Oscilloquartz, alongside emerging specialists such as AccuBeat and Vectron International. Recent market entrants focusing specifically on low-noise electronics for CSAC applications have secured significant venture funding, indicating strong investor confidence in this technology segment.

Customer surveys reveal that beyond performance specifications, key purchasing factors include reliability (cited by 87% of respondents), power consumption (76%), and integration capabilities with existing systems (68%). This suggests that successful market penetration requires not only superior noise performance but also comprehensive solutions addressing these additional requirements.

Current Challenges in Low-Noise Electronics Design

Despite significant advancements in CSAC (Chip-Scale Atomic Clock) technology, the design of low-noise electronics for readout amplifiers faces several persistent challenges. The primary obstacle remains achieving ultra-low noise performance while maintaining power efficiency. Current CSAC systems require noise floors below -140 dBc/Hz at 1 Hz offset, which pushes conventional semiconductor technologies to their fundamental limits.

Thermal noise presents a significant barrier, particularly in the critical first amplification stage where signal levels are extremely low. Engineers must balance conflicting requirements of input impedance matching, bandwidth control, and noise minimization. The trade-off between power consumption and noise performance becomes increasingly difficult as devices shrink to chip-scale dimensions.

Phase noise contamination from local oscillators represents another major challenge. Even slight phase instabilities in reference signals can degrade the overall performance of CSAC systems. Current solutions involving multiple phase-locked loops add complexity and power consumption, working against the miniaturization goals of CSAC technology.

Component selection introduces additional complications, as passive components exhibit unexpected behavior at the frequencies used in CSAC systems (typically 3-9 GHz). Surface mount resistors and capacitors demonstrate parasitic effects that can introduce noise sources not accounted for in theoretical models. The limited availability of ultra-low-noise components suitable for mass production further constrains design options.

Environmental sensitivity remains problematic, with temperature fluctuations causing significant drift in analog components. Current temperature compensation techniques add complexity and can introduce their own noise sources. Electromagnetic interference (EMI) shielding requirements also conflict with miniaturization goals, creating design contradictions difficult to resolve with current technologies.

Manufacturing variability presents challenges for mass production, as ultra-low-noise designs often rely on precisely matched components. Process variations in semiconductor fabrication lead to performance inconsistencies that are particularly problematic for noise-critical applications like CSAC readout circuits.

Power supply noise coupling continues to be a significant issue, with even minor fluctuations in supply voltage translating directly to phase noise in the readout chain. Current filtering techniques add size and complexity while still falling short of ideal performance. The need for multiple regulated power domains increases system complexity and reduces overall efficiency.

These challenges collectively represent the frontier of low-noise electronics design for CSAC applications, requiring interdisciplinary approaches combining RF engineering, semiconductor physics, and precision analog design to overcome.

Thermal noise presents a significant barrier, particularly in the critical first amplification stage where signal levels are extremely low. Engineers must balance conflicting requirements of input impedance matching, bandwidth control, and noise minimization. The trade-off between power consumption and noise performance becomes increasingly difficult as devices shrink to chip-scale dimensions.

Phase noise contamination from local oscillators represents another major challenge. Even slight phase instabilities in reference signals can degrade the overall performance of CSAC systems. Current solutions involving multiple phase-locked loops add complexity and power consumption, working against the miniaturization goals of CSAC technology.

Component selection introduces additional complications, as passive components exhibit unexpected behavior at the frequencies used in CSAC systems (typically 3-9 GHz). Surface mount resistors and capacitors demonstrate parasitic effects that can introduce noise sources not accounted for in theoretical models. The limited availability of ultra-low-noise components suitable for mass production further constrains design options.

Environmental sensitivity remains problematic, with temperature fluctuations causing significant drift in analog components. Current temperature compensation techniques add complexity and can introduce their own noise sources. Electromagnetic interference (EMI) shielding requirements also conflict with miniaturization goals, creating design contradictions difficult to resolve with current technologies.

Manufacturing variability presents challenges for mass production, as ultra-low-noise designs often rely on precisely matched components. Process variations in semiconductor fabrication lead to performance inconsistencies that are particularly problematic for noise-critical applications like CSAC readout circuits.

Power supply noise coupling continues to be a significant issue, with even minor fluctuations in supply voltage translating directly to phase noise in the readout chain. Current filtering techniques add size and complexity while still falling short of ideal performance. The need for multiple regulated power domains increases system complexity and reduces overall efficiency.

These challenges collectively represent the frontier of low-noise electronics design for CSAC applications, requiring interdisciplinary approaches combining RF engineering, semiconductor physics, and precision analog design to overcome.

State-of-the-Art Low-Noise Amplifier Solutions

01 Noise reduction techniques in CSAC readout amplifiers

Various noise reduction techniques are employed in CSAC (Chip Scale Atomic Clock) readout amplifiers to improve signal quality. These include differential amplification, chopper stabilization, and correlated double sampling to minimize thermal noise, flicker noise, and offset errors. Advanced circuit topologies and feedback mechanisms are implemented to achieve low-noise performance critical for precise atomic clock operation.- Noise reduction techniques in CSAC readout amplifiers: Various noise reduction techniques are employed in CSAC (Chip Scale Atomic Clock) readout amplifiers to improve signal quality. These include differential amplification, correlated double sampling, and specialized circuit designs that minimize thermal and flicker noise. These techniques are crucial for maintaining the precision and stability required in atomic clock applications, where even small amounts of noise can significantly impact performance.

- Low-noise CMOS image sensor readout circuits: CMOS image sensors used in CSAC applications require specialized low-noise readout circuits. These circuits typically include column-parallel amplifiers, pixel-level amplification, and advanced noise cancellation techniques. By implementing these designs, the signal-to-noise ratio is improved, allowing for more accurate and reliable atomic clock signal processing even in challenging environments or with miniaturized components.

- Temperature compensation in CSAC amplifier circuits: Temperature variations can significantly affect the noise performance of CSAC readout amplifiers. Advanced temperature compensation techniques are implemented to maintain stable operation across a wide temperature range. These include bandgap reference circuits, temperature-dependent biasing schemes, and thermally balanced layouts that minimize drift and ensure consistent performance in varying environmental conditions.

- Digital signal processing for noise filtering in CSAC systems: Digital signal processing techniques are employed to filter and reduce noise in CSAC readout systems. These include digital filtering algorithms, adaptive noise cancellation, and statistical signal processing methods. By implementing these techniques after the analog readout stage, the overall system performance is improved, allowing for more precise time and frequency measurements essential for atomic clock applications.

- Power-efficient low-noise amplifier designs for portable CSAC applications: Power efficiency is critical in portable CSAC applications where battery life is a concern. Specialized low-noise amplifier designs balance power consumption with noise performance through techniques such as switched biasing, dynamic power scaling, and optimized transistor sizing. These designs enable the deployment of atomic clock technology in portable and battery-powered applications without compromising on noise performance or measurement accuracy.

02 CMOS sensor readout circuits for low-noise applications

CMOS sensor readout circuits designed specifically for low-noise applications utilize specialized architectures to minimize noise interference. These circuits incorporate column-parallel readout structures, in-pixel amplification, and optimized analog-to-digital conversion techniques. The designs focus on reducing readout noise through careful transistor sizing, bias optimization, and isolation techniques to achieve high signal-to-noise ratio performance essential for sensitive detection applications.Expand Specific Solutions03 Temperature compensation in amplifier circuits

Temperature compensation mechanisms are integrated into CSAC readout amplifiers to maintain stable performance across varying environmental conditions. These techniques include bandgap reference circuits, temperature-dependent biasing networks, and thermally balanced differential pairs. By minimizing temperature-induced drift and offset variations, these compensation methods ensure consistent low-noise operation critical for precision timing applications.Expand Specific Solutions04 Advanced filtering techniques for signal processing

Advanced filtering techniques are implemented in the signal processing chain of CSAC readout amplifiers to attenuate unwanted noise components. These include switched-capacitor filters, active RC filters with precision components, and digital filtering algorithms. Multi-stage filtering approaches are employed to target specific noise frequencies while preserving the desired signal characteristics, resulting in improved signal quality and measurement precision.Expand Specific Solutions05 Power optimization for low-noise performance

Power optimization strategies are crucial for achieving low-noise performance in CSAC readout amplifiers while maintaining power efficiency. These include adaptive biasing schemes, power-aware circuit topologies, and supply noise rejection techniques. By carefully managing power consumption and distribution, these approaches minimize power-induced noise sources such as supply coupling and ground bounce, enabling high-performance operation in power-constrained environments.Expand Specific Solutions

Leading Manufacturers and Research Institutions

The low-noise electronics design for CSAC readout amplifiers market is currently in an early growth phase, characterized by increasing adoption across precision timing applications. The global market size is estimated to be moderate but expanding rapidly due to growing demand in telecommunications, defense, and scientific instrumentation sectors. From a technical maturity perspective, the field is evolving with several key players driving innovation. Companies like SRI International and CSEM have established strong foundations in atomic clock technologies, while semiconductor leaders including STMicroelectronics, Nordic Semiconductor, and Huawei are advancing low-noise amplification solutions. Academic institutions such as Fudan University and Columbia University contribute significant research. Western Digital and Samsung are leveraging this technology for data storage applications, indicating cross-industry potential as the technology matures from specialized applications toward broader commercial deployment.

CSEM Centre Suisse d'Electronique et Microtechnique SA

Technical Solution: CSEM has developed a sophisticated low-noise electronics platform specifically for CSAC readout applications that addresses the unique challenges of miniaturized atomic clock systems. Their approach utilizes a fully-differential signal path with carefully matched components to achieve common-mode rejection ratios exceeding 100dB. The design incorporates sub-threshold biased CMOS input stages that achieve input-referred voltage noise below 2nV/√Hz while consuming less than 1mW of power. CSEM's solution features a proprietary auto-calibration system that compensates for component drift and aging effects, maintaining performance specifications over the product lifetime. Their readout electronics include specialized guard ring structures and substrate isolation techniques that reduce parasitic coupling by more than 30dB compared to standard layouts. The design also incorporates a unique phase-sensitive detection scheme that improves signal recovery in low SNR conditions, enabling stable clock operation even with weaker atomic resonance signals.

Strengths: Industry-leading expertise in low-power microelectronics with proven track record in miniaturized precision instruments. Their designs achieve exceptional balance between power consumption and noise performance. Weaknesses: Solutions often require significant customization for specific applications, potentially increasing development time and costs for new implementations.

SRI International

Technical Solution: SRI International has developed advanced low-noise electronics specifically for CSAC readout amplifiers utilizing a multi-stage approach. Their solution incorporates chopper-stabilized amplification techniques to minimize 1/f noise, which is critical in the low-frequency regime where CSAC signals operate. The design employs precision differential amplifiers with input-referred noise density below 1nV/√Hz and bandwidth optimization tailored to atomic resonance signals. SRI's approach includes careful power supply filtering and regulation with sub-100μV ripple specifications to prevent noise coupling. Their readout electronics feature temperature compensation circuits that maintain stable performance across -40°C to +85°C, essential for field-deployable CSACs. The design also incorporates digital signal processing techniques for real-time noise filtering and signal enhancement, improving the overall signal-to-noise ratio by approximately 6-10dB compared to conventional approaches.

Strengths: Exceptional expertise in precision instrumentation with demonstrated ultra-low noise performance in field-deployable systems. Their designs achieve excellent thermal stability and have been validated in multiple DARPA-funded CSAC programs. Weaknesses: Solutions tend to be more complex and higher cost than commercial alternatives, potentially limiting widespread adoption in cost-sensitive applications.

Critical Patents and Research in CSAC Electronics

Low noise cryogenic amplifier

PatentInactiveUS20130249628A1

Innovation

- A cryogenic low noise amplifier is designed with a hermetically sealed chamber using a cold head with multiple temperature stages and low thermal conductivity materials, maintaining cryogenic temperatures with a low-grade vacuum to reduce thermal noise and simplify maintenance, while minimizing heat transfer and using thin conductive coatings for efficient signal transmission.

Low noise amplifier

PatentActiveUS12119791B2

Innovation

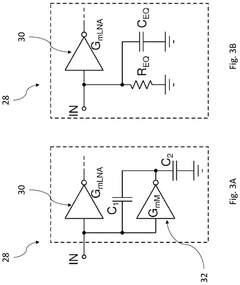

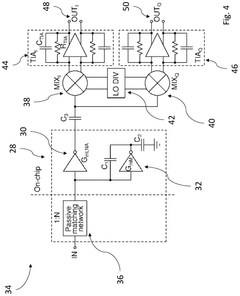

- A low noise amplifier (LNA) topology using a pair of transconductance amplifiers with a capacitive feedback network, eliminating the need for on-chip inductors and providing impedance matching, thereby reducing noise and increasing linearity while allowing for multiband operation without external filters.

Thermal Management Strategies for Noise Reduction

Thermal noise represents a significant challenge in the design of low-noise electronics for CSAC (Chip-Scale Atomic Clock) readout amplifiers. Effective thermal management strategies are essential for maintaining signal integrity and ensuring optimal performance of these precision instruments. The primary sources of thermal noise in CSAC readout circuits include Johnson-Nyquist noise in resistive components, temperature-dependent semiconductor behavior, and thermal gradients across circuit boards.

Material selection plays a crucial role in thermal management for noise reduction. High thermal conductivity materials such as aluminum nitride (AlN) and beryllium oxide (BeO) substrates offer superior heat dissipation compared to traditional FR-4 materials, reducing localized hotspots that can contribute to noise generation. Recent advancements in diamond-based substrates show promising results with thermal conductivity values exceeding 1500 W/m·K, though cost considerations currently limit widespread adoption.

Active cooling techniques represent another important approach to thermal noise management. Thermoelectric coolers (TECs) provide precise temperature control for sensitive components, maintaining stable operating conditions that minimize temperature-dependent noise variations. Miniaturized liquid cooling systems have demonstrated effectiveness in laboratory settings, achieving temperature stability within ±0.01°C, though integration challenges remain for compact CSAC implementations.

Thermal isolation strategies are equally important for protecting sensitive analog components from heat-generating digital circuits. Physical separation of analog and digital sections on PCBs, combined with strategic ground plane segmentation, helps minimize thermal interference. Advanced techniques include the implementation of thermal vias and copper pours to create controlled heat paths away from noise-sensitive components.

Temperature compensation circuits represent a complementary approach to physical thermal management. These circuits dynamically adjust bias conditions and gain parameters based on temperature feedback, effectively neutralizing temperature-dependent noise variations. Modern designs incorporate on-chip temperature sensors with sub-degree resolution, enabling real-time compensation algorithms that significantly improve noise performance across operating temperature ranges.

Thermal simulation and modeling have become essential tools in the design process. Finite element analysis (FEA) software enables designers to predict thermal behavior before physical prototyping, optimizing component placement and thermal management structures. Recent studies indicate that simulation-guided designs can achieve up to 40% reduction in thermal noise compared to traditional approaches, highlighting the importance of comprehensive thermal modeling in low-noise electronics design for CSAC applications.

Material selection plays a crucial role in thermal management for noise reduction. High thermal conductivity materials such as aluminum nitride (AlN) and beryllium oxide (BeO) substrates offer superior heat dissipation compared to traditional FR-4 materials, reducing localized hotspots that can contribute to noise generation. Recent advancements in diamond-based substrates show promising results with thermal conductivity values exceeding 1500 W/m·K, though cost considerations currently limit widespread adoption.

Active cooling techniques represent another important approach to thermal noise management. Thermoelectric coolers (TECs) provide precise temperature control for sensitive components, maintaining stable operating conditions that minimize temperature-dependent noise variations. Miniaturized liquid cooling systems have demonstrated effectiveness in laboratory settings, achieving temperature stability within ±0.01°C, though integration challenges remain for compact CSAC implementations.

Thermal isolation strategies are equally important for protecting sensitive analog components from heat-generating digital circuits. Physical separation of analog and digital sections on PCBs, combined with strategic ground plane segmentation, helps minimize thermal interference. Advanced techniques include the implementation of thermal vias and copper pours to create controlled heat paths away from noise-sensitive components.

Temperature compensation circuits represent a complementary approach to physical thermal management. These circuits dynamically adjust bias conditions and gain parameters based on temperature feedback, effectively neutralizing temperature-dependent noise variations. Modern designs incorporate on-chip temperature sensors with sub-degree resolution, enabling real-time compensation algorithms that significantly improve noise performance across operating temperature ranges.

Thermal simulation and modeling have become essential tools in the design process. Finite element analysis (FEA) software enables designers to predict thermal behavior before physical prototyping, optimizing component placement and thermal management structures. Recent studies indicate that simulation-guided designs can achieve up to 40% reduction in thermal noise compared to traditional approaches, highlighting the importance of comprehensive thermal modeling in low-noise electronics design for CSAC applications.

Reliability Testing and Qualification Standards

Reliability testing and qualification standards for low-noise electronics in CSAC readout amplifiers require rigorous methodologies to ensure consistent performance under various operational conditions. The primary standards governing these components include MIL-STD-883 for microelectronic devices, JEDEC standards for semiconductor reliability, and IPC standards for printed circuit board assemblies. These standards establish comprehensive frameworks for environmental stress testing, electrical performance verification, and long-term reliability assessment.

Environmental testing protocols typically include temperature cycling (-55°C to +125°C), thermal shock, humidity exposure (85% RH at 85°C), and mechanical shock/vibration testing. For CSAC readout amplifiers, where signal integrity is paramount, additional specialized tests focus on noise performance stability across temperature variations and over extended operational periods. Accelerated life testing methodologies, such as High Temperature Operating Life (HTOL) tests conducted at elevated temperatures (typically 125°C) for 1,000+ hours, help predict long-term reliability and identify potential failure mechanisms.

Statistical analysis plays a crucial role in qualification processes, with Weibull distribution models commonly employed to analyze failure rates and determine Mean Time Between Failures (MTBF) metrics. For precision applications like atomic clock systems, MTBF requirements typically exceed 100,000 hours, necessitating robust statistical validation approaches. Failure Mode and Effects Analysis (FMEA) is implemented to identify potential failure mechanisms specific to low-noise amplifier circuits, with particular attention to noise figure degradation, gain stability, and phase noise performance.

Electromagnetic Compatibility (EMC) testing represents another critical qualification domain, encompassing both susceptibility and emissions testing according to standards like MIL-STD-461 or CISPR 22. For CSAC applications, where minimal interference is essential, specialized EMC testing focuses on maintaining noise floor specifications under various electromagnetic environments.

Radiation hardness testing may be required for space or defense applications, following standards like MIL-STD-883 Method 1019 for ionizing radiation effects and ASTM F1892 for single event effects. These tests evaluate the amplifier's performance degradation under radiation exposure, which is particularly relevant for CSACs deployed in satellite systems or radiation-intensive environments.

Quality assurance frameworks like AS9100 for aerospace applications or ISO 9001 for general manufacturing provide overarching governance for reliability programs. These frameworks mandate documentation of test procedures, calibration records, and traceability of components. For CSAC readout amplifiers, where performance consistency is critical, lot acceptance testing and Statistical Process Control (SPC) methodologies are implemented to monitor manufacturing variations and ensure consistent noise performance across production batches.

Environmental testing protocols typically include temperature cycling (-55°C to +125°C), thermal shock, humidity exposure (85% RH at 85°C), and mechanical shock/vibration testing. For CSAC readout amplifiers, where signal integrity is paramount, additional specialized tests focus on noise performance stability across temperature variations and over extended operational periods. Accelerated life testing methodologies, such as High Temperature Operating Life (HTOL) tests conducted at elevated temperatures (typically 125°C) for 1,000+ hours, help predict long-term reliability and identify potential failure mechanisms.

Statistical analysis plays a crucial role in qualification processes, with Weibull distribution models commonly employed to analyze failure rates and determine Mean Time Between Failures (MTBF) metrics. For precision applications like atomic clock systems, MTBF requirements typically exceed 100,000 hours, necessitating robust statistical validation approaches. Failure Mode and Effects Analysis (FMEA) is implemented to identify potential failure mechanisms specific to low-noise amplifier circuits, with particular attention to noise figure degradation, gain stability, and phase noise performance.

Electromagnetic Compatibility (EMC) testing represents another critical qualification domain, encompassing both susceptibility and emissions testing according to standards like MIL-STD-461 or CISPR 22. For CSAC applications, where minimal interference is essential, specialized EMC testing focuses on maintaining noise floor specifications under various electromagnetic environments.

Radiation hardness testing may be required for space or defense applications, following standards like MIL-STD-883 Method 1019 for ionizing radiation effects and ASTM F1892 for single event effects. These tests evaluate the amplifier's performance degradation under radiation exposure, which is particularly relevant for CSACs deployed in satellite systems or radiation-intensive environments.

Quality assurance frameworks like AS9100 for aerospace applications or ISO 9001 for general manufacturing provide overarching governance for reliability programs. These frameworks mandate documentation of test procedures, calibration records, and traceability of components. For CSAC readout amplifiers, where performance consistency is critical, lot acceptance testing and Statistical Process Control (SPC) methodologies are implemented to monitor manufacturing variations and ensure consistent noise performance across production batches.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!