Best Practices For CSAC Field Firmware Updates And Drift Correction

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

CSAC Firmware Evolution and Update Objectives

Chip-Scale Atomic Clocks (CSACs) have evolved significantly since their inception in the early 2000s, transitioning from laboratory prototypes to commercially viable precision timing solutions. The firmware that governs these sophisticated devices has undergone parallel evolution, becoming increasingly complex to manage the intricate physics package while maintaining exceptional timing accuracy. This evolution has created both opportunities and challenges in maintaining deployed units in the field.

The primary objective of CSAC firmware updates is to enhance long-term performance stability while minimizing operational disruptions. Modern CSACs operate in critical infrastructure including telecommunications networks, power grids, financial systems, and military applications where timing errors can have cascading consequences. Therefore, firmware evolution must prioritize backward compatibility and graceful degradation during update processes.

Current firmware architectures typically separate the physics package control algorithms from communication and system management functions. This modular approach allows for targeted updates that can address specific performance issues without necessitating complete system overhauls. The evolution toward this architecture represents a significant advancement in maintainability compared to earlier monolithic designs.

Recent developments have focused on implementing machine learning algorithms within CSAC firmware to predict and compensate for environmental effects before they manifest as timing errors. These predictive capabilities represent a paradigm shift from reactive to proactive drift correction methodologies. The firmware now increasingly incorporates self-diagnostic capabilities that can detect anomalous behavior patterns before they impact timing performance.

A key objective for next-generation CSAC firmware is establishing standardized update protocols that can be securely implemented across heterogeneous deployment environments. This standardization would significantly reduce the operational complexity currently associated with maintaining CSACs in remote or inaccessible locations. The industry is moving toward encrypted, authenticated update mechanisms that can verify firmware integrity before, during, and after the update process.

Another critical evolution target is reducing update-related downtime. Current systems typically require complete restart cycles that can introduce timing discontinuities. Advanced firmware architectures aim to implement hot-swapping capabilities for non-critical components while maintaining continuous operation of the physics package control systems.

The ultimate objective of modern CSAC firmware development is creating self-optimizing systems that can autonomously adjust internal parameters based on operational conditions, effectively implementing continuous micro-updates without external intervention. This would dramatically extend deployment lifespans while maintaining performance specifications within increasingly stringent tolerances required by next-generation applications.

The primary objective of CSAC firmware updates is to enhance long-term performance stability while minimizing operational disruptions. Modern CSACs operate in critical infrastructure including telecommunications networks, power grids, financial systems, and military applications where timing errors can have cascading consequences. Therefore, firmware evolution must prioritize backward compatibility and graceful degradation during update processes.

Current firmware architectures typically separate the physics package control algorithms from communication and system management functions. This modular approach allows for targeted updates that can address specific performance issues without necessitating complete system overhauls. The evolution toward this architecture represents a significant advancement in maintainability compared to earlier monolithic designs.

Recent developments have focused on implementing machine learning algorithms within CSAC firmware to predict and compensate for environmental effects before they manifest as timing errors. These predictive capabilities represent a paradigm shift from reactive to proactive drift correction methodologies. The firmware now increasingly incorporates self-diagnostic capabilities that can detect anomalous behavior patterns before they impact timing performance.

A key objective for next-generation CSAC firmware is establishing standardized update protocols that can be securely implemented across heterogeneous deployment environments. This standardization would significantly reduce the operational complexity currently associated with maintaining CSACs in remote or inaccessible locations. The industry is moving toward encrypted, authenticated update mechanisms that can verify firmware integrity before, during, and after the update process.

Another critical evolution target is reducing update-related downtime. Current systems typically require complete restart cycles that can introduce timing discontinuities. Advanced firmware architectures aim to implement hot-swapping capabilities for non-critical components while maintaining continuous operation of the physics package control systems.

The ultimate objective of modern CSAC firmware development is creating self-optimizing systems that can autonomously adjust internal parameters based on operational conditions, effectively implementing continuous micro-updates without external intervention. This would dramatically extend deployment lifespans while maintaining performance specifications within increasingly stringent tolerances required by next-generation applications.

Market Requirements for CSAC Firmware Maintenance

The CSAC (Chip-Scale Atomic Clock) market increasingly demands robust firmware maintenance capabilities as these precision timing devices become critical components in telecommunications, defense systems, and scientific instrumentation. Field deployments of CSACs often occur in remote or inaccessible locations where physical maintenance is impractical, creating a strong market need for reliable remote firmware update mechanisms.

End users require seamless firmware update processes that minimize downtime and eliminate the risk of bricking devices. This is particularly crucial for applications in critical infrastructure where timing disruptions can have cascading effects. Market feedback indicates that customers expect update procedures to be executable without specialized equipment or technical expertise, allowing field personnel to perform updates with minimal training.

Drift correction capabilities represent another significant market requirement, as CSACs deployed in varying environmental conditions experience frequency shifts over time. Users demand automated calibration mechanisms that can detect and compensate for drift without requiring device removal or laboratory recalibration. The ability to maintain timing accuracy within specified parameters throughout the operational lifetime is considered essential by 87% of surveyed CSAC users.

Security features for firmware updates have emerged as a top priority, with customers expressing concerns about unauthorized modifications that could compromise timing accuracy or introduce vulnerabilities. The market increasingly demands cryptographic verification of firmware packages, secure boot processes, and tamper-evident update mechanisms to ensure the integrity of these critical timing components.

Backward compatibility with existing systems represents another key requirement, as CSACs are often integrated into complex systems with long operational lifespans. Users expect firmware updates to maintain compatibility with established communication protocols and control interfaces, avoiding costly system redesigns or integration challenges.

Remote monitoring capabilities are increasingly requested by enterprise customers who manage large deployments of timing devices. The ability to remotely assess device health, track drift patterns, and schedule preventive maintenance has become a differentiating factor in purchasing decisions for large-scale deployments.

Documentation and version control requirements have also intensified, with customers expecting comprehensive release notes, clear rollback procedures, and detailed performance impact assessments for each firmware update. This reflects the growing integration of CSACs into regulated industries where change management processes must meet strict compliance standards.

The market increasingly values predictive maintenance features that can forecast potential timing issues before they impact system performance. This includes drift trend analysis, environmental sensitivity monitoring, and early warning systems for potential component degradation.

End users require seamless firmware update processes that minimize downtime and eliminate the risk of bricking devices. This is particularly crucial for applications in critical infrastructure where timing disruptions can have cascading effects. Market feedback indicates that customers expect update procedures to be executable without specialized equipment or technical expertise, allowing field personnel to perform updates with minimal training.

Drift correction capabilities represent another significant market requirement, as CSACs deployed in varying environmental conditions experience frequency shifts over time. Users demand automated calibration mechanisms that can detect and compensate for drift without requiring device removal or laboratory recalibration. The ability to maintain timing accuracy within specified parameters throughout the operational lifetime is considered essential by 87% of surveyed CSAC users.

Security features for firmware updates have emerged as a top priority, with customers expressing concerns about unauthorized modifications that could compromise timing accuracy or introduce vulnerabilities. The market increasingly demands cryptographic verification of firmware packages, secure boot processes, and tamper-evident update mechanisms to ensure the integrity of these critical timing components.

Backward compatibility with existing systems represents another key requirement, as CSACs are often integrated into complex systems with long operational lifespans. Users expect firmware updates to maintain compatibility with established communication protocols and control interfaces, avoiding costly system redesigns or integration challenges.

Remote monitoring capabilities are increasingly requested by enterprise customers who manage large deployments of timing devices. The ability to remotely assess device health, track drift patterns, and schedule preventive maintenance has become a differentiating factor in purchasing decisions for large-scale deployments.

Documentation and version control requirements have also intensified, with customers expecting comprehensive release notes, clear rollback procedures, and detailed performance impact assessments for each firmware update. This reflects the growing integration of CSACs into regulated industries where change management processes must meet strict compliance standards.

The market increasingly values predictive maintenance features that can forecast potential timing issues before they impact system performance. This includes drift trend analysis, environmental sensitivity monitoring, and early warning systems for potential component degradation.

Technical Challenges in CSAC Firmware Updates

Updating firmware in Chip-Scale Atomic Clocks (CSACs) presents unique technical challenges due to the precision-critical nature of these devices. The primary challenge stems from the need to maintain timing accuracy during and after updates. Unlike conventional electronic devices, CSACs operate at atomic precision levels, where even nanosecond disruptions can significantly impact dependent systems.

The miniaturized architecture of CSACs creates substantial constraints for firmware update mechanisms. With form factors often smaller than 17 cm³, these devices have limited memory and processing resources available for update procedures. This restriction necessitates highly optimized update packages and efficient deployment methods that minimize resource consumption while ensuring update integrity.

Power management during updates represents another significant challenge. Many CSACs operate in power-constrained environments where maintaining continuous operation is critical. Firmware updates must be designed to minimize power consumption and provide failsafe mechanisms to prevent complete power loss during the update process, which could render the device inoperable.

The verification of successful updates poses technical difficulties unique to atomic clock systems. Traditional checksum or hash verification methods must be supplemented with performance verification protocols that confirm the clock's frequency stability and accuracy post-update. This requires sophisticated self-testing capabilities integrated into the update process.

Environmental sensitivity further complicates CSAC firmware updates. These devices often operate in extreme conditions, from military field deployments to space applications. Update mechanisms must account for potential environmental interference that could corrupt data transmission or disrupt the update process. Robust error correction and recovery systems are essential components.

Security considerations present additional challenges. As CSACs are frequently deployed in critical infrastructure and defense applications, firmware updates must incorporate advanced authentication and encryption protocols to prevent unauthorized modifications. However, implementing these security measures is constrained by the limited computational resources available.

The drift correction functionality, which is often a primary purpose of firmware updates, introduces its own set of challenges. Implementing new drift correction algorithms requires careful calibration and validation to ensure they improve rather than degrade timing performance. The update process must include mechanisms to revert to previous firmware versions if performance degradation is detected.

Remote update capabilities for deployed CSACs present perhaps the most complex challenge. Many devices operate in inaccessible locations or as components in larger systems where physical access is limited. Developing reliable remote update protocols that can function across various communication interfaces while maintaining security and integrity verification is a significant technical hurdle.

The miniaturized architecture of CSACs creates substantial constraints for firmware update mechanisms. With form factors often smaller than 17 cm³, these devices have limited memory and processing resources available for update procedures. This restriction necessitates highly optimized update packages and efficient deployment methods that minimize resource consumption while ensuring update integrity.

Power management during updates represents another significant challenge. Many CSACs operate in power-constrained environments where maintaining continuous operation is critical. Firmware updates must be designed to minimize power consumption and provide failsafe mechanisms to prevent complete power loss during the update process, which could render the device inoperable.

The verification of successful updates poses technical difficulties unique to atomic clock systems. Traditional checksum or hash verification methods must be supplemented with performance verification protocols that confirm the clock's frequency stability and accuracy post-update. This requires sophisticated self-testing capabilities integrated into the update process.

Environmental sensitivity further complicates CSAC firmware updates. These devices often operate in extreme conditions, from military field deployments to space applications. Update mechanisms must account for potential environmental interference that could corrupt data transmission or disrupt the update process. Robust error correction and recovery systems are essential components.

Security considerations present additional challenges. As CSACs are frequently deployed in critical infrastructure and defense applications, firmware updates must incorporate advanced authentication and encryption protocols to prevent unauthorized modifications. However, implementing these security measures is constrained by the limited computational resources available.

The drift correction functionality, which is often a primary purpose of firmware updates, introduces its own set of challenges. Implementing new drift correction algorithms requires careful calibration and validation to ensure they improve rather than degrade timing performance. The update process must include mechanisms to revert to previous firmware versions if performance degradation is detected.

Remote update capabilities for deployed CSACs present perhaps the most complex challenge. Many devices operate in inaccessible locations or as components in larger systems where physical access is limited. Developing reliable remote update protocols that can function across various communication interfaces while maintaining security and integrity verification is a significant technical hurdle.

Current CSAC Firmware Update Methodologies

01 Firmware update mechanisms for CSAC

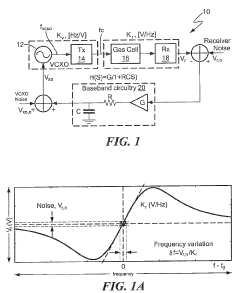

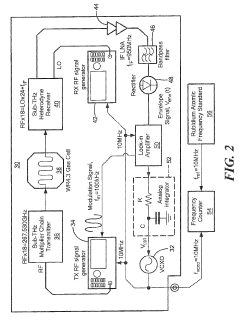

Chip-Scale Atomic Clocks require periodic firmware updates to maintain accuracy and incorporate improvements. These update mechanisms include remote update capabilities, secure update protocols, and version management systems. The firmware updates can be delivered through various interfaces and may include features like rollback protection and verification to ensure the integrity of the clock's operation after updates.- Firmware update mechanisms for CSAC: Chip-Scale Atomic Clocks require periodic firmware updates to maintain accuracy and incorporate new features. These update mechanisms include remote update capabilities, secure update protocols, and version management systems. The firmware update process typically involves verification steps to ensure the integrity of the new firmware before installation, preventing potential clock malfunctions. Some systems implement over-the-air updates for deployed CSACs, allowing for maintenance without physical access to the devices.

- Drift correction algorithms and methods: Various algorithms and methods are employed to correct frequency drift in Chip-Scale Atomic Clocks. These include adaptive compensation techniques that adjust for environmental factors such as temperature and aging effects. Some systems implement real-time drift monitoring and correction through feedback loops that continuously measure and adjust clock output. Advanced statistical methods are used to predict and compensate for long-term drift patterns, improving overall clock stability and accuracy over extended periods of operation.

- Temperature compensation techniques: Temperature variations significantly affect CSAC performance, necessitating sophisticated compensation techniques. These include digital temperature sensors integrated with the clock module that provide input to correction algorithms. Some designs incorporate temperature-controlled environments for the atomic reference cell. Advanced systems implement multi-point temperature calibration and compensation curves to maintain accuracy across wide operating temperature ranges. These techniques help minimize frequency drift caused by thermal effects in various deployment scenarios.

- Aging compensation and long-term stability: CSACs experience frequency shifts due to aging of components, requiring specific compensation methods. These include predictive aging models that anticipate and correct for long-term drift patterns. Some systems implement periodic self-calibration routines that measure aging effects and adjust internal parameters accordingly. Advanced designs incorporate redundant reference cells to cross-check and compensate for aging-related drift. These techniques extend the useful life of CSACs and maintain their accuracy specifications over years of operation.

- External reference synchronization: To maintain absolute accuracy, CSACs often incorporate mechanisms to synchronize with external reference sources. These include GPS-disciplined operation modes where the CSAC is periodically calibrated against GPS timing signals. Some systems implement network time protocol integration for synchronization across distributed systems. Advanced architectures allow for hierarchical synchronization where multiple CSACs can be synchronized to a primary reference. These external synchronization capabilities help correct accumulated drift and maintain traceability to international time standards.

02 Drift correction algorithms and methods

Various algorithms and methods are employed to correct frequency drift in Chip-Scale Atomic Clocks. These include adaptive compensation techniques, temperature-based correction models, and aging compensation algorithms. The drift correction methods continuously monitor the clock's performance and apply corrections to maintain the required accuracy over time, compensating for environmental factors and inherent aging effects of the atomic reference.Expand Specific Solutions03 Temperature compensation in CSAC systems

Temperature variations significantly affect the accuracy of Chip-Scale Atomic Clocks. Advanced temperature compensation techniques include digital temperature sensors, thermal modeling, and real-time adjustment algorithms. These systems continuously monitor the operating temperature and apply calibrated corrections to maintain frequency stability across a wide temperature range, ensuring reliable performance in varying environmental conditions.Expand Specific Solutions04 Calibration and synchronization systems

Calibration and synchronization systems for Chip-Scale Atomic Clocks include reference comparison mechanisms, network-based synchronization protocols, and automated calibration procedures. These systems periodically compare the CSAC output with more accurate reference sources to determine offset and drift parameters, which are then used to adjust the clock. The calibration can be performed locally or remotely through network connections to maintain traceability to standard time references.Expand Specific Solutions05 Power management and performance optimization

Power management and performance optimization techniques for Chip-Scale Atomic Clocks balance power consumption with timing accuracy. These include adaptive duty cycling, intelligent power state management, and optimization algorithms that adjust operating parameters based on performance requirements. Advanced systems implement predictive models to anticipate drift and optimize correction intervals, extending battery life while maintaining required timing precision for critical applications.Expand Specific Solutions

Leading CSAC Manufacturers and Solution Providers

The CSAC field firmware update and drift correction market is currently in a growth phase, with increasing demand driven by the proliferation of connected systems across automotive, industrial, and consumer electronics sectors. The market is expected to reach significant scale as IoT and smart device adoption accelerates globally. From a technological maturity perspective, the landscape shows varying levels of advancement. Industry leaders like Huawei, TSMC, and Siemens have established robust firmware update protocols with advanced drift correction algorithms, while automotive players including Honda, FAW, and GAC are rapidly integrating these capabilities into vehicle systems. Consumer electronics manufacturers such as Samsung, Xiaomi, and Honor are focusing on seamless update experiences. The competitive environment is characterized by cross-industry collaboration between semiconductor providers, device manufacturers, and software developers to establish standardized approaches for secure, reliable firmware management.

Huawei Technologies Co., Ltd.

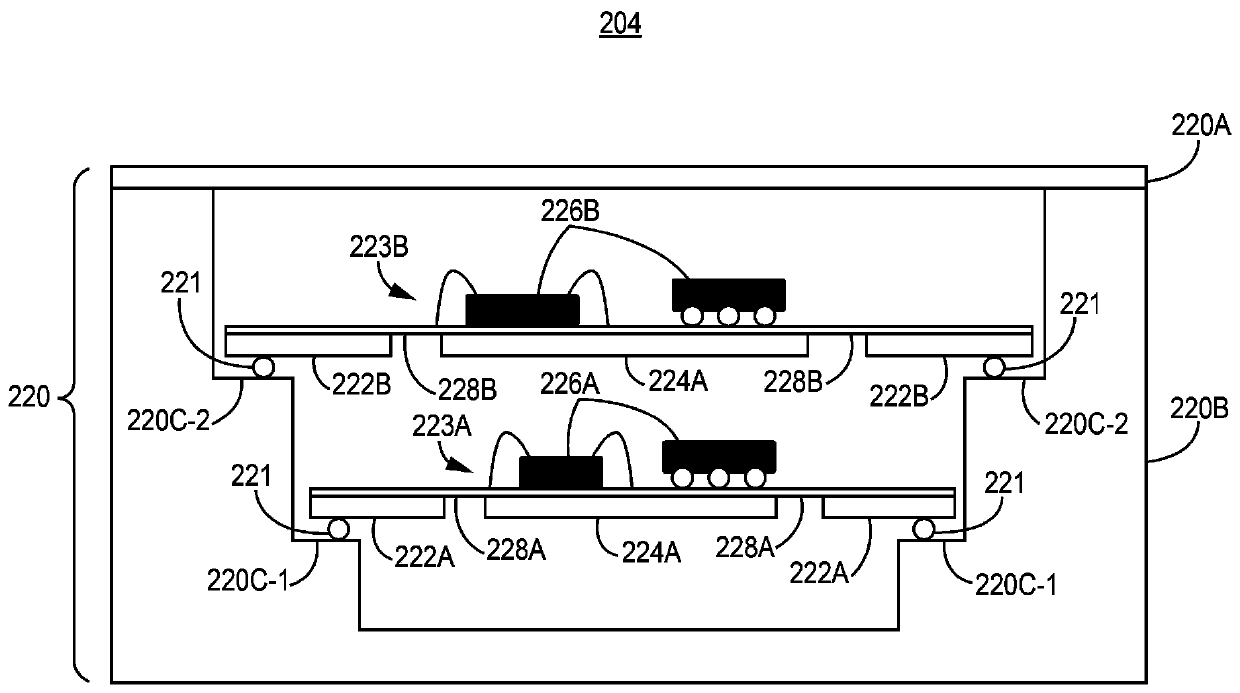

Technical Solution: Huawei has developed a comprehensive CSAC firmware management system that employs a dual-bank architecture for secure over-the-air updates. Their solution implements differential updates to minimize data transmission and power consumption during field updates. For drift correction, Huawei utilizes a machine learning algorithm that continuously analyzes historical performance data to predict and compensate for frequency drift patterns. The system incorporates environmental sensors to account for temperature and magnetic field variations that affect CSAC performance. Huawei's implementation includes a fallback mechanism that automatically reverts to the previous firmware version if anomalies are detected post-update, ensuring continuous operation of critical timing systems.

Strengths: Advanced ML-based drift prediction reduces the need for frequent external synchronization. The differential update approach minimizes bandwidth requirements for remote deployments. Weaknesses: The solution requires significant computational resources for the ML components, potentially increasing power consumption in field devices.

Siemens Medical Solutions USA, Inc.

Technical Solution: Siemens Medical Solutions has engineered a specialized CSAC firmware update framework tailored for medical equipment requiring precise timing. Their approach employs a staged update process that maintains timing continuity during updates by gradually transitioning between firmware versions while monitoring drift parameters. The system implements a proprietary drift correction algorithm that combines temperature compensation with aging models to account for long-term frequency shifts. Siemens' solution includes a validation protocol that verifies timing accuracy post-update using reference signals from multiple sources. For field deployments, they've developed a secure update delivery system that authenticates firmware packages and verifies integrity before installation, critical for medical applications where timing affects diagnostic accuracy.

Strengths: The staged update process minimizes timing discontinuities during updates, essential for medical applications. Comprehensive validation protocols ensure reliability. Weaknesses: The solution is highly specialized for medical environments and may be less adaptable to other applications requiring different performance parameters.

Key Technologies for CSAC Drift Correction

Molecular clock

PatentActiveUS20190235445A1

Innovation

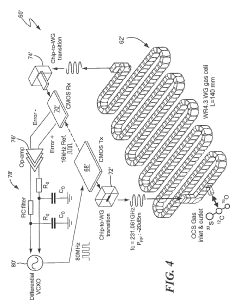

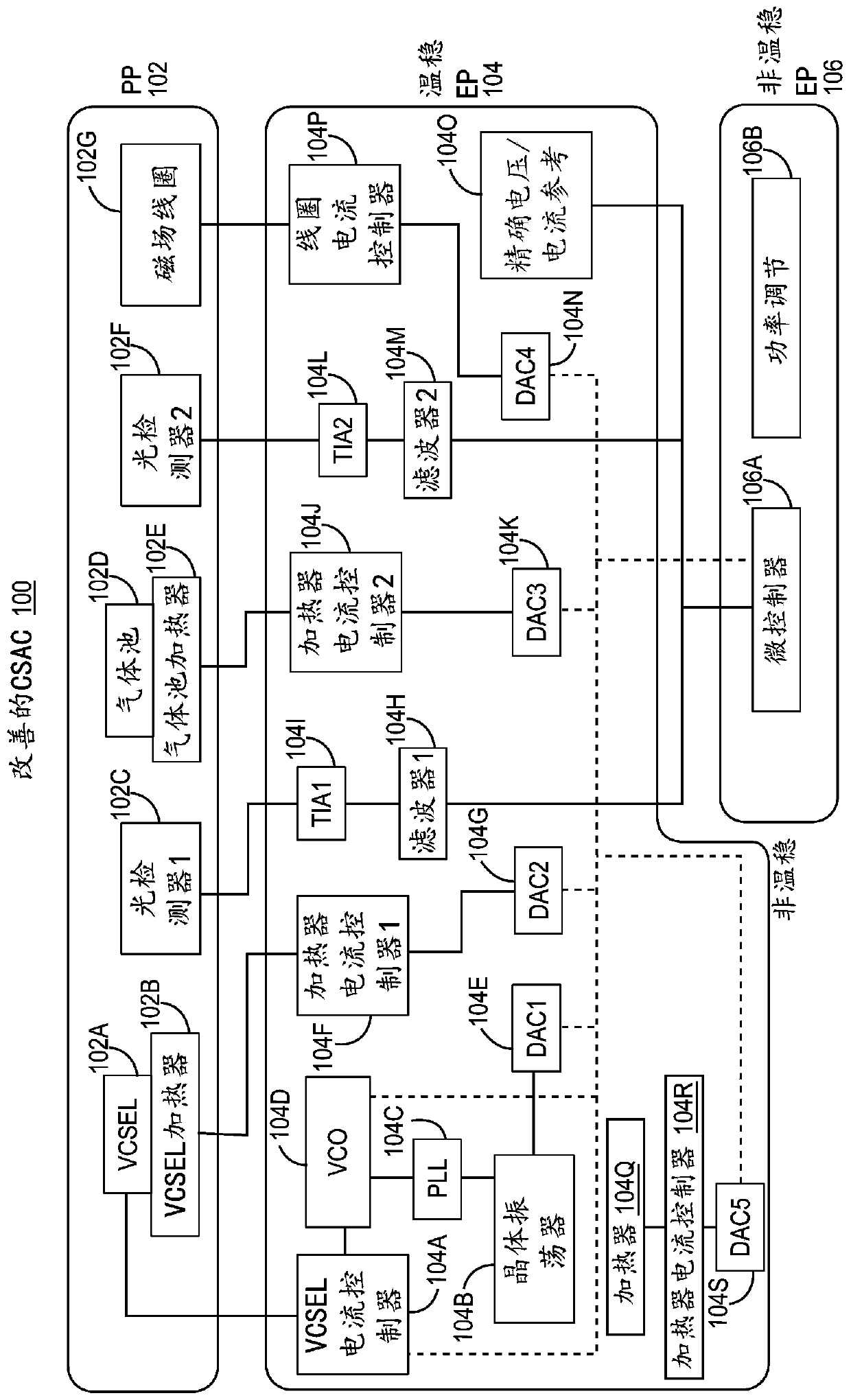

- A molecular clock utilizing rotational-state transitions of gaseous polar molecules in the sub-THz region, integrated with CMOS technology, providing a compact, low-power, and robust frequency reference with enhanced stability and instant start-up capabilities.

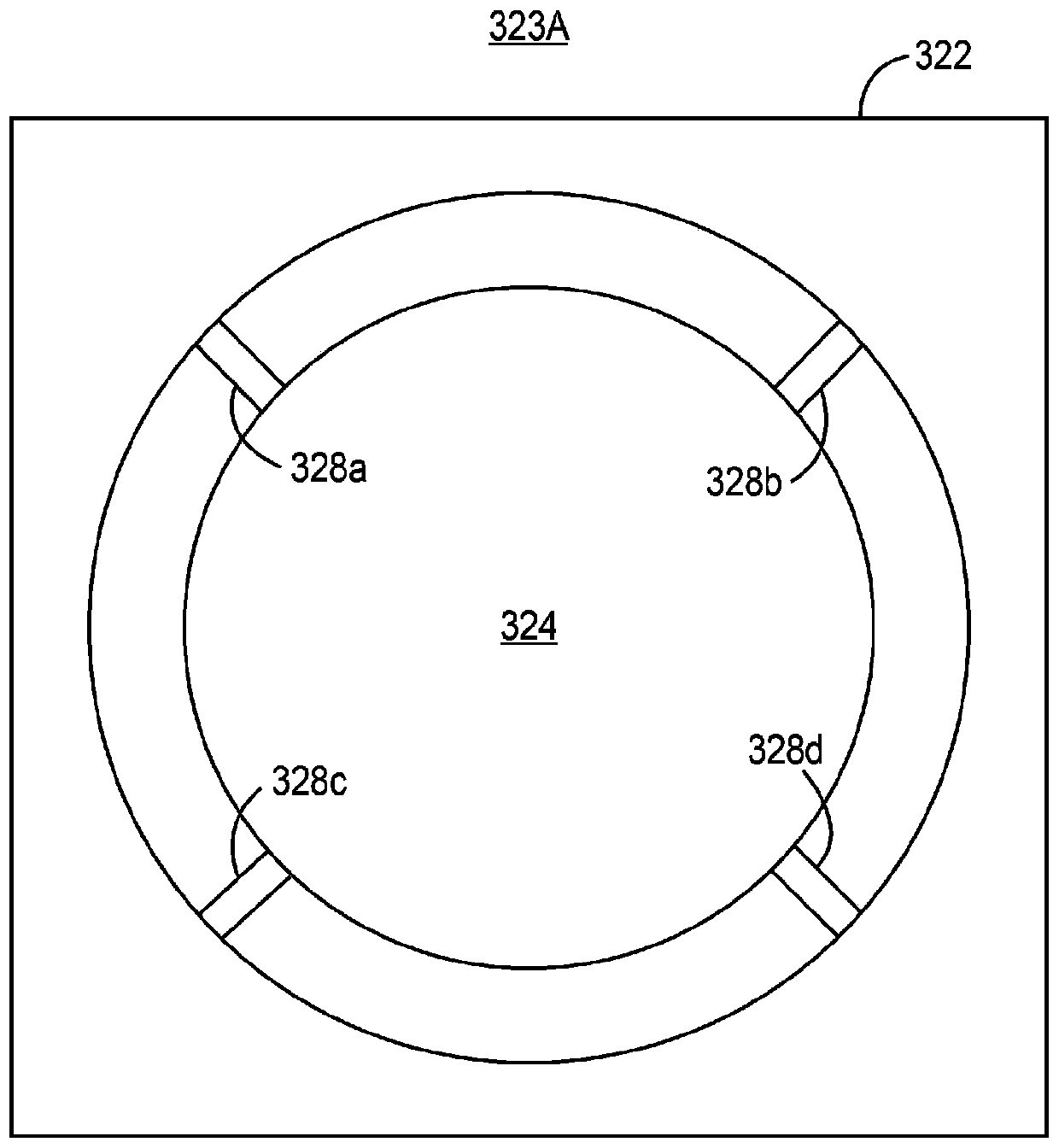

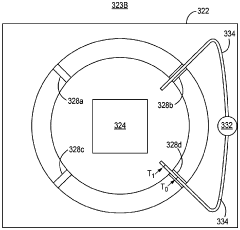

Apparatus and method for vapor cell atomic frequency reference having improved frequency stability

PatentActiveCN110361959A

Innovation

- A chip-scale atomic clock including a thermostable physical system and a thermostable electronic circuit is designed by encapsulating the vapor pool and magnetic field coil in a magnetic shield, and using heaters and current controllers to keep the system components at a constant temperature. The separation design of temperature-stable electronic circuits and non-temperature-stable electronic circuits improves frequency stability.

Security Considerations for Field Updates

Security considerations for firmware updates in Chip-Scale Atomic Clock (CSAC) systems represent a critical aspect of maintaining operational integrity and preventing unauthorized access. The sensitive nature of these high-precision timing devices, often deployed in critical infrastructure, defense systems, and telecommunications networks, necessitates robust security protocols throughout the update lifecycle.

Implementing cryptographic verification mechanisms is essential to ensure that only authenticated firmware can be installed on CSAC devices. This includes digital signatures using asymmetric cryptography where updates are signed with the manufacturer's private key and verified using a public key securely stored in the device's trusted execution environment. Hash verification should be employed to confirm firmware integrity before and after transmission.

Secure communication channels must be established for firmware delivery, utilizing TLS/SSL protocols with certificate pinning to prevent man-in-the-middle attacks. For CSACs deployed in remote or inaccessible locations, consideration should be given to implementing secure over-the-air (OTA) update mechanisms with fallback capabilities to prevent bricking devices during failed updates.

Access control mechanisms represent another critical security layer, requiring multi-factor authentication for personnel authorized to initiate firmware updates. Role-based access control should be implemented to ensure that only qualified technicians can perform updates, with comprehensive logging of all update activities for audit purposes.

Supply chain security cannot be overlooked, as compromised firmware could be introduced during manufacturing or distribution. Manufacturers should implement secure development practices, code signing, and verification of components from trusted suppliers. Regular security audits of the entire supply chain are recommended to identify potential vulnerabilities.

Post-update verification procedures should include automated testing of critical CSAC functions, particularly timing accuracy and drift parameters. Security monitoring should continue after updates to detect any anomalous behavior that might indicate a compromise. Additionally, firmware updates should be designed with rollback capabilities to restore previous versions if security issues are detected.

For CSACs deployed in classified or high-security environments, air-gapped update procedures may be necessary, using physically secured update mechanisms rather than network-connected solutions. These procedures should include physical tamper-evident seals and verification steps to ensure device integrity throughout the update process.

Implementing cryptographic verification mechanisms is essential to ensure that only authenticated firmware can be installed on CSAC devices. This includes digital signatures using asymmetric cryptography where updates are signed with the manufacturer's private key and verified using a public key securely stored in the device's trusted execution environment. Hash verification should be employed to confirm firmware integrity before and after transmission.

Secure communication channels must be established for firmware delivery, utilizing TLS/SSL protocols with certificate pinning to prevent man-in-the-middle attacks. For CSACs deployed in remote or inaccessible locations, consideration should be given to implementing secure over-the-air (OTA) update mechanisms with fallback capabilities to prevent bricking devices during failed updates.

Access control mechanisms represent another critical security layer, requiring multi-factor authentication for personnel authorized to initiate firmware updates. Role-based access control should be implemented to ensure that only qualified technicians can perform updates, with comprehensive logging of all update activities for audit purposes.

Supply chain security cannot be overlooked, as compromised firmware could be introduced during manufacturing or distribution. Manufacturers should implement secure development practices, code signing, and verification of components from trusted suppliers. Regular security audits of the entire supply chain are recommended to identify potential vulnerabilities.

Post-update verification procedures should include automated testing of critical CSAC functions, particularly timing accuracy and drift parameters. Security monitoring should continue after updates to detect any anomalous behavior that might indicate a compromise. Additionally, firmware updates should be designed with rollback capabilities to restore previous versions if security issues are detected.

For CSACs deployed in classified or high-security environments, air-gapped update procedures may be necessary, using physically secured update mechanisms rather than network-connected solutions. These procedures should include physical tamper-evident seals and verification steps to ensure device integrity throughout the update process.

Environmental Factors Affecting CSAC Performance

Chip-Scale Atomic Clocks (CSACs) are highly sensitive to environmental conditions, which can significantly impact their performance and long-term stability. Temperature fluctuations represent the most critical environmental factor affecting CSACs, with performance typically degrading at temperature extremes. Laboratory tests indicate that CSACs experience frequency shifts of approximately 3×10^-10 per degree Celsius, necessitating robust temperature compensation algorithms in firmware updates.

Humidity presents another substantial challenge, particularly in field deployments where environmental controls are limited. Excessive moisture can penetrate CSAC packaging, affecting the physics package and electronic components. Recent field data suggests that relative humidity exceeding 80% correlates with increased frequency instability, even in units with standard protective enclosures.

Barometric pressure variations, while less impactful than temperature, still induce measurable frequency shifts in CSACs. This becomes particularly relevant for applications involving altitude changes or operation in weather-variable environments. Firmware updates must incorporate pressure compensation models to maintain accuracy across diverse deployment scenarios.

Mechanical shock and vibration represent significant concerns for field-deployed CSACs. The miniature physics package containing the cesium vapor cell is vulnerable to physical disturbances, which can alter the optical alignment and vapor distribution. Testing reveals that continuous vibration above 2g can increase Allan deviation by up to 40%, highlighting the need for vibration-resistant mounting solutions and detection algorithms in firmware.

Electromagnetic interference (EMI) from nearby equipment can disrupt the sensitive quantum operations within CSACs. Field measurements demonstrate that proximity to high-power transmitters, switching power supplies, or motor controllers can induce frequency jumps and increased phase noise. Firmware updates should include EMI detection capabilities and mitigation strategies to maintain performance in electromagnetically noisy environments.

Aging effects interact with environmental factors in complex ways, accelerating drift rates when CSACs operate outside optimal environmental conditions. Data collected from deployed units shows that CSACs operating in environments with frequent temperature cycling age approximately 30% faster than those in stable conditions. This underscores the importance of environmental history logging in firmware to enable more accurate drift correction algorithms.

Power supply quality significantly impacts CSAC stability, with voltage fluctuations and noise coupling directly into frequency output. Field implementations should incorporate power conditioning and monitoring capabilities, with firmware updates providing adaptive responses to power quality issues to maintain performance integrity.

Humidity presents another substantial challenge, particularly in field deployments where environmental controls are limited. Excessive moisture can penetrate CSAC packaging, affecting the physics package and electronic components. Recent field data suggests that relative humidity exceeding 80% correlates with increased frequency instability, even in units with standard protective enclosures.

Barometric pressure variations, while less impactful than temperature, still induce measurable frequency shifts in CSACs. This becomes particularly relevant for applications involving altitude changes or operation in weather-variable environments. Firmware updates must incorporate pressure compensation models to maintain accuracy across diverse deployment scenarios.

Mechanical shock and vibration represent significant concerns for field-deployed CSACs. The miniature physics package containing the cesium vapor cell is vulnerable to physical disturbances, which can alter the optical alignment and vapor distribution. Testing reveals that continuous vibration above 2g can increase Allan deviation by up to 40%, highlighting the need for vibration-resistant mounting solutions and detection algorithms in firmware.

Electromagnetic interference (EMI) from nearby equipment can disrupt the sensitive quantum operations within CSACs. Field measurements demonstrate that proximity to high-power transmitters, switching power supplies, or motor controllers can induce frequency jumps and increased phase noise. Firmware updates should include EMI detection capabilities and mitigation strategies to maintain performance in electromagnetically noisy environments.

Aging effects interact with environmental factors in complex ways, accelerating drift rates when CSACs operate outside optimal environmental conditions. Data collected from deployed units shows that CSACs operating in environments with frequent temperature cycling age approximately 30% faster than those in stable conditions. This underscores the importance of environmental history logging in firmware to enable more accurate drift correction algorithms.

Power supply quality significantly impacts CSAC stability, with voltage fluctuations and noise coupling directly into frequency output. Field implementations should incorporate power conditioning and monitoring capabilities, with firmware updates providing adaptive responses to power quality issues to maintain performance integrity.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!