CSACs For 5G/6G Fronthaul Timing: Requirements And Integration Guides

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

CSAC Technology Evolution and Timing Goals

Chip-Scale Atomic Clocks (CSACs) have undergone significant evolution since their initial development in the early 2000s. The technology originated from DARPA-funded research aimed at miniaturizing conventional atomic clocks while maintaining comparable performance. Early CSACs were primarily focused on military applications, but their potential for telecommunications became evident as networks evolved toward higher synchronization requirements.

The progression from 3G to 4G networks introduced stricter timing requirements, but the leap to 5G has fundamentally transformed timing demands. 5G networks operate with time error tolerances measured in nanoseconds rather than microseconds, necessitating unprecedented precision in network synchronization. This shift has positioned CSACs as critical components in modern telecommunications infrastructure.

Current CSAC technology typically utilizes cesium or rubidium atoms in a vapor cell, employing coherent population trapping (CPT) resonance to achieve stable frequency references. These devices have achieved remarkable size reduction—from rack-mounted units to chip-scale packages smaller than a sugar cube—while delivering stability performance of 10^-11 to 10^-12 over one day, orders of magnitude better than traditional crystal oscillators.

For 5G fronthaul applications, timing goals have become increasingly stringent. The current specifications demand phase synchronization accuracy of ±130ns for Time Division Duplex (TDD) applications and ±65ns for enhanced Inter-Cell Interference Coordination. These requirements represent a significant challenge for traditional synchronization methods, particularly in scenarios where GNSS signals are unavailable or unreliable.

Looking toward 6G networks, timing requirements are projected to become even more demanding. Industry experts anticipate synchronization needs approaching ±30ns or better, driven by ultra-dense network deployments, higher frequency operations, and advanced beamforming techniques. These future networks will likely implement time-sensitive networking (TSN) protocols requiring sub-nanosecond precision in some applications.

The evolution of CSAC technology aims to meet these challenges through several key improvements: reducing power consumption from the current ~120mW to below 50mW, enhancing temperature stability across wider operating ranges, improving aging characteristics to extend calibration intervals, and reducing production costs to enable widespread deployment throughout network infrastructure.

Integration of CSACs into 5G/6G fronthaul systems represents a critical technological goal, requiring seamless compatibility with existing network equipment while providing the stability and reliability necessary for next-generation telecommunications services.

The progression from 3G to 4G networks introduced stricter timing requirements, but the leap to 5G has fundamentally transformed timing demands. 5G networks operate with time error tolerances measured in nanoseconds rather than microseconds, necessitating unprecedented precision in network synchronization. This shift has positioned CSACs as critical components in modern telecommunications infrastructure.

Current CSAC technology typically utilizes cesium or rubidium atoms in a vapor cell, employing coherent population trapping (CPT) resonance to achieve stable frequency references. These devices have achieved remarkable size reduction—from rack-mounted units to chip-scale packages smaller than a sugar cube—while delivering stability performance of 10^-11 to 10^-12 over one day, orders of magnitude better than traditional crystal oscillators.

For 5G fronthaul applications, timing goals have become increasingly stringent. The current specifications demand phase synchronization accuracy of ±130ns for Time Division Duplex (TDD) applications and ±65ns for enhanced Inter-Cell Interference Coordination. These requirements represent a significant challenge for traditional synchronization methods, particularly in scenarios where GNSS signals are unavailable or unreliable.

Looking toward 6G networks, timing requirements are projected to become even more demanding. Industry experts anticipate synchronization needs approaching ±30ns or better, driven by ultra-dense network deployments, higher frequency operations, and advanced beamforming techniques. These future networks will likely implement time-sensitive networking (TSN) protocols requiring sub-nanosecond precision in some applications.

The evolution of CSAC technology aims to meet these challenges through several key improvements: reducing power consumption from the current ~120mW to below 50mW, enhancing temperature stability across wider operating ranges, improving aging characteristics to extend calibration intervals, and reducing production costs to enable widespread deployment throughout network infrastructure.

Integration of CSACs into 5G/6G fronthaul systems represents a critical technological goal, requiring seamless compatibility with existing network equipment while providing the stability and reliability necessary for next-generation telecommunications services.

Market Demand for Precision Timing in 5G/6G Networks

The evolution of mobile networks from 4G to 5G and the upcoming 6G has dramatically increased the demand for precision timing solutions. As network architectures become more complex and distributed, the need for highly accurate synchronization has become paramount. The fronthaul segment of these networks, which connects radio units to centralized processing units, requires particularly stringent timing precision to ensure optimal performance.

Market research indicates that the global market for precision timing in telecommunications is experiencing robust growth, projected to reach several billion dollars by 2027. This growth is primarily driven by the ongoing deployment of 5G networks worldwide and early investments in 6G research. The transition to virtualized Radio Access Networks (vRAN) and Open RAN architectures has further amplified the need for advanced timing solutions like Chip-Scale Atomic Clocks (CSACs).

Network operators are increasingly recognizing that inadequate timing synchronization directly impacts service quality, network capacity, and operational efficiency. Field studies have demonstrated that timing errors as small as 130 nanoseconds can cause significant degradation in 5G network performance, particularly in applications requiring ultra-reliable low latency communications (URLLC).

The industrial sector represents another significant market driver, with smart factories and Industry 4.0 initiatives requiring precise synchronization for time-sensitive networking (TSN) applications. These environments demand timing accuracy in the sub-microsecond range to coordinate automated systems and ensure production efficiency.

Autonomous vehicle infrastructure and smart city deployments are emerging as substantial markets for precision timing solutions. These applications rely on synchronized networks to coordinate traffic management systems, emergency services, and vehicle-to-everything (V2X) communications, all of which require timing accuracy that only solutions like CSACs can provide.

Geographically, North America and East Asia currently lead in demand for advanced timing solutions, corresponding to their aggressive 5G deployment schedules. However, Europe is rapidly catching up as its 5G rollouts accelerate. Developing markets in South Asia and Africa represent significant future growth potential as they begin their 5G journeys.

The financial implications of timing failures have become a key consideration for network operators. Recent industry analyses suggest that synchronization failures can cost major operators millions in lost revenue and remediation expenses. This economic reality has transformed precision timing from a technical consideration to a business imperative, driving investment in more reliable solutions like CSACs.

Market research indicates that the global market for precision timing in telecommunications is experiencing robust growth, projected to reach several billion dollars by 2027. This growth is primarily driven by the ongoing deployment of 5G networks worldwide and early investments in 6G research. The transition to virtualized Radio Access Networks (vRAN) and Open RAN architectures has further amplified the need for advanced timing solutions like Chip-Scale Atomic Clocks (CSACs).

Network operators are increasingly recognizing that inadequate timing synchronization directly impacts service quality, network capacity, and operational efficiency. Field studies have demonstrated that timing errors as small as 130 nanoseconds can cause significant degradation in 5G network performance, particularly in applications requiring ultra-reliable low latency communications (URLLC).

The industrial sector represents another significant market driver, with smart factories and Industry 4.0 initiatives requiring precise synchronization for time-sensitive networking (TSN) applications. These environments demand timing accuracy in the sub-microsecond range to coordinate automated systems and ensure production efficiency.

Autonomous vehicle infrastructure and smart city deployments are emerging as substantial markets for precision timing solutions. These applications rely on synchronized networks to coordinate traffic management systems, emergency services, and vehicle-to-everything (V2X) communications, all of which require timing accuracy that only solutions like CSACs can provide.

Geographically, North America and East Asia currently lead in demand for advanced timing solutions, corresponding to their aggressive 5G deployment schedules. However, Europe is rapidly catching up as its 5G rollouts accelerate. Developing markets in South Asia and Africa represent significant future growth potential as they begin their 5G journeys.

The financial implications of timing failures have become a key consideration for network operators. Recent industry analyses suggest that synchronization failures can cost major operators millions in lost revenue and remediation expenses. This economic reality has transformed precision timing from a technical consideration to a business imperative, driving investment in more reliable solutions like CSACs.

Current CSAC Technology Landscape and Challenges

The current CSAC (Chip-Scale Atomic Clock) technology landscape presents both significant advancements and persistent challenges in meeting the stringent timing requirements of 5G and emerging 6G fronthaul networks. CSACs have evolved considerably since their introduction by DARPA in the early 2000s, with commercial availability beginning around 2011. Today's CSACs typically achieve stability performance of 1.5×10^-10 at one second, with a size reduction of approximately 100 times compared to traditional atomic clocks.

The global CSAC market is dominated by a handful of key manufacturers, including Microchip Technology, Frequency Electronics, Safran, AccuBeat, and Excelitas Technologies. Microchip's SA.45s CSAC remains the industry benchmark, offering a volume of less than 17 cc and power consumption under 120 mW. However, despite these impressive specifications, current CSAC technology faces several critical limitations when applied to 5G/6G fronthaul timing applications.

Primary technical challenges include achieving the ultra-precise synchronization required for 5G/6G networks, which demand timing accuracy in the sub-nanosecond range. Current CSACs typically provide accuracy in the range of 10^-10 to 10^-11, which may be insufficient for advanced fronthaul applications requiring phase coherence across distributed antenna systems. Additionally, aging effects and environmental sensitivities (particularly to temperature variations and magnetic fields) continue to impact long-term stability performance.

Power consumption remains another significant hurdle. While dramatically improved from traditional atomic clocks, the current 120-150 mW consumption of commercial CSACs still presents challenges for deployment in power-constrained edge computing environments that will characterize many 6G implementations. This limitation becomes particularly acute when considering the massive deployment scale anticipated for 5G/6G infrastructure.

Manufacturing scalability and cost factors also present substantial challenges. Current CSAC production processes involve complex MEMS fabrication techniques and precision assembly of optical components, resulting in unit costs that remain prohibitively high for widespread deployment across all network elements. Typical commercial CSACs cost between $1,500-$5,000 per unit, creating economic barriers to universal adoption.

Integration challenges persist regarding the interfacing of CSACs with existing network equipment. Standard protocols for timing distribution (such as IEEE 1588 PTP and SyncE) require additional hardware and software adaptations to fully leverage CSAC capabilities, creating implementation complexities for network operators seeking to upgrade existing infrastructure.

The geographical distribution of CSAC technology development remains heavily concentrated in North America and Europe, with emerging research centers in Asia, particularly in China, Japan, and South Korea, increasingly contributing to the field's advancement.

The global CSAC market is dominated by a handful of key manufacturers, including Microchip Technology, Frequency Electronics, Safran, AccuBeat, and Excelitas Technologies. Microchip's SA.45s CSAC remains the industry benchmark, offering a volume of less than 17 cc and power consumption under 120 mW. However, despite these impressive specifications, current CSAC technology faces several critical limitations when applied to 5G/6G fronthaul timing applications.

Primary technical challenges include achieving the ultra-precise synchronization required for 5G/6G networks, which demand timing accuracy in the sub-nanosecond range. Current CSACs typically provide accuracy in the range of 10^-10 to 10^-11, which may be insufficient for advanced fronthaul applications requiring phase coherence across distributed antenna systems. Additionally, aging effects and environmental sensitivities (particularly to temperature variations and magnetic fields) continue to impact long-term stability performance.

Power consumption remains another significant hurdle. While dramatically improved from traditional atomic clocks, the current 120-150 mW consumption of commercial CSACs still presents challenges for deployment in power-constrained edge computing environments that will characterize many 6G implementations. This limitation becomes particularly acute when considering the massive deployment scale anticipated for 5G/6G infrastructure.

Manufacturing scalability and cost factors also present substantial challenges. Current CSAC production processes involve complex MEMS fabrication techniques and precision assembly of optical components, resulting in unit costs that remain prohibitively high for widespread deployment across all network elements. Typical commercial CSACs cost between $1,500-$5,000 per unit, creating economic barriers to universal adoption.

Integration challenges persist regarding the interfacing of CSACs with existing network equipment. Standard protocols for timing distribution (such as IEEE 1588 PTP and SyncE) require additional hardware and software adaptations to fully leverage CSAC capabilities, creating implementation complexities for network operators seeking to upgrade existing infrastructure.

The geographical distribution of CSAC technology development remains heavily concentrated in North America and Europe, with emerging research centers in Asia, particularly in China, Japan, and South Korea, increasingly contributing to the field's advancement.

Fronthaul Timing Solutions and Implementation Approaches

01 CSAC design and architecture for improved timing precision

Chip Scale Atomic Clocks employ specific design architectures to achieve high timing precision in compact form factors. These designs include specialized vacuum packaging, miniaturized physics packages, and integrated control electronics that work together to maintain stable atomic resonance. The architecture typically incorporates MEMS technology and specialized fabrication techniques to reduce size while preserving the precision timing capabilities essential for applications requiring high accuracy in small devices.- CSAC design and architecture for improved timing precision: Chip Scale Atomic Clocks employ specific design architectures to achieve high timing precision in compact form factors. These designs include specialized physics packages, integrated control electronics, and optimized resonance chambers that maintain stable atomic transitions. The architecture typically incorporates vapor cells containing alkali metals like rubidium or cesium, with careful thermal management and shielding to minimize environmental interference, resulting in improved timing stability and precision.

- Temperature compensation techniques in CSACs: Temperature fluctuations significantly impact the timing precision of atomic clocks. Advanced temperature compensation techniques are implemented in CSACs to maintain timing accuracy across varying environmental conditions. These include active thermal control systems, temperature-insensitive buffer gas mixtures, and digital compensation algorithms that adjust for temperature-induced frequency shifts. Such techniques enable CSACs to maintain high precision timing even when subjected to temperature variations in field applications.

- Miniaturization technologies for high-precision CSACs: Miniaturization technologies are crucial for developing high-precision CSACs while maintaining small form factors. These technologies include MEMS fabrication techniques, wafer-level packaging, and integration of optical components on silicon substrates. Advanced manufacturing processes allow for the creation of microscale vapor cells and resonance cavities while preserving the quantum properties necessary for precise timing. These approaches enable the development of compact atomic clocks with timing precision suitable for portable and space-constrained applications.

- Power optimization for stable CSAC operation: Power consumption management is essential for maintaining stable CSAC operation while extending battery life in portable applications. Advanced power optimization techniques include pulsed operation modes, low-power electronics, and efficient laser or microwave sources. These approaches minimize power consumption while maintaining the stability of atomic transitions necessary for precise timing. Power-efficient designs enable CSACs to provide high-precision timing in battery-operated systems and energy-constrained environments.

- Signal processing algorithms for enhanced timing accuracy: Advanced signal processing algorithms significantly enhance the timing accuracy of CSACs. These include digital lock-in techniques, adaptive filtering, and frequency stabilization algorithms that compensate for noise and drift. Machine learning approaches are also employed to predict and correct timing errors based on historical performance data. By implementing sophisticated signal processing, CSACs can achieve sub-nanosecond timing precision and maintain synchronization across distributed systems, making them suitable for applications requiring extreme timing accuracy.

02 Temperature compensation and environmental stability techniques

Temperature variations and environmental factors can significantly affect the timing precision of CSACs. Advanced compensation techniques are implemented to maintain stability across varying conditions. These include thermal isolation structures, active temperature control systems, and compensation algorithms that adjust for environmental changes. Such techniques enable CSACs to maintain their high precision timing even when deployed in challenging environments with temperature fluctuations, vibration, or other disturbances.Expand Specific Solutions03 Integration with electronic systems and synchronization methods

CSACs require specialized integration methods to effectively synchronize with larger electronic systems while maintaining their precision. This includes interface protocols, signal conditioning circuits, and synchronization algorithms that allow the atomic clock to provide reference timing to various system components. The integration approaches focus on minimizing signal degradation, reducing electromagnetic interference, and ensuring proper power management to preserve the inherent precision of the atomic clock reference.Expand Specific Solutions04 Quantum physics and atomic resonance optimization

The fundamental timing precision of CSACs depends on optimizing atomic resonance phenomena based on quantum physics principles. This involves techniques for state preparation, coherent population trapping, laser stabilization, and detection of atomic transitions. By refining these quantum processes, engineers can enhance the stability and accuracy of the clock's frequency output. Advanced methods include improved optical pumping techniques, refined spectroscopy methods, and specialized signal processing to extract the most precise timing information from atomic transitions.Expand Specific Solutions05 Miniaturization and power efficiency improvements

Achieving high timing precision while reducing size and power consumption represents a critical challenge in CSAC development. Innovations in this area include advanced fabrication techniques, low-power electronics, and efficient atomic interrogation methods. These improvements enable CSACs to maintain sub-nanosecond precision while operating on minimal power, making them suitable for portable and battery-powered applications where both size and energy efficiency are crucial without compromising timing performance.Expand Specific Solutions

Key CSAC Manufacturers and Network Equipment Providers

The 5G/6G fronthaul timing market using CSACs (Chip-Scale Atomic Clocks) is in its early growth phase, with an expanding market as networks transition to more precise timing requirements. The technology is approaching maturity but still evolving, particularly for 6G applications. Major telecommunications equipment providers like Huawei, Ericsson, Nokia, and Samsung are leading development efforts, with significant contributions from ZTE and NEC. Network operators including China Mobile, SK Telecom, and NTT Docomo are driving implementation requirements. The competitive landscape shows traditional telecom vendors competing with specialized timing solution providers like Viavi Solutions and Murata Manufacturing, creating a dynamic market where technical expertise in precision timing is becoming a critical differentiator for next-generation network infrastructure.

Telefonaktiebolaget LM Ericsson

Technical Solution: Ericsson has developed a comprehensive CSAC integration framework for 5G/6G fronthaul timing applications. Their solution combines miniaturized atomic clock technology with advanced synchronization algorithms to meet the stringent timing requirements of next-generation networks. Ericsson's approach utilizes a distributed timing architecture where CSACs are strategically deployed at critical network nodes, complemented by their Timing as a Service (TaaS) platform that provides centralized monitoring and management. The company's implementation achieves phase alignment accuracy of ±20ns across the network, supporting enhanced MIMO and beamforming capabilities required for 5G-Advanced and 6G. Their CSACs feature built-in redundancy mechanisms that automatically switch to alternative timing sources if degradation is detected, ensuring continuous operation even during GNSS outages. Ericsson has also developed specialized fronthaul interfaces that leverage these precise timing capabilities to optimize functional splits in Cloud RAN architectures.

Strengths: Excellent integration with cloud-native network architectures; robust redundancy features; comprehensive management system for timing resources. Weaknesses: Higher implementation complexity requiring significant network planning; relatively higher power consumption compared to some competitors; requires specialized training for network engineers.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed advanced CSAC solutions specifically designed for 5G/6G fronthaul timing requirements. Their approach integrates miniaturized atomic clock technology with their 5G base stations to achieve sub-nanosecond synchronization accuracy. Huawei's CSACs utilize rubidium-based atomic resonance with proprietary ASIC designs that reduce power consumption by approximately 40% compared to traditional timing solutions. Their implementation includes adaptive temperature compensation mechanisms that maintain stability across -40°C to +85°C operational environments, critical for outdoor deployment scenarios. Huawei has also pioneered the integration of these timing solutions with their enhanced Common Public Radio Interface (eCPRI) implementations, allowing for precise phase alignment across distributed radio units with timing error below 50ns, which exceeds the 3GPP requirements for 5G-Advanced applications.

Strengths: Superior integration with existing Huawei network infrastructure; exceptional temperature stability; lower power consumption than competitors. Weaknesses: Proprietary nature limits interoperability with other vendors' equipment; higher initial cost compared to conventional timing solutions; requires specialized expertise for deployment and maintenance.

Critical Patents and Research in CSAC Technology

Radio access networks

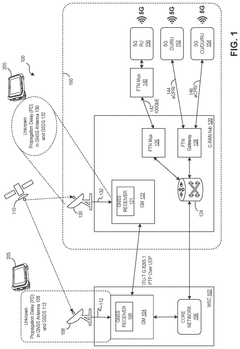

PatentPendingUS20240340883A1

Innovation

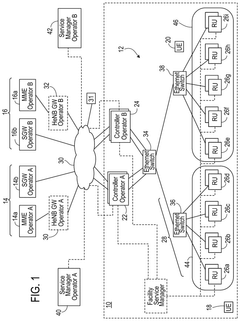

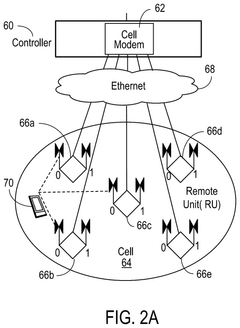

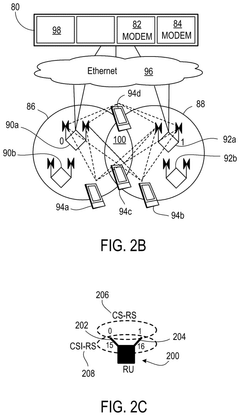

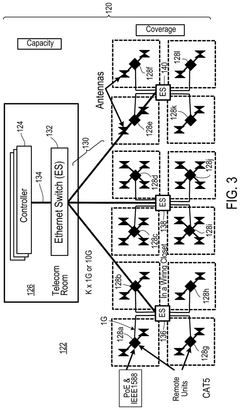

- A communication system comprising remote units and a controller, where the remote units exchange RF signals with mobile devices, and the controller, connected to an external network via an intermediate switched Ethernet network, performs real-time scheduling and compression of baseband data in the frequency domain to optimize data transmission and manage capacity dynamically.

Satellite signal propagation delay test device

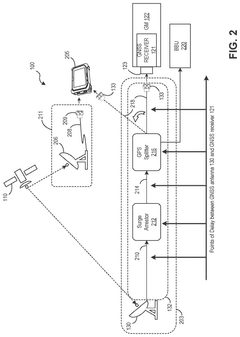

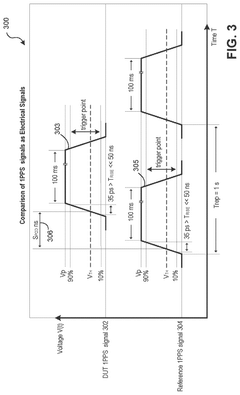

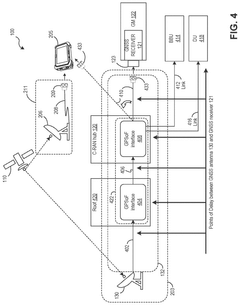

PatentActiveUS12130368B2

Innovation

- A test device is used to determine unknown propagation delays in the GNSS signal distribution system, allowing for programming a configurable delay offset in Grandmaster Clocks, thereby improving the accuracy of 1PPS signals and reducing timing errors within the network.

Standards and Compliance Requirements for Fronthaul Timing

The fronthaul timing in 5G/6G networks must adhere to stringent standards and compliance requirements to ensure seamless synchronization across the network infrastructure. The IEEE 1588 Precision Time Protocol (PTP) serves as the foundational standard, specifically with the telecom profile IEEE 1588-2008 and its enhanced version IEEE 1588-2019, which provide the framework for precise time synchronization in telecommunication networks.

ITU-T G.8271 and G.8272 standards define the time and phase synchronization aspects for packet networks, with G.8272 specifically outlining the timing characteristics for primary reference time clocks. These standards establish maximum time error (TE) limits of ±1.5 μs for fronthaul networks, which becomes increasingly challenging to maintain as network complexity grows in 6G architectures.

The O-RAN Alliance has developed specifications that build upon these standards, particularly O-RAN.WG4.CUS.0-v05.00, which details synchronization requirements for O-RAN fronthaul interfaces. These specifications mandate that Radio Units (RUs) must support both PTP and Synchronous Ethernet (SyncE) for frequency synchronization, with strict phase alignment requirements between distributed units.

For CSAC integration in fronthaul timing, compliance with ETSI EN 302 336 is essential, which governs radio equipment in the frequency range covering atomic clock operations. Additionally, 3GPP TS 38.104 outlines the base station radio transmission and reception requirements, including timing accuracy specifications that directly impact CSAC deployment.

The Small Cell Forum's specifications (SCF.173) provide guidelines for synchronization in small cell deployments, which are particularly relevant for CSAC applications due to their compact size and lower power consumption compared to traditional atomic clocks.

From a regulatory perspective, network operators must ensure that their timing solutions comply with regional telecommunications authorities' requirements. In the United States, the FCC's Part 15 regulations govern unintentional radiators, which includes timing equipment. In Europe, the Radio Equipment Directive (RED) 2014/53/EU sets compliance parameters for radio equipment, including timing devices.

As 6G development progresses, emerging standards from bodies like IEEE's Time-Sensitive Networking (TSN) task group and ITU-T's Focus Group on Technologies for Network 2030 are shaping future requirements. These evolving standards are expected to demand even more precise timing synchronization, potentially pushing the boundaries to sub-nanosecond accuracy, where CSACs will play a crucial role.

ITU-T G.8271 and G.8272 standards define the time and phase synchronization aspects for packet networks, with G.8272 specifically outlining the timing characteristics for primary reference time clocks. These standards establish maximum time error (TE) limits of ±1.5 μs for fronthaul networks, which becomes increasingly challenging to maintain as network complexity grows in 6G architectures.

The O-RAN Alliance has developed specifications that build upon these standards, particularly O-RAN.WG4.CUS.0-v05.00, which details synchronization requirements for O-RAN fronthaul interfaces. These specifications mandate that Radio Units (RUs) must support both PTP and Synchronous Ethernet (SyncE) for frequency synchronization, with strict phase alignment requirements between distributed units.

For CSAC integration in fronthaul timing, compliance with ETSI EN 302 336 is essential, which governs radio equipment in the frequency range covering atomic clock operations. Additionally, 3GPP TS 38.104 outlines the base station radio transmission and reception requirements, including timing accuracy specifications that directly impact CSAC deployment.

The Small Cell Forum's specifications (SCF.173) provide guidelines for synchronization in small cell deployments, which are particularly relevant for CSAC applications due to their compact size and lower power consumption compared to traditional atomic clocks.

From a regulatory perspective, network operators must ensure that their timing solutions comply with regional telecommunications authorities' requirements. In the United States, the FCC's Part 15 regulations govern unintentional radiators, which includes timing equipment. In Europe, the Radio Equipment Directive (RED) 2014/53/EU sets compliance parameters for radio equipment, including timing devices.

As 6G development progresses, emerging standards from bodies like IEEE's Time-Sensitive Networking (TSN) task group and ITU-T's Focus Group on Technologies for Network 2030 are shaping future requirements. These evolving standards are expected to demand even more precise timing synchronization, potentially pushing the boundaries to sub-nanosecond accuracy, where CSACs will play a crucial role.

Power Efficiency and Size Optimization Strategies

Power efficiency and size optimization are critical considerations for CSAC (Chip-Scale Atomic Clock) deployment in 5G/6G fronthaul timing applications. As network densification continues, the energy consumption and physical footprint of timing components become increasingly important factors in total cost of ownership and deployment feasibility.

Current commercial CSACs typically consume 120-150 mW of power, which represents significant improvement over previous generations but remains challenging for battery-powered or energy-constrained applications. Industry leaders are pursuing several promising approaches to further reduce power requirements. Advanced MEMS fabrication techniques are enabling smaller vapor cells with improved thermal isolation, reducing heating power requirements by up to 40%.

Innovative laser locking schemes are being developed to minimize the power needed for optical pumping while maintaining frequency stability. These include pulsed operation modes that can reduce average power consumption by cycling components during periods when full performance is not required. Such dynamic power management can achieve 30-50% power savings in real-world deployment scenarios.

Size optimization strategies focus on higher levels of integration. The latest CSACs have achieved volumes below 15 cm³, with research prototypes demonstrating potential for sub-10 cm³ implementations. Vertical integration of components is proving particularly effective, with 3D packaging technologies allowing for more efficient use of board space.

System-on-chip (SoC) approaches are integrating more of the control electronics with the physics package, reducing both size and power consumption simultaneously. Several manufacturers have demonstrated integrated solutions that combine the CSAC with temperature compensation circuits and network synchronization interfaces in a single package.

For fronthaul applications specifically, co-design approaches that optimize the CSAC characteristics for the particular timing requirements of 5G/6G networks show promise. By tailoring performance parameters to the specific needs of fronthaul timing rather than general-purpose applications, power consumption can be further reduced by 15-25% without compromising critical timing specifications.

The industry roadmap projects continued improvements, with next-generation CSACs targeting sub-100 mW power consumption and volumes below 5 cm³ within the next three years. These advancements will be crucial for enabling widespread deployment of precision timing in dense small-cell networks and edge computing nodes that characterize advanced 5G and emerging 6G architectures.

Current commercial CSACs typically consume 120-150 mW of power, which represents significant improvement over previous generations but remains challenging for battery-powered or energy-constrained applications. Industry leaders are pursuing several promising approaches to further reduce power requirements. Advanced MEMS fabrication techniques are enabling smaller vapor cells with improved thermal isolation, reducing heating power requirements by up to 40%.

Innovative laser locking schemes are being developed to minimize the power needed for optical pumping while maintaining frequency stability. These include pulsed operation modes that can reduce average power consumption by cycling components during periods when full performance is not required. Such dynamic power management can achieve 30-50% power savings in real-world deployment scenarios.

Size optimization strategies focus on higher levels of integration. The latest CSACs have achieved volumes below 15 cm³, with research prototypes demonstrating potential for sub-10 cm³ implementations. Vertical integration of components is proving particularly effective, with 3D packaging technologies allowing for more efficient use of board space.

System-on-chip (SoC) approaches are integrating more of the control electronics with the physics package, reducing both size and power consumption simultaneously. Several manufacturers have demonstrated integrated solutions that combine the CSAC with temperature compensation circuits and network synchronization interfaces in a single package.

For fronthaul applications specifically, co-design approaches that optimize the CSAC characteristics for the particular timing requirements of 5G/6G networks show promise. By tailoring performance parameters to the specific needs of fronthaul timing rather than general-purpose applications, power consumption can be further reduced by 15-25% without compromising critical timing specifications.

The industry roadmap projects continued improvements, with next-generation CSACs targeting sub-100 mW power consumption and volumes below 5 cm³ within the next three years. These advancements will be crucial for enabling widespread deployment of precision timing in dense small-cell networks and edge computing nodes that characterize advanced 5G and emerging 6G architectures.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!