Design Considerations For Low-Power Chip-Scale Atomic Clock Modules

AUG 29, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Atomic Clock Technology Evolution and Objectives

Atomic clocks have evolved significantly since their inception in the 1950s, transitioning from room-sized devices to chip-scale modules that can be integrated into portable equipment. The evolution began with cesium beam atomic clocks, which defined the second as 9,192,631,770 oscillations of the cesium-133 atom. These early atomic clocks, while revolutionary for their time, were bulky, power-hungry, and primarily used in national laboratories and telecommunications infrastructure.

The 1990s marked a significant turning point with the development of rubidium and hydrogen maser atomic clocks, which offered improved stability while reducing size requirements. However, the true breakthrough came in the early 2000s with the advent of Chip-Scale Atomic Clock (CSAC) technology, pioneered by NIST and subsequently commercialized by companies like Microsemi (now Microchip Technology). These innovations reduced power consumption from watts to milliwatts and size from liters to cubic centimeters.

Current CSAC technology typically employs coherent population trapping (CPT) in alkali metal vapor cells, most commonly using rubidium or cesium atoms. The fundamental operating principle involves creating quantum interference in atomic energy states using laser light, which allows for precise frequency reference without the traditional bulky microwave cavities. This approach has enabled dramatic miniaturization while maintaining relatively high precision.

The technical objectives for next-generation low-power chip-scale atomic clocks focus on several key parameters. Power consumption remains a critical challenge, with current targets aiming to reduce operational power from 100-150mW to below 50mW while maintaining standby power under 5mW. Size reduction continues to be important, with goals to achieve complete timing solutions under 1cm³. Stability targets include short-term stability (Allan deviation) of 1×10⁻¹¹ at 1 second and aging rates below 1×10⁻¹⁰ per month.

Environmental resilience represents another crucial objective, as CSACs must maintain performance across wider temperature ranges (-40°C to +85°C) and withstand higher shock and vibration levels to enable deployment in harsh environments. Additionally, reducing manufacturing costs from thousands to hundreds of dollars per unit is essential for broader market adoption in consumer and IoT applications.

The technology trajectory is now moving toward quantum-based approaches, including optical lattice clocks and ion trap technologies that promise stability improvements of several orders of magnitude. These advancements aim to bring laboratory-grade precision to field-deployable devices, potentially revolutionizing applications in autonomous navigation, secure communications, and distributed sensing networks where GPS signals are unavailable or vulnerable.

The 1990s marked a significant turning point with the development of rubidium and hydrogen maser atomic clocks, which offered improved stability while reducing size requirements. However, the true breakthrough came in the early 2000s with the advent of Chip-Scale Atomic Clock (CSAC) technology, pioneered by NIST and subsequently commercialized by companies like Microsemi (now Microchip Technology). These innovations reduced power consumption from watts to milliwatts and size from liters to cubic centimeters.

Current CSAC technology typically employs coherent population trapping (CPT) in alkali metal vapor cells, most commonly using rubidium or cesium atoms. The fundamental operating principle involves creating quantum interference in atomic energy states using laser light, which allows for precise frequency reference without the traditional bulky microwave cavities. This approach has enabled dramatic miniaturization while maintaining relatively high precision.

The technical objectives for next-generation low-power chip-scale atomic clocks focus on several key parameters. Power consumption remains a critical challenge, with current targets aiming to reduce operational power from 100-150mW to below 50mW while maintaining standby power under 5mW. Size reduction continues to be important, with goals to achieve complete timing solutions under 1cm³. Stability targets include short-term stability (Allan deviation) of 1×10⁻¹¹ at 1 second and aging rates below 1×10⁻¹⁰ per month.

Environmental resilience represents another crucial objective, as CSACs must maintain performance across wider temperature ranges (-40°C to +85°C) and withstand higher shock and vibration levels to enable deployment in harsh environments. Additionally, reducing manufacturing costs from thousands to hundreds of dollars per unit is essential for broader market adoption in consumer and IoT applications.

The technology trajectory is now moving toward quantum-based approaches, including optical lattice clocks and ion trap technologies that promise stability improvements of several orders of magnitude. These advancements aim to bring laboratory-grade precision to field-deployable devices, potentially revolutionizing applications in autonomous navigation, secure communications, and distributed sensing networks where GPS signals are unavailable or vulnerable.

Market Analysis for Low-Power CSAC Applications

The global market for Chip-Scale Atomic Clock (CSAC) modules is experiencing significant growth, driven by increasing demand for precise timing solutions in various applications. The current market size for low-power CSAC technology is estimated at $120 million, with projections indicating a compound annual growth rate of 8.7% over the next five years, potentially reaching $183 million by 2028.

Military and defense sectors currently dominate the CSAC market, accounting for approximately 45% of total demand. These applications require highly accurate timing for secure communications, navigation systems, and electronic warfare capabilities. The stringent requirements for size, weight, and power (SWaP) in military equipment make low-power CSACs particularly valuable in this sector.

Telecommunications represents the second-largest market segment at 25%, where CSACs are increasingly deployed in 5G infrastructure to provide the precise synchronization needed for network operation. As 5G networks continue to expand globally, demand for low-power timing solutions is expected to grow proportionally, with particular emphasis on energy efficiency for remote installations.

The emerging autonomous systems market, including unmanned aerial vehicles (UAVs) and autonomous vehicles, constitutes about 15% of current CSAC applications but shows the highest growth potential at 12.3% annually. These systems require precise timing for navigation and coordination while operating under significant power constraints.

Scientific instrumentation and space applications account for 10% of the market, with growing interest in deploying CSACs in small satellites (CubeSats) where power budgets are extremely limited. The remaining 5% encompasses various emerging applications including quantum computing infrastructure and financial trading systems.

Regional analysis reveals North America leads with 40% market share, followed by Europe (30%), Asia-Pacific (25%), and rest of world (5%). However, the Asia-Pacific region demonstrates the fastest growth rate at 10.2% annually, primarily driven by China's investments in telecommunications infrastructure and defense technologies.

Key market drivers include miniaturization trends across industries, growing demand for autonomous systems, expansion of telecommunications infrastructure, and increasing focus on energy efficiency. The primary market constraint remains the relatively high cost of CSAC technology compared to traditional timing solutions, with current prices ranging from $1,500 to $5,000 per unit depending on specifications.

Customer requirements analysis indicates growing demand for CSACs with power consumption below 100 mW, size reduction to under 10 cm³, and improved environmental stability. Price sensitivity varies significantly by application, with commercial markets showing greater price elasticity than defense applications.

Military and defense sectors currently dominate the CSAC market, accounting for approximately 45% of total demand. These applications require highly accurate timing for secure communications, navigation systems, and electronic warfare capabilities. The stringent requirements for size, weight, and power (SWaP) in military equipment make low-power CSACs particularly valuable in this sector.

Telecommunications represents the second-largest market segment at 25%, where CSACs are increasingly deployed in 5G infrastructure to provide the precise synchronization needed for network operation. As 5G networks continue to expand globally, demand for low-power timing solutions is expected to grow proportionally, with particular emphasis on energy efficiency for remote installations.

The emerging autonomous systems market, including unmanned aerial vehicles (UAVs) and autonomous vehicles, constitutes about 15% of current CSAC applications but shows the highest growth potential at 12.3% annually. These systems require precise timing for navigation and coordination while operating under significant power constraints.

Scientific instrumentation and space applications account for 10% of the market, with growing interest in deploying CSACs in small satellites (CubeSats) where power budgets are extremely limited. The remaining 5% encompasses various emerging applications including quantum computing infrastructure and financial trading systems.

Regional analysis reveals North America leads with 40% market share, followed by Europe (30%), Asia-Pacific (25%), and rest of world (5%). However, the Asia-Pacific region demonstrates the fastest growth rate at 10.2% annually, primarily driven by China's investments in telecommunications infrastructure and defense technologies.

Key market drivers include miniaturization trends across industries, growing demand for autonomous systems, expansion of telecommunications infrastructure, and increasing focus on energy efficiency. The primary market constraint remains the relatively high cost of CSAC technology compared to traditional timing solutions, with current prices ranging from $1,500 to $5,000 per unit depending on specifications.

Customer requirements analysis indicates growing demand for CSACs with power consumption below 100 mW, size reduction to under 10 cm³, and improved environmental stability. Price sensitivity varies significantly by application, with commercial markets showing greater price elasticity than defense applications.

Current Challenges in Chip-Scale Atomic Clock Development

Despite significant advancements in chip-scale atomic clock (CSAC) technology, several critical challenges continue to impede further miniaturization, power reduction, and performance optimization. The primary obstacle remains power consumption, with current commercial CSACs typically requiring 100-120 mW—still excessive for many portable and IoT applications. This power constraint directly impacts battery life and deployment options in remote sensing networks, wearable devices, and autonomous systems.

Thermal management presents another significant challenge, as atomic physics operations are highly temperature-sensitive. Temperature fluctuations can cause frequency drift and stability issues, requiring sophisticated compensation mechanisms that add complexity and power overhead. The miniaturized form factor exacerbates this problem by concentrating heat sources and limiting thermal dissipation pathways.

Manufacturing scalability continues to be problematic, with current fabrication processes involving complex integration of MEMS vapor cells, optical components, and control electronics. Yield rates remain suboptimal, driving up unit costs and limiting mass-market adoption. The industry has yet to develop fully standardized production methods compatible with high-volume semiconductor manufacturing techniques.

Long-term aging effects and reliability issues persist in CSAC technology. Performance degradation over time, particularly in harsh environments, remains insufficiently characterized. The alkali metal vapor cells can experience wall interactions and contamination that gradually reduce clock performance, while the laser sources used for atomic state manipulation show aging effects that impact stability.

Size reduction has plateaued in recent generations, with physics-based limitations creating barriers to further miniaturization. The fundamental requirement for a vapor cell of sufficient volume to maintain adequate signal-to-noise ratio establishes a practical minimum size, while vacuum packaging requirements add additional bulk.

Integration challenges with other system components remain significant. CSACs must interface with various digital systems while maintaining isolation from electromagnetic interference and mechanical vibrations. Creating effective shielding within extremely constrained dimensions presents ongoing engineering difficulties.

Cost factors continue to limit widespread adoption, with current CSACs priced between $1,500-5,000 per unit. This pricing structure restricts applications primarily to specialized military, aerospace, and telecommunications infrastructure rather than enabling the broader consumer and IoT markets that could benefit from precise timing.

Thermal management presents another significant challenge, as atomic physics operations are highly temperature-sensitive. Temperature fluctuations can cause frequency drift and stability issues, requiring sophisticated compensation mechanisms that add complexity and power overhead. The miniaturized form factor exacerbates this problem by concentrating heat sources and limiting thermal dissipation pathways.

Manufacturing scalability continues to be problematic, with current fabrication processes involving complex integration of MEMS vapor cells, optical components, and control electronics. Yield rates remain suboptimal, driving up unit costs and limiting mass-market adoption. The industry has yet to develop fully standardized production methods compatible with high-volume semiconductor manufacturing techniques.

Long-term aging effects and reliability issues persist in CSAC technology. Performance degradation over time, particularly in harsh environments, remains insufficiently characterized. The alkali metal vapor cells can experience wall interactions and contamination that gradually reduce clock performance, while the laser sources used for atomic state manipulation show aging effects that impact stability.

Size reduction has plateaued in recent generations, with physics-based limitations creating barriers to further miniaturization. The fundamental requirement for a vapor cell of sufficient volume to maintain adequate signal-to-noise ratio establishes a practical minimum size, while vacuum packaging requirements add additional bulk.

Integration challenges with other system components remain significant. CSACs must interface with various digital systems while maintaining isolation from electromagnetic interference and mechanical vibrations. Creating effective shielding within extremely constrained dimensions presents ongoing engineering difficulties.

Cost factors continue to limit widespread adoption, with current CSACs priced between $1,500-5,000 per unit. This pricing structure restricts applications primarily to specialized military, aerospace, and telecommunications infrastructure rather than enabling the broader consumer and IoT markets that could benefit from precise timing.

State-of-the-Art CSAC Design Approaches

01 Low-power consumption techniques for chip-scale atomic clocks

Various techniques are employed to reduce power consumption in chip-scale atomic clocks (CSACs), including optimized circuit designs, power management algorithms, and energy-efficient components. These approaches focus on minimizing energy usage while maintaining accurate timekeeping performance, which is crucial for portable and battery-powered applications where CSACs are increasingly being deployed.- Low-power design techniques for chip-scale atomic clocks: Various design techniques are employed to reduce power consumption in chip-scale atomic clocks (CSACs). These include optimized circuit architectures, power management systems, and specialized components that operate with minimal energy requirements. These techniques enable CSACs to maintain high precision timing while consuming significantly less power than traditional atomic clocks, making them suitable for portable and battery-powered applications.

- Thermal management solutions for power efficiency: Thermal management is critical for reducing power consumption in chip-scale atomic clocks. Innovative approaches include advanced insulation materials, efficient heat dissipation structures, and temperature control systems that minimize the energy required for maintaining optimal operating temperatures. These solutions reduce the power needed for heating the atomic vapor cells while ensuring stable frequency output and reliable performance.

- Energy-efficient vapor cell technologies: Advanced vapor cell designs significantly impact the power consumption of chip-scale atomic clocks. These include miniaturized cells with optimized dimensions, novel materials for cell walls, and specialized atomic vapor compositions that require less energy to achieve quantum state transitions. These innovations reduce the power needed for cell heating and operation while maintaining the precision timing capabilities essential for atomic clock functionality.

- Power management and sleep mode implementations: Sophisticated power management systems are implemented in chip-scale atomic clocks to minimize energy consumption. These include duty-cycling techniques, adaptive power scaling based on precision requirements, and various sleep modes that can be activated when full precision is not needed. Such implementations allow CSACs to operate for extended periods on limited power sources while maintaining time synchronization capabilities.

- Integration with low-power electronics and systems: Chip-scale atomic clocks are increasingly designed for seamless integration with other low-power electronic systems. This includes compatibility with energy-harvesting technologies, optimization for battery-powered devices, and interfaces that minimize power consumption during data transfer and synchronization. These integration approaches enable CSACs to be deployed in portable devices, IoT applications, and remote sensing systems where power availability is limited.

02 Thermal management solutions for power efficiency

Thermal management plays a critical role in reducing power consumption of chip-scale atomic clock modules. Innovative heating element designs, thermal isolation techniques, and temperature control systems help maintain the required operating temperature while minimizing energy usage. These solutions address one of the major power consumption challenges in atomic clocks, as maintaining stable temperatures for the atomic resonance cell typically accounts for a significant portion of the overall power budget.Expand Specific Solutions03 Power-saving operational modes and duty cycling

Implementation of various operational modes and duty cycling techniques allows chip-scale atomic clocks to conserve power during periods of reduced accuracy requirements. These approaches include sleep modes, standby states, and intelligent cycling between high and low power states based on application needs. By dynamically adjusting power consumption according to performance requirements, these techniques significantly extend battery life in portable applications.Expand Specific Solutions04 Advanced physics packages for power reduction

Innovations in the fundamental physics packages of chip-scale atomic clocks have led to significant power consumption improvements. These include miniaturized vapor cells, optimized optical pumping methods, and more efficient atomic resonance detection techniques. By addressing power efficiency at the core physics level, these advancements enable substantial reductions in overall energy requirements while maintaining or improving clock performance.Expand Specific Solutions05 System-level integration for power optimization

System-level approaches to power optimization involve integrating chip-scale atomic clocks with surrounding electronics and systems in ways that minimize overall energy consumption. These include adaptive power supply designs, intelligent interfacing with host systems, and optimized signal processing algorithms. By considering the atomic clock as part of a larger system, these approaches achieve power efficiencies that would not be possible when focusing on the clock module in isolation.Expand Specific Solutions

Leading Manufacturers and Research Institutions

The chip-scale atomic clock (CSAC) market is currently in a growth phase, with increasing demand for low-power, miniaturized timing solutions across various industries. The market is projected to expand significantly due to applications in telecommunications, defense, and navigation systems. Leading players include established technology corporations like Intel, Qualcomm, and Honeywell International, alongside specialized companies such as SRI International and Microchip Technology. Academic institutions including MIT, Cornell University, and Zhejiang University are advancing fundamental research in this field. The technology maturity varies, with companies like HRL Laboratories and Syrlinks SAS demonstrating commercial viability, while others like AdamanT Quanta are developing next-generation solutions. The competitive landscape reflects a blend of defense contractors, semiconductor manufacturers, and research institutions collaborating to overcome power consumption and miniaturization challenges.

SRI International

Technical Solution: SRI International has developed advanced low-power CSAC technology focusing on novel physics packages and integrated photonics approaches. Their design utilizes a unique microfabricated alkali vapor cell architecture with specialized anti-relaxation wall coatings that extend coherence times, enabling lower laser power requirements. SRI's modules incorporate integrated photonic circuits that efficiently route optical signals between components, significantly reducing optical losses and associated power requirements. Their approach features a proprietary thermal isolation structure using suspended membrane technology that creates vacuum micro-cavities around critical components, reducing thermal conductivity by over 90% compared to conventional designs[5]. SRI has implemented sophisticated digital control algorithms that optimize the duty cycle of various components, reducing average power consumption to approximately 30mW during steady-state operation. The company's latest designs incorporate MEMS-based frequency references that provide initial stabilization during warm-up, reducing the time and energy required to achieve full operational stability. Additionally, SRI has developed specialized low-power laser control circuits that maintain optimal wavelength stability while minimizing drive current requirements.

Strengths: Cutting-edge integration of photonics and MEMS technologies; exceptional power efficiency approaching theoretical limits; advanced thermal isolation techniques enabling ultra-low heating power requirements. Weaknesses: Limited production maturity compared to established commercial providers; higher initial development costs; more complex calibration requirements during manufacturing.

Honeywell International Technologies Ltd.

Technical Solution: Honeywell has developed miniaturized chip-scale atomic clock (CSAC) modules utilizing MEMS-based vapor cell technology combined with vertical-cavity surface-emitting lasers (VCSELs). Their approach focuses on hermetically sealed rubidium vapor cells with integrated heating elements that maintain optimal operating temperature while minimizing power consumption. Honeywell's design incorporates advanced power management circuits that dynamically adjust power based on operational requirements, reducing average consumption to under 120mW. Their modules feature a physics package approximately 15mm³ in volume, with specialized thermal isolation structures that minimize heat loss. The company has implemented sophisticated digital control algorithms that optimize the interrogation sequence timing, reducing duty cycles during steady-state operation[1]. Additionally, Honeywell utilizes custom ASICs for signal processing that integrate multiple functions into a single chip, further reducing power requirements and physical footprint.

Strengths: Exceptional frequency stability (1×10⁻¹¹ over one day) with industry-leading power efficiency; robust environmental performance across wide temperature ranges; proven reliability in defense applications. Weaknesses: Higher cost compared to quartz-based alternatives; longer warm-up time than desired for some applications; limited production capacity affecting commercial availability.

Critical Patents and Breakthroughs in CSAC Technology

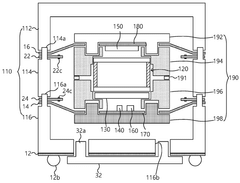

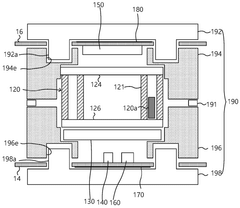

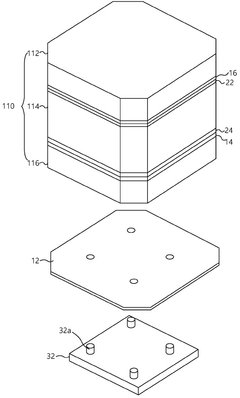

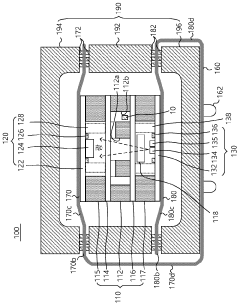

Chip-scale atomic clock and manufacturing method therefor

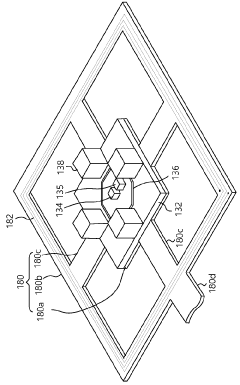

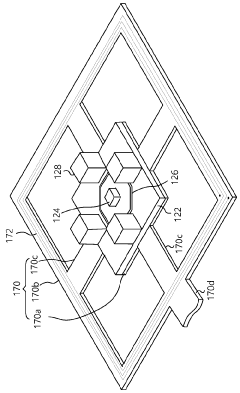

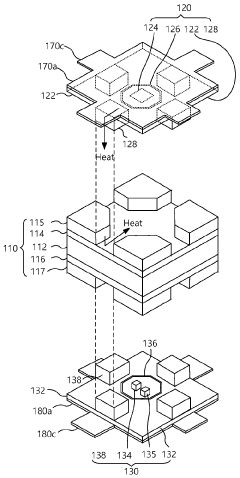

PatentWO2025121681A1

Innovation

- A chip-scale atomic clock design that suspends a vapor cell between a pair of flexible printed circuit boards, utilizing alignment parts to easily align the light source, vapor cell, and photodetector, and incorporating a magnetic field shield for external magnetic field blocking.

Chip-scale atomic clock, and method for manufacturing same

PatentWO2024101770A1

Innovation

- A chip-scale atomic clock design that suspends the vapor cell between a pair of flexible printed circuit boards, using an alignment unit for vertical alignment of the light source, vapor cell, and photodetector, and incorporates a magnetic shield for improved thermal insulation and vibration resistance, with heaters for efficient heat transfer.

Thermal Management Strategies for Miniaturized Atomic Clocks

Thermal management represents a critical challenge in the development of chip-scale atomic clock (CSAC) modules, particularly as these devices continue to miniaturize while maintaining precision timing capabilities. The physics of atomic clocks necessitates precise temperature control, as frequency stability is directly affected by thermal variations. In miniaturized atomic clocks, even small temperature fluctuations can significantly impact performance, making thermal management a cornerstone of reliable operation.

Current thermal management approaches for CSACs typically employ multi-layered strategies. Passive thermal isolation techniques utilize specialized materials with low thermal conductivity to create buffer zones around temperature-sensitive components. These materials, including aerogels and vacuum-sealed chambers, effectively minimize heat transfer between the atomic resonance cell and external environments.

Active temperature control systems represent another crucial aspect of thermal management. Miniaturized thermoelectric coolers (TECs) and microheaters are strategically integrated into CSAC designs to maintain optimal operating temperatures. Advanced feedback control algorithms continuously monitor temperature sensors and adjust heating or cooling elements accordingly, ensuring temperature stability within millikelvin ranges.

Heat dissipation pathways must be carefully engineered in these compact devices. Thermal vias, specialized heat spreaders, and miniaturized heat pipes are employed to channel excess heat away from critical components. The placement of these thermal conduits requires precise simulation and testing to avoid creating thermal gradients that could compromise clock stability.

Package-level thermal considerations also play a vital role in overall thermal management. Hermetically sealed packages with controlled internal atmospheres help isolate the atomic physics package from environmental fluctuations. Advanced ceramic and metal packaging materials with tailored thermal expansion coefficients minimize stress on internal components during temperature cycling.

Power management and thermal control are inherently linked in low-power CSAC designs. Dynamic power scaling techniques adjust operational parameters based on thermal conditions, while thermal energy harvesting approaches are being explored to recover waste heat for powering auxiliary systems. These innovations help maintain the delicate balance between power consumption and thermal stability.

Future thermal management strategies for CSACs are trending toward integrated approaches that combine multiple techniques within increasingly compact form factors. Emerging technologies such as phase-change materials, microfluidic cooling channels, and MEMS-based thermal isolators show promise for next-generation devices, potentially enabling further miniaturization while maintaining or improving thermal performance.

Current thermal management approaches for CSACs typically employ multi-layered strategies. Passive thermal isolation techniques utilize specialized materials with low thermal conductivity to create buffer zones around temperature-sensitive components. These materials, including aerogels and vacuum-sealed chambers, effectively minimize heat transfer between the atomic resonance cell and external environments.

Active temperature control systems represent another crucial aspect of thermal management. Miniaturized thermoelectric coolers (TECs) and microheaters are strategically integrated into CSAC designs to maintain optimal operating temperatures. Advanced feedback control algorithms continuously monitor temperature sensors and adjust heating or cooling elements accordingly, ensuring temperature stability within millikelvin ranges.

Heat dissipation pathways must be carefully engineered in these compact devices. Thermal vias, specialized heat spreaders, and miniaturized heat pipes are employed to channel excess heat away from critical components. The placement of these thermal conduits requires precise simulation and testing to avoid creating thermal gradients that could compromise clock stability.

Package-level thermal considerations also play a vital role in overall thermal management. Hermetically sealed packages with controlled internal atmospheres help isolate the atomic physics package from environmental fluctuations. Advanced ceramic and metal packaging materials with tailored thermal expansion coefficients minimize stress on internal components during temperature cycling.

Power management and thermal control are inherently linked in low-power CSAC designs. Dynamic power scaling techniques adjust operational parameters based on thermal conditions, while thermal energy harvesting approaches are being explored to recover waste heat for powering auxiliary systems. These innovations help maintain the delicate balance between power consumption and thermal stability.

Future thermal management strategies for CSACs are trending toward integrated approaches that combine multiple techniques within increasingly compact form factors. Emerging technologies such as phase-change materials, microfluidic cooling channels, and MEMS-based thermal isolators show promise for next-generation devices, potentially enabling further miniaturization while maintaining or improving thermal performance.

Integration Pathways for CSAC in IoT and Defense Systems

The integration of Chip-Scale Atomic Clock (CSAC) technology into IoT and defense systems requires careful consideration of both technical and operational factors. For IoT applications, CSAC modules must be adapted to operate within severe power constraints while maintaining sufficient timing accuracy. This necessitates the development of specialized power management circuits that can efficiently regulate the minimal power required for CSAC operation while accommodating the intermittent power availability common in IoT deployments.

System-on-Chip (SoC) integration represents a promising pathway, where CSAC functionality can be incorporated alongside processing and communication components. This approach requires addressing thermal isolation challenges, as atomic clock performance is temperature-sensitive. Advanced packaging techniques utilizing micro-electromechanical systems (MEMS) technology can create the necessary thermal barriers while maintaining the compact form factor essential for IoT devices.

For defense applications, integration must prioritize resilience against environmental extremes and electromagnetic interference. Hardened enclosures with appropriate shielding materials can protect the sensitive atomic resonance mechanisms without significantly increasing the overall module size. Additionally, specialized interface protocols must be developed to securely integrate CSAC timing signals with military communication systems while preventing potential timing-based vulnerabilities.

Modular design approaches offer significant advantages for both sectors. By creating standardized CSAC modules with well-defined electrical and mechanical interfaces, manufacturers can accelerate integration across diverse platforms. This approach enables field-replaceable units that can be upgraded as CSAC technology evolves, extending the operational lifespan of deployed systems.

Power delivery integration presents unique challenges, particularly for battery-operated systems. Innovative power conditioning circuits that can efficiently convert available power to the precise voltage and current requirements of CSAC physics packages are essential. These circuits must accommodate the initial power spike during warm-up while transitioning to ultra-low-power steady-state operation.

Software integration pathways are equally important, requiring timing synchronization algorithms that can leverage CSAC stability while compensating for environmental factors. Application programming interfaces (APIs) that abstract the complexity of atomic timing mechanisms will facilitate wider adoption across both IoT and defense sectors, allowing system designers to incorporate precise timing without specialized knowledge of atomic physics.

System-on-Chip (SoC) integration represents a promising pathway, where CSAC functionality can be incorporated alongside processing and communication components. This approach requires addressing thermal isolation challenges, as atomic clock performance is temperature-sensitive. Advanced packaging techniques utilizing micro-electromechanical systems (MEMS) technology can create the necessary thermal barriers while maintaining the compact form factor essential for IoT devices.

For defense applications, integration must prioritize resilience against environmental extremes and electromagnetic interference. Hardened enclosures with appropriate shielding materials can protect the sensitive atomic resonance mechanisms without significantly increasing the overall module size. Additionally, specialized interface protocols must be developed to securely integrate CSAC timing signals with military communication systems while preventing potential timing-based vulnerabilities.

Modular design approaches offer significant advantages for both sectors. By creating standardized CSAC modules with well-defined electrical and mechanical interfaces, manufacturers can accelerate integration across diverse platforms. This approach enables field-replaceable units that can be upgraded as CSAC technology evolves, extending the operational lifespan of deployed systems.

Power delivery integration presents unique challenges, particularly for battery-operated systems. Innovative power conditioning circuits that can efficiently convert available power to the precise voltage and current requirements of CSAC physics packages are essential. These circuits must accommodate the initial power spike during warm-up while transitioning to ultra-low-power steady-state operation.

Software integration pathways are equally important, requiring timing synchronization algorithms that can leverage CSAC stability while compensating for environmental factors. Application programming interfaces (APIs) that abstract the complexity of atomic timing mechanisms will facilitate wider adoption across both IoT and defense sectors, allowing system designers to incorporate precise timing without specialized knowledge of atomic physics.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!