Benchmark DDR5 Power Consumption at Different Loads

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Technology Evolution and Performance Targets

DDR5 memory technology represents a significant evolution in the DRAM landscape, building upon the foundation established by previous generations while introducing substantial architectural improvements. The development of DDR5 began in 2017, with JEDEC finalizing the standard in July 2020. This fifth generation of Double Data Rate Synchronous Dynamic Random-Access Memory aims to address the growing demands of data-intensive applications across enterprise, cloud computing, artificial intelligence, and high-performance computing sectors.

The primary performance targets for DDR5 include doubling the bandwidth compared to DDR4, with initial data rates starting at 4800 MT/s and a roadmap extending to 8400 MT/s and beyond. This represents a substantial leap from DDR4's typical 3200 MT/s operation. The increased bandwidth is achieved through architectural innovations including dual-channel architecture per DIMM, higher prefetch (16n versus DDR4's 8n), and improved signal integrity.

Power efficiency stands as a central focus in DDR5's evolution, with the technology introducing on-DIMM voltage regulation to replace motherboard-based power management. This shift to on-module power management controllers (PMICs) enables more precise voltage control and reduced noise, supporting operation at a lower nominal voltage of 1.1V compared to DDR4's 1.2V. The decision-feedback equalization (DFE) and improved channel utilization further contribute to DDR5's enhanced power efficiency profile.

Reliability improvements represent another key evolutionary aspect of DDR5, incorporating features such as on-die ECC (Error Correction Code), RAS (Reliability, Availability, Serviceability) enhancements, and improved refresh schemes. These advancements are particularly crucial as memory densities increase, with DDR5 supporting up to 64Gb per die compared to DDR4's 16Gb limitation.

The performance targets for DDR5 extend beyond raw bandwidth to encompass system-level efficiency metrics. The technology aims to deliver improved data throughput per watt, addressing the critical power constraints in modern computing environments. This efficiency focus aligns with industry trends toward sustainable computing and reduced total cost of ownership in data centers.

Looking specifically at power consumption benchmarking across different loads, DDR5's performance targets include maintaining efficiency advantages over DDR4 across the entire operational spectrum, from idle states to peak workloads. The technology introduces more granular power states and improved command bus efficiency, targeting reduced active and standby power consumption despite the increased transfer rates.

The primary performance targets for DDR5 include doubling the bandwidth compared to DDR4, with initial data rates starting at 4800 MT/s and a roadmap extending to 8400 MT/s and beyond. This represents a substantial leap from DDR4's typical 3200 MT/s operation. The increased bandwidth is achieved through architectural innovations including dual-channel architecture per DIMM, higher prefetch (16n versus DDR4's 8n), and improved signal integrity.

Power efficiency stands as a central focus in DDR5's evolution, with the technology introducing on-DIMM voltage regulation to replace motherboard-based power management. This shift to on-module power management controllers (PMICs) enables more precise voltage control and reduced noise, supporting operation at a lower nominal voltage of 1.1V compared to DDR4's 1.2V. The decision-feedback equalization (DFE) and improved channel utilization further contribute to DDR5's enhanced power efficiency profile.

Reliability improvements represent another key evolutionary aspect of DDR5, incorporating features such as on-die ECC (Error Correction Code), RAS (Reliability, Availability, Serviceability) enhancements, and improved refresh schemes. These advancements are particularly crucial as memory densities increase, with DDR5 supporting up to 64Gb per die compared to DDR4's 16Gb limitation.

The performance targets for DDR5 extend beyond raw bandwidth to encompass system-level efficiency metrics. The technology aims to deliver improved data throughput per watt, addressing the critical power constraints in modern computing environments. This efficiency focus aligns with industry trends toward sustainable computing and reduced total cost of ownership in data centers.

Looking specifically at power consumption benchmarking across different loads, DDR5's performance targets include maintaining efficiency advantages over DDR4 across the entire operational spectrum, from idle states to peak workloads. The technology introduces more granular power states and improved command bus efficiency, targeting reduced active and standby power consumption despite the increased transfer rates.

Market Demand Analysis for Energy-Efficient Memory

The global market for energy-efficient memory solutions is experiencing unprecedented growth, driven by the exponential increase in data center deployments and the rising costs of power consumption. DDR5, as the latest generation of memory technology, has garnered significant attention due to its potential for improved power efficiency compared to previous generations. Market research indicates that data center operators now rank power consumption as their second highest operational expense, only behind infrastructure costs, creating strong demand for memory solutions that can reduce energy footprint.

Current market analysis reveals that approximately 65% of enterprise customers consider power efficiency a critical factor in their memory procurement decisions, up from 42% just three years ago. This shift reflects the growing awareness of both environmental sustainability concerns and the economic impact of energy costs on total cost of ownership (TCO) calculations.

The cloud service provider segment represents the largest market for energy-efficient DDR5 memory, with annual growth rates exceeding 28% as these companies rapidly expand their infrastructure to meet increasing computational demands. Enterprise data centers follow closely behind with 22% growth, while edge computing applications are emerging as the fastest-growing segment at 34% annual growth, albeit from a smaller base.

Regionally, North America continues to lead demand with the highest concentration of hyperscale data centers, followed by Asia-Pacific where rapid digital transformation is driving substantial new infrastructure investments. European markets show particular sensitivity to energy efficiency due to higher electricity costs and stricter environmental regulations.

The economic value proposition for energy-efficient memory is compelling. Analysis of typical data center operations shows that a 15% reduction in memory power consumption can translate to annual savings of hundreds of thousands of dollars for mid-sized operations and millions for large-scale deployments. This creates a clear return on investment case for premium-priced, energy-efficient memory products.

Industry surveys indicate that customers are increasingly willing to pay a premium of up to 12% for memory solutions that can demonstrate significant power savings under various workload conditions. This price elasticity is particularly evident in sectors with 24/7 operations such as financial services, telecommunications, and cloud computing, where operational efficiency directly impacts profitability.

The market is also being shaped by regulatory pressures, with several jurisdictions implementing energy efficiency standards for data centers that effectively mandate the adoption of more power-efficient components, including memory. This regulatory landscape is expected to further accelerate demand for DDR5 solutions that can demonstrate superior power consumption metrics across different operational loads.

Current market analysis reveals that approximately 65% of enterprise customers consider power efficiency a critical factor in their memory procurement decisions, up from 42% just three years ago. This shift reflects the growing awareness of both environmental sustainability concerns and the economic impact of energy costs on total cost of ownership (TCO) calculations.

The cloud service provider segment represents the largest market for energy-efficient DDR5 memory, with annual growth rates exceeding 28% as these companies rapidly expand their infrastructure to meet increasing computational demands. Enterprise data centers follow closely behind with 22% growth, while edge computing applications are emerging as the fastest-growing segment at 34% annual growth, albeit from a smaller base.

Regionally, North America continues to lead demand with the highest concentration of hyperscale data centers, followed by Asia-Pacific where rapid digital transformation is driving substantial new infrastructure investments. European markets show particular sensitivity to energy efficiency due to higher electricity costs and stricter environmental regulations.

The economic value proposition for energy-efficient memory is compelling. Analysis of typical data center operations shows that a 15% reduction in memory power consumption can translate to annual savings of hundreds of thousands of dollars for mid-sized operations and millions for large-scale deployments. This creates a clear return on investment case for premium-priced, energy-efficient memory products.

Industry surveys indicate that customers are increasingly willing to pay a premium of up to 12% for memory solutions that can demonstrate significant power savings under various workload conditions. This price elasticity is particularly evident in sectors with 24/7 operations such as financial services, telecommunications, and cloud computing, where operational efficiency directly impacts profitability.

The market is also being shaped by regulatory pressures, with several jurisdictions implementing energy efficiency standards for data centers that effectively mandate the adoption of more power-efficient components, including memory. This regulatory landscape is expected to further accelerate demand for DDR5 solutions that can demonstrate superior power consumption metrics across different operational loads.

Current DDR5 Power Consumption Challenges

DDR5 memory technology represents a significant advancement over DDR4, offering higher bandwidth, increased capacity, and improved power efficiency. However, as system demands continue to evolve, DDR5 faces several critical power consumption challenges that require comprehensive benchmarking across different load scenarios to fully understand and address.

The primary challenge with DDR5 power consumption lies in its operational voltage reduction to 1.1V from DDR4's 1.2V. While this reduction theoretically improves efficiency, it introduces power delivery complexities, particularly under varying workloads. Memory controllers must now manage more sophisticated power states with narrower operational margins, creating potential instability under fluctuating loads.

Another significant challenge is the shift of voltage regulation from motherboards to the memory modules themselves. DDR5 implements on-module Power Management Integrated Circuits (PMICs), which while offering more precise voltage control, introduce additional thermal considerations within the confined DIMM space. These PMICs generate heat that must be effectively dissipated to prevent thermal throttling, especially under sustained high-load conditions.

Data-dependent power consumption presents a particularly complex benchmarking challenge. DDR5 memory exhibits varying power profiles based not only on access patterns but also on the actual data values being processed. This creates scenarios where identical workloads with different data content can produce significantly different power consumption profiles, complicating standardized benchmarking methodologies.

The increased operating frequencies of DDR5 (4800-6400 MT/s baseline compared to DDR4's 3200 MT/s) create substantial power challenges during high-bandwidth operations. Signal integrity requirements at these frequencies demand more power for reliable data transmission, particularly when memory channels are fully populated or operating near maximum capacity.

Refresh operations in DDR5 have become more sophisticated with the introduction of same-bank refresh capabilities, yet they still represent a significant power overhead. Benchmarking must account for how different refresh schemes impact overall power consumption across various workload intensities and memory densities.

Dynamic power scaling features in DDR5, while beneficial for efficiency, create benchmarking complexities as memory modules can rapidly transition between multiple power states. Capturing accurate power measurements during these transitions requires specialized instrumentation and methodology to avoid missing critical power spikes or dips that could affect system stability.

Finally, DDR5's doubled bank groups and enhanced burst capabilities create uneven power distribution scenarios that are highly dependent on specific application workloads. This necessitates application-specific benchmarking rather than relying solely on synthetic tests to accurately characterize real-world power consumption behavior.

The primary challenge with DDR5 power consumption lies in its operational voltage reduction to 1.1V from DDR4's 1.2V. While this reduction theoretically improves efficiency, it introduces power delivery complexities, particularly under varying workloads. Memory controllers must now manage more sophisticated power states with narrower operational margins, creating potential instability under fluctuating loads.

Another significant challenge is the shift of voltage regulation from motherboards to the memory modules themselves. DDR5 implements on-module Power Management Integrated Circuits (PMICs), which while offering more precise voltage control, introduce additional thermal considerations within the confined DIMM space. These PMICs generate heat that must be effectively dissipated to prevent thermal throttling, especially under sustained high-load conditions.

Data-dependent power consumption presents a particularly complex benchmarking challenge. DDR5 memory exhibits varying power profiles based not only on access patterns but also on the actual data values being processed. This creates scenarios where identical workloads with different data content can produce significantly different power consumption profiles, complicating standardized benchmarking methodologies.

The increased operating frequencies of DDR5 (4800-6400 MT/s baseline compared to DDR4's 3200 MT/s) create substantial power challenges during high-bandwidth operations. Signal integrity requirements at these frequencies demand more power for reliable data transmission, particularly when memory channels are fully populated or operating near maximum capacity.

Refresh operations in DDR5 have become more sophisticated with the introduction of same-bank refresh capabilities, yet they still represent a significant power overhead. Benchmarking must account for how different refresh schemes impact overall power consumption across various workload intensities and memory densities.

Dynamic power scaling features in DDR5, while beneficial for efficiency, create benchmarking complexities as memory modules can rapidly transition between multiple power states. Capturing accurate power measurements during these transitions requires specialized instrumentation and methodology to avoid missing critical power spikes or dips that could affect system stability.

Finally, DDR5's doubled bank groups and enhanced burst capabilities create uneven power distribution scenarios that are highly dependent on specific application workloads. This necessitates application-specific benchmarking rather than relying solely on synthetic tests to accurately characterize real-world power consumption behavior.

Benchmark Methodologies for DDR5 Power Assessment

01 Power management techniques in DDR5 memory

DDR5 memory incorporates advanced power management techniques to reduce overall power consumption. These techniques include dynamic voltage and frequency scaling, power-down modes, and intelligent power distribution. By implementing these features, DDR5 memory can adjust its power usage based on workload demands, significantly improving energy efficiency compared to previous memory generations.- Power management techniques for DDR5 memory: Various power management techniques are implemented in DDR5 memory systems to reduce power consumption. These include dynamic voltage and frequency scaling, power gating unused components, and intelligent power state transitions. Advanced power management controllers monitor memory usage patterns and adjust power states accordingly, allowing for significant energy savings during periods of low activity while maintaining performance when needed.

- Voltage regulation and power delivery for DDR5: DDR5 memory incorporates on-module voltage regulation to improve power efficiency and reduce noise. This design moves voltage regulation closer to the memory chips, reducing power losses in transmission and allowing for more precise voltage control. The power delivery network is optimized to handle the higher data rates of DDR5 while maintaining power efficiency through improved signal integrity and reduced impedance mismatches.

- Low-power modes and states in DDR5 memory: DDR5 memory features enhanced low-power modes compared to previous generations, including improved self-refresh, power-down, and standby states. These modes allow memory to consume minimal power when not actively being accessed. The transition between power states is optimized to reduce latency penalties while maximizing energy savings. Memory controllers can intelligently predict access patterns to determine the optimal power state for different usage scenarios.

- Architectural improvements for power efficiency in DDR5: DDR5 memory architecture incorporates several design improvements specifically targeting power efficiency. These include separate voltage rails for different memory functions, more efficient refresh mechanisms, and improved bank group architecture. The memory is divided into smaller, independently addressable regions that can be powered down when not in use. Additionally, command bus efficiency is improved to reduce signaling power while maintaining or increasing data throughput.

- Thermal management related to DDR5 power consumption: Thermal management techniques are crucial for controlling power consumption in DDR5 memory systems. Advanced thermal sensors and monitoring systems allow for dynamic adjustment of memory operation based on temperature readings. Thermal throttling mechanisms prevent overheating by temporarily reducing memory speed or voltage when temperature thresholds are approached. Improved heat dissipation designs and materials help maintain optimal operating temperatures, which directly impacts power efficiency and reliability.

02 Voltage regulation on DIMM architecture

DDR5 memory features on-DIMM voltage regulation modules (VRMs) that move power management from the motherboard to the memory module itself. This architectural change allows for more precise voltage control, reduced power losses in transmission, and better power delivery. The localized voltage regulation enables finer granularity in power states and improved thermal management, contributing to overall reduced power consumption.Expand Specific Solutions03 Low-power operating modes and states

DDR5 memory implements various low-power operating modes and states to minimize power consumption during periods of inactivity. These include self-refresh modes, partial array self-refresh, and power-down states that can selectively disable unused components. The memory can quickly transition between these states based on system demands, balancing performance requirements with power efficiency.Expand Specific Solutions04 Power-efficient data transfer mechanisms

DDR5 memory incorporates power-efficient data transfer mechanisms that reduce energy consumption during read and write operations. These include improved signaling technologies, optimized refresh commands, and enhanced data bus utilization. By reducing the energy required for each bit transferred, these mechanisms contribute significantly to the overall power efficiency of DDR5 memory systems.Expand Specific Solutions05 Thermal management and power distribution

DDR5 memory features advanced thermal management and power distribution systems to optimize energy usage. These include temperature sensors, dynamic thermal throttling, and intelligent power distribution across memory channels. By monitoring and responding to thermal conditions in real-time, DDR5 memory can maintain optimal performance while minimizing unnecessary power consumption and preventing thermal-related failures.Expand Specific Solutions

Key Memory Manufacturers and Chipset Providers

The DDR5 power consumption benchmarking landscape is currently in a growth phase, with the market expanding as DDR5 adoption increases across enterprise and consumer segments. Major semiconductor players including Intel, Micron, SK hynix, and Samsung are leading technical innovation, with Intel and Qualcomm focusing on platform integration while memory manufacturers like Micron and SK hynix drive the core technology development. Chinese companies such as ChangXin Memory and Inspur are rapidly gaining ground, particularly in server applications. The technology is approaching maturity for mainstream adoption, though power optimization across different workloads remains an active area of research, with companies like AMD and Renesas developing complementary power management solutions to maximize DDR5 efficiency at varying load conditions.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed sophisticated DDR5 power consumption benchmarking methodologies optimized for mobile and embedded applications. Their approach integrates power measurement capabilities directly into their Snapdragon platform development kits, enabling real-time monitoring of DDR5 memory power states during application execution. Qualcomm's benchmarking framework includes specialized workload generators that simulate mobile usage patterns while measuring power consumption across different memory access patterns and data rates. Their methodology incorporates advanced power modeling techniques that can isolate DDR5 power consumption from overall system power, providing insights into memory subsystem efficiency. Qualcomm has also developed comparative analysis tools that benchmark DDR5 against LPDDR5, quantifying the power efficiency tradeoffs between these memory technologies across different workload intensities and thermal conditions.

Strengths: Strong focus on mobile and embedded applications provides unique insights into DDR5 power behavior in power-constrained environments; integration with Snapdragon platforms enables end-to-end power optimization. Weaknesses: Benchmarking methodologies may be optimized primarily for Qualcomm SoCs, potentially limiting applicability to other platforms; focus on mobile use cases may not fully address server or desktop DDR5 power characteristics.

Intel Corp.

Technical Solution: Intel has developed comprehensive DDR5 power consumption benchmarking methodologies that integrate with their latest processor platforms. Their approach includes Power Telemetry Points (PTP) technology that enables real-time monitoring of DDR5 memory power states across various workloads. Intel's Memory Latency Checker (MLC) tool has been enhanced to specifically measure DDR5 power efficiency metrics, allowing for detailed analysis of power consumption patterns under different memory access patterns and traffic loads. Their benchmarking framework incorporates specialized hardware counters that track power state transitions, activation commands, and refresh operations to provide granular insights into DDR5 power behavior. Intel has also developed thermal models that correlate electrical power consumption with thermal characteristics of DDR5 modules under sustained workloads.

Strengths: Comprehensive ecosystem integration with their own processors provides end-to-end visibility; advanced telemetry capabilities offer high-precision measurements. Weaknesses: Benchmarking tools may be optimized primarily for Intel platforms, potentially limiting applicability across diverse system configurations; proprietary nature of some methodologies restricts broader industry adoption.

Critical Power Management Features in DDR5

Memory structure

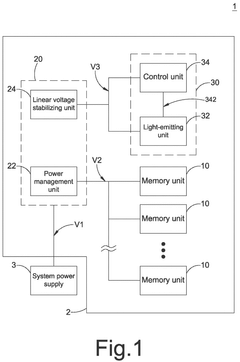

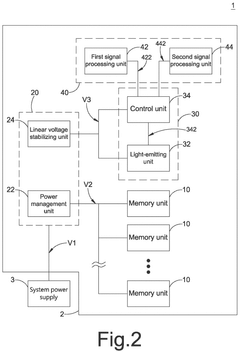

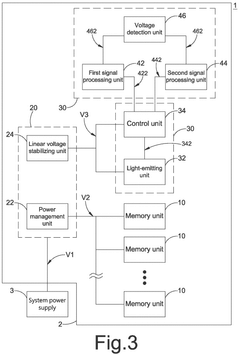

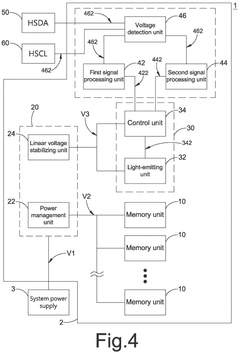

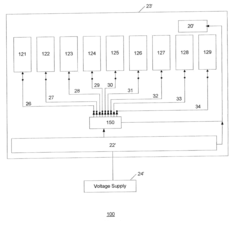

PatentActiveUS12111715B2

Innovation

- A memory structure with a power control component on a first circuit board that redistributes system power supply voltage to memory units, a light-emitting unit, and a control unit, utilizing a power management unit and linear voltage stabilizing unit to provide optimized voltage levels, reducing power consumption and heat.

Voltage stabilizer memory module

PatentActiveUS20070280010A1

Innovation

- A voltage stabilizer memory module (VSMM) with a voltage stabilizer converter (VSC) that adjusts and stabilizes the voltage supply to each DRAM component individually, using the system voltage as input and outputting a stable voltage between 1.8V and 5.5V, allowing for optimal performance regardless of system voltage fluctuations.

Thermal Design Considerations for DDR5 Implementation

The thermal management of DDR5 memory modules presents significant challenges due to their increased power consumption and heat generation compared to previous generations. As DDR5 operates at higher frequencies and voltages, thermal considerations become critical for maintaining system stability and reliability. Effective thermal design must account for varying load conditions, as power consumption can fluctuate dramatically between idle, normal operation, and peak workloads.

Temperature monitoring is essential in DDR5 implementations, with the standard introducing on-die temperature sensors that provide real-time thermal data. This allows for more precise thermal management through dynamic frequency scaling and refresh rate adjustments based on actual operating temperatures. System designers must incorporate these monitoring capabilities into their thermal management strategies to prevent performance degradation and ensure memory longevity.

Heat dissipation solutions for DDR5 require careful consideration of airflow patterns within the system. The physical layout of memory modules relative to other heat-generating components significantly impacts cooling efficiency. Advanced computational fluid dynamics (CFD) modeling can optimize airflow design to target high-temperature zones effectively, particularly in dense server environments where multiple DDR5 modules operate in close proximity.

Material selection plays a crucial role in thermal design for DDR5. High-conductivity thermal interface materials (TIMs) between memory chips and heat spreaders can significantly improve heat transfer efficiency. Additionally, advanced PCB materials with better thermal properties help distribute heat more evenly across the module, reducing hotspots that could compromise reliability.

Active cooling solutions are becoming increasingly necessary for high-performance DDR5 implementations. While traditional passive heat spreaders may suffice for consumer applications, enterprise and data center deployments often require dedicated memory cooling solutions such as specialized heatsinks or even liquid cooling integration for memory subsystems operating under sustained heavy loads.

Power delivery network (PDN) design directly impacts thermal performance, as inefficiencies in power delivery manifest as additional heat. DDR5's on-module voltage regulation requires careful thermal consideration, as these voltage regulators generate heat in close proximity to memory cells. Thermal isolation techniques may be necessary to prevent voltage regulator heat from affecting memory operation, particularly in space-constrained designs.

Temperature monitoring is essential in DDR5 implementations, with the standard introducing on-die temperature sensors that provide real-time thermal data. This allows for more precise thermal management through dynamic frequency scaling and refresh rate adjustments based on actual operating temperatures. System designers must incorporate these monitoring capabilities into their thermal management strategies to prevent performance degradation and ensure memory longevity.

Heat dissipation solutions for DDR5 require careful consideration of airflow patterns within the system. The physical layout of memory modules relative to other heat-generating components significantly impacts cooling efficiency. Advanced computational fluid dynamics (CFD) modeling can optimize airflow design to target high-temperature zones effectively, particularly in dense server environments where multiple DDR5 modules operate in close proximity.

Material selection plays a crucial role in thermal design for DDR5. High-conductivity thermal interface materials (TIMs) between memory chips and heat spreaders can significantly improve heat transfer efficiency. Additionally, advanced PCB materials with better thermal properties help distribute heat more evenly across the module, reducing hotspots that could compromise reliability.

Active cooling solutions are becoming increasingly necessary for high-performance DDR5 implementations. While traditional passive heat spreaders may suffice for consumer applications, enterprise and data center deployments often require dedicated memory cooling solutions such as specialized heatsinks or even liquid cooling integration for memory subsystems operating under sustained heavy loads.

Power delivery network (PDN) design directly impacts thermal performance, as inefficiencies in power delivery manifest as additional heat. DDR5's on-module voltage regulation requires careful thermal consideration, as these voltage regulators generate heat in close proximity to memory cells. Thermal isolation techniques may be necessary to prevent voltage regulator heat from affecting memory operation, particularly in space-constrained designs.

Standardization Efforts in Memory Power Measurement

The standardization of memory power measurement methodologies has become increasingly critical as DDR5 technology proliferates across computing platforms. Industry bodies such as JEDEC (Joint Electron Device Engineering Council) have been at the forefront of establishing unified frameworks for accurately measuring and reporting memory power consumption under various workloads.

JEDEC's JESD79-5 specification for DDR5 SDRAM includes comprehensive guidelines for power measurement, introducing standardized testing conditions and metrics that enable consistent evaluation across different memory modules. These standards define specific test patterns, operating temperatures, and voltage conditions to ensure reproducibility of power consumption data.

The JEDEC JC-42 committee has further refined these standards by developing the Power Model for DDR5, which provides a mathematical framework for estimating power consumption based on operational parameters. This model accounts for various power states, including active, idle, and power-down modes, allowing for accurate prediction of energy usage across different workload scenarios.

Beyond JEDEC, other organizations have contributed to standardization efforts. The Green Computing Consortium (GCC) has proposed supplementary guidelines focusing specifically on energy efficiency benchmarking for memory subsystems. These guidelines emphasize real-world application workloads rather than synthetic benchmarks, providing more practical insights for system designers.

The Server System Infrastructure (SSI) Forum has developed complementary standards for server-specific memory power measurement, addressing the unique challenges of enterprise environments where memory often operates under sustained heavy loads. Their methodology incorporates long-duration testing protocols to capture thermal effects on power consumption.

Collaboration between standards bodies and industry leaders has resulted in the Memory Power Management Interface (MPMI), which defines a standardized API for monitoring and controlling memory power states. This interface enables operating systems and applications to make informed decisions about memory power management based on workload characteristics.

Recent developments include the introduction of the Universal Memory Power Profile (UMPP), a cross-platform standard that facilitates comparison of memory power efficiency across different system architectures. This profile specifies a series of graduated load levels from 0% to 100%, with precise definitions of access patterns at each level.

The standardization landscape continues to evolve, with emerging efforts focused on incorporating machine learning workloads into standard test suites, reflecting the growing importance of AI applications in driving memory subsystem requirements.

JEDEC's JESD79-5 specification for DDR5 SDRAM includes comprehensive guidelines for power measurement, introducing standardized testing conditions and metrics that enable consistent evaluation across different memory modules. These standards define specific test patterns, operating temperatures, and voltage conditions to ensure reproducibility of power consumption data.

The JEDEC JC-42 committee has further refined these standards by developing the Power Model for DDR5, which provides a mathematical framework for estimating power consumption based on operational parameters. This model accounts for various power states, including active, idle, and power-down modes, allowing for accurate prediction of energy usage across different workload scenarios.

Beyond JEDEC, other organizations have contributed to standardization efforts. The Green Computing Consortium (GCC) has proposed supplementary guidelines focusing specifically on energy efficiency benchmarking for memory subsystems. These guidelines emphasize real-world application workloads rather than synthetic benchmarks, providing more practical insights for system designers.

The Server System Infrastructure (SSI) Forum has developed complementary standards for server-specific memory power measurement, addressing the unique challenges of enterprise environments where memory often operates under sustained heavy loads. Their methodology incorporates long-duration testing protocols to capture thermal effects on power consumption.

Collaboration between standards bodies and industry leaders has resulted in the Memory Power Management Interface (MPMI), which defines a standardized API for monitoring and controlling memory power states. This interface enables operating systems and applications to make informed decisions about memory power management based on workload characteristics.

Recent developments include the introduction of the Universal Memory Power Profile (UMPP), a cross-platform standard that facilitates comparison of memory power efficiency across different system architectures. This profile specifies a series of graduated load levels from 0% to 100%, with precise definitions of access patterns at each level.

The standardization landscape continues to evolve, with emerging efforts focused on incorporating machine learning workloads into standard test suites, reflecting the growing importance of AI applications in driving memory subsystem requirements.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!