Chiplet Applications in High-Performance Computing Systems

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Tech Evolution

The evolution of chiplet technology in high-performance computing systems has been marked by significant milestones and innovations. Initially, the focus was on monolithic chip designs, where all components were integrated onto a single die. However, as Moore's Law began to slow down and the challenges of scaling traditional monolithic designs became more apparent, the industry started exploring alternative approaches.

The concept of chiplets emerged as a promising solution to overcome the limitations of monolithic designs. This approach involves breaking down complex systems into smaller, more manageable components that can be manufactured separately and then integrated onto a single package. The early stages of chiplet technology focused on developing effective methods for interconnecting these separate dies.

As the technology progressed, advancements in packaging techniques played a crucial role. The introduction of 2.5D and 3D packaging technologies allowed for more efficient integration of chiplets, enabling higher bandwidth and lower latency communication between components. This marked a significant step forward in the evolution of chiplet-based high-performance computing systems.

The development of standardized interfaces for chiplet communication has been another key milestone. Initiatives like the Advanced Interface Bus (AIB) and Universal Chiplet Interconnect Express (UCIe) have aimed to create industry-wide standards, facilitating interoperability and reducing design complexities.

Recent years have seen a focus on improving the efficiency and performance of chiplet-based systems. This has involved advancements in areas such as thermal management, power delivery, and signal integrity. The integration of heterogeneous chiplets, combining different process nodes or even different types of semiconductors, has opened up new possibilities for system optimization.

Looking towards the future, the evolution of chiplet technology is likely to continue in several directions. One area of focus is the development of even more advanced packaging technologies, potentially including optical interconnects for ultra-high-bandwidth communication between chiplets. Another trend is the increasing use of artificial intelligence and machine learning techniques to optimize chiplet designs and system-level integration.

The ongoing evolution of chiplet technology is also closely tied to advancements in manufacturing processes. As the industry pushes towards more advanced nodes, chiplets offer a way to balance the benefits of cutting-edge fabrication with cost-effective integration of less critical components. This approach is expected to play a crucial role in sustaining performance improvements in high-performance computing systems beyond the limits of traditional Moore's Law scaling.

The concept of chiplets emerged as a promising solution to overcome the limitations of monolithic designs. This approach involves breaking down complex systems into smaller, more manageable components that can be manufactured separately and then integrated onto a single package. The early stages of chiplet technology focused on developing effective methods for interconnecting these separate dies.

As the technology progressed, advancements in packaging techniques played a crucial role. The introduction of 2.5D and 3D packaging technologies allowed for more efficient integration of chiplets, enabling higher bandwidth and lower latency communication between components. This marked a significant step forward in the evolution of chiplet-based high-performance computing systems.

The development of standardized interfaces for chiplet communication has been another key milestone. Initiatives like the Advanced Interface Bus (AIB) and Universal Chiplet Interconnect Express (UCIe) have aimed to create industry-wide standards, facilitating interoperability and reducing design complexities.

Recent years have seen a focus on improving the efficiency and performance of chiplet-based systems. This has involved advancements in areas such as thermal management, power delivery, and signal integrity. The integration of heterogeneous chiplets, combining different process nodes or even different types of semiconductors, has opened up new possibilities for system optimization.

Looking towards the future, the evolution of chiplet technology is likely to continue in several directions. One area of focus is the development of even more advanced packaging technologies, potentially including optical interconnects for ultra-high-bandwidth communication between chiplets. Another trend is the increasing use of artificial intelligence and machine learning techniques to optimize chiplet designs and system-level integration.

The ongoing evolution of chiplet technology is also closely tied to advancements in manufacturing processes. As the industry pushes towards more advanced nodes, chiplets offer a way to balance the benefits of cutting-edge fabrication with cost-effective integration of less critical components. This approach is expected to play a crucial role in sustaining performance improvements in high-performance computing systems beyond the limits of traditional Moore's Law scaling.

HPC Market Demand

The High-Performance Computing (HPC) market has been experiencing significant growth and transformation, driven by the increasing demand for advanced computational capabilities across various industries. As organizations seek to tackle complex problems and process massive datasets, the need for more powerful and efficient HPC systems has become paramount. This demand is particularly evident in sectors such as scientific research, financial modeling, weather forecasting, and artificial intelligence.

The global HPC market size was valued at approximately $39 billion in 2020 and is projected to reach $49 billion by 2025, growing at a CAGR of 5.5% during the forecast period. This growth is fueled by the rising adoption of cloud-based HPC solutions, the proliferation of big data analytics, and the increasing focus on AI and machine learning applications.

One of the key drivers of HPC market demand is the need for faster and more efficient data processing. As the volume of data generated by businesses and research institutions continues to explode, traditional computing systems are struggling to keep up. HPC systems, with their ability to perform complex calculations and simulations at high speeds, are becoming essential tools for organizations looking to gain insights from their data and maintain a competitive edge.

The scientific research sector remains a major consumer of HPC resources, with applications ranging from genomics and drug discovery to climate modeling and particle physics. The financial services industry is another significant market for HPC, utilizing these systems for risk analysis, algorithmic trading, and fraud detection. Additionally, government agencies and defense organizations are investing heavily in HPC capabilities for national security and intelligence applications.

The emergence of exascale computing is expected to further drive demand in the HPC market. Exascale systems, capable of performing a quintillion calculations per second, promise to revolutionize fields such as materials science, renewable energy research, and personalized medicine. As countries and organizations race to develop and deploy exascale systems, the demand for advanced HPC technologies, including chiplet-based solutions, is likely to surge.

The COVID-19 pandemic has also highlighted the critical role of HPC in addressing global challenges. From modeling virus spread to accelerating vaccine development, HPC systems have been instrumental in the fight against the pandemic. This has led to increased recognition of the importance of HPC investments among policymakers and business leaders, potentially driving further market growth in the coming years.

As the HPC market continues to evolve, there is a growing emphasis on energy efficiency and sustainability. Organizations are seeking HPC solutions that can deliver high performance while minimizing power consumption and environmental impact. This trend is likely to drive innovation in chiplet-based architectures, which offer the potential for more modular and energy-efficient HPC systems.

The global HPC market size was valued at approximately $39 billion in 2020 and is projected to reach $49 billion by 2025, growing at a CAGR of 5.5% during the forecast period. This growth is fueled by the rising adoption of cloud-based HPC solutions, the proliferation of big data analytics, and the increasing focus on AI and machine learning applications.

One of the key drivers of HPC market demand is the need for faster and more efficient data processing. As the volume of data generated by businesses and research institutions continues to explode, traditional computing systems are struggling to keep up. HPC systems, with their ability to perform complex calculations and simulations at high speeds, are becoming essential tools for organizations looking to gain insights from their data and maintain a competitive edge.

The scientific research sector remains a major consumer of HPC resources, with applications ranging from genomics and drug discovery to climate modeling and particle physics. The financial services industry is another significant market for HPC, utilizing these systems for risk analysis, algorithmic trading, and fraud detection. Additionally, government agencies and defense organizations are investing heavily in HPC capabilities for national security and intelligence applications.

The emergence of exascale computing is expected to further drive demand in the HPC market. Exascale systems, capable of performing a quintillion calculations per second, promise to revolutionize fields such as materials science, renewable energy research, and personalized medicine. As countries and organizations race to develop and deploy exascale systems, the demand for advanced HPC technologies, including chiplet-based solutions, is likely to surge.

The COVID-19 pandemic has also highlighted the critical role of HPC in addressing global challenges. From modeling virus spread to accelerating vaccine development, HPC systems have been instrumental in the fight against the pandemic. This has led to increased recognition of the importance of HPC investments among policymakers and business leaders, potentially driving further market growth in the coming years.

As the HPC market continues to evolve, there is a growing emphasis on energy efficiency and sustainability. Organizations are seeking HPC solutions that can deliver high performance while minimizing power consumption and environmental impact. This trend is likely to drive innovation in chiplet-based architectures, which offer the potential for more modular and energy-efficient HPC systems.

Chiplet Challenges

While chiplets offer significant advantages in high-performance computing systems, they also present several challenges that need to be addressed for their successful implementation and widespread adoption.

One of the primary challenges is the integration of multiple chiplets into a single package. This process requires advanced packaging technologies and precise alignment techniques to ensure proper interconnection between the different chiplets. The complexity of this integration increases with the number of chiplets involved, leading to potential yield and reliability issues.

Thermal management is another critical challenge in chiplet-based systems. As multiple chiplets are packed closely together, heat dissipation becomes more difficult. Efficient cooling solutions must be developed to prevent thermal throttling and maintain optimal performance. This challenge is particularly acute in high-performance computing applications where power consumption and heat generation are already significant concerns.

Inter-chiplet communication presents a significant technical hurdle. Ensuring high-bandwidth, low-latency communication between chiplets is crucial for system performance. This requires advanced interconnect technologies and sophisticated communication protocols. The design of efficient inter-chiplet interfaces that can handle the required data rates while minimizing power consumption and signal integrity issues is a complex task.

Power distribution and management across multiple chiplets pose another challenge. Ensuring uniform and stable power delivery to each chiplet, especially in high-performance scenarios, requires careful design of power delivery networks. Additionally, managing power consumption across multiple chiplets to optimize overall system efficiency is a complex task that requires advanced power management techniques.

Testing and validation of chiplet-based systems present unique challenges. Traditional testing methods may not be sufficient for complex multi-chiplet designs. New testing strategies and methodologies need to be developed to ensure the reliability and functionality of the integrated system. This includes testing individual chiplets before integration as well as comprehensive system-level testing after assembly.

The design and optimization of chiplet-based systems also face challenges in terms of software and architecture. Developing software that can effectively utilize the distributed nature of chiplet-based systems and optimize workload distribution across multiple chiplets is a complex task. This requires advancements in compiler technologies, operating systems, and application software to fully leverage the potential of chiplet architectures.

Standardization is another significant challenge in the chiplet ecosystem. The lack of industry-wide standards for chiplet interfaces, protocols, and packaging can hinder interoperability and limit the potential for mix-and-match chiplet designs from different vendors. Establishing common standards is crucial for fostering innovation and enabling a more diverse and competitive chiplet marketplace.

One of the primary challenges is the integration of multiple chiplets into a single package. This process requires advanced packaging technologies and precise alignment techniques to ensure proper interconnection between the different chiplets. The complexity of this integration increases with the number of chiplets involved, leading to potential yield and reliability issues.

Thermal management is another critical challenge in chiplet-based systems. As multiple chiplets are packed closely together, heat dissipation becomes more difficult. Efficient cooling solutions must be developed to prevent thermal throttling and maintain optimal performance. This challenge is particularly acute in high-performance computing applications where power consumption and heat generation are already significant concerns.

Inter-chiplet communication presents a significant technical hurdle. Ensuring high-bandwidth, low-latency communication between chiplets is crucial for system performance. This requires advanced interconnect technologies and sophisticated communication protocols. The design of efficient inter-chiplet interfaces that can handle the required data rates while minimizing power consumption and signal integrity issues is a complex task.

Power distribution and management across multiple chiplets pose another challenge. Ensuring uniform and stable power delivery to each chiplet, especially in high-performance scenarios, requires careful design of power delivery networks. Additionally, managing power consumption across multiple chiplets to optimize overall system efficiency is a complex task that requires advanced power management techniques.

Testing and validation of chiplet-based systems present unique challenges. Traditional testing methods may not be sufficient for complex multi-chiplet designs. New testing strategies and methodologies need to be developed to ensure the reliability and functionality of the integrated system. This includes testing individual chiplets before integration as well as comprehensive system-level testing after assembly.

The design and optimization of chiplet-based systems also face challenges in terms of software and architecture. Developing software that can effectively utilize the distributed nature of chiplet-based systems and optimize workload distribution across multiple chiplets is a complex task. This requires advancements in compiler technologies, operating systems, and application software to fully leverage the potential of chiplet architectures.

Standardization is another significant challenge in the chiplet ecosystem. The lack of industry-wide standards for chiplet interfaces, protocols, and packaging can hinder interoperability and limit the potential for mix-and-match chiplet designs from different vendors. Establishing common standards is crucial for fostering innovation and enabling a more diverse and competitive chiplet marketplace.

Current Chiplet Designs

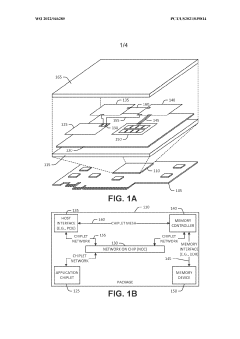

01 Chiplet integration and packaging

Chiplets are integrated circuit dies that can be combined to form larger, more complex systems. This approach allows for modular design and improved manufacturing yields. Advanced packaging techniques are used to interconnect multiple chiplets, enabling high-performance and cost-effective semiconductor solutions.- Chiplet integration and packaging: Chiplets are integrated circuit dies that can be combined to form larger, more complex systems. This approach allows for modular design and improved manufacturing yields. Advanced packaging techniques are used to interconnect multiple chiplets, enabling high-performance and cost-effective solutions for various applications.

- Interconnect technologies for chiplets: Various interconnect technologies are employed to facilitate communication between chiplets. These may include advanced interposers, silicon bridges, or through-silicon vias (TSVs). The choice of interconnect technology impacts system performance, power efficiency, and overall integration density.

- Thermal management in chiplet designs: Effective thermal management is crucial in chiplet-based systems due to the high power density and potential hotspots. Innovative cooling solutions and thermal interface materials are developed to ensure optimal performance and reliability of multi-chiplet packages.

- Power distribution and management for chiplets: Efficient power distribution and management are essential for chiplet-based systems. This includes developing advanced power delivery networks, voltage regulation techniques, and power gating strategies to optimize energy consumption across multiple chiplets.

- Testing and yield improvement for chiplet manufacturing: Specialized testing methodologies and yield improvement techniques are developed for chiplet manufacturing. These include pre-bond and post-bond testing strategies, as well as advanced defect detection and isolation methods to ensure high-quality chiplet integration.

02 Interconnect technologies for chiplets

Various interconnect technologies are employed to facilitate communication between chiplets. These may include advanced interposers, silicon bridges, or through-silicon vias (TSVs). The choice of interconnect technology impacts the overall performance, power efficiency, and cost of the chiplet-based system.Expand Specific Solutions03 Thermal management in chiplet designs

Effective thermal management is crucial in chiplet-based systems due to the high power density and potential heat concentration. Innovative cooling solutions and thermal interface materials are developed to ensure optimal performance and reliability of chiplet assemblies.Expand Specific Solutions04 Chiplet-based memory solutions

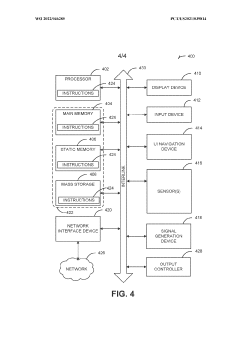

Memory chiplets are used to create high-capacity, high-bandwidth memory subsystems. These can be stacked or placed alongside processing chiplets to optimize data transfer rates and reduce latency in complex computing systems.Expand Specific Solutions05 Design and verification tools for chiplet systems

Specialized electronic design automation (EDA) tools are developed to address the unique challenges of chiplet-based system design. These tools assist in optimizing chiplet placement, routing, and system-level verification to ensure seamless integration and functionality of multi-chiplet designs.Expand Specific Solutions

Key HPC Players

The chiplet applications in high-performance computing systems market is in a growth phase, driven by increasing demand for more powerful and efficient computing solutions. The market size is expanding rapidly, with major players like Intel, AMD, and Micron Technology leading the way. Technological maturity varies, with established companies having advanced capabilities, while newer entrants like Primemas and Moore Thread are innovating in specific areas. The competitive landscape is dynamic, with traditional semiconductor giants facing challenges from specialized chiplet startups and research institutions like Zhejiang Lab and Peng Cheng Laboratory, which are pushing the boundaries of chiplet technology.

Intel Corp.

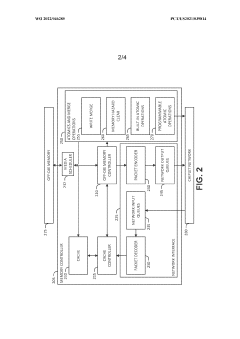

Technical Solution: Intel's Foveros 3D packaging technology is a key enabler for chiplet-based high-performance computing systems. This advanced packaging solution allows for the vertical stacking of multiple chiplets, enabling higher performance and lower power consumption[1]. Intel's Ponte Vecchio GPU, designed for HPC and AI workloads, utilizes over 40 chiplets fabricated on different process nodes, demonstrating the scalability and flexibility of their chiplet approach[2]. The company has also introduced the Intel On Chip System Fabric (IOSF) to facilitate efficient communication between chiplets, reducing latency and improving overall system performance[3].

Strengths: Advanced 3D packaging technology, scalable architecture, and efficient inter-chiplet communication. Weaknesses: Complexity in design and manufacturing, potential thermal management challenges in densely packed 3D structures.

Advanced Micro Devices, Inc.

Technical Solution: AMD's chiplet strategy for HPC systems centers around their Infinity Fabric interconnect technology. This approach allows AMD to combine multiple smaller dies (chiplets) to create high-performance processors like the EPYC server CPUs and Threadripper HEDT processors[4]. The company's 3rd generation EPYC processors, codenamed "Milan," utilize up to eight 7nm CPU chiplets connected to a central I/O die, enabling scalable performance for HPC applications[5]. AMD has also extended this chiplet approach to their GPUs, with the MI200 series accelerators using multiple compute dies interconnected with high-bandwidth passive crosslinks[6].

Strengths: Highly scalable architecture, cost-effective manufacturing by using smaller dies, and flexibility in product configurations. Weaknesses: Potential latency issues between chiplets, complexity in managing thermal output across multiple dies.

Chiplet Innovations

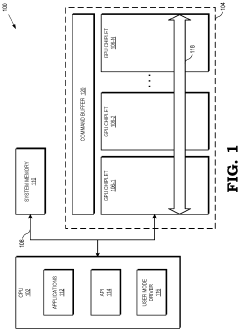

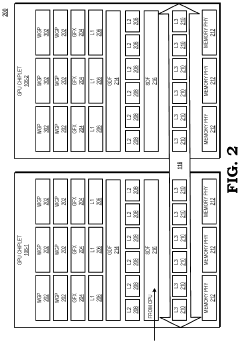

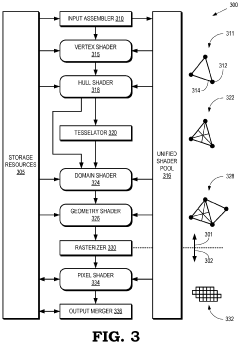

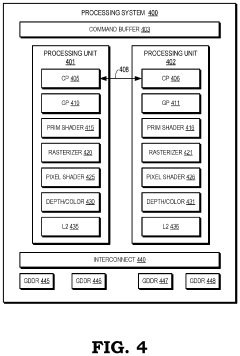

Data flow in a distributed graphics processing unit architecture

PatentActiveUS20210158599A1

Innovation

- A distributed architecture using chiplets with high-performance interconnection, where geometry and pixel workloads are processed by multiple processing units with duplicated fixed function hardware blocks and shaders, and a shared coherent cache, allowing for checkerboarding of pixel processing across units to manage synchronization and bandwidth effectively.

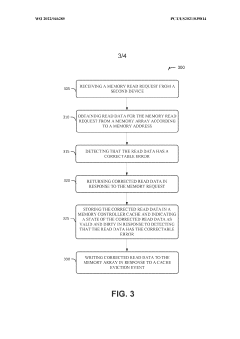

Method of demand scrubbing by placing corrected data in memory-side cache

PatentWO2022046285A1

Innovation

- Implementing a memory controller chiplet with cache management and error correction capabilities that allow for demand scrubbing by storing corrected data in the memory controller cache and writing it back to the storage array during cache eviction events, thereby minimizing the need for additional read-modify-write paths and simplifying data correction.

Thermal Management

Thermal management is a critical aspect of Chiplet applications in high-performance computing systems. As the demand for increased computational power continues to grow, the heat generated by these systems becomes a significant challenge. Chiplet-based designs, while offering advantages in terms of modularity and performance, also introduce unique thermal considerations.

The primary concern in thermal management for Chiplet-based systems is the increased power density. With multiple chiplets packed closely together, heat dissipation becomes more complex compared to traditional monolithic designs. This concentration of heat sources can lead to hotspots, which may cause performance degradation or even system failure if not properly addressed.

To combat these thermal challenges, several strategies have been developed. One approach is the use of advanced cooling solutions, such as liquid cooling or phase-change cooling systems. These methods can more effectively remove heat from the chiplets compared to traditional air cooling. Additionally, the integration of thermal interface materials (TIMs) between chiplets and heat spreaders has shown promise in improving heat transfer efficiency.

Another important aspect of thermal management in Chiplet-based systems is the implementation of intelligent power management techniques. Dynamic voltage and frequency scaling (DVFS) can be applied at the chiplet level, allowing for fine-grained control over power consumption and heat generation. This approach enables the system to optimize performance while maintaining safe operating temperatures.

The physical design and layout of chiplets also play a crucial role in thermal management. Careful consideration must be given to the placement of high-power chiplets relative to lower-power ones, as well as the overall system architecture. This includes the strategic positioning of thermal sensors and the implementation of thermal-aware routing algorithms for inter-chiplet communication.

Emerging technologies, such as 3D stacking and through-silicon vias (TSVs), offer new possibilities for thermal management in Chiplet-based systems. These technologies allow for more efficient heat dissipation pathways and can potentially reduce the overall thermal resistance of the system. However, they also introduce new challenges, such as managing heat flow in vertical stacks of chiplets.

As Chiplet technology continues to evolve, research into novel thermal management solutions remains a priority. This includes the development of advanced materials with superior thermal properties, as well as the exploration of new cooling technologies such as on-chip microfluidic cooling channels. The integration of artificial intelligence and machine learning algorithms for predictive thermal management is also an area of active research, promising more efficient and adaptive cooling strategies for future high-performance computing systems.

The primary concern in thermal management for Chiplet-based systems is the increased power density. With multiple chiplets packed closely together, heat dissipation becomes more complex compared to traditional monolithic designs. This concentration of heat sources can lead to hotspots, which may cause performance degradation or even system failure if not properly addressed.

To combat these thermal challenges, several strategies have been developed. One approach is the use of advanced cooling solutions, such as liquid cooling or phase-change cooling systems. These methods can more effectively remove heat from the chiplets compared to traditional air cooling. Additionally, the integration of thermal interface materials (TIMs) between chiplets and heat spreaders has shown promise in improving heat transfer efficiency.

Another important aspect of thermal management in Chiplet-based systems is the implementation of intelligent power management techniques. Dynamic voltage and frequency scaling (DVFS) can be applied at the chiplet level, allowing for fine-grained control over power consumption and heat generation. This approach enables the system to optimize performance while maintaining safe operating temperatures.

The physical design and layout of chiplets also play a crucial role in thermal management. Careful consideration must be given to the placement of high-power chiplets relative to lower-power ones, as well as the overall system architecture. This includes the strategic positioning of thermal sensors and the implementation of thermal-aware routing algorithms for inter-chiplet communication.

Emerging technologies, such as 3D stacking and through-silicon vias (TSVs), offer new possibilities for thermal management in Chiplet-based systems. These technologies allow for more efficient heat dissipation pathways and can potentially reduce the overall thermal resistance of the system. However, they also introduce new challenges, such as managing heat flow in vertical stacks of chiplets.

As Chiplet technology continues to evolve, research into novel thermal management solutions remains a priority. This includes the development of advanced materials with superior thermal properties, as well as the exploration of new cooling technologies such as on-chip microfluidic cooling channels. The integration of artificial intelligence and machine learning algorithms for predictive thermal management is also an area of active research, promising more efficient and adaptive cooling strategies for future high-performance computing systems.

Chiplet Standardization

Chiplet standardization is a critical aspect of advancing the adoption and implementation of chiplet technology in high-performance computing systems. As the industry moves towards disaggregated chip designs, the need for common standards and protocols becomes increasingly important to ensure interoperability and scalability.

One of the key initiatives in chiplet standardization is the Universal Chiplet Interconnect Express (UCIe) consortium. Formed by leading semiconductor companies, UCIe aims to establish an open industry standard for die-to-die interconnects. This standard addresses various aspects of chiplet integration, including physical layer specifications, protocol stack, and software abstraction layers.

The UCIe standard defines two primary interfaces: the Die-to-Die (D2D) interface for chiplets within a package, and the Package-to-Package (P2P) interface for communication between different packages. These standardized interfaces enable seamless integration of chiplets from different vendors, fostering innovation and competition in the chiplet ecosystem.

Another important standardization effort is the Open Compute Project's (OCP) Chiplet Design Exchange (CDX) format. CDX aims to create a common language for describing chiplet designs, facilitating easier exchange of chiplet intellectual property (IP) between different companies and design teams.

The JEDEC Solid State Technology Association has also been actively involved in chiplet standardization. Their JC-63 Committee for Multichip Packages is working on developing standards for chiplet-based systems, focusing on areas such as thermal management, testing, and reliability.

Standardization efforts extend beyond interconnects and design exchanges. Power delivery, thermal management, and signal integrity are other crucial areas where industry-wide standards are being developed. These standards aim to address the unique challenges posed by chiplet-based architectures in high-performance computing systems.

As chiplet technology continues to evolve, standardization efforts are likely to expand into new areas. Future standards may address advanced packaging technologies, 3D integration techniques, and novel interconnect solutions specific to chiplet-based designs. The ongoing collaboration between industry leaders, research institutions, and standards bodies will be crucial in shaping the future of chiplet technology and its applications in high-performance computing systems.

One of the key initiatives in chiplet standardization is the Universal Chiplet Interconnect Express (UCIe) consortium. Formed by leading semiconductor companies, UCIe aims to establish an open industry standard for die-to-die interconnects. This standard addresses various aspects of chiplet integration, including physical layer specifications, protocol stack, and software abstraction layers.

The UCIe standard defines two primary interfaces: the Die-to-Die (D2D) interface for chiplets within a package, and the Package-to-Package (P2P) interface for communication between different packages. These standardized interfaces enable seamless integration of chiplets from different vendors, fostering innovation and competition in the chiplet ecosystem.

Another important standardization effort is the Open Compute Project's (OCP) Chiplet Design Exchange (CDX) format. CDX aims to create a common language for describing chiplet designs, facilitating easier exchange of chiplet intellectual property (IP) between different companies and design teams.

The JEDEC Solid State Technology Association has also been actively involved in chiplet standardization. Their JC-63 Committee for Multichip Packages is working on developing standards for chiplet-based systems, focusing on areas such as thermal management, testing, and reliability.

Standardization efforts extend beyond interconnects and design exchanges. Power delivery, thermal management, and signal integrity are other crucial areas where industry-wide standards are being developed. These standards aim to address the unique challenges posed by chiplet-based architectures in high-performance computing systems.

As chiplet technology continues to evolve, standardization efforts are likely to expand into new areas. Future standards may address advanced packaging technologies, 3D integration techniques, and novel interconnect solutions specific to chiplet-based designs. The ongoing collaboration between industry leaders, research institutions, and standards bodies will be crucial in shaping the future of chiplet technology and its applications in high-performance computing systems.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!