How Chiplet Applications Facilitate Comprehensive System Management?

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Tech Evolution

The evolution of chiplet technology represents a paradigm shift in semiconductor design and manufacturing, driven by the need for improved performance, power efficiency, and cost-effectiveness in complex computing systems. This technological progression can be traced through several key stages, each marked by significant advancements and innovations.

In the early 2010s, the concept of chiplets began to gain traction as a response to the limitations of traditional monolithic chip designs. As Moore's Law approached its physical limits, chiplets emerged as a viable alternative to continue scaling performance and functionality. The initial focus was on developing interconnect technologies that could enable high-bandwidth, low-latency communication between multiple die on a single package.

By the mid-2010s, industry leaders such as AMD and Intel started implementing chiplet-based designs in their high-performance processors. AMD's Zen architecture, introduced in 2017, utilized a multi-chip module approach that combined multiple CPU dies with an I/O die. This marked a significant milestone in chiplet adoption for mainstream computing applications.

The late 2010s saw the expansion of chiplet technology beyond CPUs to other components such as GPUs, memory, and specialized accelerators. This period was characterized by the development of advanced packaging technologies like 2.5D and 3D integration, which allowed for more efficient interconnects and higher chip density.

As chiplet technology matured, the focus shifted towards standardization and interoperability. The development of open standards like Universal Chiplet Interconnect Express (UCIe) in the early 2020s aimed to create a common ecosystem for chiplet-based designs, enabling mix-and-match capabilities across different vendors and technologies.

The most recent phase of chiplet evolution has been centered on comprehensive system management. This includes advancements in power distribution, thermal management, and system-level optimization across multiple chiplets. The integration of AI and machine learning algorithms for dynamic resource allocation and performance tuning has become a key area of innovation.

Looking forward, the chiplet technology roadmap is expected to include further miniaturization of interconnects, increased integration of heterogeneous components, and the development of more sophisticated system-level management techniques. These advancements will be crucial in addressing the growing demands of emerging applications such as artificial intelligence, edge computing, and high-performance data centers.

In the early 2010s, the concept of chiplets began to gain traction as a response to the limitations of traditional monolithic chip designs. As Moore's Law approached its physical limits, chiplets emerged as a viable alternative to continue scaling performance and functionality. The initial focus was on developing interconnect technologies that could enable high-bandwidth, low-latency communication between multiple die on a single package.

By the mid-2010s, industry leaders such as AMD and Intel started implementing chiplet-based designs in their high-performance processors. AMD's Zen architecture, introduced in 2017, utilized a multi-chip module approach that combined multiple CPU dies with an I/O die. This marked a significant milestone in chiplet adoption for mainstream computing applications.

The late 2010s saw the expansion of chiplet technology beyond CPUs to other components such as GPUs, memory, and specialized accelerators. This period was characterized by the development of advanced packaging technologies like 2.5D and 3D integration, which allowed for more efficient interconnects and higher chip density.

As chiplet technology matured, the focus shifted towards standardization and interoperability. The development of open standards like Universal Chiplet Interconnect Express (UCIe) in the early 2020s aimed to create a common ecosystem for chiplet-based designs, enabling mix-and-match capabilities across different vendors and technologies.

The most recent phase of chiplet evolution has been centered on comprehensive system management. This includes advancements in power distribution, thermal management, and system-level optimization across multiple chiplets. The integration of AI and machine learning algorithms for dynamic resource allocation and performance tuning has become a key area of innovation.

Looking forward, the chiplet technology roadmap is expected to include further miniaturization of interconnects, increased integration of heterogeneous components, and the development of more sophisticated system-level management techniques. These advancements will be crucial in addressing the growing demands of emerging applications such as artificial intelligence, edge computing, and high-performance data centers.

System Mgmt Demands

The increasing complexity of modern computing systems has led to a growing demand for comprehensive system management solutions. As chiplet-based architectures gain prominence, they offer unique opportunities to address these management challenges more effectively. System management demands in chiplet applications encompass a wide range of requirements, including power management, thermal control, performance optimization, and fault tolerance.

Power management is a critical aspect of system management in chiplet-based designs. With multiple chiplets integrated into a single package, precise control over power distribution and consumption becomes essential. System managers must be able to dynamically allocate power resources among chiplets based on workload requirements and thermal constraints. This necessitates sophisticated power gating and voltage scaling techniques that can be applied at the chiplet level.

Thermal management is another crucial demand in chiplet applications. The high-density integration of multiple chiplets can lead to localized hotspots and thermal gradients across the package. Effective system management requires real-time temperature monitoring and adaptive cooling strategies to maintain optimal operating conditions for each chiplet. This may involve techniques such as dynamic frequency scaling, workload migration, and intelligent thermal-aware task scheduling.

Performance optimization is a key objective of system management in chiplet-based architectures. The disaggregated nature of chiplets allows for fine-grained control over individual components, enabling system managers to dynamically adjust performance parameters based on application requirements. This includes managing inter-chiplet communication bandwidth, optimizing cache coherence protocols, and balancing workloads across heterogeneous chiplets.

Fault tolerance and reliability are critical demands in chiplet-based systems, particularly for high-availability applications. System management must incorporate robust error detection and correction mechanisms at both the chiplet and system levels. This includes implementing redundancy schemes, managing chiplet-level reconfigurations in case of failures, and coordinating graceful degradation strategies to maintain system functionality even in the presence of faults.

Resource allocation and quality of service (QoS) management are essential aspects of system management in chiplet applications. With multiple chiplets sharing common resources such as memory bandwidth and I/O interfaces, system managers must implement sophisticated arbitration and prioritization schemes to ensure fair and efficient resource utilization. This requires real-time monitoring of resource usage and dynamic adjustment of allocation policies based on application priorities and service level agreements.

Security management is an increasingly important demand in chiplet-based systems. As chiplets may come from different vendors and incorporate various intellectual properties, system management must address potential security vulnerabilities at the chiplet interfaces and ensure secure communication between chiplets. This includes implementing encryption and authentication mechanisms, managing secure boot processes, and providing isolation between chiplets with different trust levels.

Power management is a critical aspect of system management in chiplet-based designs. With multiple chiplets integrated into a single package, precise control over power distribution and consumption becomes essential. System managers must be able to dynamically allocate power resources among chiplets based on workload requirements and thermal constraints. This necessitates sophisticated power gating and voltage scaling techniques that can be applied at the chiplet level.

Thermal management is another crucial demand in chiplet applications. The high-density integration of multiple chiplets can lead to localized hotspots and thermal gradients across the package. Effective system management requires real-time temperature monitoring and adaptive cooling strategies to maintain optimal operating conditions for each chiplet. This may involve techniques such as dynamic frequency scaling, workload migration, and intelligent thermal-aware task scheduling.

Performance optimization is a key objective of system management in chiplet-based architectures. The disaggregated nature of chiplets allows for fine-grained control over individual components, enabling system managers to dynamically adjust performance parameters based on application requirements. This includes managing inter-chiplet communication bandwidth, optimizing cache coherence protocols, and balancing workloads across heterogeneous chiplets.

Fault tolerance and reliability are critical demands in chiplet-based systems, particularly for high-availability applications. System management must incorporate robust error detection and correction mechanisms at both the chiplet and system levels. This includes implementing redundancy schemes, managing chiplet-level reconfigurations in case of failures, and coordinating graceful degradation strategies to maintain system functionality even in the presence of faults.

Resource allocation and quality of service (QoS) management are essential aspects of system management in chiplet applications. With multiple chiplets sharing common resources such as memory bandwidth and I/O interfaces, system managers must implement sophisticated arbitration and prioritization schemes to ensure fair and efficient resource utilization. This requires real-time monitoring of resource usage and dynamic adjustment of allocation policies based on application priorities and service level agreements.

Security management is an increasingly important demand in chiplet-based systems. As chiplets may come from different vendors and incorporate various intellectual properties, system management must address potential security vulnerabilities at the chiplet interfaces and ensure secure communication between chiplets. This includes implementing encryption and authentication mechanisms, managing secure boot processes, and providing isolation between chiplets with different trust levels.

Chiplet Challenges

While chiplets offer numerous advantages in system design and performance, they also present significant challenges that need to be addressed for successful implementation and comprehensive system management. One of the primary challenges is the complexity of integration. Chiplets require sophisticated packaging technologies and interconnect solutions to function as a cohesive system. This integration complexity can lead to increased design time, higher costs, and potential reliability issues if not managed properly.

Another major challenge is thermal management. As chiplets allow for higher performance density, they can generate significant heat in a concentrated area. This heat dissipation becomes more challenging in a multi-chiplet system, requiring advanced cooling solutions and careful thermal design considerations to maintain optimal operating temperatures and prevent performance degradation.

Power management presents another hurdle in chiplet-based systems. Each chiplet may have different power requirements and operating voltages, necessitating complex power delivery networks and sophisticated power management schemes. Balancing power consumption across multiple chiplets while optimizing overall system performance adds another layer of complexity to system management.

Interoperability and standardization pose significant challenges in the chiplet ecosystem. The lack of universal standards for chiplet interfaces and protocols can hinder the development of a robust chiplet marketplace and limit the ability to mix and match chiplets from different vendors. This challenge extends to software and firmware development, where ensuring compatibility and seamless operation across diverse chiplet configurations becomes crucial.

Testing and validation of chiplet-based systems present unique challenges. Traditional testing methodologies may not be sufficient for multi-chiplet designs, requiring new approaches to ensure system-level reliability and performance. This includes developing comprehensive test strategies that can verify the functionality and performance of individual chiplets as well as their interactions within the complete system.

Lastly, the challenge of yield management in chiplet production cannot be overlooked. While chiplets can potentially improve overall yield by allowing smaller, more manageable die sizes, the increased number of components and interfaces in a multi-chiplet system can introduce new yield challenges. Ensuring consistent quality and performance across all chiplets in a system becomes critical for maintaining overall product reliability and cost-effectiveness.

Another major challenge is thermal management. As chiplets allow for higher performance density, they can generate significant heat in a concentrated area. This heat dissipation becomes more challenging in a multi-chiplet system, requiring advanced cooling solutions and careful thermal design considerations to maintain optimal operating temperatures and prevent performance degradation.

Power management presents another hurdle in chiplet-based systems. Each chiplet may have different power requirements and operating voltages, necessitating complex power delivery networks and sophisticated power management schemes. Balancing power consumption across multiple chiplets while optimizing overall system performance adds another layer of complexity to system management.

Interoperability and standardization pose significant challenges in the chiplet ecosystem. The lack of universal standards for chiplet interfaces and protocols can hinder the development of a robust chiplet marketplace and limit the ability to mix and match chiplets from different vendors. This challenge extends to software and firmware development, where ensuring compatibility and seamless operation across diverse chiplet configurations becomes crucial.

Testing and validation of chiplet-based systems present unique challenges. Traditional testing methodologies may not be sufficient for multi-chiplet designs, requiring new approaches to ensure system-level reliability and performance. This includes developing comprehensive test strategies that can verify the functionality and performance of individual chiplets as well as their interactions within the complete system.

Lastly, the challenge of yield management in chiplet production cannot be overlooked. While chiplets can potentially improve overall yield by allowing smaller, more manageable die sizes, the increased number of components and interfaces in a multi-chiplet system can introduce new yield challenges. Ensuring consistent quality and performance across all chiplets in a system becomes critical for maintaining overall product reliability and cost-effectiveness.

Chiplet Mgmt Solutions

01 Power management in chiplet systems

Efficient power management techniques for chiplet-based systems, including dynamic voltage and frequency scaling, power gating, and intelligent power distribution across multiple chiplets. These methods aim to optimize energy consumption while maintaining performance in complex multi-chiplet architectures.- Power management in chiplet systems: Chiplet systems employ advanced power management techniques to optimize energy consumption across multiple chiplets. This includes dynamic voltage and frequency scaling, power gating, and intelligent power distribution strategies to balance performance and efficiency in multi-chiplet architectures.

- Thermal management for chiplet-based designs: Effective thermal management is crucial in chiplet systems to maintain optimal performance and reliability. This involves innovative cooling solutions, temperature monitoring, and thermal-aware task scheduling across chiplets to prevent hotspots and ensure uniform heat distribution.

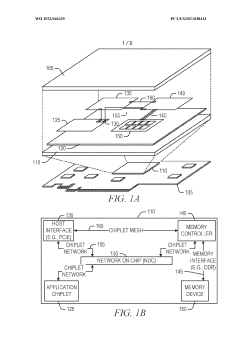

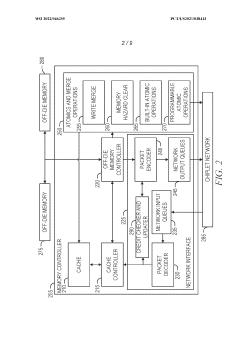

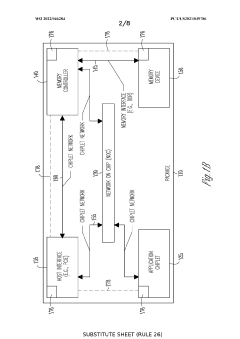

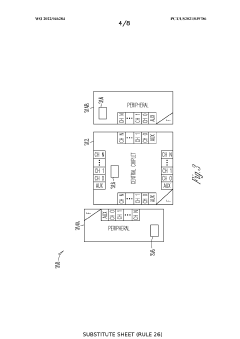

- Inter-chiplet communication and data management: Managing data flow and communication between chiplets is essential for system performance. This includes high-speed interconnects, efficient routing protocols, and data coherency mechanisms to ensure seamless integration and operation of multiple chiplets within a single package.

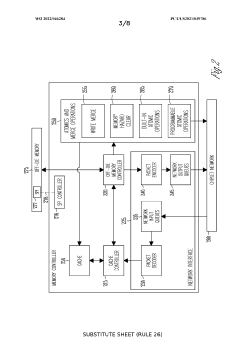

- System-level integration and management of heterogeneous chiplets: Integrating diverse chiplets with different functionalities and technologies requires sophisticated system-level management. This involves coordinating heterogeneous components, managing resource allocation, and optimizing overall system performance through intelligent chiplet orchestration.

- Reliability and fault tolerance in chiplet systems: Ensuring reliability in multi-chiplet systems is critical. This includes implementing fault detection and isolation mechanisms, redundancy strategies, and adaptive reconfiguration techniques to maintain system integrity and performance in the event of chiplet failures or degradation.

02 Thermal management for chiplet architectures

Advanced thermal management solutions for chiplet systems, incorporating on-chip sensors, adaptive cooling mechanisms, and thermal-aware task scheduling. These approaches help maintain optimal operating temperatures across chiplets, enhancing overall system reliability and performance.Expand Specific Solutions03 Inter-chiplet communication and data management

Innovative techniques for managing data flow and communication between chiplets, including high-speed interconnects, network-on-chip architectures, and intelligent routing algorithms. These solutions aim to minimize latency and maximize bandwidth in multi-chiplet systems.Expand Specific Solutions04 System-level integration and management of heterogeneous chiplets

Strategies for integrating and managing diverse chiplets with different functionalities, process nodes, or from various manufacturers. This includes adaptive resource allocation, dynamic reconfiguration, and unified management interfaces for heterogeneous chiplet ecosystems.Expand Specific Solutions05 Reliability and fault tolerance in chiplet systems

Methods to enhance reliability and fault tolerance in chiplet-based architectures, including redundancy mechanisms, error detection and correction techniques, and graceful degradation strategies. These approaches aim to maintain system integrity and performance in the event of chiplet failures or errors.Expand Specific Solutions

Chiplet Ecosystem

The chiplet application market is in a growth phase, driven by increasing demand for high-performance computing and AI applications. The market size is expanding rapidly, with major players like Intel, AMD, and TSMC investing heavily in chiplet technology. The competitive landscape is characterized by a mix of established semiconductor giants and innovative startups. Companies such as Intel, Micron Technology, and Huawei Technologies are at the forefront of chiplet development, leveraging their expertise in chip design and manufacturing. The technology's maturity is advancing quickly, with companies like ASUSTek Computer and VIA Technologies contributing to system-level integration. As the industry progresses, we can expect to see more collaborations and standardization efforts to address challenges in chiplet interconnects and system management.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei's chiplet strategy for system management focuses on their Kirin series SoCs and custom AI accelerators. The company has developed a chiplet-based architecture called "Da Vinci" for AI computing, which allows for flexible combination of processing units and memory[4]. Huawei's approach includes a high-speed interconnect fabric that enables efficient communication between chiplets, supporting heterogeneous integration of various IP blocks[5]. Their chiplet design also incorporates advanced power management techniques, such as fine-grained power gating and dynamic voltage and frequency scaling, to optimize energy efficiency across the entire system[6].

Strengths: Flexible AI acceleration capabilities, efficient heterogeneous integration, and advanced power management. Weaknesses: Potential challenges in ecosystem development and international supply chain dependencies.

Intel Corp.

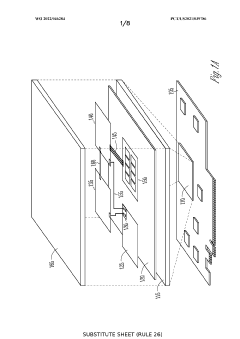

Technical Solution: Intel's approach to chiplet applications for comprehensive system management involves their Foveros 3D packaging technology. This advanced packaging solution allows for the vertical stacking of multiple chiplets, enabling more efficient power delivery and thermal management[1]. Intel's Ponte Vecchio GPU, built using Foveros, incorporates over 100 billion transistors across 47 chiplets, demonstrating the scalability and flexibility of this approach[2]. The company has also developed the Advanced Interface Bus (AIB) standard for high-bandwidth, low-power die-to-die communication between chiplets[3]. This facilitates seamless integration of diverse IP blocks and enables modular design for improved system management and customization.

Strengths: Advanced 3D packaging technology, high integration density, and standardized die-to-die communication. Weaknesses: Potential thermal challenges in densely packed 3D structures and higher manufacturing complexity.

Chiplet Innovations

Network credit return mechanisms

PatentWO2022046255A1

Innovation

- Implementing a simplified credit return mechanism where only one flit per transfer cycle includes credit return data, using a wide bus to transmit multiple flits, and employing bitwise-OR operations to combine credit return data, reducing the need for additional circuitry and minimizing delays in the critical path.

Method for configuring multiple input-output channels

PatentWO2022046284A1

Innovation

- The implementation of a Chiplet Protocol Interface (CPI) network with Advanced Interface Bus (AIB) channels and credit-based flow control, allowing for flexible virtual channel mapping and minimizing latency and energy consumption through packetized protocols and serialization-deserialization (SERDES) hardware, while enabling efficient inter-chiplet communication.

Chiplet Standards

Chiplet standards play a crucial role in facilitating comprehensive system management within chiplet applications. These standards provide a framework for interoperability, communication, and integration of diverse chiplet components, enabling efficient and effective system-level management.

The development of chiplet standards has been driven by the need for modular and scalable chip designs. Organizations such as the Open Compute Project (OCP) and the Universal Chiplet Interconnect Express (UCIe) consortium have been at the forefront of establishing these standards. Their efforts have resulted in specifications that address various aspects of chiplet integration, including physical interconnects, protocols, and power management.

One of the key chiplet standards is UCIe, which defines a die-to-die interconnect specification for chiplets. This standard enables high-bandwidth, low-latency communication between different chiplets within a package. By providing a common interface, UCIe allows for the seamless integration of chiplets from different vendors, fostering innovation and competition in the chiplet ecosystem.

Another important standard is the Advanced Interface Bus (AIB), developed by Intel. AIB provides a standardized interface for chip-to-chip communication, supporting high-speed data transfer and power efficiency. This standard has been widely adopted in the industry and has contributed to the advancement of chiplet-based designs.

The Bunch of Wires (BoW) interface, promoted by the OCP, is another significant chiplet standard. BoW offers a simple and cost-effective approach to chiplet interconnection, making it suitable for a wide range of applications. This standard has gained traction in the industry due to its flexibility and ease of implementation.

Chiplet standards also address power management and thermal considerations. The Power Management Bus (PMBus) specification, for instance, provides a standardized approach to power management across different chiplets. This enables coordinated power control and optimization at the system level, contributing to improved energy efficiency and thermal management.

The adoption of these standards has significant implications for system management in chiplet applications. They enable seamless integration of diverse chiplets, allowing system designers to mix and match components from different vendors to create optimized solutions. This modularity and flexibility facilitate more efficient system-level management, as individual chiplets can be monitored, controlled, and updated independently.

Furthermore, chiplet standards promote interoperability and reduce design complexity. This simplifies system management tasks such as performance monitoring, fault detection, and software updates. The standardized interfaces and protocols also enable the development of common management tools and software, further enhancing the efficiency of system management in chiplet-based designs.

The development of chiplet standards has been driven by the need for modular and scalable chip designs. Organizations such as the Open Compute Project (OCP) and the Universal Chiplet Interconnect Express (UCIe) consortium have been at the forefront of establishing these standards. Their efforts have resulted in specifications that address various aspects of chiplet integration, including physical interconnects, protocols, and power management.

One of the key chiplet standards is UCIe, which defines a die-to-die interconnect specification for chiplets. This standard enables high-bandwidth, low-latency communication between different chiplets within a package. By providing a common interface, UCIe allows for the seamless integration of chiplets from different vendors, fostering innovation and competition in the chiplet ecosystem.

Another important standard is the Advanced Interface Bus (AIB), developed by Intel. AIB provides a standardized interface for chip-to-chip communication, supporting high-speed data transfer and power efficiency. This standard has been widely adopted in the industry and has contributed to the advancement of chiplet-based designs.

The Bunch of Wires (BoW) interface, promoted by the OCP, is another significant chiplet standard. BoW offers a simple and cost-effective approach to chiplet interconnection, making it suitable for a wide range of applications. This standard has gained traction in the industry due to its flexibility and ease of implementation.

Chiplet standards also address power management and thermal considerations. The Power Management Bus (PMBus) specification, for instance, provides a standardized approach to power management across different chiplets. This enables coordinated power control and optimization at the system level, contributing to improved energy efficiency and thermal management.

The adoption of these standards has significant implications for system management in chiplet applications. They enable seamless integration of diverse chiplets, allowing system designers to mix and match components from different vendors to create optimized solutions. This modularity and flexibility facilitate more efficient system-level management, as individual chiplets can be monitored, controlled, and updated independently.

Furthermore, chiplet standards promote interoperability and reduce design complexity. This simplifies system management tasks such as performance monitoring, fault detection, and software updates. The standardized interfaces and protocols also enable the development of common management tools and software, further enhancing the efficiency of system management in chiplet-based designs.

Chiplet Security

Chiplet security has become a critical concern in the era of disaggregated chip design. As chiplets from various sources are integrated into a single package, ensuring the integrity and confidentiality of data across these components presents unique challenges. The security of chiplet-based systems must be addressed at multiple levels, from individual chiplets to the interconnects and the overall system architecture.

At the chiplet level, manufacturers are implementing hardware-based security features such as secure boot processes, cryptographic engines, and tamper-resistant storage. These measures aim to protect against unauthorized access and manipulation of chiplet functionality. Additionally, unique identifiers and authentication mechanisms are being embedded within chiplets to verify their authenticity and prevent counterfeiting.

The interconnects between chiplets represent potential vulnerabilities that must be secured. Encryption of data in transit between chiplets is becoming standard practice to protect against eavesdropping and data interception. Advanced protocols are being developed to ensure secure communication channels and maintain data integrity across the chiplet ecosystem.

System-level security in chiplet architectures involves coordinating security policies and mechanisms across all integrated components. This includes implementing a root of trust that extends across the entire package, managing cryptographic keys, and establishing secure channels for inter-chiplet communication. Security management engines are being designed to oversee and orchestrate these security functions across the heterogeneous chiplet environment.

The modular nature of chiplets introduces new considerations for supply chain security. With components potentially sourced from multiple vendors, ensuring the trustworthiness of each chiplet becomes paramount. Rigorous validation and verification processes are being developed to detect malicious insertions or compromised chiplets before integration.

As chiplet technology evolves, security standards and best practices are emerging to guide manufacturers and system integrators. These include specifications for secure chiplet interfaces, protocols for attestation and authentication, and guidelines for implementing end-to-end security in chiplet-based systems. Collaborative efforts within the industry are driving the development of comprehensive security frameworks tailored to the unique challenges of chiplet architectures.

At the chiplet level, manufacturers are implementing hardware-based security features such as secure boot processes, cryptographic engines, and tamper-resistant storage. These measures aim to protect against unauthorized access and manipulation of chiplet functionality. Additionally, unique identifiers and authentication mechanisms are being embedded within chiplets to verify their authenticity and prevent counterfeiting.

The interconnects between chiplets represent potential vulnerabilities that must be secured. Encryption of data in transit between chiplets is becoming standard practice to protect against eavesdropping and data interception. Advanced protocols are being developed to ensure secure communication channels and maintain data integrity across the chiplet ecosystem.

System-level security in chiplet architectures involves coordinating security policies and mechanisms across all integrated components. This includes implementing a root of trust that extends across the entire package, managing cryptographic keys, and establishing secure channels for inter-chiplet communication. Security management engines are being designed to oversee and orchestrate these security functions across the heterogeneous chiplet environment.

The modular nature of chiplets introduces new considerations for supply chain security. With components potentially sourced from multiple vendors, ensuring the trustworthiness of each chiplet becomes paramount. Rigorous validation and verification processes are being developed to detect malicious insertions or compromised chiplets before integration.

As chiplet technology evolves, security standards and best practices are emerging to guide manufacturers and system integrators. These include specifications for secure chiplet interfaces, protocols for attestation and authentication, and guidelines for implementing end-to-end security in chiplet-based systems. Collaborative efforts within the industry are driving the development of comprehensive security frameworks tailored to the unique challenges of chiplet architectures.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!