Chiplet Power in Transformative Telecommunication Systems

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Power Evolution

The evolution of chiplet power in transformative telecommunication systems has been marked by significant advancements and paradigm shifts. Initially, chiplets were primarily used to address the limitations of monolithic chip designs, offering improved yield and cost-effectiveness. As the demand for more powerful and efficient telecommunication systems grew, chiplet technology evolved to meet these challenges.

In the early stages, chiplet power management focused on basic voltage regulation and distribution across multiple dies. However, as the complexity of telecommunication systems increased, more sophisticated power management techniques emerged. The introduction of advanced packaging technologies, such as 2.5D and 3D integration, allowed for better power distribution and thermal management among chiplets.

A key milestone in chiplet power evolution was the development of fine-grained power gating techniques. This innovation enabled individual chiplets or specific functional blocks within chiplets to be powered down when not in use, significantly reducing overall power consumption. As a result, telecommunication systems could achieve higher energy efficiency without compromising performance.

The advent of artificial intelligence and machine learning in telecommunication systems further drove the evolution of chiplet power management. Adaptive power management algorithms were developed to dynamically adjust power allocation based on workload and environmental conditions. This approach allowed for optimal power utilization across different chiplets, enhancing overall system efficiency.

Another significant development was the integration of advanced power delivery networks (PDNs) specifically designed for chiplet-based architectures. These PDNs enabled more precise voltage control and reduced power loss, addressing the unique challenges posed by multi-die configurations in telecommunication systems.

As the industry moved towards 5G and beyond, the focus shifted to ultra-low power chiplet designs for edge computing and IoT applications. This led to the development of novel power-aware interconnect technologies and chiplet-level power management units (PMUs) capable of fine-tuning power consumption based on real-time network demands.

Recent advancements in chiplet power evolution include the exploration of novel materials and packaging technologies to further improve power efficiency. For instance, the use of gallium nitride (GaN) and silicon carbide (SiC) in power management circuits has shown promising results in reducing power losses and improving thermal performance in high-frequency telecommunication applications.

Looking ahead, the evolution of chiplet power in transformative telecommunication systems is expected to continue, with a focus on heterogeneous integration, AI-driven power optimization, and the development of energy-harvesting techniques to support self-powered chiplets in next-generation communication networks.

In the early stages, chiplet power management focused on basic voltage regulation and distribution across multiple dies. However, as the complexity of telecommunication systems increased, more sophisticated power management techniques emerged. The introduction of advanced packaging technologies, such as 2.5D and 3D integration, allowed for better power distribution and thermal management among chiplets.

A key milestone in chiplet power evolution was the development of fine-grained power gating techniques. This innovation enabled individual chiplets or specific functional blocks within chiplets to be powered down when not in use, significantly reducing overall power consumption. As a result, telecommunication systems could achieve higher energy efficiency without compromising performance.

The advent of artificial intelligence and machine learning in telecommunication systems further drove the evolution of chiplet power management. Adaptive power management algorithms were developed to dynamically adjust power allocation based on workload and environmental conditions. This approach allowed for optimal power utilization across different chiplets, enhancing overall system efficiency.

Another significant development was the integration of advanced power delivery networks (PDNs) specifically designed for chiplet-based architectures. These PDNs enabled more precise voltage control and reduced power loss, addressing the unique challenges posed by multi-die configurations in telecommunication systems.

As the industry moved towards 5G and beyond, the focus shifted to ultra-low power chiplet designs for edge computing and IoT applications. This led to the development of novel power-aware interconnect technologies and chiplet-level power management units (PMUs) capable of fine-tuning power consumption based on real-time network demands.

Recent advancements in chiplet power evolution include the exploration of novel materials and packaging technologies to further improve power efficiency. For instance, the use of gallium nitride (GaN) and silicon carbide (SiC) in power management circuits has shown promising results in reducing power losses and improving thermal performance in high-frequency telecommunication applications.

Looking ahead, the evolution of chiplet power in transformative telecommunication systems is expected to continue, with a focus on heterogeneous integration, AI-driven power optimization, and the development of energy-harvesting techniques to support self-powered chiplets in next-generation communication networks.

Telecom Market Demands

The telecommunications market is experiencing a significant shift driven by the increasing demand for high-performance, energy-efficient systems. This transformation is particularly evident in the growing interest in chiplet-based architectures for next-generation telecommunication equipment. The market demand for chiplet power solutions in transformative telecommunication systems is being fueled by several key factors.

Firstly, the exponential growth in data traffic and the need for higher bandwidth are pushing telecom operators to seek more powerful and efficient network infrastructure. As 5G networks continue to expand and 6G technologies are on the horizon, there is a pressing need for telecommunication systems that can handle massive data throughputs while maintaining low latency. Chiplet-based designs offer a promising solution to meet these demands by allowing for modular, scalable, and high-performance systems.

The telecom industry is also facing increasing pressure to reduce energy consumption and operational costs. With data centers and network infrastructure accounting for a significant portion of global energy usage, there is a strong market pull for more power-efficient solutions. Chiplet architectures, with their ability to optimize power distribution and thermal management, are seen as a key technology to address these concerns.

Moreover, the market is demanding greater flexibility and customization in telecommunication systems. Traditional monolithic chip designs are becoming less viable as the complexity and diversity of telecom applications increase. Chiplet-based approaches allow for mix-and-match capabilities, enabling telecom equipment manufacturers to create tailored solutions for specific network requirements more efficiently and cost-effectively.

Another driving force in the market is the need for improved time-to-market and reduced development costs. The modular nature of chiplets allows for faster product development cycles and easier upgrades, which is crucial in the fast-paced telecom industry. This aligns well with the industry's push towards more agile and adaptable network infrastructures.

The market is also showing a strong interest in solutions that can support edge computing and distributed network architectures. As telecom networks evolve to support IoT, AI, and other emerging technologies, there is a growing demand for chiplet-based systems that can provide high-performance computing capabilities closer to the network edge.

Lastly, the global semiconductor supply chain challenges have highlighted the need for more resilient and diversified sourcing strategies. Chiplet-based designs offer the potential for greater supply chain flexibility, as different components can be sourced from various manufacturers, reducing dependency on single suppliers and mitigating risks associated with geopolitical tensions or production disruptions.

Firstly, the exponential growth in data traffic and the need for higher bandwidth are pushing telecom operators to seek more powerful and efficient network infrastructure. As 5G networks continue to expand and 6G technologies are on the horizon, there is a pressing need for telecommunication systems that can handle massive data throughputs while maintaining low latency. Chiplet-based designs offer a promising solution to meet these demands by allowing for modular, scalable, and high-performance systems.

The telecom industry is also facing increasing pressure to reduce energy consumption and operational costs. With data centers and network infrastructure accounting for a significant portion of global energy usage, there is a strong market pull for more power-efficient solutions. Chiplet architectures, with their ability to optimize power distribution and thermal management, are seen as a key technology to address these concerns.

Moreover, the market is demanding greater flexibility and customization in telecommunication systems. Traditional monolithic chip designs are becoming less viable as the complexity and diversity of telecom applications increase. Chiplet-based approaches allow for mix-and-match capabilities, enabling telecom equipment manufacturers to create tailored solutions for specific network requirements more efficiently and cost-effectively.

Another driving force in the market is the need for improved time-to-market and reduced development costs. The modular nature of chiplets allows for faster product development cycles and easier upgrades, which is crucial in the fast-paced telecom industry. This aligns well with the industry's push towards more agile and adaptable network infrastructures.

The market is also showing a strong interest in solutions that can support edge computing and distributed network architectures. As telecom networks evolve to support IoT, AI, and other emerging technologies, there is a growing demand for chiplet-based systems that can provide high-performance computing capabilities closer to the network edge.

Lastly, the global semiconductor supply chain challenges have highlighted the need for more resilient and diversified sourcing strategies. Chiplet-based designs offer the potential for greater supply chain flexibility, as different components can be sourced from various manufacturers, reducing dependency on single suppliers and mitigating risks associated with geopolitical tensions or production disruptions.

Chiplet Power Challenges

As chiplet technology continues to revolutionize the telecommunications industry, power management has emerged as a critical challenge. The integration of multiple chiplets within a single package introduces complex power distribution and thermal management issues that must be addressed to ensure optimal system performance and reliability.

One of the primary challenges in chiplet power management is the need for efficient power delivery to individual chiplets. Traditional power delivery networks may struggle to provide adequate power to each chiplet, especially in high-performance systems with multiple processing units. This challenge is exacerbated by the increasing power density of modern chiplets, which can lead to localized hotspots and thermal management issues.

Another significant hurdle is the management of power consumption across different chiplets. As each chiplet may have varying power requirements and operating conditions, coordinating power states and optimizing overall system efficiency becomes increasingly complex. This challenge is particularly pronounced in heterogeneous systems that combine chiplets with different functionalities and power profiles.

The integration of chiplets also introduces challenges related to power integrity and signal integrity. As chiplets are interconnected through high-speed interfaces, maintaining clean power and ground planes becomes crucial to prevent signal degradation and ensure reliable communication between chiplets. This requires careful consideration of power distribution network design and decoupling strategies.

Thermal management presents another set of challenges in chiplet-based systems. The close proximity of multiple chiplets can lead to thermal coupling effects, where heat generated by one chiplet affects the performance and reliability of adjacent chiplets. Developing effective cooling solutions that can address these localized thermal issues while maintaining overall system efficiency is a significant engineering challenge.

Power gating and dynamic power management techniques, which are commonly used in traditional monolithic designs, must be adapted and optimized for chiplet-based architectures. Implementing fine-grained power control across multiple chiplets while maintaining system coherency and performance requires sophisticated power management algorithms and hardware support.

Furthermore, the diverse nature of chiplet-based systems introduces challenges in power modeling and simulation. Accurately predicting power consumption and thermal behavior in complex multi-chiplet configurations requires advanced modeling techniques and tools that can account for the interactions between different chiplets and their impact on overall system power characteristics.

As the telecommunications industry continues to push the boundaries of performance and integration, addressing these chiplet power challenges will be crucial for realizing the full potential of this transformative technology. Innovative solutions in power delivery, thermal management, and system-level power optimization will be key to overcoming these hurdles and enabling the next generation of high-performance, energy-efficient telecommunication systems.

One of the primary challenges in chiplet power management is the need for efficient power delivery to individual chiplets. Traditional power delivery networks may struggle to provide adequate power to each chiplet, especially in high-performance systems with multiple processing units. This challenge is exacerbated by the increasing power density of modern chiplets, which can lead to localized hotspots and thermal management issues.

Another significant hurdle is the management of power consumption across different chiplets. As each chiplet may have varying power requirements and operating conditions, coordinating power states and optimizing overall system efficiency becomes increasingly complex. This challenge is particularly pronounced in heterogeneous systems that combine chiplets with different functionalities and power profiles.

The integration of chiplets also introduces challenges related to power integrity and signal integrity. As chiplets are interconnected through high-speed interfaces, maintaining clean power and ground planes becomes crucial to prevent signal degradation and ensure reliable communication between chiplets. This requires careful consideration of power distribution network design and decoupling strategies.

Thermal management presents another set of challenges in chiplet-based systems. The close proximity of multiple chiplets can lead to thermal coupling effects, where heat generated by one chiplet affects the performance and reliability of adjacent chiplets. Developing effective cooling solutions that can address these localized thermal issues while maintaining overall system efficiency is a significant engineering challenge.

Power gating and dynamic power management techniques, which are commonly used in traditional monolithic designs, must be adapted and optimized for chiplet-based architectures. Implementing fine-grained power control across multiple chiplets while maintaining system coherency and performance requires sophisticated power management algorithms and hardware support.

Furthermore, the diverse nature of chiplet-based systems introduces challenges in power modeling and simulation. Accurately predicting power consumption and thermal behavior in complex multi-chiplet configurations requires advanced modeling techniques and tools that can account for the interactions between different chiplets and their impact on overall system power characteristics.

As the telecommunications industry continues to push the boundaries of performance and integration, addressing these chiplet power challenges will be crucial for realizing the full potential of this transformative technology. Innovative solutions in power delivery, thermal management, and system-level power optimization will be key to overcoming these hurdles and enabling the next generation of high-performance, energy-efficient telecommunication systems.

Current Power Solutions

01 Power management in chiplet architectures

Chiplet architectures employ advanced power management techniques to optimize energy efficiency across multiple dies. This includes dynamic voltage and frequency scaling, power gating, and intelligent power distribution among chiplets based on workload requirements. These strategies help balance performance and power consumption in complex multi-die systems.- Power management in chiplet architectures: Chiplet architectures employ advanced power management techniques to optimize energy consumption across multiple dies. This includes dynamic voltage and frequency scaling, power gating, and intelligent power distribution among chiplets based on workload requirements. These strategies help balance performance and power efficiency in complex multi-die systems.

- Inter-chiplet power delivery networks: Efficient power delivery networks are crucial for chiplet-based designs. These networks involve sophisticated power routing schemes, on-chip voltage regulators, and advanced packaging technologies to ensure stable and uniform power distribution across multiple chiplets. This approach minimizes power loss and improves overall system efficiency.

- Thermal management for chiplet systems: Thermal management is critical in chiplet designs due to high power densities. Advanced cooling solutions, including integrated liquid cooling, microchannel heat sinks, and thermal interface materials, are employed to efficiently dissipate heat from multiple chiplets. This ensures optimal performance and reliability of the integrated system.

- Power-aware chiplet interconnects: Chiplet interconnect technologies focus on reducing power consumption while maintaining high bandwidth. This includes the development of low-power SerDes, optical interconnects, and advanced packaging techniques that minimize signal loss and power requirements for inter-chiplet communication, contributing to overall system energy efficiency.

- AI-driven power optimization for chiplets: Artificial intelligence techniques are being applied to optimize power consumption in chiplet-based systems. Machine learning algorithms predict power requirements, dynamically adjust power states, and optimize workload distribution across chiplets. This approach enables real-time power management and enhances overall energy efficiency of complex multi-die architectures.

02 Inter-chiplet power delivery networks

Efficient power delivery networks are crucial in chiplet designs to ensure stable and uniform power distribution across multiple dies. This involves innovative packaging technologies, advanced interconnects, and integrated voltage regulators to minimize power loss and maintain signal integrity between chiplets.Expand Specific Solutions03 Thermal management for chiplet systems

Thermal management is critical in chiplet designs due to the high power density and potential hotspots. Advanced cooling solutions, such as integrated liquid cooling, microchannel heat sinks, and thermal-aware chiplet placement, are employed to maintain optimal operating temperatures and prevent thermal throttling.Expand Specific Solutions04 Power-aware chiplet communication

Efficient communication between chiplets is essential for overall system performance and power efficiency. Low-power interconnect technologies, such as advanced SerDes and optical interconnects, are used to minimize power consumption during data transfer between chiplets while maintaining high bandwidth.Expand Specific Solutions05 AI-driven power optimization for chiplets

Artificial intelligence and machine learning techniques are increasingly used to optimize power consumption in chiplet-based systems. These approaches enable real-time power prediction, adaptive power management, and intelligent workload distribution among chiplets to maximize energy efficiency while meeting performance requirements.Expand Specific Solutions

Key Industry Players

The research on Chiplet Power in Transformative Telecommunication Systems is at a critical juncture, with the industry in a transitional phase. The market is experiencing rapid growth, driven by increasing demand for high-performance, energy-efficient telecommunication systems. Key players like Huawei, Ericsson, and Qualcomm are leading the charge, investing heavily in chiplet technology. The technology's maturity is advancing, with companies like ZTE and Samsung making significant strides. However, challenges remain in standardization and integration, indicating that the technology is still evolving. Collaboration between industry giants and research institutions is accelerating progress, positioning chiplet power as a transformative force in the telecommunications landscape.

Telefonaktiebolaget LM Ericsson

Technical Solution: Ericsson's research on chiplet power for telecommunication systems focuses on developing energy-efficient solutions for 5G and future 6G networks. Their approach involves a modular chiplet architecture that allows for flexible integration of different functional blocks, such as baseband processing, radio frequency (RF) components, and network management modules[7]. Ericsson has implemented advanced power management techniques, including dynamic power gating and per-chiplet voltage/frequency scaling, to optimize energy consumption based on network traffic patterns and environmental conditions. Their solution also incorporates high-efficiency voltage regulators and low-power interconnects between chiplets to minimize power losses[8]. Ericsson has developed a software-defined power management system that uses AI algorithms to predict network load and dynamically allocate power resources across the chiplet-based platform, ensuring optimal performance while minimizing energy consumption[9].

Strengths: Modular architecture for flexible integration, AI-driven power management, and optimization for 5G/6G networks. Weaknesses: Potential challenges in integrating with legacy telecommunication infrastructure.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed advanced chiplet power solutions for transformative telecommunication systems. Their approach involves a multi-chip module (MCM) design that integrates heterogeneous dies using 2.5D and 3D packaging technologies[1]. This allows for optimized power distribution and thermal management across different functional blocks. Huawei's chiplet architecture incorporates high-bandwidth interconnects and intelligent power management systems, enabling dynamic voltage and frequency scaling (DVFS) for each chiplet[2]. They have also implemented advanced power gating techniques to reduce static power consumption in idle chiplets. Huawei's solution includes on-chip voltage regulators and power delivery networks optimized for chiplet-based designs, ensuring efficient power delivery to individual dies[3].

Strengths: Advanced packaging technologies, optimized power distribution, and intelligent power management. Weaknesses: Potential increased complexity in manufacturing and higher initial costs.

Innovative Power Tech

Edge interface placements to enable chiplet rotation into multi-chiplet cluster

PatentPendingUS20240332257A1

Innovation

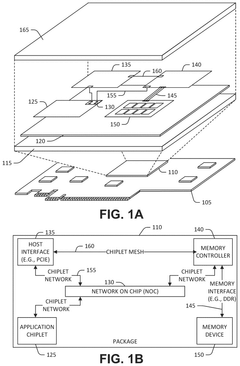

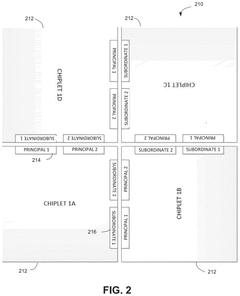

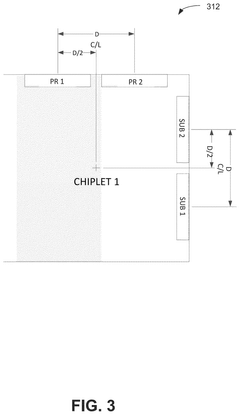

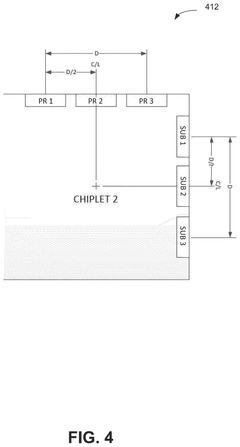

- The implementation of a chiplet architecture that uses a network-on-chip (NOC) with a chiplet protocol interface (CPI) to facilitate high-speed, flexible inter-chiplet communication, combined with a tightly packed matrix arrangement of chiplets and I/O micro-bumps for close-coupled interconnects, allowing for proper alignment and minimal footprint.

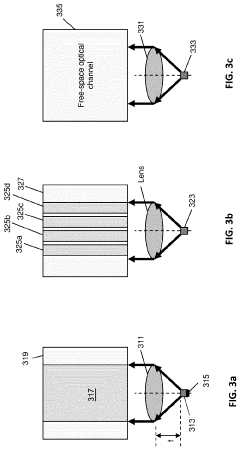

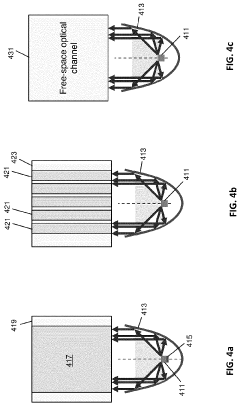

Interconnect networks using microLED-based optical links

PatentActiveUS11824590B2

Innovation

- The use of optical chip-to-chip interconnects with microLEDs as light sources, enabling high-density connections with linear densities over 10 Tbps/mm and low power consumption, along with vertically and planar launched parallel optical links to interconnect IC chips efficiently.

Thermal Management

Thermal management is a critical aspect of chiplet power in transformative telecommunication systems. As chiplets become more prevalent in advanced telecommunication devices, managing heat dissipation becomes increasingly challenging. The compact nature of chiplet designs leads to higher power densities, necessitating innovative cooling solutions to maintain optimal performance and reliability.

One of the primary thermal management strategies for chiplet-based systems is the implementation of advanced packaging technologies. These include the use of interposers and through-silicon vias (TSVs) to facilitate efficient heat transfer between chiplets and the package substrate. Additionally, the integration of thermal interface materials (TIMs) with superior thermal conductivity helps to reduce thermal resistance between components.

Active cooling techniques play a crucial role in chiplet thermal management. Liquid cooling systems, such as microchannel cold plates and two-phase cooling, are being explored to address the high heat fluxes generated by chiplets. These solutions offer significantly higher cooling capacities compared to traditional air cooling methods, enabling the development of more powerful and compact telecommunication systems.

Passive cooling methods are also being optimized for chiplet architectures. Heat spreaders and vapor chambers are being redesigned to accommodate the unique thermal profiles of chiplet-based designs. Advanced materials, such as graphene and carbon nanotubes, are being investigated for their exceptional thermal conductivity properties, potentially revolutionizing heat dissipation in future telecommunication devices.

Thermal-aware design methodologies are becoming increasingly important in chiplet-based systems. This involves considering thermal constraints during the early stages of system design, including chiplet placement, power distribution, and interconnect routing. Sophisticated thermal modeling and simulation tools are being developed to accurately predict and optimize the thermal behavior of complex chiplet arrangements.

Dynamic thermal management techniques are also being implemented to address the varying thermal loads in telecommunication systems. These include adaptive clock gating, dynamic voltage and frequency scaling (DVFS), and intelligent power management algorithms that can dynamically adjust system performance based on thermal conditions.

As telecommunication systems continue to evolve, the integration of artificial intelligence (AI) and machine learning (ML) algorithms for thermal management is gaining traction. These advanced techniques can predict thermal hotspots, optimize cooling resource allocation, and proactively adjust system parameters to maintain optimal thermal performance under varying workloads and environmental conditions.

One of the primary thermal management strategies for chiplet-based systems is the implementation of advanced packaging technologies. These include the use of interposers and through-silicon vias (TSVs) to facilitate efficient heat transfer between chiplets and the package substrate. Additionally, the integration of thermal interface materials (TIMs) with superior thermal conductivity helps to reduce thermal resistance between components.

Active cooling techniques play a crucial role in chiplet thermal management. Liquid cooling systems, such as microchannel cold plates and two-phase cooling, are being explored to address the high heat fluxes generated by chiplets. These solutions offer significantly higher cooling capacities compared to traditional air cooling methods, enabling the development of more powerful and compact telecommunication systems.

Passive cooling methods are also being optimized for chiplet architectures. Heat spreaders and vapor chambers are being redesigned to accommodate the unique thermal profiles of chiplet-based designs. Advanced materials, such as graphene and carbon nanotubes, are being investigated for their exceptional thermal conductivity properties, potentially revolutionizing heat dissipation in future telecommunication devices.

Thermal-aware design methodologies are becoming increasingly important in chiplet-based systems. This involves considering thermal constraints during the early stages of system design, including chiplet placement, power distribution, and interconnect routing. Sophisticated thermal modeling and simulation tools are being developed to accurately predict and optimize the thermal behavior of complex chiplet arrangements.

Dynamic thermal management techniques are also being implemented to address the varying thermal loads in telecommunication systems. These include adaptive clock gating, dynamic voltage and frequency scaling (DVFS), and intelligent power management algorithms that can dynamically adjust system performance based on thermal conditions.

As telecommunication systems continue to evolve, the integration of artificial intelligence (AI) and machine learning (ML) algorithms for thermal management is gaining traction. These advanced techniques can predict thermal hotspots, optimize cooling resource allocation, and proactively adjust system parameters to maintain optimal thermal performance under varying workloads and environmental conditions.

Standardization Efforts

Standardization efforts in chiplet power for transformative telecommunication systems have gained significant momentum in recent years. The increasing complexity and heterogeneity of modern telecommunication systems have necessitated the development of standardized approaches to chiplet power management. These efforts aim to address the challenges of power efficiency, thermal management, and system integration in multi-chip module designs.

Several industry consortia and standards organizations have been actively working on developing specifications and guidelines for chiplet power standardization. The JEDEC Solid State Technology Association has been at the forefront of these efforts, with its JC-42 Committee focusing on the development of standards for chiplet interfaces and power management. The committee's work includes defining power delivery architectures, voltage regulation specifications, and power state management protocols for chiplet-based systems.

In parallel, the Open Compute Project (OCP) has been driving standardization efforts through its Open Domain-Specific Architecture (ODSA) subproject. The ODSA working group has been developing specifications for chiplet-to-chiplet interfaces, including power management and distribution aspects. Their efforts have resulted in the creation of the Bunch of Wires (BoW) interface specification, which addresses power delivery and management for chiplet interconnects.

The IEEE has also been contributing to chiplet power standardization through its P2851 working group. This group is developing standards for power modeling and estimation in heterogeneous systems, including chiplet-based designs. Their work aims to provide a standardized framework for power analysis and optimization across different chiplet implementations.

Collaboration between industry leaders has been crucial in advancing chiplet power standardization. Companies such as Intel, AMD, and TSMC have been actively participating in various standardization initiatives, sharing their expertise and aligning their efforts to create interoperable solutions. These collaborations have led to the development of technologies like Advanced Interface Bus (AIB) and Universal Chiplet Interconnect Express (UCIe), which incorporate standardized power management features for chiplet-based systems.

The standardization efforts extend beyond electrical specifications to encompass thermal management aspects as well. Organizations like ASHRAE and SEMI have been working on developing guidelines for thermal design and management in chiplet-based systems, addressing the unique challenges posed by densely packed multi-chip modules.

As these standardization efforts continue to evolve, they are expected to play a crucial role in enabling the widespread adoption of chiplet-based architectures in transformative telecommunication systems. By providing a common framework for power management and distribution, these standards will facilitate interoperability, reduce design complexity, and accelerate innovation in the field of chiplet technology for next-generation telecommunication infrastructure.

Several industry consortia and standards organizations have been actively working on developing specifications and guidelines for chiplet power standardization. The JEDEC Solid State Technology Association has been at the forefront of these efforts, with its JC-42 Committee focusing on the development of standards for chiplet interfaces and power management. The committee's work includes defining power delivery architectures, voltage regulation specifications, and power state management protocols for chiplet-based systems.

In parallel, the Open Compute Project (OCP) has been driving standardization efforts through its Open Domain-Specific Architecture (ODSA) subproject. The ODSA working group has been developing specifications for chiplet-to-chiplet interfaces, including power management and distribution aspects. Their efforts have resulted in the creation of the Bunch of Wires (BoW) interface specification, which addresses power delivery and management for chiplet interconnects.

The IEEE has also been contributing to chiplet power standardization through its P2851 working group. This group is developing standards for power modeling and estimation in heterogeneous systems, including chiplet-based designs. Their work aims to provide a standardized framework for power analysis and optimization across different chiplet implementations.

Collaboration between industry leaders has been crucial in advancing chiplet power standardization. Companies such as Intel, AMD, and TSMC have been actively participating in various standardization initiatives, sharing their expertise and aligning their efforts to create interoperable solutions. These collaborations have led to the development of technologies like Advanced Interface Bus (AIB) and Universal Chiplet Interconnect Express (UCIe), which incorporate standardized power management features for chiplet-based systems.

The standardization efforts extend beyond electrical specifications to encompass thermal management aspects as well. Organizations like ASHRAE and SEMI have been working on developing guidelines for thermal design and management in chiplet-based systems, addressing the unique challenges posed by densely packed multi-chip modules.

As these standardization efforts continue to evolve, they are expected to play a crucial role in enabling the widespread adoption of chiplet-based architectures in transformative telecommunication systems. By providing a common framework for power management and distribution, these standards will facilitate interoperability, reduce design complexity, and accelerate innovation in the field of chiplet technology for next-generation telecommunication infrastructure.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!