How Chiplets Support High-Efficiency Power Management Solutions?

JUL 16, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Power Management Evolution and Objectives

Chiplet technology has revolutionized the semiconductor industry, offering a modular approach to chip design that addresses the challenges of traditional monolithic architectures. In the realm of power management, chiplets have emerged as a game-changing solution, enabling more efficient and flexible power distribution across complex systems-on-chip (SoCs).

The evolution of chiplet-based power management can be traced back to the early 2010s when the limitations of monolithic designs became increasingly apparent. As chip sizes grew and power demands escalated, designers faced significant challenges in maintaining uniform power delivery across large die areas. This led to the exploration of disaggregated architectures, where different functional blocks could be fabricated separately and integrated using advanced packaging technologies.

The primary objective of chiplet-based power management is to optimize power delivery and consumption in multi-die systems. By breaking down a large SoC into smaller, more manageable chiplets, designers can implement localized power management strategies tailored to the specific needs of each functional block. This granular approach allows for more precise control over voltage and current distribution, resulting in improved overall system efficiency.

Another key goal is to enhance scalability and flexibility in chip design. Chiplets enable mix-and-match capabilities, allowing manufacturers to combine different process nodes and intellectual property (IP) blocks to create customized solutions. This modularity extends to power management, where specialized power management integrated circuits (PMICs) can be integrated as separate chiplets, providing advanced power control features without the need for redesigning the entire SoC.

Reducing power consumption and improving thermal management are also critical objectives in chiplet-based designs. By optimizing power delivery on a per-chiplet basis, designers can minimize power losses associated with long-distance power distribution in large monolithic dies. This localized approach also facilitates more effective heat dissipation, as thermal hotspots can be more easily identified and managed at the chiplet level.

As the semiconductor industry continues to push the boundaries of performance and integration, chiplet technology is expected to play an increasingly important role in power management solutions. Future objectives include the development of even more sophisticated inter-chiplet power management techniques, such as dynamic power sharing and adaptive voltage scaling across multiple dies. Additionally, there is a growing focus on standardizing chiplet interfaces and power management protocols to facilitate broader adoption and interoperability across different vendors and platforms.

The evolution of chiplet-based power management represents a significant shift in how we approach the design and optimization of complex semiconductor systems. By leveraging the modularity and flexibility of chiplets, designers can create more efficient, scalable, and customizable power management solutions that address the ever-increasing demands of modern computing applications.

The evolution of chiplet-based power management can be traced back to the early 2010s when the limitations of monolithic designs became increasingly apparent. As chip sizes grew and power demands escalated, designers faced significant challenges in maintaining uniform power delivery across large die areas. This led to the exploration of disaggregated architectures, where different functional blocks could be fabricated separately and integrated using advanced packaging technologies.

The primary objective of chiplet-based power management is to optimize power delivery and consumption in multi-die systems. By breaking down a large SoC into smaller, more manageable chiplets, designers can implement localized power management strategies tailored to the specific needs of each functional block. This granular approach allows for more precise control over voltage and current distribution, resulting in improved overall system efficiency.

Another key goal is to enhance scalability and flexibility in chip design. Chiplets enable mix-and-match capabilities, allowing manufacturers to combine different process nodes and intellectual property (IP) blocks to create customized solutions. This modularity extends to power management, where specialized power management integrated circuits (PMICs) can be integrated as separate chiplets, providing advanced power control features without the need for redesigning the entire SoC.

Reducing power consumption and improving thermal management are also critical objectives in chiplet-based designs. By optimizing power delivery on a per-chiplet basis, designers can minimize power losses associated with long-distance power distribution in large monolithic dies. This localized approach also facilitates more effective heat dissipation, as thermal hotspots can be more easily identified and managed at the chiplet level.

As the semiconductor industry continues to push the boundaries of performance and integration, chiplet technology is expected to play an increasingly important role in power management solutions. Future objectives include the development of even more sophisticated inter-chiplet power management techniques, such as dynamic power sharing and adaptive voltage scaling across multiple dies. Additionally, there is a growing focus on standardizing chiplet interfaces and power management protocols to facilitate broader adoption and interoperability across different vendors and platforms.

The evolution of chiplet-based power management represents a significant shift in how we approach the design and optimization of complex semiconductor systems. By leveraging the modularity and flexibility of chiplets, designers can create more efficient, scalable, and customizable power management solutions that address the ever-increasing demands of modern computing applications.

Market Demand for Efficient Power Solutions

The demand for efficient power management solutions has been steadily increasing across various industries, driven by the growing complexity of electronic systems and the need for improved energy efficiency. Chiplets, as a modular approach to semiconductor design, are playing a crucial role in meeting this demand by enabling more sophisticated and flexible power management architectures.

In the consumer electronics sector, the proliferation of mobile devices, wearables, and Internet of Things (IoT) devices has created a significant market for power-efficient solutions. These devices require extended battery life and minimal heat generation, which can be achieved through advanced power management techniques enabled by chiplet technology. The ability to integrate specialized power management units (PMUs) as separate chiplets allows for more precise control over power distribution and consumption.

The data center and cloud computing industry is another major driver of demand for efficient power solutions. With the exponential growth in data processing and storage requirements, data centers are facing unprecedented challenges in managing power consumption and heat dissipation. Chiplet-based power management solutions offer the potential to significantly reduce energy costs and improve overall data center efficiency by allowing for more granular control over power delivery to different components.

In the automotive sector, the transition towards electric and autonomous vehicles has intensified the need for sophisticated power management systems. Chiplet technology enables the integration of advanced power control units that can efficiently manage the complex power requirements of electric drivetrains, battery management systems, and numerous sensors and processors in modern vehicles.

The industrial and manufacturing sectors are also experiencing increased demand for efficient power solutions as they move towards Industry 4.0 and smart manufacturing practices. Chiplet-based power management systems can provide the necessary flexibility and scalability to optimize energy consumption in complex industrial processes and automation systems.

Furthermore, the telecommunications industry, particularly with the rollout of 5G networks, requires highly efficient power management solutions to support the increased power demands of new infrastructure. Chiplet technology allows for the development of power-efficient base stations and network equipment that can handle the higher data rates and lower latency requirements of 5G while minimizing energy consumption.

The market for chiplet-based power management solutions is also being driven by regulatory pressures and sustainability initiatives. Governments and organizations worldwide are implementing stricter energy efficiency standards, pushing manufacturers to adopt more advanced power management technologies. Chiplets offer a pathway to meet these regulations while maintaining or improving product performance.

As the demand for efficient power solutions continues to grow across these diverse sectors, chiplet technology is poised to play an increasingly important role in addressing the complex power management challenges of modern electronic systems. The modular nature of chiplets allows for rapid innovation and customization, enabling manufacturers to quickly adapt to evolving market needs and energy efficiency requirements.

In the consumer electronics sector, the proliferation of mobile devices, wearables, and Internet of Things (IoT) devices has created a significant market for power-efficient solutions. These devices require extended battery life and minimal heat generation, which can be achieved through advanced power management techniques enabled by chiplet technology. The ability to integrate specialized power management units (PMUs) as separate chiplets allows for more precise control over power distribution and consumption.

The data center and cloud computing industry is another major driver of demand for efficient power solutions. With the exponential growth in data processing and storage requirements, data centers are facing unprecedented challenges in managing power consumption and heat dissipation. Chiplet-based power management solutions offer the potential to significantly reduce energy costs and improve overall data center efficiency by allowing for more granular control over power delivery to different components.

In the automotive sector, the transition towards electric and autonomous vehicles has intensified the need for sophisticated power management systems. Chiplet technology enables the integration of advanced power control units that can efficiently manage the complex power requirements of electric drivetrains, battery management systems, and numerous sensors and processors in modern vehicles.

The industrial and manufacturing sectors are also experiencing increased demand for efficient power solutions as they move towards Industry 4.0 and smart manufacturing practices. Chiplet-based power management systems can provide the necessary flexibility and scalability to optimize energy consumption in complex industrial processes and automation systems.

Furthermore, the telecommunications industry, particularly with the rollout of 5G networks, requires highly efficient power management solutions to support the increased power demands of new infrastructure. Chiplet technology allows for the development of power-efficient base stations and network equipment that can handle the higher data rates and lower latency requirements of 5G while minimizing energy consumption.

The market for chiplet-based power management solutions is also being driven by regulatory pressures and sustainability initiatives. Governments and organizations worldwide are implementing stricter energy efficiency standards, pushing manufacturers to adopt more advanced power management technologies. Chiplets offer a pathway to meet these regulations while maintaining or improving product performance.

As the demand for efficient power solutions continues to grow across these diverse sectors, chiplet technology is poised to play an increasingly important role in addressing the complex power management challenges of modern electronic systems. The modular nature of chiplets allows for rapid innovation and customization, enabling manufacturers to quickly adapt to evolving market needs and energy efficiency requirements.

Chiplet Technology State and Challenges

Chiplet technology has emerged as a promising solution for addressing the challenges of power management in modern semiconductor designs. The current state of chiplet technology is characterized by significant advancements in integration and efficiency, but it also faces several challenges that need to be overcome for widespread adoption.

One of the primary advantages of chiplet technology is its ability to support high-efficiency power management solutions. By disaggregating complex system-on-chip (SoC) designs into smaller, more manageable chiplets, designers can optimize power distribution and consumption across different functional blocks. This modular approach allows for more precise control over power domains, enabling dynamic power gating and voltage scaling at a granular level.

However, the implementation of chiplet-based power management solutions is not without its challenges. One of the key issues is the increased complexity of power delivery networks (PDNs) in multi-chiplet systems. The interconnects between chiplets introduce additional resistive and inductive losses, which can impact overall power efficiency. Designers must carefully consider the placement and routing of power distribution to minimize these losses and ensure stable voltage delivery across all chiplets.

Another significant challenge is the thermal management of chiplet-based systems. While chiplets allow for better heat dissipation compared to monolithic designs, the increased integration density can lead to localized hotspots. This requires advanced cooling solutions and thermal-aware design strategies to maintain optimal performance and reliability.

The heterogeneous nature of chiplet-based systems also presents challenges in power management. Different chiplets may have varying power requirements and operating voltages, necessitating sophisticated power management integrated circuits (PMICs) capable of handling multiple voltage domains and power states. This complexity extends to the software layer, where power management algorithms must be adapted to account for the distributed nature of chiplet architectures.

Standardization remains a critical challenge in the chiplet ecosystem. While initiatives like the Universal Chiplet Interconnect Express (UCIe) are making progress, the lack of widespread industry standards for chiplet interfaces and power management protocols hinders interoperability and limits the potential for mix-and-match chiplet designs from different vendors.

Despite these challenges, ongoing research and development efforts are driving innovations in chiplet-based power management. Advanced packaging technologies, such as 2.5D and 3D integration, are enabling more efficient power delivery and thermal management solutions. Additionally, the development of AI-driven power management algorithms is showing promise in optimizing energy efficiency across complex chiplet systems.

As the technology matures, we can expect to see further improvements in chiplet-based power management solutions, addressing current limitations and unlocking new possibilities for high-performance, energy-efficient semiconductor designs.

One of the primary advantages of chiplet technology is its ability to support high-efficiency power management solutions. By disaggregating complex system-on-chip (SoC) designs into smaller, more manageable chiplets, designers can optimize power distribution and consumption across different functional blocks. This modular approach allows for more precise control over power domains, enabling dynamic power gating and voltage scaling at a granular level.

However, the implementation of chiplet-based power management solutions is not without its challenges. One of the key issues is the increased complexity of power delivery networks (PDNs) in multi-chiplet systems. The interconnects between chiplets introduce additional resistive and inductive losses, which can impact overall power efficiency. Designers must carefully consider the placement and routing of power distribution to minimize these losses and ensure stable voltage delivery across all chiplets.

Another significant challenge is the thermal management of chiplet-based systems. While chiplets allow for better heat dissipation compared to monolithic designs, the increased integration density can lead to localized hotspots. This requires advanced cooling solutions and thermal-aware design strategies to maintain optimal performance and reliability.

The heterogeneous nature of chiplet-based systems also presents challenges in power management. Different chiplets may have varying power requirements and operating voltages, necessitating sophisticated power management integrated circuits (PMICs) capable of handling multiple voltage domains and power states. This complexity extends to the software layer, where power management algorithms must be adapted to account for the distributed nature of chiplet architectures.

Standardization remains a critical challenge in the chiplet ecosystem. While initiatives like the Universal Chiplet Interconnect Express (UCIe) are making progress, the lack of widespread industry standards for chiplet interfaces and power management protocols hinders interoperability and limits the potential for mix-and-match chiplet designs from different vendors.

Despite these challenges, ongoing research and development efforts are driving innovations in chiplet-based power management. Advanced packaging technologies, such as 2.5D and 3D integration, are enabling more efficient power delivery and thermal management solutions. Additionally, the development of AI-driven power management algorithms is showing promise in optimizing energy efficiency across complex chiplet systems.

As the technology matures, we can expect to see further improvements in chiplet-based power management solutions, addressing current limitations and unlocking new possibilities for high-performance, energy-efficient semiconductor designs.

Current Chiplet-based Power Solutions

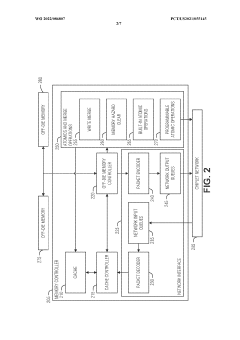

01 Dynamic power management for chiplets

Implementing dynamic power management techniques specifically for chiplet-based architectures. This involves real-time monitoring and adjustment of power consumption in individual chiplets based on workload and performance requirements, optimizing overall system efficiency.- Dynamic power management for chiplets: Implementing dynamic power management techniques specifically for chiplet-based architectures. This involves real-time monitoring and adjustment of power consumption in individual chiplets based on workload and performance requirements, optimizing overall system efficiency.

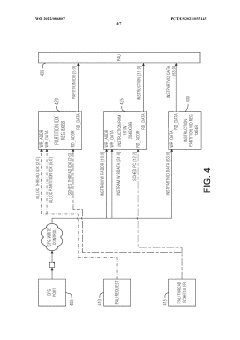

- Inter-chiplet power distribution and control: Developing efficient methods for distributing and controlling power between multiple chiplets in a system. This includes intelligent power routing, load balancing, and communication protocols to ensure optimal power utilization across the entire chiplet ecosystem.

- Thermal management for chiplet efficiency: Integrating advanced thermal management solutions specifically designed for chiplet architectures. This involves innovative cooling techniques, thermal-aware task scheduling, and temperature-based power gating to maintain optimal operating conditions and enhance overall power efficiency.

- Voltage and frequency scaling in chiplet designs: Implementing sophisticated voltage and frequency scaling techniques tailored for chiplet-based systems. This includes per-chiplet dynamic voltage and frequency scaling (DVFS), adaptive voltage scaling, and fine-grained power states to maximize energy efficiency while meeting performance targets.

- Power-aware interconnect and communication: Developing energy-efficient interconnect technologies and communication protocols specifically for chiplet-to-chiplet and chiplet-to-system interactions. This focuses on reducing power consumption in data transfer, optimizing signaling techniques, and implementing power-aware routing strategies.

02 Inter-chiplet power distribution and control

Developing efficient methods for distributing and controlling power between multiple chiplets in a system. This includes designing power delivery networks, implementing voltage regulators, and coordinating power states across chiplets to minimize energy waste and optimize performance.Expand Specific Solutions03 Thermal management for chiplet-based systems

Creating innovative thermal management solutions tailored for chiplet architectures. This involves designing heat spreaders, implementing advanced cooling techniques, and developing thermal-aware power management strategies to maintain optimal operating temperatures across multiple chiplets.Expand Specific Solutions04 AI-driven power optimization for chiplets

Utilizing artificial intelligence and machine learning algorithms to optimize power management in chiplet-based systems. This includes predictive power allocation, adaptive voltage and frequency scaling, and intelligent workload distribution among chiplets to maximize energy efficiency.Expand Specific Solutions05 Heterogeneous chiplet integration for power efficiency

Designing and integrating heterogeneous chiplets with varying power characteristics and capabilities. This approach allows for optimized power consumption by utilizing specialized chiplets for specific tasks, enabling fine-grained power management across the system.Expand Specific Solutions

Key Players in Chiplet Power Management

The chiplet technology market for high-efficiency power management solutions is in a growth phase, driven by increasing demand for more efficient and compact computing systems. The market size is expanding rapidly, with major players like Intel, AMD, and Qualcomm investing heavily in chiplet-based architectures. Technologically, chiplets are maturing, allowing for more modular and flexible power management designs. Companies such as Micron, VIA Technologies, and IBM are also exploring chiplet integration for improved power efficiency. While still evolving, the technology shows promise in addressing power constraints in advanced computing systems, with ongoing research and development efforts across the industry.

Intel Corp.

Technical Solution: Intel's chiplet-based approach for power management involves their Foveros 3D packaging technology. This allows for the integration of multiple chiplets, including power management ICs (PMICs), in a single package. Their design incorporates dedicated chiplets for voltage regulation and power delivery, which can be optimized independently from the main processing units. This modular approach enables fine-grained power control, with each chiplet potentially operating at different voltage and frequency levels[1][3]. Intel's implementation includes advanced power gating techniques and dynamic voltage and frequency scaling (DVFS) at the chiplet level, allowing for more efficient power distribution and thermal management across the entire package[2].

Strengths: Highly customizable power solutions for different chiplets, improved thermal management, and potential for better overall system efficiency. Weaknesses: Increased complexity in system design and potential for higher manufacturing costs due to advanced packaging requirements.

Advanced Micro Devices, Inc.

Technical Solution: AMD's chiplet-based power management strategy centers around their Infinity Fabric interconnect technology. This approach allows for the integration of multiple chiplets, each potentially having its own power domain. AMD implements a distributed power management system where each chiplet can have its own voltage regulators and power control units. This enables precise control over power states and clock frequencies for individual chiplets[4]. AMD's design also incorporates advanced power gating techniques and per-chiplet DVFS capabilities. Their latest implementations include AI-enhanced power management algorithms that can predict workload patterns and optimize power distribution across chiplets in real-time[5].

Strengths: Scalable architecture allowing for efficient power management across different product tiers, potential for significant power savings in multi-chiplet designs. Weaknesses: Complexity in managing power across multiple chiplets, potential for increased latency due to inter-chiplet communication.

Innovative Power Management Chiplet Designs

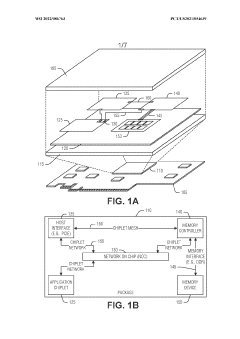

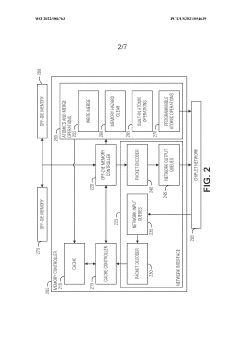

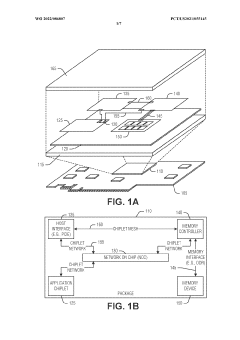

Thread scheduling control and memory splitting in a barrel processor

PatentWO2022086763A1

Innovation

- Implementing a thread scheduling control mechanism that organizes threads into separate groups, each with its own memory device, and alternates between groups for read and write access to reduce memory contention, allowing threads to progress through the pipeline more efficiently and reducing power draw.

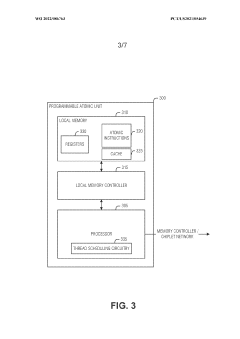

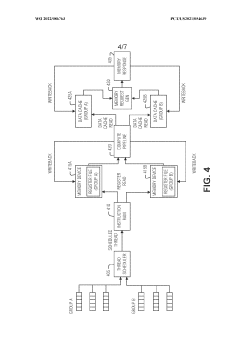

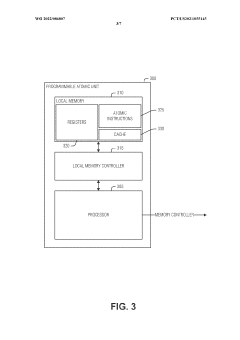

On-demand programmable atomic kernel loading

PatentWO2022086807A1

Innovation

- Implementing an on-demand mechanism for loading PAO kernels, where PAUs register for potential use and reserve space, loading the kernel only when requested, and signaling a trap to initiate kernel transfer when needed.

Thermal Management in Chiplet Systems

Thermal management is a critical aspect of chiplet-based systems, as the increased integration density and power consumption of these advanced architectures pose significant challenges for heat dissipation. The modular nature of chiplets allows for more efficient thermal management strategies compared to monolithic designs, but it also introduces unique thermal considerations.

One of the primary advantages of chiplet-based designs in thermal management is the ability to distribute heat sources more evenly across the package. By separating different functional units into individual chiplets, designers can optimize the placement of high-power components to minimize hot spots and improve overall thermal performance. This approach enables more effective heat spreading and can potentially reduce the peak temperature of the system.

Chiplet architectures also offer greater flexibility in implementing advanced cooling solutions. The interposer or substrate used to connect chiplets can be designed with integrated cooling channels or heat spreaders, providing direct cooling to individual chiplets. This targeted cooling approach can be more efficient than traditional methods used in monolithic designs, as it allows for customized thermal management solutions for different chiplets based on their specific power and thermal requirements.

The use of heterogeneous integration in chiplet systems presents both opportunities and challenges for thermal management. While it allows for the optimization of each chiplet's process technology and thermal characteristics, it also introduces thermal interfaces between chiplets and the package substrate. These interfaces can create thermal bottlenecks if not properly managed. Advanced thermal interface materials (TIMs) and novel bonding techniques are being developed to address these challenges and improve heat transfer across chiplet boundaries.

Another important consideration in chiplet thermal management is the impact of power delivery networks (PDNs) on heat generation and distribution. The modular nature of chiplets requires careful design of PDNs to ensure efficient power delivery to each chiplet while minimizing resistive losses and associated heat generation. Advanced packaging technologies, such as embedded bridge interconnects and through-silicon vias (TSVs), play a crucial role in optimizing PDNs for chiplet systems and contributing to overall thermal management.

As chiplet designs continue to evolve, new thermal management techniques are being explored to address the increasing power densities and thermal challenges. These include the use of liquid cooling solutions directly integrated into the chiplet package, advanced heat spreading materials, and dynamic thermal management strategies that leverage the modularity of chiplet architectures to optimize performance and power consumption based on real-time thermal conditions.

One of the primary advantages of chiplet-based designs in thermal management is the ability to distribute heat sources more evenly across the package. By separating different functional units into individual chiplets, designers can optimize the placement of high-power components to minimize hot spots and improve overall thermal performance. This approach enables more effective heat spreading and can potentially reduce the peak temperature of the system.

Chiplet architectures also offer greater flexibility in implementing advanced cooling solutions. The interposer or substrate used to connect chiplets can be designed with integrated cooling channels or heat spreaders, providing direct cooling to individual chiplets. This targeted cooling approach can be more efficient than traditional methods used in monolithic designs, as it allows for customized thermal management solutions for different chiplets based on their specific power and thermal requirements.

The use of heterogeneous integration in chiplet systems presents both opportunities and challenges for thermal management. While it allows for the optimization of each chiplet's process technology and thermal characteristics, it also introduces thermal interfaces between chiplets and the package substrate. These interfaces can create thermal bottlenecks if not properly managed. Advanced thermal interface materials (TIMs) and novel bonding techniques are being developed to address these challenges and improve heat transfer across chiplet boundaries.

Another important consideration in chiplet thermal management is the impact of power delivery networks (PDNs) on heat generation and distribution. The modular nature of chiplets requires careful design of PDNs to ensure efficient power delivery to each chiplet while minimizing resistive losses and associated heat generation. Advanced packaging technologies, such as embedded bridge interconnects and through-silicon vias (TSVs), play a crucial role in optimizing PDNs for chiplet systems and contributing to overall thermal management.

As chiplet designs continue to evolve, new thermal management techniques are being explored to address the increasing power densities and thermal challenges. These include the use of liquid cooling solutions directly integrated into the chiplet package, advanced heat spreading materials, and dynamic thermal management strategies that leverage the modularity of chiplet architectures to optimize performance and power consumption based on real-time thermal conditions.

Standardization Efforts for Chiplet Integration

The standardization efforts for chiplet integration are crucial for enabling high-efficiency power management solutions in the semiconductor industry. These efforts aim to establish common protocols, interfaces, and design methodologies that facilitate seamless integration of diverse chiplets from different manufacturers.

One of the key standardization initiatives is the Universal Chiplet Interconnect Express (UCIe), which defines a die-to-die interconnect standard for chiplet-based designs. UCIe provides a unified approach to chiplet integration, allowing for improved interoperability and reduced design complexity. This standardization effort is particularly beneficial for power management solutions, as it enables more efficient communication between power-related chiplets and other system components.

Another significant standardization effort is the Advanced Interface Bus (AIB) consortium, which focuses on developing open-source interconnect standards for chiplet-to-chiplet communication. AIB standards contribute to the development of modular power management solutions by providing a common framework for integrating power-related chiplets with other functional blocks.

The Open Compute Project (OCP) has also been instrumental in driving standardization efforts for chiplet integration. OCP's Open Domain-Specific Architecture (ODSA) workgroup is developing open architectures and standards for chiplet-based designs, including power management considerations. These efforts aim to create a more open and collaborative ecosystem for chiplet integration, fostering innovation in power-efficient solutions.

Standardization efforts extend to packaging technologies as well. The Joint Electron Device Engineering Council (JEDEC) has been working on standards for advanced packaging technologies, such as 2.5D and 3D integration, which are critical for efficient chiplet-based power management solutions. These standards help ensure compatibility and reliability in multi-chip module designs.

Furthermore, industry consortia like the CHIPS Alliance are focusing on open-source hardware design and verification tools that support chiplet integration. These efforts contribute to the development of standardized design methodologies and tools that can be used to create more efficient power management solutions using chiplet technology.

The IEEE has also been active in this space, developing standards for test and verification of chiplet-based systems. These standards are essential for ensuring the reliability and performance of integrated power management solutions in chiplet designs.

As standardization efforts continue to evolve, they are expected to drive greater adoption of chiplet-based architectures in power management applications. This will lead to more modular, scalable, and efficient power solutions that can be easily integrated into a wide range of electronic systems.

One of the key standardization initiatives is the Universal Chiplet Interconnect Express (UCIe), which defines a die-to-die interconnect standard for chiplet-based designs. UCIe provides a unified approach to chiplet integration, allowing for improved interoperability and reduced design complexity. This standardization effort is particularly beneficial for power management solutions, as it enables more efficient communication between power-related chiplets and other system components.

Another significant standardization effort is the Advanced Interface Bus (AIB) consortium, which focuses on developing open-source interconnect standards for chiplet-to-chiplet communication. AIB standards contribute to the development of modular power management solutions by providing a common framework for integrating power-related chiplets with other functional blocks.

The Open Compute Project (OCP) has also been instrumental in driving standardization efforts for chiplet integration. OCP's Open Domain-Specific Architecture (ODSA) workgroup is developing open architectures and standards for chiplet-based designs, including power management considerations. These efforts aim to create a more open and collaborative ecosystem for chiplet integration, fostering innovation in power-efficient solutions.

Standardization efforts extend to packaging technologies as well. The Joint Electron Device Engineering Council (JEDEC) has been working on standards for advanced packaging technologies, such as 2.5D and 3D integration, which are critical for efficient chiplet-based power management solutions. These standards help ensure compatibility and reliability in multi-chip module designs.

Furthermore, industry consortia like the CHIPS Alliance are focusing on open-source hardware design and verification tools that support chiplet integration. These efforts contribute to the development of standardized design methodologies and tools that can be used to create more efficient power management solutions using chiplet technology.

The IEEE has also been active in this space, developing standards for test and verification of chiplet-based systems. These standards are essential for ensuring the reliability and performance of integrated power management solutions in chiplet designs.

As standardization efforts continue to evolve, they are expected to drive greater adoption of chiplet-based architectures in power management applications. This will lead to more modular, scalable, and efficient power solutions that can be easily integrated into a wide range of electronic systems.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!