Exploring Chiplet Potential in Multithread Execution Models

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Tech Evolution

The evolution of chiplet technology represents a significant paradigm shift in the semiconductor industry, driven by the need to overcome the limitations of traditional monolithic chip designs. This progression can be traced through several key stages, each marked by technological advancements and innovative approaches to chip architecture.

In the early 2000s, the concept of chiplets began to emerge as a potential solution to the challenges posed by Moore's Law. As transistor scaling became increasingly difficult and expensive, researchers and engineers started exploring modular chip designs. This initial phase focused on developing the fundamental principles of chiplet-based architectures, including the integration of multiple dies on a single package.

The mid-2010s saw a surge in chiplet research and development, with major semiconductor companies investing heavily in this technology. During this period, significant advancements were made in die-to-die interconnect technologies, packaging techniques, and system-level integration. The introduction of 2.5D and 3D packaging technologies played a crucial role in enabling more efficient chiplet designs.

By 2018, the first commercial chiplet-based products began to enter the market, demonstrating the viability of this approach. These early implementations primarily focused on combining different types of processors or integrating memory with compute elements. The success of these products paved the way for broader adoption of chiplet technology across various semiconductor applications.

In recent years, the focus has shifted towards optimizing chiplet designs for specific use cases, including high-performance computing, artificial intelligence, and edge computing. This has led to the development of more sophisticated interconnect technologies, such as silicon interposers and advanced packaging solutions, which enable higher bandwidth and lower latency communication between chiplets.

The current phase of chiplet evolution is characterized by efforts to standardize chiplet interfaces and protocols. Industry consortia and standardization bodies are working to establish common specifications, which will facilitate interoperability between chiplets from different manufacturers. This standardization is crucial for creating a more diverse and competitive chiplet ecosystem.

Looking ahead, the future of chiplet technology is likely to involve further miniaturization, increased integration of heterogeneous components, and the development of more advanced packaging technologies. As multithread execution models become increasingly complex, chiplets are expected to play a pivotal role in enabling more efficient and scalable computing architectures.

In the early 2000s, the concept of chiplets began to emerge as a potential solution to the challenges posed by Moore's Law. As transistor scaling became increasingly difficult and expensive, researchers and engineers started exploring modular chip designs. This initial phase focused on developing the fundamental principles of chiplet-based architectures, including the integration of multiple dies on a single package.

The mid-2010s saw a surge in chiplet research and development, with major semiconductor companies investing heavily in this technology. During this period, significant advancements were made in die-to-die interconnect technologies, packaging techniques, and system-level integration. The introduction of 2.5D and 3D packaging technologies played a crucial role in enabling more efficient chiplet designs.

By 2018, the first commercial chiplet-based products began to enter the market, demonstrating the viability of this approach. These early implementations primarily focused on combining different types of processors or integrating memory with compute elements. The success of these products paved the way for broader adoption of chiplet technology across various semiconductor applications.

In recent years, the focus has shifted towards optimizing chiplet designs for specific use cases, including high-performance computing, artificial intelligence, and edge computing. This has led to the development of more sophisticated interconnect technologies, such as silicon interposers and advanced packaging solutions, which enable higher bandwidth and lower latency communication between chiplets.

The current phase of chiplet evolution is characterized by efforts to standardize chiplet interfaces and protocols. Industry consortia and standardization bodies are working to establish common specifications, which will facilitate interoperability between chiplets from different manufacturers. This standardization is crucial for creating a more diverse and competitive chiplet ecosystem.

Looking ahead, the future of chiplet technology is likely to involve further miniaturization, increased integration of heterogeneous components, and the development of more advanced packaging technologies. As multithread execution models become increasingly complex, chiplets are expected to play a pivotal role in enabling more efficient and scalable computing architectures.

Market Demand Analysis

The market demand for chiplet technology in multithread execution models has been steadily growing, driven by the increasing complexity of modern computing systems and the need for more efficient, scalable, and cost-effective solutions. As traditional monolithic chip designs approach their physical limits, chiplets offer a promising alternative that allows for greater flexibility and performance optimization.

The global semiconductor market, which forms the backdrop for chiplet adoption, is projected to reach significant growth in the coming years. This growth is largely fueled by the rising demand for high-performance computing in various sectors, including data centers, artificial intelligence, 5G networks, and edge computing. These applications require advanced processing capabilities that can handle massive parallel workloads efficiently, making chiplet-based multithread execution models particularly attractive.

In the data center segment, where multithread execution is crucial for handling concurrent tasks and maximizing resource utilization, there is a strong demand for chiplet solutions. Cloud service providers and enterprise data centers are constantly seeking ways to improve performance per watt and reduce total cost of ownership. Chiplet-based designs offer the potential to address these needs by allowing for more optimized combinations of processing elements and improved thermal management.

The artificial intelligence and machine learning market is another key driver for chiplet adoption in multithread execution models. As AI workloads become increasingly complex and data-intensive, there is a growing need for specialized processing units that can efficiently handle parallel computations. Chiplets enable the integration of diverse processing elements, such as CPUs, GPUs, and AI accelerators, on a single package, providing the flexibility to tailor solutions for specific AI applications.

In the telecommunications sector, the rollout of 5G networks and the anticipated move towards 6G is creating demand for advanced processing capabilities at the network edge. Chiplet-based designs can offer the necessary performance and energy efficiency for edge computing devices, which often require multithreaded processing to handle diverse workloads in real-time.

The automotive industry is also showing interest in chiplet technology for advanced driver assistance systems (ADAS) and autonomous vehicles. These applications require high-performance, low-latency processing of multiple data streams simultaneously, making chiplet-based multithread execution models an attractive option.

Despite the growing demand, challenges remain in the widespread adoption of chiplet technology. Interoperability standards, packaging technologies, and design tools are still evolving, which can impact time-to-market and development costs. However, industry collaborations and standardization efforts are underway to address these challenges and accelerate market adoption.

The global semiconductor market, which forms the backdrop for chiplet adoption, is projected to reach significant growth in the coming years. This growth is largely fueled by the rising demand for high-performance computing in various sectors, including data centers, artificial intelligence, 5G networks, and edge computing. These applications require advanced processing capabilities that can handle massive parallel workloads efficiently, making chiplet-based multithread execution models particularly attractive.

In the data center segment, where multithread execution is crucial for handling concurrent tasks and maximizing resource utilization, there is a strong demand for chiplet solutions. Cloud service providers and enterprise data centers are constantly seeking ways to improve performance per watt and reduce total cost of ownership. Chiplet-based designs offer the potential to address these needs by allowing for more optimized combinations of processing elements and improved thermal management.

The artificial intelligence and machine learning market is another key driver for chiplet adoption in multithread execution models. As AI workloads become increasingly complex and data-intensive, there is a growing need for specialized processing units that can efficiently handle parallel computations. Chiplets enable the integration of diverse processing elements, such as CPUs, GPUs, and AI accelerators, on a single package, providing the flexibility to tailor solutions for specific AI applications.

In the telecommunications sector, the rollout of 5G networks and the anticipated move towards 6G is creating demand for advanced processing capabilities at the network edge. Chiplet-based designs can offer the necessary performance and energy efficiency for edge computing devices, which often require multithreaded processing to handle diverse workloads in real-time.

The automotive industry is also showing interest in chiplet technology for advanced driver assistance systems (ADAS) and autonomous vehicles. These applications require high-performance, low-latency processing of multiple data streams simultaneously, making chiplet-based multithread execution models an attractive option.

Despite the growing demand, challenges remain in the widespread adoption of chiplet technology. Interoperability standards, packaging technologies, and design tools are still evolving, which can impact time-to-market and development costs. However, industry collaborations and standardization efforts are underway to address these challenges and accelerate market adoption.

Chiplet Challenges

While chiplets offer promising solutions for multithread execution models, they also present several significant challenges that need to be addressed. One of the primary obstacles is the interconnect bottleneck between chiplets. As the number of chiplets increases, the communication bandwidth and latency between them become critical factors affecting overall system performance. Designing efficient and scalable interconnect architectures that can handle the high-speed data transfer requirements of multithreaded applications is a complex task.

Another challenge lies in the thermal management of chiplet-based systems. With multiple chiplets packed closely together, heat dissipation becomes a crucial concern. Uneven heat distribution across chiplets can lead to thermal hotspots, potentially causing performance degradation or reliability issues. Developing advanced cooling solutions and thermal management techniques specifically tailored for chiplet architectures is essential to ensure optimal performance and longevity of the system.

Power management presents yet another hurdle in chiplet-based designs. Each chiplet may have different power requirements and characteristics, making it challenging to implement efficient power delivery and distribution across the entire system. Balancing power consumption among chiplets while maintaining overall system performance is a delicate task that requires sophisticated power management strategies.

The integration and packaging of chiplets also pose significant challenges. As chiplets become smaller and more numerous, the complexity of assembling them into a cohesive system increases. Advanced packaging technologies, such as 2.5D and 3D integration, are required to achieve high-density interconnects between chiplets. However, these technologies come with their own set of challenges, including manufacturing complexity, yield issues, and cost considerations.

Memory coherence and data consistency across chiplets are critical aspects that need careful consideration in multithread execution models. Ensuring efficient and consistent memory access across multiple chiplets while maintaining cache coherency can be complex, especially as the number of chiplets and threads increases. Developing scalable coherence protocols and memory hierarchies that can effectively manage data across chiplets is crucial for achieving optimal performance in multithreaded applications.

Lastly, the software ecosystem and programming models for chiplet-based systems present challenges in terms of optimization and utilization. Existing software may not be optimized to take full advantage of the chiplet architecture, requiring significant efforts in software development and optimization. Creating programming models and tools that can effectively leverage the parallelism and unique characteristics of chiplet-based systems is essential for realizing their full potential in multithread execution models.

Another challenge lies in the thermal management of chiplet-based systems. With multiple chiplets packed closely together, heat dissipation becomes a crucial concern. Uneven heat distribution across chiplets can lead to thermal hotspots, potentially causing performance degradation or reliability issues. Developing advanced cooling solutions and thermal management techniques specifically tailored for chiplet architectures is essential to ensure optimal performance and longevity of the system.

Power management presents yet another hurdle in chiplet-based designs. Each chiplet may have different power requirements and characteristics, making it challenging to implement efficient power delivery and distribution across the entire system. Balancing power consumption among chiplets while maintaining overall system performance is a delicate task that requires sophisticated power management strategies.

The integration and packaging of chiplets also pose significant challenges. As chiplets become smaller and more numerous, the complexity of assembling them into a cohesive system increases. Advanced packaging technologies, such as 2.5D and 3D integration, are required to achieve high-density interconnects between chiplets. However, these technologies come with their own set of challenges, including manufacturing complexity, yield issues, and cost considerations.

Memory coherence and data consistency across chiplets are critical aspects that need careful consideration in multithread execution models. Ensuring efficient and consistent memory access across multiple chiplets while maintaining cache coherency can be complex, especially as the number of chiplets and threads increases. Developing scalable coherence protocols and memory hierarchies that can effectively manage data across chiplets is crucial for achieving optimal performance in multithreaded applications.

Lastly, the software ecosystem and programming models for chiplet-based systems present challenges in terms of optimization and utilization. Existing software may not be optimized to take full advantage of the chiplet architecture, requiring significant efforts in software development and optimization. Creating programming models and tools that can effectively leverage the parallelism and unique characteristics of chiplet-based systems is essential for realizing their full potential in multithread execution models.

Current Chiplet Solutions

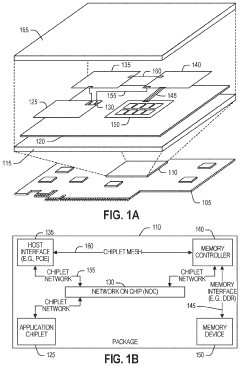

01 Chiplet-based multithread execution architecture

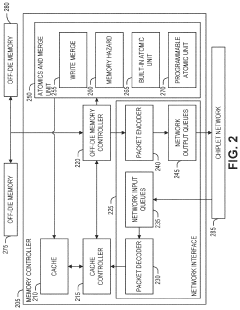

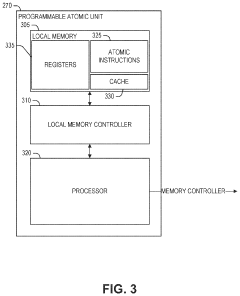

This approach involves designing processor architectures using multiple chiplets to enable efficient multithread execution. The chiplet-based design allows for better scalability, improved performance, and reduced power consumption in multi-core processors. Each chiplet can contain multiple cores capable of executing threads independently, enhancing overall system performance.- Chiplet-based multithread execution architecture: This approach involves designing processors using multiple chiplets, each capable of handling multiple threads. The architecture allows for efficient distribution of workloads across different chiplets, improving overall performance and scalability. It enables better utilization of resources and can lead to improved energy efficiency in multi-core systems.

- Thread scheduling and management in chiplet systems: Efficient thread scheduling and management techniques are crucial for optimizing performance in chiplet-based multithread systems. This includes load balancing across chiplets, prioritizing threads based on various factors, and dynamically adjusting thread allocation to maximize resource utilization and minimize latency.

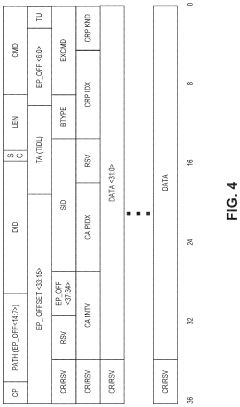

- Inter-chiplet communication for multithread coordination: Effective communication between chiplets is essential for coordinating multithread execution. This involves designing low-latency, high-bandwidth interconnects and protocols that allow for efficient data exchange and synchronization between threads running on different chiplets. Optimizing this communication is key to achieving high performance in chiplet-based systems.

- Power management in chiplet multithread systems: Implementing sophisticated power management techniques in chiplet-based multithread systems is crucial for optimizing energy efficiency. This includes dynamic voltage and frequency scaling, selective power-gating of idle chiplets or cores, and intelligent thread migration to balance workload and thermal distribution across the system.

- Cache coherency in chiplet multithread architectures: Maintaining cache coherency across multiple chiplets in a multithread execution environment is challenging but essential for system correctness and performance. This involves implementing efficient coherency protocols, designing appropriate cache hierarchies, and optimizing data sharing mechanisms between threads on different chiplets.

02 Thread scheduling and load balancing across chiplets

Efficient thread scheduling and load balancing mechanisms are implemented to distribute workloads across multiple chiplets. These techniques ensure optimal utilization of available resources, minimize inter-chiplet communication overhead, and improve overall system performance. Advanced algorithms are used to dynamically allocate threads to chiplets based on factors such as workload characteristics and thermal constraints.Expand Specific Solutions03 Inter-chiplet communication for multithread coordination

Specialized interconnect technologies and protocols are developed to facilitate efficient communication between chiplets for multithread coordination. These communication mechanisms enable low-latency data exchange, synchronization, and coherence maintenance across chiplets, ensuring seamless execution of multithreaded applications on chiplet-based architectures.Expand Specific Solutions04 Power management and thermal optimization for chiplet-based multithread execution

Advanced power management and thermal optimization techniques are implemented to ensure efficient operation of chiplet-based multithread execution systems. These techniques include dynamic voltage and frequency scaling, power gating, and intelligent thermal management across chiplets to maximize performance while maintaining power efficiency and thermal stability.Expand Specific Solutions05 Memory hierarchy and cache coherence in chiplet-based multithread systems

Specialized memory hierarchies and cache coherence protocols are designed to support efficient multithread execution in chiplet-based architectures. These innovations include distributed shared caches, non-uniform memory access (NUMA) optimizations, and scalable coherence mechanisms to minimize memory access latencies and ensure data consistency across chiplets.Expand Specific Solutions

Key Industry Players

The exploration of chiplet potential in multithread execution models is currently in an early development stage, with the market showing promising growth potential. The technology is gaining traction due to its ability to enhance performance and efficiency in multi-core processors. Key players like Intel, AMD, and IBM are investing heavily in chiplet technology, with varying levels of maturity in their implementations. Smaller companies and research institutions are also contributing to the field, indicating a competitive and diverse landscape. As the technology evolves, we can expect to see increased adoption across different computing sectors, potentially reshaping the semiconductor industry's approach to processor design and manufacturing.

Intel Corp.

Technical Solution: Intel's approach to chiplet technology in multithread execution models focuses on their Foveros 3D packaging technology. This allows for the vertical stacking of chiplets, enabling higher performance and lower power consumption[1]. Their latest Meteor Lake processors utilize this technology, combining compute, graphics, and AI tiles[2]. Intel's implementation includes advanced interconnect technologies like EMIB (Embedded Multi-die Interconnect Bridge) for high-bandwidth, low-latency communication between chiplets[3]. This architecture allows for more efficient distribution of workloads across multiple cores, enhancing multithreading capabilities.

Strengths: Advanced 3D packaging, high integration density, and flexibility in combining different process nodes. Weaknesses: Complexity in thermal management and potential yield issues in 3D stacking.

International Business Machines Corp.

Technical Solution: IBM's approach to chiplet technology in multithread execution models is exemplified by their Power10 processor architecture. This design incorporates multiple chiplets interconnected using advanced packaging technologies[4]. IBM utilizes a modular approach, allowing for scalable performance by combining multiple chiplets. The Power10 architecture supports SMT8 (Simultaneous Multi-Threading with 8 threads per core), significantly enhancing multithreaded performance[5]. IBM's implementation also includes advanced memory subsystems and interconnects to support high-bandwidth, low-latency communication between chiplets, crucial for efficient multithread execution.

Strengths: High thread count per core, scalable performance, and advanced memory subsystems. Weaknesses: Limited market presence outside of enterprise and high-performance computing sectors.

Chiplet Innovations

Method of executing programmable atomic unit resources within a multi-process system

PatentActiveUS12020062B2

Innovation

- A method is disclosed that involves determining a unique identifier for a programmable atomic transaction within a process, using a mapping table to generate a system-wide identifier, and issuing requests to a memory controller to perform the transaction, allowing for efficient execution and response handling through a programmable atomic unit.

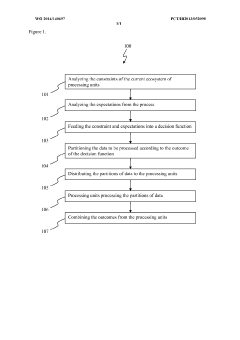

A method for data partitioning and assignment

PatentWO2014140697A1

Innovation

- A method that analyzes the constraints and capabilities of the processing units, combined with user expectations, to determine the optimal partitioning and assignment of data across various processors, using a decision function that can adapt to changing conditions and learn from input data.

Chiplet Ecosystem

The chiplet ecosystem has emerged as a transformative force in the semiconductor industry, revolutionizing the way complex integrated circuits are designed and manufactured. This ecosystem encompasses a wide range of technologies, methodologies, and stakeholders that collectively enable the development and production of chiplet-based systems. At its core, the chiplet approach involves disaggregating large monolithic chips into smaller, more manageable functional blocks that can be manufactured separately and then integrated using advanced packaging technologies.

The foundation of the chiplet ecosystem lies in the development of standardized interfaces and protocols that allow seamless communication between different chiplets. These standards, such as Universal Chiplet Interconnect Express (UCIe) and Advanced Interface Bus (AIB), facilitate interoperability and enable the creation of modular, mix-and-match chip designs. This standardization has fostered a more open and collaborative environment within the semiconductor industry, allowing companies to specialize in specific chiplet designs while leveraging the expertise of others.

Manufacturing processes play a crucial role in the chiplet ecosystem. Advanced packaging technologies, including 2.5D and 3D integration, are essential for connecting multiple chiplets into a single functional unit. These packaging innovations have driven the development of new materials, equipment, and processes to address the unique challenges of chiplet integration, such as thermal management and signal integrity.

The chiplet ecosystem has also given rise to new business models and supply chain dynamics. Fabless companies can now focus on designing specialized chiplets without the need for massive investments in manufacturing facilities. Meanwhile, foundries and outsourced semiconductor assembly and test (OSAT) providers have expanded their offerings to include advanced packaging services, creating a more diverse and flexible semiconductor value chain.

Software and design tools form another critical component of the chiplet ecosystem. Electronic design automation (EDA) companies have developed new tools and methodologies to support chiplet-based design flows, addressing challenges such as system-level optimization, die-to-die interface design, and multi-chiplet verification. These advancements have enabled designers to fully leverage the potential of chiplet architectures in creating complex, high-performance systems.

As the chiplet ecosystem continues to evolve, it is driving innovation across the entire semiconductor industry. From enabling more efficient and cost-effective chip designs to fostering greater collaboration and specialization among industry players, the chiplet approach is reshaping the landscape of integrated circuit development and manufacturing. This ecosystem's growth and maturation will play a pivotal role in addressing the increasing demands for performance, power efficiency, and scalability in next-generation computing systems.

The foundation of the chiplet ecosystem lies in the development of standardized interfaces and protocols that allow seamless communication between different chiplets. These standards, such as Universal Chiplet Interconnect Express (UCIe) and Advanced Interface Bus (AIB), facilitate interoperability and enable the creation of modular, mix-and-match chip designs. This standardization has fostered a more open and collaborative environment within the semiconductor industry, allowing companies to specialize in specific chiplet designs while leveraging the expertise of others.

Manufacturing processes play a crucial role in the chiplet ecosystem. Advanced packaging technologies, including 2.5D and 3D integration, are essential for connecting multiple chiplets into a single functional unit. These packaging innovations have driven the development of new materials, equipment, and processes to address the unique challenges of chiplet integration, such as thermal management and signal integrity.

The chiplet ecosystem has also given rise to new business models and supply chain dynamics. Fabless companies can now focus on designing specialized chiplets without the need for massive investments in manufacturing facilities. Meanwhile, foundries and outsourced semiconductor assembly and test (OSAT) providers have expanded their offerings to include advanced packaging services, creating a more diverse and flexible semiconductor value chain.

Software and design tools form another critical component of the chiplet ecosystem. Electronic design automation (EDA) companies have developed new tools and methodologies to support chiplet-based design flows, addressing challenges such as system-level optimization, die-to-die interface design, and multi-chiplet verification. These advancements have enabled designers to fully leverage the potential of chiplet architectures in creating complex, high-performance systems.

As the chiplet ecosystem continues to evolve, it is driving innovation across the entire semiconductor industry. From enabling more efficient and cost-effective chip designs to fostering greater collaboration and specialization among industry players, the chiplet approach is reshaping the landscape of integrated circuit development and manufacturing. This ecosystem's growth and maturation will play a pivotal role in addressing the increasing demands for performance, power efficiency, and scalability in next-generation computing systems.

Performance Metrics

Performance metrics play a crucial role in evaluating the effectiveness of chiplet-based designs in multithread execution models. These metrics provide quantitative measures to assess the performance gains, efficiency improvements, and potential bottlenecks in chiplet architectures.

One of the primary performance metrics for chiplet-based systems is throughput, which measures the number of tasks or operations completed per unit of time. In the context of multithread execution models, this metric becomes particularly important as it reflects the system's ability to handle concurrent workloads efficiently. Chiplet designs aim to enhance throughput by enabling parallel processing across multiple dies, potentially leading to significant performance improvements over monolithic designs.

Latency is another critical metric that evaluates the time taken for a single operation or task to complete. In chiplet architectures, inter-die communication can introduce additional latency, which must be carefully managed to maintain overall system performance. Optimizing the interconnect technology and die-to-die communication protocols becomes essential to minimize latency overhead in multithread execution scenarios.

Power efficiency is a key consideration in chiplet designs, as it directly impacts the system's thermal characteristics and energy consumption. Performance per watt serves as a valuable metric to assess the energy efficiency of chiplet-based solutions compared to traditional monolithic designs. This metric is particularly relevant in data center and high-performance computing environments, where power consumption and cooling requirements are significant concerns.

Scalability is an essential metric for evaluating chiplet potential in multithread execution models. It measures how well the system's performance scales with the addition of more chiplets or cores. Ideal scaling would result in linear performance improvements as resources are added, but in practice, factors such as communication overhead and workload characteristics can limit scalability.

Memory bandwidth and cache performance metrics are crucial for assessing the effectiveness of chiplet designs in handling data-intensive multithreaded workloads. These metrics include memory access latency, cache hit rates, and memory throughput. Chiplet architectures must efficiently manage data movement between dies and optimize cache coherence protocols to maintain high performance in multithread scenarios.

Utilization metrics provide insights into how effectively the available resources in a chiplet-based system are being used. These metrics can help identify potential bottlenecks or underutilized components, guiding optimization efforts and informing future design decisions. In multithread execution models, balanced utilization across chiplets is essential for maximizing overall system performance.

One of the primary performance metrics for chiplet-based systems is throughput, which measures the number of tasks or operations completed per unit of time. In the context of multithread execution models, this metric becomes particularly important as it reflects the system's ability to handle concurrent workloads efficiently. Chiplet designs aim to enhance throughput by enabling parallel processing across multiple dies, potentially leading to significant performance improvements over monolithic designs.

Latency is another critical metric that evaluates the time taken for a single operation or task to complete. In chiplet architectures, inter-die communication can introduce additional latency, which must be carefully managed to maintain overall system performance. Optimizing the interconnect technology and die-to-die communication protocols becomes essential to minimize latency overhead in multithread execution scenarios.

Power efficiency is a key consideration in chiplet designs, as it directly impacts the system's thermal characteristics and energy consumption. Performance per watt serves as a valuable metric to assess the energy efficiency of chiplet-based solutions compared to traditional monolithic designs. This metric is particularly relevant in data center and high-performance computing environments, where power consumption and cooling requirements are significant concerns.

Scalability is an essential metric for evaluating chiplet potential in multithread execution models. It measures how well the system's performance scales with the addition of more chiplets or cores. Ideal scaling would result in linear performance improvements as resources are added, but in practice, factors such as communication overhead and workload characteristics can limit scalability.

Memory bandwidth and cache performance metrics are crucial for assessing the effectiveness of chiplet designs in handling data-intensive multithreaded workloads. These metrics include memory access latency, cache hit rates, and memory throughput. Chiplet architectures must efficiently manage data movement between dies and optimize cache coherence protocols to maintain high performance in multithread scenarios.

Utilization metrics provide insights into how effectively the available resources in a chiplet-based system are being used. These metrics can help identify potential bottlenecks or underutilized components, guiding optimization efforts and informing future design decisions. In multithread execution models, balanced utilization across chiplets is essential for maximizing overall system performance.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!