How to Utilize Chiplet Technology for Enhanced System Control?

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Tech Evolution

Chiplet technology has undergone significant evolution since its inception, marking a paradigm shift in system-on-chip (SoC) design and manufacturing. The journey of chiplets began as a response to the challenges posed by Moore's Law, which was reaching its physical and economic limits in traditional monolithic chip designs.

In the early 2010s, the concept of disaggregating complex SoCs into smaller, more manageable chiplets gained traction. This approach allowed for the integration of diverse components manufactured using different process nodes, optimizing performance and cost. The initial focus was on improving yield and reducing manufacturing costs for high-performance computing applications.

As the technology matured, chiplet designs expanded beyond simple disaggregation. Advanced packaging technologies, such as 2.5D and 3D integration, emerged as critical enablers for chiplet-based systems. These packaging innovations allowed for higher bandwidth interconnects between chiplets, reducing latency and improving overall system performance.

The mid-2010s saw the introduction of standardized interfaces for chiplet communication, such as AMD's Infinity Fabric and Intel's Advanced Interface Bus (AIB). These interfaces facilitated the development of modular chip designs, enabling mix-and-match capabilities for different functional blocks.

By the late 2010s, chiplet technology had evolved to address power efficiency concerns. The ability to optimize each chiplet for its specific function and process node led to significant improvements in energy consumption, particularly crucial for data center and mobile applications.

The most recent developments in chiplet technology focus on enhancing system control through advanced integration techniques. This includes the implementation of artificial intelligence and machine learning algorithms directly into chiplet-based systems, allowing for more sophisticated power management, thermal control, and performance optimization.

Looking forward, the evolution of chiplet technology is expected to continue with a focus on even finer-grained disaggregation, potentially down to the level of individual IP blocks. This trend is likely to be accompanied by advancements in heterogeneous integration, enabling the seamless combination of digital, analog, and RF components within a single package.

The ongoing evolution of chiplet technology is set to revolutionize system control by offering unprecedented flexibility, scalability, and performance optimization. As the technology continues to mature, it promises to unlock new possibilities in areas such as edge computing, 5G/6G communications, and next-generation AI accelerators, further solidifying its role in shaping the future of computing systems.

In the early 2010s, the concept of disaggregating complex SoCs into smaller, more manageable chiplets gained traction. This approach allowed for the integration of diverse components manufactured using different process nodes, optimizing performance and cost. The initial focus was on improving yield and reducing manufacturing costs for high-performance computing applications.

As the technology matured, chiplet designs expanded beyond simple disaggregation. Advanced packaging technologies, such as 2.5D and 3D integration, emerged as critical enablers for chiplet-based systems. These packaging innovations allowed for higher bandwidth interconnects between chiplets, reducing latency and improving overall system performance.

The mid-2010s saw the introduction of standardized interfaces for chiplet communication, such as AMD's Infinity Fabric and Intel's Advanced Interface Bus (AIB). These interfaces facilitated the development of modular chip designs, enabling mix-and-match capabilities for different functional blocks.

By the late 2010s, chiplet technology had evolved to address power efficiency concerns. The ability to optimize each chiplet for its specific function and process node led to significant improvements in energy consumption, particularly crucial for data center and mobile applications.

The most recent developments in chiplet technology focus on enhancing system control through advanced integration techniques. This includes the implementation of artificial intelligence and machine learning algorithms directly into chiplet-based systems, allowing for more sophisticated power management, thermal control, and performance optimization.

Looking forward, the evolution of chiplet technology is expected to continue with a focus on even finer-grained disaggregation, potentially down to the level of individual IP blocks. This trend is likely to be accompanied by advancements in heterogeneous integration, enabling the seamless combination of digital, analog, and RF components within a single package.

The ongoing evolution of chiplet technology is set to revolutionize system control by offering unprecedented flexibility, scalability, and performance optimization. As the technology continues to mature, it promises to unlock new possibilities in areas such as edge computing, 5G/6G communications, and next-generation AI accelerators, further solidifying its role in shaping the future of computing systems.

System Control Demand

The demand for advanced system control in modern electronic devices and systems has been steadily increasing, driven by the need for higher performance, improved energy efficiency, and enhanced functionality. Chiplet technology has emerged as a promising solution to address these demands, offering a modular approach to system design that can significantly enhance control capabilities.

In the context of system control, chiplet technology provides several key advantages. Firstly, it allows for the integration of specialized control modules within a single package, enabling more precise and efficient management of various system components. This modular approach facilitates the implementation of sophisticated control algorithms and feedback mechanisms, resulting in improved overall system performance.

The market for chiplet-based system control solutions is experiencing rapid growth, particularly in sectors such as automotive, industrial automation, and consumer electronics. As these industries continue to evolve towards more complex and interconnected systems, the demand for advanced control capabilities is expected to surge. Chiplet technology offers a scalable and flexible solution to meet these evolving requirements, allowing manufacturers to adapt their designs quickly to changing market needs.

One of the primary drivers for chiplet adoption in system control applications is the increasing complexity of modern electronic systems. Traditional monolithic designs are reaching their limits in terms of performance and integration, making it challenging to implement advanced control features efficiently. Chiplet technology addresses this issue by enabling the integration of diverse control functions, such as sensor fusion, real-time processing, and adaptive algorithms, into a single package while maintaining optimal performance and power efficiency.

The automotive industry, in particular, has shown significant interest in chiplet-based system control solutions. As vehicles become more autonomous and electrified, the demand for sophisticated control systems has skyrocketed. Chiplet technology enables the integration of multiple control units, such as those for powertrain management, advanced driver assistance systems (ADAS), and battery management, into a single, highly efficient package. This integration not only improves overall system performance but also reduces complexity and enhances reliability.

In the industrial automation sector, chiplet technology is being leveraged to create more intelligent and responsive control systems. The ability to combine different types of processing elements, such as high-performance CPUs, GPUs, and specialized accelerators, within a single package allows for the development of more capable and efficient industrial control systems. These systems can handle complex tasks such as real-time process optimization, predictive maintenance, and adaptive manufacturing with greater efficiency and flexibility.

The consumer electronics market is also driving demand for chiplet-based system control solutions. As devices become more feature-rich and interconnected, the need for sophisticated control systems that can manage power consumption, thermal performance, and user interactions efficiently has increased. Chiplet technology enables the integration of dedicated control modules for specific functions, such as AI-powered voice recognition or gesture control, alongside general-purpose processors, resulting in more capable and energy-efficient devices.

In the context of system control, chiplet technology provides several key advantages. Firstly, it allows for the integration of specialized control modules within a single package, enabling more precise and efficient management of various system components. This modular approach facilitates the implementation of sophisticated control algorithms and feedback mechanisms, resulting in improved overall system performance.

The market for chiplet-based system control solutions is experiencing rapid growth, particularly in sectors such as automotive, industrial automation, and consumer electronics. As these industries continue to evolve towards more complex and interconnected systems, the demand for advanced control capabilities is expected to surge. Chiplet technology offers a scalable and flexible solution to meet these evolving requirements, allowing manufacturers to adapt their designs quickly to changing market needs.

One of the primary drivers for chiplet adoption in system control applications is the increasing complexity of modern electronic systems. Traditional monolithic designs are reaching their limits in terms of performance and integration, making it challenging to implement advanced control features efficiently. Chiplet technology addresses this issue by enabling the integration of diverse control functions, such as sensor fusion, real-time processing, and adaptive algorithms, into a single package while maintaining optimal performance and power efficiency.

The automotive industry, in particular, has shown significant interest in chiplet-based system control solutions. As vehicles become more autonomous and electrified, the demand for sophisticated control systems has skyrocketed. Chiplet technology enables the integration of multiple control units, such as those for powertrain management, advanced driver assistance systems (ADAS), and battery management, into a single, highly efficient package. This integration not only improves overall system performance but also reduces complexity and enhances reliability.

In the industrial automation sector, chiplet technology is being leveraged to create more intelligent and responsive control systems. The ability to combine different types of processing elements, such as high-performance CPUs, GPUs, and specialized accelerators, within a single package allows for the development of more capable and efficient industrial control systems. These systems can handle complex tasks such as real-time process optimization, predictive maintenance, and adaptive manufacturing with greater efficiency and flexibility.

The consumer electronics market is also driving demand for chiplet-based system control solutions. As devices become more feature-rich and interconnected, the need for sophisticated control systems that can manage power consumption, thermal performance, and user interactions efficiently has increased. Chiplet technology enables the integration of dedicated control modules for specific functions, such as AI-powered voice recognition or gesture control, alongside general-purpose processors, resulting in more capable and energy-efficient devices.

Chiplet Challenges

While chiplet technology offers numerous advantages for enhanced system control, it also presents several significant challenges that need to be addressed. One of the primary obstacles is the complexity of integration. Combining multiple chiplets into a single package requires sophisticated interconnect technologies and precise alignment, which can be technically demanding and costly. This integration challenge extends to both physical and electrical domains, necessitating advanced packaging solutions and high-bandwidth, low-latency communication interfaces between chiplets.

Another critical challenge lies in the thermal management of chiplet-based systems. As multiple chiplets are packed closely together, heat dissipation becomes a major concern. Efficient cooling solutions must be developed to prevent thermal throttling and ensure optimal performance across all chiplets. This challenge is particularly acute in high-performance computing applications where power density is already a limiting factor.

Standardization and interoperability pose additional hurdles for chiplet technology. The lack of universal standards for chiplet interfaces and protocols can hinder the development of a robust ecosystem. This fragmentation may lead to compatibility issues between chiplets from different manufacturers, potentially limiting the flexibility and cost-effectiveness that chiplet technology promises.

The design and verification process for chiplet-based systems is also more complex compared to traditional monolithic chips. Engineers must consider the interactions between multiple chiplets, each potentially having different process nodes, performance characteristics, and power requirements. This complexity extends to system-level optimization, where balancing performance, power consumption, and cost across multiple chiplets becomes a multidimensional challenge.

Testing and quality assurance present unique challenges in chiplet technology. Traditional testing methodologies may not be sufficient for assessing the performance and reliability of interconnected chiplets. New testing strategies and equipment may be required to ensure the integrity of inter-chiplet connections and overall system functionality.

From a manufacturing perspective, chiplet technology introduces new yield management challenges. While it allows for the use of optimal process nodes for different components, it also requires high yields for each chiplet and the integration process itself. Any defects in individual chiplets or the integration process can impact the overall system yield, potentially offsetting the cost advantages of chiplet technology.

Lastly, the supply chain and logistics for chiplet-based systems are more complex than those for traditional monolithic chips. Managing the production, inventory, and assembly of multiple chiplets from potentially different suppliers adds layers of complexity to the manufacturing process. This can impact time-to-market and require new approaches to supply chain management in the semiconductor industry.

Another critical challenge lies in the thermal management of chiplet-based systems. As multiple chiplets are packed closely together, heat dissipation becomes a major concern. Efficient cooling solutions must be developed to prevent thermal throttling and ensure optimal performance across all chiplets. This challenge is particularly acute in high-performance computing applications where power density is already a limiting factor.

Standardization and interoperability pose additional hurdles for chiplet technology. The lack of universal standards for chiplet interfaces and protocols can hinder the development of a robust ecosystem. This fragmentation may lead to compatibility issues between chiplets from different manufacturers, potentially limiting the flexibility and cost-effectiveness that chiplet technology promises.

The design and verification process for chiplet-based systems is also more complex compared to traditional monolithic chips. Engineers must consider the interactions between multiple chiplets, each potentially having different process nodes, performance characteristics, and power requirements. This complexity extends to system-level optimization, where balancing performance, power consumption, and cost across multiple chiplets becomes a multidimensional challenge.

Testing and quality assurance present unique challenges in chiplet technology. Traditional testing methodologies may not be sufficient for assessing the performance and reliability of interconnected chiplets. New testing strategies and equipment may be required to ensure the integrity of inter-chiplet connections and overall system functionality.

From a manufacturing perspective, chiplet technology introduces new yield management challenges. While it allows for the use of optimal process nodes for different components, it also requires high yields for each chiplet and the integration process itself. Any defects in individual chiplets or the integration process can impact the overall system yield, potentially offsetting the cost advantages of chiplet technology.

Lastly, the supply chain and logistics for chiplet-based systems are more complex than those for traditional monolithic chips. Managing the production, inventory, and assembly of multiple chiplets from potentially different suppliers adds layers of complexity to the manufacturing process. This can impact time-to-market and require new approaches to supply chain management in the semiconductor industry.

Current Chiplet Sols

01 Power management in chiplet systems

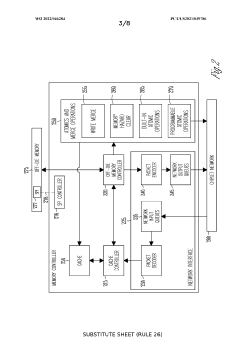

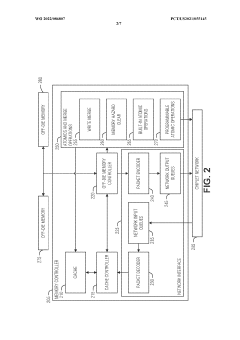

Chiplet technology systems employ advanced power management techniques to optimize energy consumption across multiple chiplets. This includes dynamic voltage and frequency scaling, power gating, and intelligent power distribution mechanisms to ensure efficient operation of the entire system while maintaining performance requirements.- Power management in chiplet systems: Chiplet technology systems employ advanced power management techniques to optimize energy consumption across multiple chiplets. This includes dynamic voltage and frequency scaling, power gating, and intelligent power distribution strategies to balance performance and efficiency in multi-chiplet architectures.

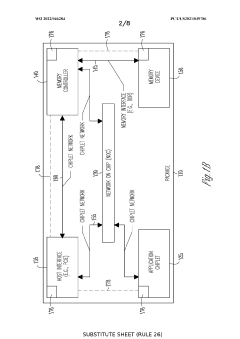

- Inter-chiplet communication protocols: Efficient communication between chiplets is crucial for system performance. Advanced protocols are developed to manage data transfer, synchronization, and coherency between chiplets, ensuring low-latency and high-bandwidth connections while maintaining system integrity and reducing overall complexity.

- Thermal management in chiplet systems: Thermal control is critical in chiplet-based designs due to high-density integration. Advanced cooling solutions and thermal management techniques are implemented to maintain optimal operating temperatures across chiplets, preventing hotspots and ensuring reliable system performance.

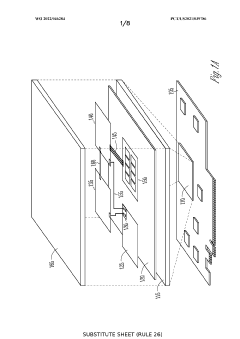

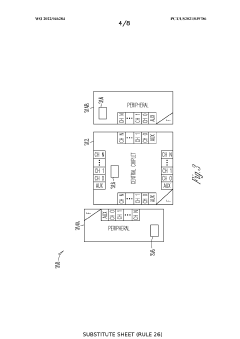

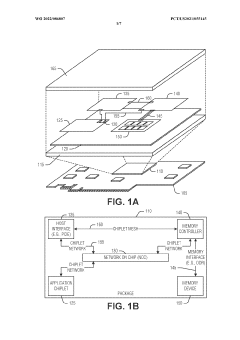

- Chiplet integration and packaging technologies: Novel packaging and integration techniques are developed to efficiently combine multiple chiplets into a single system. This includes advanced interconnect technologies, 2.5D and 3D integration methods, and innovative substrate designs to optimize performance, power, and form factor of chiplet-based systems.

- System-level control and optimization for chiplets: Sophisticated control mechanisms are implemented at the system level to manage and optimize the overall performance of chiplet-based architectures. This includes adaptive resource allocation, workload balancing across chiplets, and intelligent scheduling algorithms to maximize system efficiency and responsiveness.

02 Inter-chiplet communication protocols

Efficient communication between chiplets is crucial for system performance. Advanced protocols are implemented to facilitate high-speed, low-latency data transfer between chiplets, including serialization/deserialization techniques, packet-based communication, and adaptive routing algorithms to optimize data flow and reduce bottlenecks.Expand Specific Solutions03 Thermal management and control

Chiplet systems require sophisticated thermal management to maintain optimal operating temperatures across all components. This involves the use of advanced cooling solutions, thermal sensors, and intelligent heat distribution techniques to prevent hotspots and ensure consistent performance across the entire chiplet array.Expand Specific Solutions04 System-level integration and control

Chiplet technology systems necessitate complex integration strategies to ensure seamless operation of heterogeneous components. This includes the development of advanced packaging technologies, system-on-chip (SoC) architectures, and centralized control mechanisms to coordinate the functions of various chiplets and optimize overall system performance.Expand Specific Solutions05 Fault tolerance and error management

Ensuring reliability in chiplet-based systems involves implementing robust fault tolerance mechanisms. This includes error detection and correction techniques, redundancy schemes, and dynamic reconfiguration capabilities to maintain system integrity and performance in the event of component failures or errors within individual chiplets.Expand Specific Solutions

Key Chiplet Players

The chiplet technology market is in its growth phase, with increasing adoption across the semiconductor industry. The market size is expanding rapidly, driven by demand for more efficient and scalable chip designs. Technologically, chiplets are maturing, with major players like Intel, AMD, and TSMC making significant advancements. Companies such as Micron, Huawei, and Samsung are also investing heavily in chiplet development, indicating a competitive landscape. The technology's maturity varies, with some firms like Intel and AMD already commercializing chiplet-based products, while others are in earlier stages of research and development. This diverse ecosystem suggests a dynamic market with potential for further innovation and growth in system control applications.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has been actively developing chiplet technology to enhance its semiconductor capabilities. The company's approach involves creating a "chiplet ecosystem" that allows for the integration of various IP blocks from different vendors. Huawei's Kunpeng series of processors utilizes chiplet-based designs to achieve high performance and energy efficiency in server and data center applications[7]. The company is also exploring the use of chiplets in its mobile SoCs to improve system control and performance in smartphones and other devices[8].

Strengths: Focus on creating an open chiplet ecosystem. Experience in both mobile and server chiplet applications. Weaknesses: Geopolitical challenges affecting access to certain technologies. Potential limitations in advanced manufacturing processes.

Intel Corp.

Technical Solution: Intel's chiplet technology, known as "Foveros," utilizes 3D packaging to stack multiple chiplets vertically. This approach allows for the integration of diverse IP blocks and process nodes within a single package. Intel's Foveros technology enables the combination of high-performance compute tiles with low-power process technology tiles, resulting in improved system control and efficiency[1]. The company has implemented this technology in products like Lakefield processors, demonstrating its ability to mix and match different process nodes and IP blocks for optimized performance and power consumption[2].

Strengths: Vertical stacking allows for higher density and performance. Flexibility in combining different process nodes. Weaknesses: Potential thermal management challenges in 3D stacked designs. Higher manufacturing complexity and cost.

Chiplet Innovations

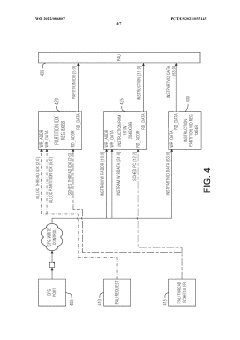

Method for configuring multiple input-output channels

PatentWO2022046284A1

Innovation

- The implementation of a Chiplet Protocol Interface (CPI) network with Advanced Interface Bus (AIB) channels and credit-based flow control, allowing for flexible virtual channel mapping and minimizing latency and energy consumption through packetized protocols and serialization-deserialization (SERDES) hardware, while enabling efficient inter-chiplet communication.

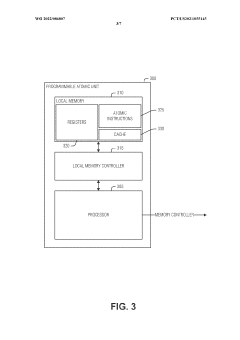

On-demand programmable atomic kernel loading

PatentWO2022086807A1

Innovation

- Implementing an on-demand mechanism for loading PAO kernels, where PAUs register for potential use and reserve space, loading the kernel only when requested, and signaling a trap to initiate kernel transfer when needed.

Chiplet Standards

Chiplet standards play a crucial role in enabling the effective utilization of chiplet technology for enhanced system control. These standards provide a framework for interoperability, communication, and integration of chiplets from different manufacturers, ensuring seamless functionality within a single package.

The Universal Chiplet Interconnect Express (UCIe) standard, developed by a consortium of industry leaders, has emerged as a key player in chiplet standardization. UCIe defines protocols for die-to-die interconnects, allowing chiplets to communicate efficiently within a package. This standard supports both parallel and serial interfaces, catering to various bandwidth and latency requirements across different applications.

Another significant standard in the chiplet ecosystem is the Advanced Interface Bus (AIB), which focuses on high-speed die-to-die communication. AIB provides a standardized interface for chiplets, enabling modular design and facilitating the integration of heterogeneous components. This standard has been widely adopted by major semiconductor companies and is continuously evolving to meet the demands of advanced system control applications.

The Open Compute Project (OCP) has also contributed to chiplet standardization efforts through its Open Domain-Specific Architecture (ODSA) workgroup. The ODSA aims to develop open architectures and standards for chiplet-based designs, promoting interoperability and reducing time-to-market for chiplet-based systems.

Standardization efforts extend beyond interconnects to include power management and thermal considerations. The Heterogeneous Integration Roadmap (HIR), supported by IEEE, SEMI, and other industry organizations, provides guidelines for chiplet integration, addressing challenges such as power delivery and thermal management in multi-chiplet systems.

As chiplet technology continues to evolve, emerging standards are focusing on advanced packaging techniques and 3D integration. These standards aim to address the challenges of vertical stacking and through-silicon via (TSV) technology, enabling more compact and efficient chiplet-based designs for enhanced system control.

The adoption of these standards is crucial for the widespread implementation of chiplet technology in system control applications. By adhering to established standards, manufacturers can ensure compatibility between chiplets from different sources, reduce development costs, and accelerate time-to-market for innovative chiplet-based solutions.

The Universal Chiplet Interconnect Express (UCIe) standard, developed by a consortium of industry leaders, has emerged as a key player in chiplet standardization. UCIe defines protocols for die-to-die interconnects, allowing chiplets to communicate efficiently within a package. This standard supports both parallel and serial interfaces, catering to various bandwidth and latency requirements across different applications.

Another significant standard in the chiplet ecosystem is the Advanced Interface Bus (AIB), which focuses on high-speed die-to-die communication. AIB provides a standardized interface for chiplets, enabling modular design and facilitating the integration of heterogeneous components. This standard has been widely adopted by major semiconductor companies and is continuously evolving to meet the demands of advanced system control applications.

The Open Compute Project (OCP) has also contributed to chiplet standardization efforts through its Open Domain-Specific Architecture (ODSA) workgroup. The ODSA aims to develop open architectures and standards for chiplet-based designs, promoting interoperability and reducing time-to-market for chiplet-based systems.

Standardization efforts extend beyond interconnects to include power management and thermal considerations. The Heterogeneous Integration Roadmap (HIR), supported by IEEE, SEMI, and other industry organizations, provides guidelines for chiplet integration, addressing challenges such as power delivery and thermal management in multi-chiplet systems.

As chiplet technology continues to evolve, emerging standards are focusing on advanced packaging techniques and 3D integration. These standards aim to address the challenges of vertical stacking and through-silicon via (TSV) technology, enabling more compact and efficient chiplet-based designs for enhanced system control.

The adoption of these standards is crucial for the widespread implementation of chiplet technology in system control applications. By adhering to established standards, manufacturers can ensure compatibility between chiplets from different sources, reduce development costs, and accelerate time-to-market for innovative chiplet-based solutions.

Thermal Management

Thermal management is a critical aspect of chiplet technology implementation for enhanced system control. As chiplets allow for the integration of multiple dies on a single package, managing heat dissipation becomes increasingly complex. The compact nature of chiplet designs leads to higher power densities, necessitating advanced cooling solutions to maintain optimal performance and reliability.

One of the primary challenges in chiplet thermal management is the non-uniform heat distribution across the package. Different chiplets may generate varying amounts of heat, creating hotspots that can impact overall system performance. To address this issue, designers are exploring innovative cooling techniques such as liquid cooling, microfluidic channels, and phase-change materials. These solutions aim to provide more efficient and targeted heat removal from specific areas of the package.

Another key consideration in chiplet thermal management is the thermal interface material (TIM) used between the chiplets and the heat spreader. Advanced TIMs with higher thermal conductivity and improved mechanical properties are being developed to enhance heat transfer and reduce thermal resistance. These materials play a crucial role in maintaining consistent temperatures across the chiplet package and preventing thermal bottlenecks.

The integration of thermal sensors within chiplet designs is becoming increasingly important for real-time temperature monitoring and dynamic thermal management. By incorporating temperature sensors in strategic locations, system controllers can implement adaptive cooling strategies, adjusting power consumption and clock speeds to optimize performance while maintaining safe operating temperatures.

Furthermore, the use of advanced packaging technologies, such as 2.5D and 3D integration, introduces new thermal challenges and opportunities. These packaging approaches allow for closer integration of chiplets, potentially reducing overall power consumption but also increasing thermal density. Novel thermal management solutions, such as through-silicon vias (TSVs) for heat dissipation and interposer-level cooling channels, are being explored to address these challenges.

As chiplet technology continues to evolve, thermal management strategies must adapt to support higher performance and more complex system designs. This includes the development of sophisticated thermal modeling and simulation tools to accurately predict heat distribution and optimize cooling solutions during the design phase. Additionally, the integration of artificial intelligence and machine learning algorithms for dynamic thermal management is emerging as a promising approach to further enhance system control and energy efficiency in chiplet-based architectures.

One of the primary challenges in chiplet thermal management is the non-uniform heat distribution across the package. Different chiplets may generate varying amounts of heat, creating hotspots that can impact overall system performance. To address this issue, designers are exploring innovative cooling techniques such as liquid cooling, microfluidic channels, and phase-change materials. These solutions aim to provide more efficient and targeted heat removal from specific areas of the package.

Another key consideration in chiplet thermal management is the thermal interface material (TIM) used between the chiplets and the heat spreader. Advanced TIMs with higher thermal conductivity and improved mechanical properties are being developed to enhance heat transfer and reduce thermal resistance. These materials play a crucial role in maintaining consistent temperatures across the chiplet package and preventing thermal bottlenecks.

The integration of thermal sensors within chiplet designs is becoming increasingly important for real-time temperature monitoring and dynamic thermal management. By incorporating temperature sensors in strategic locations, system controllers can implement adaptive cooling strategies, adjusting power consumption and clock speeds to optimize performance while maintaining safe operating temperatures.

Furthermore, the use of advanced packaging technologies, such as 2.5D and 3D integration, introduces new thermal challenges and opportunities. These packaging approaches allow for closer integration of chiplets, potentially reducing overall power consumption but also increasing thermal density. Novel thermal management solutions, such as through-silicon vias (TSVs) for heat dissipation and interposer-level cooling channels, are being explored to address these challenges.

As chiplet technology continues to evolve, thermal management strategies must adapt to support higher performance and more complex system designs. This includes the development of sophisticated thermal modeling and simulation tools to accurately predict heat distribution and optimize cooling solutions during the design phase. Additionally, the integration of artificial intelligence and machine learning algorithms for dynamic thermal management is emerging as a promising approach to further enhance system control and energy efficiency in chiplet-based architectures.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!