Chiplet Strategies: Innovations in Embedded Processor Design

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Evolution and Objectives

Chiplet technology has emerged as a revolutionary approach in embedded processor design, offering a paradigm shift in how complex systems-on-chip (SoCs) are conceived and manufactured. The evolution of chiplets can be traced back to the early 2010s when the semiconductor industry began facing significant challenges in scaling monolithic chip designs. As Moore's Law slowed down, chiplets presented a viable solution to continue improving performance and functionality while managing costs and yield issues.

The primary objective of chiplet strategies is to disaggregate large, complex SoCs into smaller, more manageable dies that can be manufactured separately and then integrated onto a single package. This approach allows for the mixing and matching of different process nodes, optimizing each component for its specific requirements. By enabling the use of the most suitable manufacturing process for each chiplet, designers can achieve better performance, power efficiency, and cost-effectiveness compared to traditional monolithic designs.

Another key goal of chiplet technology is to enhance scalability and flexibility in processor design. By breaking down a system into modular components, manufacturers can more easily customize and upgrade specific parts of the processor without redesigning the entire chip. This modularity also facilitates faster time-to-market for new products and allows for more efficient reuse of intellectual property across different product lines.

Chiplet strategies aim to address the increasing complexity of modern embedded systems by simplifying the design and verification process. By working with smaller, more manageable chiplets, engineers can focus on optimizing individual components while reducing the overall system complexity. This approach can lead to improved yield rates and potentially lower production costs, especially for high-performance processors that would be challenging to manufacture as a single, large die.

As chiplet technology continues to evolve, a significant objective is to standardize interconnect protocols and packaging technologies. Industry initiatives like the Universal Chiplet Interconnect Express (UCIe) consortium are working towards creating open standards for chiplet-to-chiplet communication. These efforts aim to foster a more diverse and competitive ecosystem, enabling interoperability between chiplets from different vendors and accelerating innovation in the embedded processor space.

Looking ahead, the chiplet strategy is poised to play a crucial role in advancing embedded processor design beyond traditional silicon scaling. Objectives include enabling heterogeneous integration of diverse technologies, such as analog, RF, and even photonic components, alongside digital logic. This integration has the potential to unlock new capabilities and applications in areas like artificial intelligence, edge computing, and high-performance embedded systems.

The primary objective of chiplet strategies is to disaggregate large, complex SoCs into smaller, more manageable dies that can be manufactured separately and then integrated onto a single package. This approach allows for the mixing and matching of different process nodes, optimizing each component for its specific requirements. By enabling the use of the most suitable manufacturing process for each chiplet, designers can achieve better performance, power efficiency, and cost-effectiveness compared to traditional monolithic designs.

Another key goal of chiplet technology is to enhance scalability and flexibility in processor design. By breaking down a system into modular components, manufacturers can more easily customize and upgrade specific parts of the processor without redesigning the entire chip. This modularity also facilitates faster time-to-market for new products and allows for more efficient reuse of intellectual property across different product lines.

Chiplet strategies aim to address the increasing complexity of modern embedded systems by simplifying the design and verification process. By working with smaller, more manageable chiplets, engineers can focus on optimizing individual components while reducing the overall system complexity. This approach can lead to improved yield rates and potentially lower production costs, especially for high-performance processors that would be challenging to manufacture as a single, large die.

As chiplet technology continues to evolve, a significant objective is to standardize interconnect protocols and packaging technologies. Industry initiatives like the Universal Chiplet Interconnect Express (UCIe) consortium are working towards creating open standards for chiplet-to-chiplet communication. These efforts aim to foster a more diverse and competitive ecosystem, enabling interoperability between chiplets from different vendors and accelerating innovation in the embedded processor space.

Looking ahead, the chiplet strategy is poised to play a crucial role in advancing embedded processor design beyond traditional silicon scaling. Objectives include enabling heterogeneous integration of diverse technologies, such as analog, RF, and even photonic components, alongside digital logic. This integration has the potential to unlock new capabilities and applications in areas like artificial intelligence, edge computing, and high-performance embedded systems.

Market Demand Analysis for Chiplet-based Processors

The market demand for chiplet-based processors has been steadily increasing, driven by the growing need for more powerful and efficient computing solutions across various industries. As traditional monolithic chip designs approach their physical limits, chiplet technology offers a promising alternative to meet the escalating performance requirements of modern applications.

In the data center and cloud computing sector, there is a significant demand for chiplet-based processors due to their ability to deliver higher performance and improved energy efficiency. These processors can handle the increasing workloads associated with artificial intelligence, machine learning, and big data analytics more effectively than traditional designs. The flexibility of chiplet architecture allows for customization and scalability, which is particularly attractive to cloud service providers seeking to optimize their infrastructure.

The telecommunications industry, especially with the ongoing rollout of 5G networks, represents another substantial market for chiplet-based processors. These processors can provide the necessary computing power to handle the complex signal processing and network management tasks required in 5G base stations and edge computing nodes. The modular nature of chiplets allows for easier integration of specialized components, such as RF modules, which is crucial for 5G applications.

In the consumer electronics market, chiplet-based processors are gaining traction in high-performance devices such as gaming consoles, laptops, and smartphones. The technology enables manufacturers to create more powerful and energy-efficient devices while potentially reducing production costs through improved yield rates. This is particularly important in the competitive consumer electronics landscape where performance, battery life, and price are key differentiators.

The automotive industry is another sector showing increased interest in chiplet-based processors. As vehicles become more autonomous and connected, there is a growing need for advanced computing capabilities. Chiplet technology can provide the necessary processing power for autonomous driving systems, infotainment, and vehicle-to-everything (V2X) communication while meeting the stringent reliability and safety requirements of the automotive sector.

Looking at market trends, the adoption of chiplet technology is expected to accelerate in the coming years. This growth is fueled by the increasing demand for high-performance computing across various applications and the limitations of traditional monolithic chip designs. The modular nature of chiplets aligns well with the industry's move towards more specialized and heterogeneous computing solutions, allowing for greater flexibility and innovation in processor design.

However, challenges such as standardization of chiplet interfaces and the complexity of system integration need to be addressed to fully realize the market potential of chiplet-based processors. Despite these challenges, the overall market outlook for chiplet technology remains positive, with significant growth opportunities across multiple sectors.

In the data center and cloud computing sector, there is a significant demand for chiplet-based processors due to their ability to deliver higher performance and improved energy efficiency. These processors can handle the increasing workloads associated with artificial intelligence, machine learning, and big data analytics more effectively than traditional designs. The flexibility of chiplet architecture allows for customization and scalability, which is particularly attractive to cloud service providers seeking to optimize their infrastructure.

The telecommunications industry, especially with the ongoing rollout of 5G networks, represents another substantial market for chiplet-based processors. These processors can provide the necessary computing power to handle the complex signal processing and network management tasks required in 5G base stations and edge computing nodes. The modular nature of chiplets allows for easier integration of specialized components, such as RF modules, which is crucial for 5G applications.

In the consumer electronics market, chiplet-based processors are gaining traction in high-performance devices such as gaming consoles, laptops, and smartphones. The technology enables manufacturers to create more powerful and energy-efficient devices while potentially reducing production costs through improved yield rates. This is particularly important in the competitive consumer electronics landscape where performance, battery life, and price are key differentiators.

The automotive industry is another sector showing increased interest in chiplet-based processors. As vehicles become more autonomous and connected, there is a growing need for advanced computing capabilities. Chiplet technology can provide the necessary processing power for autonomous driving systems, infotainment, and vehicle-to-everything (V2X) communication while meeting the stringent reliability and safety requirements of the automotive sector.

Looking at market trends, the adoption of chiplet technology is expected to accelerate in the coming years. This growth is fueled by the increasing demand for high-performance computing across various applications and the limitations of traditional monolithic chip designs. The modular nature of chiplets aligns well with the industry's move towards more specialized and heterogeneous computing solutions, allowing for greater flexibility and innovation in processor design.

However, challenges such as standardization of chiplet interfaces and the complexity of system integration need to be addressed to fully realize the market potential of chiplet-based processors. Despite these challenges, the overall market outlook for chiplet technology remains positive, with significant growth opportunities across multiple sectors.

Current Chiplet Technology Landscape

The current chiplet technology landscape is characterized by a dynamic and rapidly evolving ecosystem, driven by the need for more efficient and scalable processor designs. Chiplets, which are smaller, modular components that can be combined to form larger, more complex systems, have emerged as a promising solution to address the challenges of traditional monolithic chip designs.

In the embedded processor domain, chiplet strategies are gaining significant traction. Major semiconductor companies, including AMD, Intel, and TSMC, have invested heavily in chiplet technologies, recognizing their potential to revolutionize processor architecture. These companies are developing advanced packaging technologies, such as AMD's Infinity Fabric and Intel's EMIB (Embedded Multi-die Interconnect Bridge), to enable seamless integration of chiplets.

The adoption of chiplets in embedded processors offers several advantages. Firstly, it allows for greater flexibility in design, enabling manufacturers to mix and match different components to create customized solutions for specific applications. This modular approach also facilitates easier upgrades and reduces time-to-market for new products.

Furthermore, chiplet technology addresses the limitations of traditional monolithic designs, particularly in terms of yield and cost-effectiveness. By fabricating smaller, individual components, manufacturers can achieve higher yields and reduce overall production costs. This is especially crucial as the industry moves towards more advanced process nodes, where defect rates tend to increase.

Interoperability and standardization efforts are also shaping the chiplet landscape. Initiatives like the Universal Chiplet Interconnect Express (UCIe) consortium are working towards establishing industry-wide standards for chiplet interfaces, promoting compatibility and fostering innovation across the ecosystem.

In terms of performance, chiplet-based designs are demonstrating impressive capabilities. They enable the integration of heterogeneous components, such as CPUs, GPUs, and specialized accelerators, on a single package. This approach allows for optimized performance and power efficiency, crucial factors in embedded systems where resources are often constrained.

However, challenges remain in the widespread adoption of chiplet technology. These include thermal management issues, signal integrity concerns in high-speed inter-chiplet communications, and the need for advanced packaging solutions. Ongoing research and development efforts are focused on addressing these challenges, with innovations in areas such as through-silicon vias (TSVs) and advanced cooling techniques.

As the chiplet ecosystem continues to mature, we are witnessing a shift in the design paradigm for embedded processors. The ability to create more powerful, efficient, and customizable solutions through chiplet integration is driving innovation across various sectors, from edge computing to automotive systems and beyond.

In the embedded processor domain, chiplet strategies are gaining significant traction. Major semiconductor companies, including AMD, Intel, and TSMC, have invested heavily in chiplet technologies, recognizing their potential to revolutionize processor architecture. These companies are developing advanced packaging technologies, such as AMD's Infinity Fabric and Intel's EMIB (Embedded Multi-die Interconnect Bridge), to enable seamless integration of chiplets.

The adoption of chiplets in embedded processors offers several advantages. Firstly, it allows for greater flexibility in design, enabling manufacturers to mix and match different components to create customized solutions for specific applications. This modular approach also facilitates easier upgrades and reduces time-to-market for new products.

Furthermore, chiplet technology addresses the limitations of traditional monolithic designs, particularly in terms of yield and cost-effectiveness. By fabricating smaller, individual components, manufacturers can achieve higher yields and reduce overall production costs. This is especially crucial as the industry moves towards more advanced process nodes, where defect rates tend to increase.

Interoperability and standardization efforts are also shaping the chiplet landscape. Initiatives like the Universal Chiplet Interconnect Express (UCIe) consortium are working towards establishing industry-wide standards for chiplet interfaces, promoting compatibility and fostering innovation across the ecosystem.

In terms of performance, chiplet-based designs are demonstrating impressive capabilities. They enable the integration of heterogeneous components, such as CPUs, GPUs, and specialized accelerators, on a single package. This approach allows for optimized performance and power efficiency, crucial factors in embedded systems where resources are often constrained.

However, challenges remain in the widespread adoption of chiplet technology. These include thermal management issues, signal integrity concerns in high-speed inter-chiplet communications, and the need for advanced packaging solutions. Ongoing research and development efforts are focused on addressing these challenges, with innovations in areas such as through-silicon vias (TSVs) and advanced cooling techniques.

As the chiplet ecosystem continues to mature, we are witnessing a shift in the design paradigm for embedded processors. The ability to create more powerful, efficient, and customizable solutions through chiplet integration is driving innovation across various sectors, from edge computing to automotive systems and beyond.

Existing Chiplet Integration Solutions

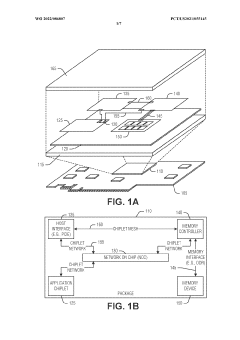

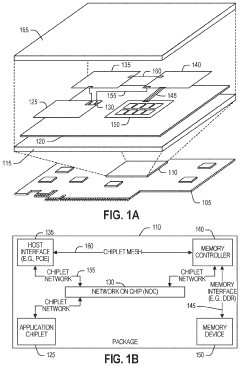

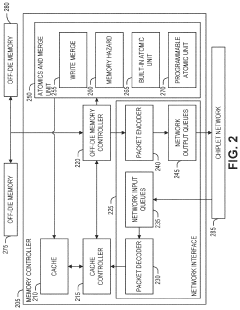

01 Chiplet-based processor architecture

Chiplet-based processor design involves integrating multiple smaller silicon dies (chiplets) onto a single package. This approach allows for more flexible and scalable processor designs, enabling the combination of different functional units or cores manufactured using various process technologies. The chiplet architecture can improve performance, reduce costs, and enhance manufacturing yields compared to monolithic designs.- Chiplet-based processor architecture: Chiplet-based processor design involves integrating multiple smaller silicon dies (chiplets) onto a single package. This approach allows for more flexible and scalable processor designs, improved yield, and potentially lower manufacturing costs. The architecture enables mixing and matching of different chiplets with various functionalities, such as CPU cores, GPU units, or memory controllers.

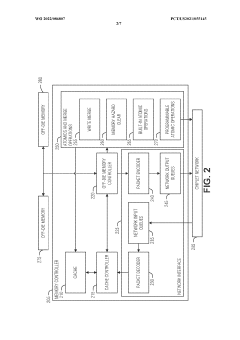

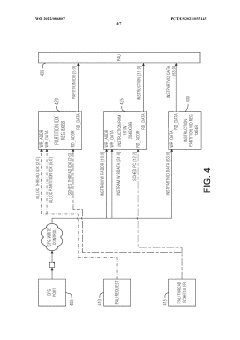

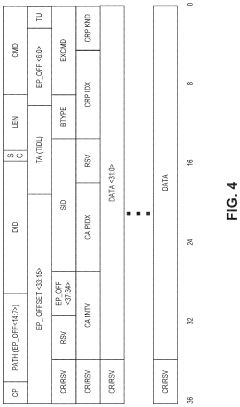

- Inter-chiplet communication and interconnects: Efficient communication between chiplets is crucial for overall processor performance. This involves designing high-speed, low-latency interconnects and protocols for data transfer between different chiplets. Advanced packaging technologies, such as silicon interposers or organic substrates with fine-pitch interconnects, are used to facilitate this communication.

- Power management and thermal optimization: Chiplet-based processors require sophisticated power management and thermal optimization strategies. This includes implementing fine-grained power control for individual chiplets, designing efficient heat dissipation mechanisms, and optimizing the overall thermal envelope of the multi-chiplet package.

- Heterogeneous integration and specialized chiplets: Chiplet-based designs allow for the integration of heterogeneous components, each optimized for specific tasks. This can include specialized chiplets for AI acceleration, signal processing, or other domain-specific functions. The ability to mix and match different types of chiplets enables highly customized processor designs tailored to specific application requirements.

- Packaging and manufacturing techniques: Advanced packaging technologies play a crucial role in chiplet-based processor design. This includes developing new methods for die-to-die bonding, 3D stacking of chiplets, and creating high-density interconnects. Manufacturing techniques such as advanced lithography and wafer-level packaging are essential for producing high-performance chiplet-based processors.

02 Inter-chiplet communication and interconnects

Efficient communication between chiplets is crucial for overall processor performance. This involves designing high-speed, low-latency interconnects and protocols for data transfer between different chiplets. Advanced packaging technologies, such as silicon interposers or organic substrates with high-density interconnects, are used to facilitate inter-chiplet communication and integration.Expand Specific Solutions03 Power management and thermal optimization

Chiplet-based processors require sophisticated power management and thermal optimization strategies. This includes implementing fine-grained power control for individual chiplets, designing efficient heat dissipation solutions, and optimizing the overall thermal envelope of the multi-chiplet package. Advanced cooling techniques and materials may be employed to manage heat distribution across the chiplets.Expand Specific Solutions04 Heterogeneous integration and specialized chiplets

Chiplet-based designs allow for the integration of heterogeneous components, combining different types of processors, accelerators, or specialized functions on a single package. This approach enables the creation of highly customized and optimized systems-on-chip (SoCs) tailored for specific applications or workloads, such as AI acceleration, graphics processing, or high-performance computing.Expand Specific Solutions05 Packaging and integration technologies

Advanced packaging technologies play a crucial role in chiplet-based processor design. This includes the development of 2.5D and 3D packaging techniques, through-silicon vias (TSVs), and advanced bonding methods to integrate multiple chiplets. These technologies enable higher integration density, improved performance, and enhanced functionality of chiplet-based processors.Expand Specific Solutions

Key Players in Chiplet Industry

The chiplet strategies market for embedded processor design is in a growth phase, with increasing adoption across the semiconductor industry. The market size is expanding rapidly as major players invest heavily in this technology. Technological maturity varies, with companies like Intel, AMD, and IBM leading in innovation. Intel's advanced packaging technologies and AMD's chiplet-based processors demonstrate high maturity levels. Micron and Huawei are also making significant strides in chiplet integration for memory and mobile applications, respectively. The competitive landscape is intensifying as more companies recognize the potential of chiplet strategies to address scaling challenges and improve performance in embedded systems.

Micron Technology, Inc.

Technical Solution: Micron's involvement in Chiplet strategies focuses on advanced memory solutions that can be integrated into chiplet-based designs. Their Hybrid Memory Cube (HMC) technology, while not strictly a chiplet approach, demonstrates their capability in 3D stacking of memory dies[11]. Micron is also developing high-bandwidth memory solutions that can be efficiently integrated with processor chiplets. Their research into through-silicon vias (TSVs) and advanced packaging technologies positions them to provide memory solutions optimized for chiplet-based architectures[12].

Strengths: Expertise in memory technologies crucial for chiplet integration, advanced packaging capabilities. Weaknesses: Limited direct involvement in processor chiplet design, reliance on partnerships for full system integration.

Intel Corp.

Technical Solution: Intel's Chiplet strategy, known as "Foveros", is a 3D packaging technology that allows for the vertical stacking of compute tiles[1]. This approach enables the integration of heterogeneous architectures, combining high-performance and low-power cores, as well as different process nodes, in a single package. Intel's Meteor Lake processors utilize this technology, featuring separate tiles for CPU, GPU, and I/O, manufactured on different process nodes[2]. This modular approach allows for more flexible designs and potentially faster time-to-market for new products[3].

Strengths: Flexibility in design, ability to mix different process nodes, potential for improved yield. Weaknesses: Increased complexity in manufacturing and thermal management, potential for higher costs initially.

Core Chiplet Interconnect Innovations

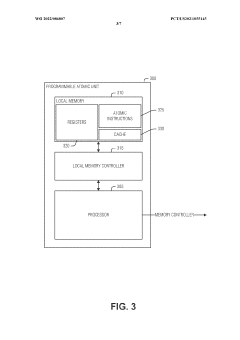

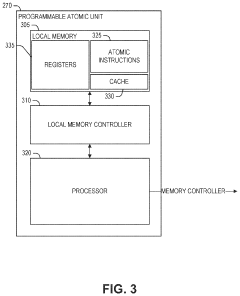

On-demand programmable atomic kernel loading

PatentWO2022086807A1

Innovation

- Implementing an on-demand mechanism for loading PAO kernels, where PAUs register for potential use and reserve space, loading the kernel only when requested, and signaling a trap to initiate kernel transfer when needed.

Method of executing programmable atomic unit resources within a multi-process system

PatentActiveUS12020062B2

Innovation

- A method is disclosed that involves determining a unique identifier for a programmable atomic transaction within a process, using a mapping table to generate a system-wide identifier, and issuing requests to a memory controller to perform the transaction, allowing for efficient execution and response handling through a programmable atomic unit.

Thermal Management Strategies

Thermal management is a critical aspect of chiplet-based embedded processor design, as the increased integration density and power consumption of these multi-chip modules pose significant challenges for heat dissipation. Effective thermal management strategies are essential to maintain optimal performance, reliability, and longevity of chiplet-based systems.

One of the primary thermal management approaches for chiplet designs is the implementation of advanced packaging technologies. These include the use of high-performance thermal interface materials (TIMs) between the chiplets and the heat spreader, as well as the integration of through-silicon vias (TSVs) for improved heat conduction. Additionally, the development of novel heat spreader designs, such as vapor chambers or micro-channel liquid cooling systems, can significantly enhance heat dissipation capabilities.

Another key strategy involves the optimization of chiplet placement and interconnect design to minimize hotspots and ensure uniform heat distribution across the package. This can be achieved through careful thermal modeling and simulation during the design phase, allowing engineers to identify potential thermal issues and optimize the layout accordingly. Furthermore, the implementation of dynamic thermal management techniques, such as adaptive clock gating and power gating, can help regulate heat generation in real-time based on workload and environmental conditions.

Advanced cooling solutions are also being explored for chiplet-based systems. These include the use of phase-change materials for passive cooling, as well as the integration of micro-electromechanical systems (MEMS) based cooling devices directly into the chiplet package. Some researchers are investigating the potential of two-phase cooling systems, which utilize the latent heat of vaporization to achieve more efficient heat removal.

The development of thermally-aware design methodologies is crucial for optimizing the thermal performance of chiplet-based processors. This involves considering thermal constraints throughout the design process, from architectural decisions to physical implementation. Techniques such as thermal-aware floorplanning, power-aware scheduling, and temperature-driven routing can help mitigate thermal issues and improve overall system efficiency.

Lastly, the integration of on-chip temperature sensors and intelligent thermal management algorithms is becoming increasingly important for chiplet-based designs. These systems can provide real-time temperature monitoring and enable adaptive thermal management strategies, such as dynamic voltage and frequency scaling (DVFS) or task migration between chiplets, to maintain optimal thermal conditions and prevent thermal emergencies.

One of the primary thermal management approaches for chiplet designs is the implementation of advanced packaging technologies. These include the use of high-performance thermal interface materials (TIMs) between the chiplets and the heat spreader, as well as the integration of through-silicon vias (TSVs) for improved heat conduction. Additionally, the development of novel heat spreader designs, such as vapor chambers or micro-channel liquid cooling systems, can significantly enhance heat dissipation capabilities.

Another key strategy involves the optimization of chiplet placement and interconnect design to minimize hotspots and ensure uniform heat distribution across the package. This can be achieved through careful thermal modeling and simulation during the design phase, allowing engineers to identify potential thermal issues and optimize the layout accordingly. Furthermore, the implementation of dynamic thermal management techniques, such as adaptive clock gating and power gating, can help regulate heat generation in real-time based on workload and environmental conditions.

Advanced cooling solutions are also being explored for chiplet-based systems. These include the use of phase-change materials for passive cooling, as well as the integration of micro-electromechanical systems (MEMS) based cooling devices directly into the chiplet package. Some researchers are investigating the potential of two-phase cooling systems, which utilize the latent heat of vaporization to achieve more efficient heat removal.

The development of thermally-aware design methodologies is crucial for optimizing the thermal performance of chiplet-based processors. This involves considering thermal constraints throughout the design process, from architectural decisions to physical implementation. Techniques such as thermal-aware floorplanning, power-aware scheduling, and temperature-driven routing can help mitigate thermal issues and improve overall system efficiency.

Lastly, the integration of on-chip temperature sensors and intelligent thermal management algorithms is becoming increasingly important for chiplet-based designs. These systems can provide real-time temperature monitoring and enable adaptive thermal management strategies, such as dynamic voltage and frequency scaling (DVFS) or task migration between chiplets, to maintain optimal thermal conditions and prevent thermal emergencies.

Standardization Efforts in Chiplet Ecosystem

The standardization efforts in the chiplet ecosystem are crucial for enabling interoperability and fostering innovation in embedded processor design. Several industry consortia and organizations are actively working towards establishing common standards and protocols for chiplet integration.

One of the most prominent initiatives is the Universal Chiplet Interconnect Express (UCIe) consortium, which aims to create an open industry standard for die-to-die interconnects. UCIe focuses on defining a common physical layer, protocol stack, and software model to facilitate seamless integration of chiplets from different vendors. This standardization effort is supported by major players in the semiconductor industry, including Intel, AMD, Arm, and TSMC.

Another significant standardization effort is the Open Compute Project's (OCP) Chiplet Design Exchange (CDX) working group. CDX is developing a set of specifications and guidelines for chiplet-based system design, focusing on aspects such as thermal management, power delivery, and signal integrity. The group's work complements UCIe by addressing system-level integration challenges.

The CHIPS Alliance, an open-source hardware organization, is also contributing to chiplet standardization through its Advanced Interface Bus (AIB) specification. AIB provides a standardized die-to-die interface for high-bandwidth, low-latency communication between chiplets. This open-source approach aims to accelerate adoption and innovation in chiplet-based designs.

In addition to these industry-led efforts, government initiatives are also supporting chiplet standardization. For instance, the U.S. Department of Defense's CHIPS (Common Heterogeneous Integration and IP Reuse Strategies) program is funding research and development of modular chip designs and standardized interfaces for military applications.

The IEEE is also playing a role in chiplet standardization through its P2851 working group, which is developing standards for 3D stacking and chiplet integration. This effort focuses on creating a common language and methodology for describing chiplet-based systems, facilitating design and verification processes.

These standardization efforts are critical for realizing the full potential of chiplet-based designs in embedded processor architectures. By establishing common interfaces and protocols, they enable a more diverse and competitive ecosystem, allowing system integrators to mix and match chiplets from different vendors. This approach not only fosters innovation but also has the potential to reduce development costs and time-to-market for complex embedded systems.

One of the most prominent initiatives is the Universal Chiplet Interconnect Express (UCIe) consortium, which aims to create an open industry standard for die-to-die interconnects. UCIe focuses on defining a common physical layer, protocol stack, and software model to facilitate seamless integration of chiplets from different vendors. This standardization effort is supported by major players in the semiconductor industry, including Intel, AMD, Arm, and TSMC.

Another significant standardization effort is the Open Compute Project's (OCP) Chiplet Design Exchange (CDX) working group. CDX is developing a set of specifications and guidelines for chiplet-based system design, focusing on aspects such as thermal management, power delivery, and signal integrity. The group's work complements UCIe by addressing system-level integration challenges.

The CHIPS Alliance, an open-source hardware organization, is also contributing to chiplet standardization through its Advanced Interface Bus (AIB) specification. AIB provides a standardized die-to-die interface for high-bandwidth, low-latency communication between chiplets. This open-source approach aims to accelerate adoption and innovation in chiplet-based designs.

In addition to these industry-led efforts, government initiatives are also supporting chiplet standardization. For instance, the U.S. Department of Defense's CHIPS (Common Heterogeneous Integration and IP Reuse Strategies) program is funding research and development of modular chip designs and standardized interfaces for military applications.

The IEEE is also playing a role in chiplet standardization through its P2851 working group, which is developing standards for 3D stacking and chiplet integration. This effort focuses on creating a common language and methodology for describing chiplet-based systems, facilitating design and verification processes.

These standardization efforts are critical for realizing the full potential of chiplet-based designs in embedded processor architectures. By establishing common interfaces and protocols, they enable a more diverse and competitive ecosystem, allowing system integrators to mix and match chiplets from different vendors. This approach not only fosters innovation but also has the potential to reduce development costs and time-to-market for complex embedded systems.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!