DDR5 Testing Protocols for High-Performance Storage Solutions

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Testing Objectives

DDR5 memory technology represents a significant evolution in the DRAM landscape, building upon its predecessor DDR4 with substantial improvements in bandwidth, capacity, and power efficiency. The development of DDR5 began in 2016, with JEDEC finalizing the standard in 2020, marking a crucial milestone in memory technology advancement. This fifth generation of double data rate synchronous dynamic random-access memory aims to address the growing demands of data-intensive applications, particularly in enterprise storage solutions where performance bottlenecks have increasingly shifted to memory subsystems.

The historical trajectory of DDR technology shows consistent progression in transfer rates, from DDR4's maximum of 3200 MT/s to DDR5's initial offerings at 4800 MT/s and roadmaps extending to 8400 MT/s. This represents more than a doubling of bandwidth capability, critical for high-performance storage applications where data movement between memory and processing units often constrains overall system performance.

Beyond raw speed improvements, DDR5 introduces architectural innovations including dual-channel architecture per DIMM, on-die ECC, and improved power management through voltage regulation moved from motherboards to memory modules. These advancements collectively support the technical objectives of modern storage solutions: increased reliability, reduced latency, and enhanced throughput for massive parallel operations.

The testing objectives for DDR5 in storage contexts must address several dimensions simultaneously. First, signal integrity testing becomes more complex with higher frequencies, requiring advanced methodologies to ensure reliable operation at increased speeds. Second, power delivery and thermal management testing gains importance as DDR5 modules operate with tighter tolerances and potentially higher power density.

Compatibility testing represents another critical objective, particularly during the transition period where systems may need to support both DDR4 and DDR5 technologies. This requires comprehensive validation across diverse hardware configurations and firmware versions to ensure seamless integration.

Performance characterization under varied workloads constitutes perhaps the most significant testing objective. Storage solutions experience highly variable access patterns depending on application requirements, from sequential large-block transfers to random small-block operations. Testing protocols must accurately model these diverse scenarios to provide meaningful performance metrics that translate to real-world advantages.

Long-term reliability testing gains prominence with DDR5, as enterprise storage solutions typically demand extended operational lifespans. Accelerated aging tests, stress testing under maximum loads, and environmental variation testing become essential components of comprehensive validation methodologies.

The historical trajectory of DDR technology shows consistent progression in transfer rates, from DDR4's maximum of 3200 MT/s to DDR5's initial offerings at 4800 MT/s and roadmaps extending to 8400 MT/s. This represents more than a doubling of bandwidth capability, critical for high-performance storage applications where data movement between memory and processing units often constrains overall system performance.

Beyond raw speed improvements, DDR5 introduces architectural innovations including dual-channel architecture per DIMM, on-die ECC, and improved power management through voltage regulation moved from motherboards to memory modules. These advancements collectively support the technical objectives of modern storage solutions: increased reliability, reduced latency, and enhanced throughput for massive parallel operations.

The testing objectives for DDR5 in storage contexts must address several dimensions simultaneously. First, signal integrity testing becomes more complex with higher frequencies, requiring advanced methodologies to ensure reliable operation at increased speeds. Second, power delivery and thermal management testing gains importance as DDR5 modules operate with tighter tolerances and potentially higher power density.

Compatibility testing represents another critical objective, particularly during the transition period where systems may need to support both DDR4 and DDR5 technologies. This requires comprehensive validation across diverse hardware configurations and firmware versions to ensure seamless integration.

Performance characterization under varied workloads constitutes perhaps the most significant testing objective. Storage solutions experience highly variable access patterns depending on application requirements, from sequential large-block transfers to random small-block operations. Testing protocols must accurately model these diverse scenarios to provide meaningful performance metrics that translate to real-world advantages.

Long-term reliability testing gains prominence with DDR5, as enterprise storage solutions typically demand extended operational lifespans. Accelerated aging tests, stress testing under maximum loads, and environmental variation testing become essential components of comprehensive validation methodologies.

Market Demand for High-Performance Storage

The global demand for high-performance storage solutions has experienced unprecedented growth in recent years, primarily driven by the exponential increase in data generation across various sectors. Enterprise data centers, cloud service providers, and hyperscale computing facilities are continuously seeking storage technologies that can handle massive data volumes while maintaining low latency and high throughput performance. This market expansion is particularly evident in industries such as artificial intelligence, machine learning, big data analytics, and high-definition content creation.

DDR5 memory, as the latest generation of dynamic random-access memory technology, represents a significant advancement in addressing these high-performance storage requirements. Market research indicates that the global DDR5 market is projected to grow substantially through 2028, with enterprise storage solutions representing one of the fastest-growing segments. The transition from DDR4 to DDR5 is accelerating as organizations recognize the performance benefits, particularly in data-intensive applications where memory bandwidth becomes a critical bottleneck.

The demand for robust DDR5 testing protocols stems directly from the increasing reliability requirements in enterprise environments. Data center operators report that memory-related failures account for a significant percentage of system downtime incidents, making comprehensive testing protocols essential for maintaining operational continuity. Furthermore, as storage solutions become more integrated with computational resources in modern architectures, the performance characteristics of memory subsystems have become increasingly critical to overall system performance.

Financial services, healthcare, and telecommunications sectors demonstrate particularly strong demand for high-performance storage with rigorous testing protocols. These industries handle sensitive data where system failures can have severe consequences, ranging from financial losses to compromised patient care. The regulatory environment in these sectors also mandates higher reliability standards, further driving the need for comprehensive DDR5 testing methodologies.

From a geographical perspective, North America and Asia-Pacific regions lead in the adoption of high-performance storage technologies, with Europe following closely. The Asia-Pacific region, particularly China, Taiwan, and South Korea, shows the fastest growth rate due to the concentration of semiconductor manufacturing facilities and increasing investments in digital infrastructure. This regional distribution of demand influences the development of testing protocols that must address diverse operational environments and compliance requirements.

The market also shows a clear trend toward storage solutions that optimize power efficiency alongside performance metrics. As data centers face increasing pressure to reduce energy consumption, DDR5 technologies that deliver higher performance per watt are gaining market share. This trend necessitates testing protocols that evaluate not only raw performance but also energy efficiency characteristics under various workload conditions.

DDR5 memory, as the latest generation of dynamic random-access memory technology, represents a significant advancement in addressing these high-performance storage requirements. Market research indicates that the global DDR5 market is projected to grow substantially through 2028, with enterprise storage solutions representing one of the fastest-growing segments. The transition from DDR4 to DDR5 is accelerating as organizations recognize the performance benefits, particularly in data-intensive applications where memory bandwidth becomes a critical bottleneck.

The demand for robust DDR5 testing protocols stems directly from the increasing reliability requirements in enterprise environments. Data center operators report that memory-related failures account for a significant percentage of system downtime incidents, making comprehensive testing protocols essential for maintaining operational continuity. Furthermore, as storage solutions become more integrated with computational resources in modern architectures, the performance characteristics of memory subsystems have become increasingly critical to overall system performance.

Financial services, healthcare, and telecommunications sectors demonstrate particularly strong demand for high-performance storage with rigorous testing protocols. These industries handle sensitive data where system failures can have severe consequences, ranging from financial losses to compromised patient care. The regulatory environment in these sectors also mandates higher reliability standards, further driving the need for comprehensive DDR5 testing methodologies.

From a geographical perspective, North America and Asia-Pacific regions lead in the adoption of high-performance storage technologies, with Europe following closely. The Asia-Pacific region, particularly China, Taiwan, and South Korea, shows the fastest growth rate due to the concentration of semiconductor manufacturing facilities and increasing investments in digital infrastructure. This regional distribution of demand influences the development of testing protocols that must address diverse operational environments and compliance requirements.

The market also shows a clear trend toward storage solutions that optimize power efficiency alongside performance metrics. As data centers face increasing pressure to reduce energy consumption, DDR5 technologies that deliver higher performance per watt are gaining market share. This trend necessitates testing protocols that evaluate not only raw performance but also energy efficiency characteristics under various workload conditions.

DDR5 Testing Challenges and Limitations

Despite the significant advancements in DDR5 memory technology, testing protocols for high-performance storage solutions face numerous challenges and limitations. The increased operating frequencies of DDR5 (up to 6400 MT/s and beyond) create substantial signal integrity issues during testing procedures. Traditional testing methodologies struggle with accurately measuring and validating signals at these elevated speeds, leading to potential false positives or missed defects.

Power management testing presents another significant challenge, as DDR5's sophisticated voltage regulation architecture with on-DIMM power management IC (PMIC) requires complex test scenarios to verify proper operation across various power states and transitions. The decentralized power delivery system introduces additional variables that must be accounted for in comprehensive testing protocols.

Thermal considerations have become increasingly critical in DDR5 testing. The higher operating frequencies generate more heat, necessitating advanced thermal testing methodologies to ensure reliable operation under various thermal conditions. Current testing equipment often lacks the capability to accurately simulate real-world thermal environments while maintaining precise electrical measurements.

The complexity of DDR5's error correction code (ECC) functionality presents unique verification challenges. Testing must now verify not only data integrity but also the proper functioning of on-die ECC mechanisms, requiring more sophisticated test patterns and analysis tools than were needed for previous memory generations. Many existing automated test equipment (ATE) platforms require significant upgrades to handle these requirements.

Channel utilization testing has become more complex with DDR5's dual-channel architecture. Verifying proper operation across both sub-channels simultaneously while maintaining signal integrity presents technical difficulties that current testing methodologies struggle to address effectively. The increased number of test cases required to validate all operational modes exponentially increases testing time and complexity.

Compatibility testing across different vendor implementations poses another significant limitation. With DDR5's more complex initialization sequences and training procedures, ensuring interoperability between memory controllers from different manufacturers and various DDR5 modules requires extensive testing matrices that are time-consuming and resource-intensive.

Finally, the industry faces a shortage of standardized testing methodologies specifically optimized for DDR5 high-performance storage applications. While JEDEC provides baseline specifications, specialized testing protocols for storage-specific use cases remain underdeveloped, leading to inconsistent validation approaches across the industry and potential reliability issues in deployed systems.

Power management testing presents another significant challenge, as DDR5's sophisticated voltage regulation architecture with on-DIMM power management IC (PMIC) requires complex test scenarios to verify proper operation across various power states and transitions. The decentralized power delivery system introduces additional variables that must be accounted for in comprehensive testing protocols.

Thermal considerations have become increasingly critical in DDR5 testing. The higher operating frequencies generate more heat, necessitating advanced thermal testing methodologies to ensure reliable operation under various thermal conditions. Current testing equipment often lacks the capability to accurately simulate real-world thermal environments while maintaining precise electrical measurements.

The complexity of DDR5's error correction code (ECC) functionality presents unique verification challenges. Testing must now verify not only data integrity but also the proper functioning of on-die ECC mechanisms, requiring more sophisticated test patterns and analysis tools than were needed for previous memory generations. Many existing automated test equipment (ATE) platforms require significant upgrades to handle these requirements.

Channel utilization testing has become more complex with DDR5's dual-channel architecture. Verifying proper operation across both sub-channels simultaneously while maintaining signal integrity presents technical difficulties that current testing methodologies struggle to address effectively. The increased number of test cases required to validate all operational modes exponentially increases testing time and complexity.

Compatibility testing across different vendor implementations poses another significant limitation. With DDR5's more complex initialization sequences and training procedures, ensuring interoperability between memory controllers from different manufacturers and various DDR5 modules requires extensive testing matrices that are time-consuming and resource-intensive.

Finally, the industry faces a shortage of standardized testing methodologies specifically optimized for DDR5 high-performance storage applications. While JEDEC provides baseline specifications, specialized testing protocols for storage-specific use cases remain underdeveloped, leading to inconsistent validation approaches across the industry and potential reliability issues in deployed systems.

Current DDR5 Testing Methodologies

01 DDR5 Memory Testing Methodologies

Testing methodologies specifically designed for DDR5 memory involve comprehensive protocols to verify performance, stability, and compliance with specifications. These methodologies include signal integrity testing, timing parameter verification, and stress testing under various operating conditions. Advanced testing frameworks enable validation of high-speed data transfer rates, power efficiency, and compatibility with different system configurations.- DDR5 Memory Testing Methodologies: Testing methodologies specifically designed for DDR5 memory modules that include protocols for verifying data integrity, timing parameters, and signal integrity. These methodologies incorporate specialized test patterns and algorithms to validate the higher speeds and improved power efficiency of DDR5 compared to previous memory generations. The testing protocols ensure compatibility with various system configurations and validate compliance with DDR5 specifications.

- Automated Testing Systems for High-Speed Memory: Automated testing systems designed specifically for high-speed memory interfaces like DDR5. These systems include hardware and software components that can execute comprehensive test suites to verify memory performance, reliability, and compliance with standards. The testing protocols incorporate real-time monitoring, error detection, and analysis capabilities to identify potential issues in memory operation under various conditions and workloads.

- Signal Integrity and Error Detection Protocols: Testing protocols focused on signal integrity verification and error detection mechanisms for DDR5 memory interfaces. These protocols include methods for measuring signal quality, timing margins, and voltage levels at high speeds. They also incorporate advanced error detection and correction techniques to ensure data reliability. The testing methodologies validate the robustness of DDR5 interfaces under various operating conditions including temperature variations and voltage fluctuations.

- Performance and Stress Testing Frameworks: Comprehensive frameworks for performance and stress testing of DDR5 memory systems. These protocols include methods for measuring throughput, latency, and power consumption under various workloads. The testing methodologies incorporate stress testing to validate memory behavior under extreme conditions, including maximum bandwidth utilization, thermal stress, and extended operation periods. These frameworks help identify performance bottlenecks and stability issues in DDR5 implementations.

- Compliance and Interoperability Testing: Testing protocols designed to verify DDR5 compliance with industry standards and interoperability with various system components. These methodologies include verification of electrical specifications, timing parameters, and command protocols as defined in the DDR5 standard. The testing procedures ensure that memory modules from different manufacturers can work together reliably and that they function correctly with various memory controllers and system configurations.

02 Automated Test Equipment for Memory Interfaces

Specialized automated test equipment designed for memory interfaces, including DDR5, provides capabilities for high-precision timing measurements, voltage margin testing, and error detection. These systems incorporate calibration procedures, reference clock generation, and programmable test patterns to thoroughly evaluate memory performance. The equipment supports both manufacturing testing and design validation phases with configurable test parameters.Expand Specific Solutions03 Protocol Compliance and Interoperability Testing

Testing protocols for DDR5 memory focus on verifying compliance with industry standards and ensuring interoperability across different platforms. These protocols include verification of command sequences, addressing schemes, and refresh operations. Testing procedures validate proper initialization sequences, mode register settings, and response to training patterns, ensuring reliable operation in diverse system environments.Expand Specific Solutions04 Error Detection and Recovery Mechanisms

Testing protocols for error detection and recovery mechanisms in DDR5 memory systems evaluate the effectiveness of error correction codes, retry mechanisms, and fault tolerance features. These tests simulate various error conditions to verify system resilience and data integrity preservation. The protocols include verification of on-die ECC functionality, cyclic redundancy checks, and system-level error handling capabilities.Expand Specific Solutions05 Power Management and Thermal Testing

Testing protocols for DDR5 memory power management features evaluate efficiency across different operating modes and verify thermal characteristics under various workloads. These tests measure power consumption during active, idle, and self-refresh states, and validate proper implementation of voltage regulation and power state transitions. Thermal testing assesses heat dissipation patterns and verifies thermal throttling mechanisms to ensure reliable operation under stress conditions.Expand Specific Solutions

Key Industry Players in DDR5 Testing

The DDR5 testing protocols market for high-performance storage solutions is currently in a growth phase, with an expanding market size driven by increasing demand for faster, more reliable memory solutions. The technology maturity varies across key players, with established semiconductor giants like Micron Technology, Samsung Electronics, and Intel leading innovation with comprehensive testing frameworks. Chinese companies including ChangXin Memory Technologies and Huawei are rapidly advancing their capabilities, narrowing the technology gap. Academic institutions such as the National University of Defense Technology and Huazhong University collaborate with industry partners to develop standardized protocols. The competitive landscape features traditional memory manufacturers competing with emerging specialized testing solution providers, creating a dynamic ecosystem balancing established expertise with innovative approaches to DDR5 validation methodologies.

ChangXin Memory Technologies, Inc.

Technical Solution: ChangXin Memory Technologies has developed a multi-phase DDR5 testing protocol specifically optimized for high-density storage applications. Their methodology incorporates parallel test vectors that simultaneously evaluate multiple DDR5 modules under varying workloads to accelerate validation cycles. The company's approach features proprietary algorithms for power integrity analysis that monitor voltage fluctuations across different memory access patterns, critical for maintaining data integrity in high-performance storage solutions. ChangXin's testing framework includes specialized jitter tolerance measurements that evaluate performance degradation under adverse signal conditions, ensuring robust operation in enterprise environments. Their protocol also implements advanced thermal profiling techniques that map heat distribution across memory modules during intensive I/O operations, identifying potential reliability issues before deployment. Additionally, they've developed automated regression testing tools that continuously validate firmware updates against established performance baselines.

Strengths: Deep expertise in memory manufacturing with testing protocols specifically optimized for Chinese market requirements and domestic storage solutions. Weaknesses: Less established global presence compared to competitors, potentially limiting the adoption of their testing standards in international markets.

Micron Technology, Inc.

Technical Solution: Micron has developed comprehensive DDR5 testing protocols that incorporate multi-level signal integrity validation across various operating conditions. Their approach includes advanced eye diagram analysis techniques that evaluate signal margins at multiple voltage thresholds, allowing for precise characterization of DDR5 memory performance in high-performance storage applications. Micron's testing methodology implements specialized algorithms for detecting subtle timing violations that might only manifest under specific workload patterns. Their protocol includes automated stress testing that cycles through temperature variations while monitoring performance parameters, ensuring reliability in enterprise storage environments. Additionally, Micron has pioneered on-die ECC verification methods specifically designed for DDR5's higher frequencies and decision feedback equalization testing to validate signal integrity at speeds exceeding 6400 MT/s.

Strengths: Industry-leading expertise in memory technology with extensive validation infrastructure; comprehensive approach that addresses both electrical and thermal aspects of DDR5 testing. Weaknesses: Their testing protocols may require specialized equipment that increases implementation costs for smaller storage solution providers.

Critical DDR5 Testing Patents and Standards

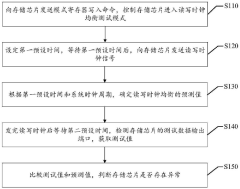

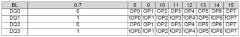

Memory chip testing method and device, medium and equipment

PatentPendingCN117352035A

Innovation

- By sending a mode register write command to the memory chip, it is controlled to enter the read and write clock balance test mode, the preset time is set to send the read and write clock signals, the predicted value is determined based on the system clock cycle, and the test value and the predicted value are compared to determine the storage Is there any abnormality in the chip?

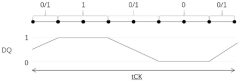

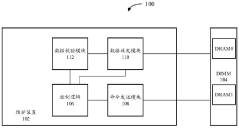

Maintenance device, method, equipment and storage medium for maintaining DDR5 memory subsystem

PatentActiveCN112349342B

Innovation

- By introducing a data verification module into the DDR5 memory subsystem, the mode register read command (MRR) is used to read the DQ data of the DDR5 memory, perform data grouping and XOR operations, and verify the correctness of the DQ data to ensure that it is based on correct data. Maintain the memory subsystem to avoid incorrect operations caused by direct dependence on the DQ signal.

Compliance and Certification Requirements

Compliance with industry standards and regulatory requirements is paramount for DDR5 memory technologies in high-performance storage solutions. The JEDEC Solid State Technology Association has established comprehensive specifications for DDR5 that manufacturers must adhere to, including electrical characteristics, timing parameters, and physical dimensions. These specifications ensure interoperability across different platforms and systems, which is critical for enterprise storage solutions where reliability is non-negotiable.

Testing protocols for DDR5 memory must align with multiple certification frameworks. The primary certification requirement comes from JEDEC's JESD79-5 standard, which outlines the fundamental compliance parameters for DDR5 SDRAM. Additionally, storage solutions incorporating DDR5 technology must often meet UL/CSA safety standards, FCC electromagnetic compatibility requirements in the United States, and CE marking criteria for European markets.

Environmental compliance testing represents another critical dimension of DDR5 certification. This includes RoHS (Restriction of Hazardous Substances) and REACH (Registration, Evaluation, Authorization and Restriction of Chemicals) compliance for materials used in memory modules. For high-performance storage applications, additional testing for temperature tolerance, humidity resistance, and vibration endurance is mandatory according to standards like MIL-STD-810 or JEDEC's JESD22 environmental test methods.

Performance validation constitutes a significant portion of compliance requirements. DDR5 modules must undergo rigorous testing to verify data transfer rates, which have doubled compared to DDR4, reaching up to 6400 MT/s in initial implementations. Signal integrity testing becomes increasingly important at these higher frequencies, with eye diagram analysis and jitter measurements forming essential components of the certification process.

Security certification requirements have gained prominence with DDR5, particularly for enterprise storage solutions. The on-die ECC (Error Correction Code) feature of DDR5 must be validated according to specific bit error rate standards. Additionally, storage solutions implementing DDR5 with security features may require certification against common criteria protection profiles or FIPS 140-3 for cryptographic modules if they incorporate encryption capabilities.

Interoperability certification ensures that DDR5 memory functions correctly across different system configurations. This involves testing with various chipsets, processors, and motherboards from different manufacturers. The CMTL (Computer Memory Test Labs) and Intel Platform Validation programs provide standardized testing methodologies for this purpose, offering certification that the memory will function reliably in specified system environments.

Testing protocols for DDR5 memory must align with multiple certification frameworks. The primary certification requirement comes from JEDEC's JESD79-5 standard, which outlines the fundamental compliance parameters for DDR5 SDRAM. Additionally, storage solutions incorporating DDR5 technology must often meet UL/CSA safety standards, FCC electromagnetic compatibility requirements in the United States, and CE marking criteria for European markets.

Environmental compliance testing represents another critical dimension of DDR5 certification. This includes RoHS (Restriction of Hazardous Substances) and REACH (Registration, Evaluation, Authorization and Restriction of Chemicals) compliance for materials used in memory modules. For high-performance storage applications, additional testing for temperature tolerance, humidity resistance, and vibration endurance is mandatory according to standards like MIL-STD-810 or JEDEC's JESD22 environmental test methods.

Performance validation constitutes a significant portion of compliance requirements. DDR5 modules must undergo rigorous testing to verify data transfer rates, which have doubled compared to DDR4, reaching up to 6400 MT/s in initial implementations. Signal integrity testing becomes increasingly important at these higher frequencies, with eye diagram analysis and jitter measurements forming essential components of the certification process.

Security certification requirements have gained prominence with DDR5, particularly for enterprise storage solutions. The on-die ECC (Error Correction Code) feature of DDR5 must be validated according to specific bit error rate standards. Additionally, storage solutions implementing DDR5 with security features may require certification against common criteria protection profiles or FIPS 140-3 for cryptographic modules if they incorporate encryption capabilities.

Interoperability certification ensures that DDR5 memory functions correctly across different system configurations. This involves testing with various chipsets, processors, and motherboards from different manufacturers. The CMTL (Computer Memory Test Labs) and Intel Platform Validation programs provide standardized testing methodologies for this purpose, offering certification that the memory will function reliably in specified system environments.

Power Efficiency and Thermal Management

Power efficiency and thermal management represent critical considerations in DDR5 testing protocols for high-performance storage solutions. DDR5 memory operates at significantly higher frequencies than its predecessors, with data rates reaching 4800-6400 MT/s in current implementations and roadmaps extending to 8400 MT/s. This performance increase naturally results in elevated power consumption and heat generation, necessitating sophisticated testing methodologies to ensure reliable operation within thermal constraints.

The power architecture of DDR5 has undergone substantial changes, moving from a memory controller-based power management to on-module voltage regulation. This shift requires comprehensive testing protocols that evaluate both the efficiency of the voltage regulation modules (VRMs) and their impact on overall system power consumption. Testing must verify that the on-die power management features, including multiple voltage domains and fine-grained refresh controls, function correctly across various workloads and environmental conditions.

Thermal testing for DDR5 memory in storage applications presents unique challenges due to the dense packaging requirements of modern storage solutions. Test protocols must account for the thermal characteristics of DDR5 modules operating in confined spaces with limited airflow, particularly in edge storage devices and high-density server environments. Temperature gradient mapping across memory modules during sustained high-bandwidth operations has become a standard component of comprehensive DDR5 testing regimes.

Advanced testing methodologies now incorporate real-time power and thermal monitoring during performance benchmarks. These approaches utilize embedded thermal sensors within DDR5 modules to collect granular temperature data while simultaneously measuring power consumption at various load levels. The correlation between power efficiency metrics and thermal profiles provides valuable insights into the sustainability of memory performance under extended workloads typical in storage applications.

Testing protocols must also evaluate the effectiveness of DDR5's enhanced power management features, including the new Decision Feedback Equalization (DFE) circuits that optimize signal integrity while minimizing power consumption. The dynamic voltage and frequency scaling capabilities require specialized test sequences that verify proper operation across the entire range of power states, ensuring that transitions between power modes occur without data corruption or performance degradation.

For enterprise storage solutions, DDR5 testing must additionally verify compliance with data center efficiency standards and thermal design power (TDP) specifications. This includes stress testing under maximum power consumption scenarios to validate thermal management systems and ensure that memory modules can maintain data integrity even under worst-case thermal conditions. The testing protocols increasingly incorporate accelerated life testing methodologies to predict long-term reliability under various thermal and power cycling conditions.

The power architecture of DDR5 has undergone substantial changes, moving from a memory controller-based power management to on-module voltage regulation. This shift requires comprehensive testing protocols that evaluate both the efficiency of the voltage regulation modules (VRMs) and their impact on overall system power consumption. Testing must verify that the on-die power management features, including multiple voltage domains and fine-grained refresh controls, function correctly across various workloads and environmental conditions.

Thermal testing for DDR5 memory in storage applications presents unique challenges due to the dense packaging requirements of modern storage solutions. Test protocols must account for the thermal characteristics of DDR5 modules operating in confined spaces with limited airflow, particularly in edge storage devices and high-density server environments. Temperature gradient mapping across memory modules during sustained high-bandwidth operations has become a standard component of comprehensive DDR5 testing regimes.

Advanced testing methodologies now incorporate real-time power and thermal monitoring during performance benchmarks. These approaches utilize embedded thermal sensors within DDR5 modules to collect granular temperature data while simultaneously measuring power consumption at various load levels. The correlation between power efficiency metrics and thermal profiles provides valuable insights into the sustainability of memory performance under extended workloads typical in storage applications.

Testing protocols must also evaluate the effectiveness of DDR5's enhanced power management features, including the new Decision Feedback Equalization (DFE) circuits that optimize signal integrity while minimizing power consumption. The dynamic voltage and frequency scaling capabilities require specialized test sequences that verify proper operation across the entire range of power states, ensuring that transitions between power modes occur without data corruption or performance degradation.

For enterprise storage solutions, DDR5 testing must additionally verify compliance with data center efficiency standards and thermal design power (TDP) specifications. This includes stress testing under maximum power consumption scenarios to validate thermal management systems and ensure that memory modules can maintain data integrity even under worst-case thermal conditions. The testing protocols increasingly incorporate accelerated life testing methodologies to predict long-term reliability under various thermal and power cycling conditions.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!