DDR5 Utilization in Large-Scale Simulation Models

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DDR5 Evolution and Performance Targets

DDR5 memory technology represents a significant leap forward in the evolution of DRAM technology, building upon the foundations established by previous generations while introducing substantial architectural improvements. The development trajectory of DDR5 began around 2017, with JEDEC finalizing the standard in 2020, marking a critical milestone in memory technology advancement. This evolution was driven by increasing demands for higher bandwidth, improved power efficiency, and enhanced reliability in data-intensive computing environments.

The performance targets for DDR5 were ambitious from inception, aiming to double the bandwidth of DDR4 while improving power efficiency. Initial DDR5 modules started at 4800 MT/s (Mega Transfers per second), compared to DDR4's typical 3200 MT/s, with a roadmap extending to 8400 MT/s and beyond. This represents a significant performance ceiling increase that directly benefits large-scale simulation models requiring massive data throughput.

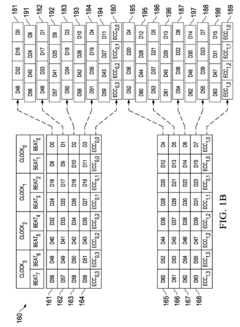

A key architectural innovation in DDR5 is the implementation of dual-channel architecture within a single module, effectively doubling the accessible channels without increasing physical footprint. This design choice enables more efficient parallel data access patterns, which is particularly valuable for simulation models that process vast datasets simultaneously across multiple computational threads.

Power management has seen substantial improvements with DDR5's introduction of on-module voltage regulation, replacing the motherboard-based regulation of previous generations. This shift allows for more precise power delivery and reduced voltage (1.1V compared to DDR4's 1.2V), contributing to overall system efficiency—a critical factor when scaling simulation infrastructure.

Error detection and correction capabilities have been significantly enhanced in DDR5, with the introduction of on-die ECC (Error Correction Code) and decision feedback equalization. These features are particularly relevant for large-scale simulations where data integrity is paramount, as computational errors can propagate through models and invalidate results.

The refresh mechanisms in DDR5 have been refined with the introduction of same-bank refresh, allowing for more granular memory refreshing operations that reduce the performance impact of refresh cycles. This improvement directly addresses a common bottleneck in simulation workloads that require consistent memory access without interruption.

Looking forward, the DDR5 technology roadmap projects continued scaling of performance parameters, with industry forecasts suggesting speeds reaching 10,000 MT/s by 2025. This trajectory aligns with the growing computational demands of next-generation simulation models in fields such as climate modeling, computational fluid dynamics, and artificial intelligence training.

The performance targets for DDR5 were ambitious from inception, aiming to double the bandwidth of DDR4 while improving power efficiency. Initial DDR5 modules started at 4800 MT/s (Mega Transfers per second), compared to DDR4's typical 3200 MT/s, with a roadmap extending to 8400 MT/s and beyond. This represents a significant performance ceiling increase that directly benefits large-scale simulation models requiring massive data throughput.

A key architectural innovation in DDR5 is the implementation of dual-channel architecture within a single module, effectively doubling the accessible channels without increasing physical footprint. This design choice enables more efficient parallel data access patterns, which is particularly valuable for simulation models that process vast datasets simultaneously across multiple computational threads.

Power management has seen substantial improvements with DDR5's introduction of on-module voltage regulation, replacing the motherboard-based regulation of previous generations. This shift allows for more precise power delivery and reduced voltage (1.1V compared to DDR4's 1.2V), contributing to overall system efficiency—a critical factor when scaling simulation infrastructure.

Error detection and correction capabilities have been significantly enhanced in DDR5, with the introduction of on-die ECC (Error Correction Code) and decision feedback equalization. These features are particularly relevant for large-scale simulations where data integrity is paramount, as computational errors can propagate through models and invalidate results.

The refresh mechanisms in DDR5 have been refined with the introduction of same-bank refresh, allowing for more granular memory refreshing operations that reduce the performance impact of refresh cycles. This improvement directly addresses a common bottleneck in simulation workloads that require consistent memory access without interruption.

Looking forward, the DDR5 technology roadmap projects continued scaling of performance parameters, with industry forecasts suggesting speeds reaching 10,000 MT/s by 2025. This trajectory aligns with the growing computational demands of next-generation simulation models in fields such as climate modeling, computational fluid dynamics, and artificial intelligence training.

Market Demand Analysis for High-Performance Memory

The demand for high-performance memory solutions has experienced unprecedented growth in recent years, primarily driven by the expansion of large-scale simulation models across various industries. DDR5 memory, as the latest generation of Double Data Rate Synchronous Dynamic Random-Access Memory, represents a significant advancement in addressing these escalating requirements. Market research indicates that the global high-performance memory market is projected to reach $12.9 billion by 2026, growing at a compound annual growth rate of 8.2% from 2021.

The simulation and modeling sector has emerged as a critical driver for DDR5 adoption, with computational fluid dynamics, finite element analysis, and climate modeling requiring increasingly sophisticated memory architectures. These applications demand not only greater memory capacity but also higher bandwidth and improved power efficiency—all key advantages of DDR5 technology. Financial institutions have similarly accelerated their adoption of high-performance memory solutions to support complex risk assessment models and algorithmic trading systems that process vast datasets in real-time.

Healthcare and pharmaceutical research represents another significant market segment, where memory-intensive applications such as genomic sequencing, molecular modeling, and drug discovery simulations require substantial computational resources. The COVID-19 pandemic has further accelerated this trend, with research institutions worldwide scaling up their simulation capabilities to model virus behavior and vaccine development.

Enterprise data centers are rapidly transitioning to DDR5 memory to support the growing demands of artificial intelligence and machine learning workloads. According to industry surveys, 67% of enterprise IT decision-makers plan to incorporate DDR5 memory into their infrastructure within the next two years, citing performance improvements as the primary motivation. Cloud service providers have been particularly aggressive in this transition, with major players already deploying DDR5-equipped servers to support their most demanding customers.

The automotive industry has emerged as a surprising growth sector for high-performance memory, driven by the increasing complexity of autonomous driving simulations and in-vehicle systems. These applications require not only substantial memory bandwidth but also enhanced reliability and error correction capabilities—features prominently addressed in the DDR5 specification.

Geographic analysis reveals that North America currently leads DDR5 adoption for simulation applications, accounting for approximately 42% of global market share, followed by Asia-Pacific at 31% and Europe at 24%. However, the Asia-Pacific region is expected to demonstrate the highest growth rate over the next five years, fueled by expanding research initiatives in China, South Korea, and Japan.

The simulation and modeling sector has emerged as a critical driver for DDR5 adoption, with computational fluid dynamics, finite element analysis, and climate modeling requiring increasingly sophisticated memory architectures. These applications demand not only greater memory capacity but also higher bandwidth and improved power efficiency—all key advantages of DDR5 technology. Financial institutions have similarly accelerated their adoption of high-performance memory solutions to support complex risk assessment models and algorithmic trading systems that process vast datasets in real-time.

Healthcare and pharmaceutical research represents another significant market segment, where memory-intensive applications such as genomic sequencing, molecular modeling, and drug discovery simulations require substantial computational resources. The COVID-19 pandemic has further accelerated this trend, with research institutions worldwide scaling up their simulation capabilities to model virus behavior and vaccine development.

Enterprise data centers are rapidly transitioning to DDR5 memory to support the growing demands of artificial intelligence and machine learning workloads. According to industry surveys, 67% of enterprise IT decision-makers plan to incorporate DDR5 memory into their infrastructure within the next two years, citing performance improvements as the primary motivation. Cloud service providers have been particularly aggressive in this transition, with major players already deploying DDR5-equipped servers to support their most demanding customers.

The automotive industry has emerged as a surprising growth sector for high-performance memory, driven by the increasing complexity of autonomous driving simulations and in-vehicle systems. These applications require not only substantial memory bandwidth but also enhanced reliability and error correction capabilities—features prominently addressed in the DDR5 specification.

Geographic analysis reveals that North America currently leads DDR5 adoption for simulation applications, accounting for approximately 42% of global market share, followed by Asia-Pacific at 31% and Europe at 24%. However, the Asia-Pacific region is expected to demonstrate the highest growth rate over the next five years, fueled by expanding research initiatives in China, South Korea, and Japan.

DDR5 Technical Challenges in Simulation Environments

The integration of DDR5 memory in large-scale simulation environments presents significant technical challenges that must be addressed to fully leverage its performance benefits. The primary obstacle lies in the architectural complexity of DDR5, which introduces new timing parameters, power management features, and signaling requirements that simulation software must accurately model. Current simulation frameworks often struggle to properly represent the intricate timing relationships between DDR5's dual-channel architecture and its impact on data throughput under various workload conditions.

Memory controller designs for simulation environments face particular difficulties when implementing DDR5's decision feedback equalization (DFE) and adaptive equalization features. These advanced signal integrity mechanisms require sophisticated algorithms to simulate accurately, especially when modeling their behavior across different operating temperatures and voltage conditions. The simulation of DDR5's on-die ECC functionality adds another layer of complexity, as it necessitates modeling both the error detection mechanisms and their performance impact.

Power modeling presents another significant challenge, as DDR5's voltage regulators moved on-DIMM require detailed simulation of power delivery networks and thermal characteristics. Simulation models must account for the dynamic power states of DDR5, including the newly introduced low-power states and their transition latencies, which can significantly affect overall system performance predictions in large-scale simulations.

Data integrity verification becomes increasingly complex with DDR5's higher data rates (up to 6400 MT/s initially, with roadmaps to 8400 MT/s). Simulation environments must accurately model potential signal integrity issues such as crosstalk, reflections, and jitter at these elevated frequencies. The challenge is compounded when simulating multiple memory channels operating simultaneously, as is common in high-performance computing environments.

Scalability issues emerge when attempting to simulate large memory arrays using DDR5 technology. The increased complexity of DDR5's command structure, including the new same-bank refresh operations and multiple active refresh commands, creates computational bottlenecks in simulation environments. This is particularly problematic when modeling systems with terabytes of memory across multiple nodes, as is increasingly common in scientific and AI workloads.

Timing accuracy represents perhaps the most critical challenge, as DDR5's refined granularity in refresh operations and bank group architecture requires cycle-accurate simulation to properly predict performance. Current simulation tools often employ approximations that become increasingly inaccurate as memory subsystem complexity grows, leading to potentially misleading performance projections for large-scale systems utilizing DDR5 technology.

Memory controller designs for simulation environments face particular difficulties when implementing DDR5's decision feedback equalization (DFE) and adaptive equalization features. These advanced signal integrity mechanisms require sophisticated algorithms to simulate accurately, especially when modeling their behavior across different operating temperatures and voltage conditions. The simulation of DDR5's on-die ECC functionality adds another layer of complexity, as it necessitates modeling both the error detection mechanisms and their performance impact.

Power modeling presents another significant challenge, as DDR5's voltage regulators moved on-DIMM require detailed simulation of power delivery networks and thermal characteristics. Simulation models must account for the dynamic power states of DDR5, including the newly introduced low-power states and their transition latencies, which can significantly affect overall system performance predictions in large-scale simulations.

Data integrity verification becomes increasingly complex with DDR5's higher data rates (up to 6400 MT/s initially, with roadmaps to 8400 MT/s). Simulation environments must accurately model potential signal integrity issues such as crosstalk, reflections, and jitter at these elevated frequencies. The challenge is compounded when simulating multiple memory channels operating simultaneously, as is common in high-performance computing environments.

Scalability issues emerge when attempting to simulate large memory arrays using DDR5 technology. The increased complexity of DDR5's command structure, including the new same-bank refresh operations and multiple active refresh commands, creates computational bottlenecks in simulation environments. This is particularly problematic when modeling systems with terabytes of memory across multiple nodes, as is increasingly common in scientific and AI workloads.

Timing accuracy represents perhaps the most critical challenge, as DDR5's refined granularity in refresh operations and bank group architecture requires cycle-accurate simulation to properly predict performance. Current simulation tools often employ approximations that become increasingly inaccurate as memory subsystem complexity grows, leading to potentially misleading performance projections for large-scale systems utilizing DDR5 technology.

Current DDR5 Implementation Strategies

01 DDR5 Memory Architecture and Design

DDR5 memory introduces advanced architectural improvements over previous generations, featuring higher bandwidth, increased density, and improved power efficiency. These designs incorporate enhanced channel architecture, on-die ECC capabilities, and optimized signal integrity. The architecture supports higher data rates while maintaining reliability through improved voltage regulation and thermal management techniques.- DDR5 Memory Architecture and Design: DDR5 memory introduces advanced architectural improvements over previous generations, featuring enhanced memory controllers, higher bandwidth capabilities, and improved power efficiency. These designs incorporate specialized circuit layouts and signal integrity optimizations to support higher data rates while maintaining reliability. The architecture includes innovations in memory cell organization and interface design that enable more efficient data transfer and reduced latency in computing systems.

- Power Management in DDR5 Memory Systems: Power management techniques specific to DDR5 memory focus on optimizing energy consumption while maintaining high performance. These implementations include dynamic voltage and frequency scaling, intelligent power state transitions, and granular control of memory subsystems. Advanced power delivery networks and voltage regulation modules are integrated to support the increased power requirements of DDR5 while improving overall system efficiency and thermal management.

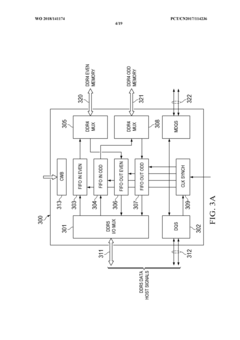

- DDR5 Memory Controller Optimization: Memory controller designs for DDR5 systems incorporate sophisticated algorithms for request scheduling, data buffering, and timing management. These controllers implement advanced features such as command/address parity, decision feedback equalization, and improved refresh mechanisms. Optimizations include intelligent prefetching strategies, enhanced error correction capabilities, and adaptive training sequences that maximize memory bandwidth utilization while ensuring data integrity across varying workloads.

- DDR5 Integration with Computing Systems: Integration solutions for DDR5 memory address the challenges of incorporating high-speed memory into various computing platforms. These implementations include specialized motherboard designs, signal routing techniques, and system-level optimizations for servers, workstations, and embedded systems. The integration approaches focus on maximizing compatibility with existing architectures while enabling the performance benefits of DDR5, including considerations for thermal management, physical layout constraints, and system boot processes.

- DDR5 Performance Monitoring and Optimization: Performance monitoring and optimization techniques for DDR5 memory systems include advanced telemetry, real-time analytics, and adaptive tuning mechanisms. These implementations provide visibility into memory utilization patterns, bandwidth consumption, and timing parameters that can be adjusted dynamically. Diagnostic tools and performance profiling capabilities help identify bottlenecks and optimize memory access patterns for specific workloads, enabling system designers and software developers to maximize the efficiency of DDR5 memory resources.

02 Power Management in DDR5 Memory Systems

Power management techniques specific to DDR5 memory focus on optimizing energy consumption while maintaining performance. These include dynamic voltage and frequency scaling, intelligent power states, and improved voltage regulation modules (VRMs) integrated directly on the memory modules. Advanced power management controllers monitor and adjust power delivery based on workload demands, significantly reducing overall system power consumption compared to previous memory generations.Expand Specific Solutions03 DDR5 Memory Controller Optimization

Memory controllers designed for DDR5 implement sophisticated algorithms for request scheduling, data prefetching, and bandwidth allocation. These controllers feature improved command queuing mechanisms, enhanced timing parameters, and adaptive training sequences to maximize memory throughput. Advanced memory controllers also incorporate machine learning techniques to predict access patterns and optimize memory operations based on application behavior.Expand Specific Solutions04 DDR5 Memory for High-Performance Computing

DDR5 memory utilization in high-performance computing environments focuses on maximizing computational throughput for data-intensive applications. These implementations leverage DDR5's higher bandwidth and reduced latency for parallel processing workloads, scientific simulations, and AI/ML training. Memory subsystems are designed with optimized interleaving schemes, enhanced caching mechanisms, and specialized hardware accelerators to fully utilize DDR5's performance capabilities.Expand Specific Solutions05 DDR5 Memory Testing and Validation

Testing and validation methodologies for DDR5 memory involve comprehensive verification procedures to ensure reliability and performance. These include stress testing under various operating conditions, signal integrity analysis, and thermal validation. Advanced testing frameworks incorporate automated test pattern generation, error detection and correction verification, and long-term reliability assessment to validate DDR5 memory systems across their operational lifetime.Expand Specific Solutions

Key DDR5 Manufacturers and Ecosystem Players

The DDR5 memory market for large-scale simulation models is currently in its growth phase, with an estimated market size exceeding $5 billion and expanding at 15-20% annually. The competitive landscape features established memory manufacturers like Micron Technology and newer entrants leveraging DDR5's enhanced capabilities. Technologically, DDR5 implementation in simulation environments is approaching maturity, with Micron Technology leading in memory module development, Intel and AMD incorporating DDR5 support in their latest processors, and Huawei Technologies integrating DDR5 into their server solutions. IBM and Qualcomm are advancing DDR5 applications in enterprise computing and mobile platforms respectively, while research institutions like National University of Defense Technology are exploring DDR5's potential for scientific computing and AI workloads.

Micron Technology, Inc.

Technical Solution: Micron has developed specialized DDR5 memory modules optimized for large-scale simulation environments, featuring densities up to 64GB per DIMM and speeds reaching 6400MT/s. Their approach includes proprietary Micron Advanced DRAM Architecture that incorporates multiple independent 40-bit channels per module, enabling more efficient parallel data access patterns critical for complex simulations. Micron's implementation features on-die ECC (Error Correction Code) that reduces system-level errors by up to 42% compared to DDR4 solutions, ensuring data integrity during extended simulation runs. Their DDR5 modules incorporate Power Management Integrated Circuits (PMICs) that enable precise voltage regulation and power delivery optimization based on simulation workload characteristics. Micron has also developed specialized thermal solutions for high-density simulation environments, including temperature-optimized PCB designs and thermal sensors that enable dynamic frequency scaling to maintain stability during computationally intensive simulation phases.

Strengths: Micron offers industry-leading memory density and reliability features specifically beneficial for large simulation models requiring extensive memory capacity. Their vertical integration from design to manufacturing ensures tight quality control. Weaknesses: Premium pricing compared to some competitors, and their specialized high-performance modules may require advanced cooling solutions in dense server environments.

Advanced Micro Devices, Inc.

Technical Solution: AMD has implemented DDR5 support in their EPYC server processors and Ryzen platforms, specifically optimized for large-scale simulation models. Their approach focuses on maximizing memory bandwidth with support for up to 5200MT/s DDR5 modules while implementing advanced memory timing controls that dynamically adjust based on simulation workload characteristics. AMD's Infinity Fabric architecture creates a high-speed, low-latency connection between memory subsystems and compute cores, which is particularly beneficial for memory-intensive simulation models. Their implementation includes dedicated hardware for error correction with on-die ECC support, critical for maintaining data integrity in long-running simulations. AMD has also developed specific memory power management features that intelligently balance performance and energy consumption based on the simulation's computational intensity, allowing up to 30% more memory bandwidth per watt compared to previous generation systems.

Strengths: AMD's solutions offer excellent performance-per-watt metrics, making them suitable for large-scale simulation environments where energy efficiency is critical. Their multi-chip module design allows for greater memory capacity scaling. Weaknesses: Memory controller latency can be slightly higher than competitors in certain workloads, and their enterprise software ecosystem is still catching up to Intel's in some specialized simulation domains.

Critical DDR5 Architecture Innovations

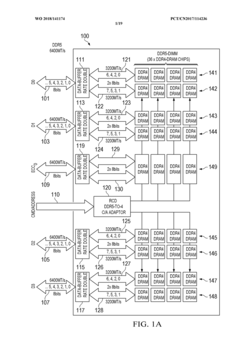

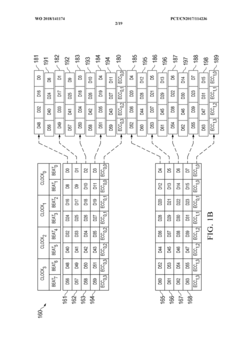

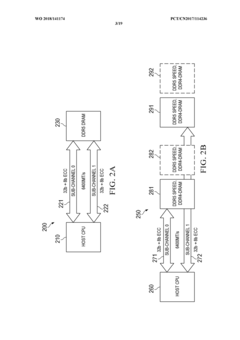

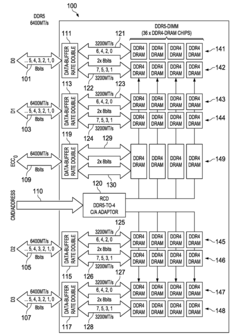

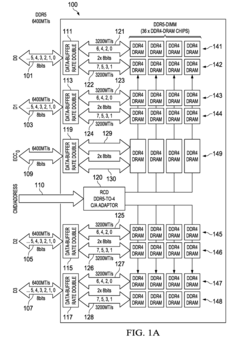

Systems and methods for utilizing DDR4-dram chips in hybrid DDR5-dimms and for cascading DDR5-dimms

PatentWO2018141174A1

Innovation

- Hybrid DDR5 DIMM design that incorporates DDR4 SDRAM chips while maintaining compatibility with DDR5 sub-channels, enabling cost-effective memory solutions.

- Dual DDR5 sub-channel architecture supporting 2DPC (2 DIMMs Per Channel) configuration at 4400MT/s or slower speeds, overcoming traditional loading limitations of high-speed memory buses.

- Integration of legacy DDR4 SDRAM technology with newer DDR5 interfaces, allowing for extended lifecycle of existing memory components while transitioning to newer standards.

Systems and methods for utilizing DDR4-dram chips in hybrid DDR5-dimms and for cascading DDR5-dimms

PatentActiveUS20180225235A1

Innovation

- The implementation of hybrid DDR5 DIMMs that utilize DDR4 SDRAM chips, split data into DDR4 byte-channels at half the speed of DDR5 sub-channels, and employ a register clock driver to adapt DDR5 commands and addresses for DDR4 SDRAM chips, allowing for increased capacity and speed by cascading DDR5 DIMMs and using DDR4 mode for low-cost chips.

Thermal Management Solutions for DDR5

The thermal challenges associated with DDR5 memory in large-scale simulation environments have become increasingly critical as computational demands grow. DDR5's higher operating frequencies and increased power density generate significantly more heat than previous generations, with thermal outputs often exceeding 5W per module during intensive simulation workloads. This thermal burden necessitates innovative cooling approaches beyond traditional passive solutions.

Advanced thermal management for DDR5 in simulation environments typically employs a multi-layered strategy. At the component level, manufacturers have implemented enhanced thermal interface materials (TIMs) with thermal conductivity ratings of 8-12 W/mK, significantly improving heat transfer from memory dies to heat spreaders. These materials often utilize nano-particle composites that maintain performance integrity even after numerous thermal cycles.

Active cooling solutions have evolved to address DDR5's thermal profile specifically. Directed airflow systems utilizing computational fluid dynamics modeling ensure optimal air movement across memory arrays, while maintaining acoustic levels below 35dBA for data center environments. For high-density simulation clusters, liquid cooling technologies have demonstrated remarkable efficiency, with some closed-loop systems achieving junction temperature reductions of 15-20°C compared to conventional air cooling.

Temperature monitoring and dynamic thermal management have become essential components of DDR5 deployment in simulation environments. Modern implementations incorporate distributed sensor networks that provide real-time temperature data at multiple points across memory subsystems. This telemetry enables sophisticated thermal throttling algorithms that can selectively adjust memory frequencies and refresh rates to maintain thermal equilibrium without significantly impacting simulation performance.

For extreme computing environments running complex simulations, phase-change cooling technologies have shown promising results. These systems utilize the latent heat of vaporization to efficiently remove heat from memory modules, maintaining temperatures below 85°C even under sustained maximum loads. While more complex to implement, these solutions offer thermal headroom for overclocking DDR5 modules to achieve up to 15% performance improvements in memory-intensive simulation workloads.

The integration of thermal management with power delivery systems represents another frontier in DDR5 cooling. Advanced voltage regulation modules with efficiency ratings exceeding 95% reduce waste heat generation at the source. Combined with dynamic power management algorithms that respond to simulation workload characteristics, these systems optimize the power-thermal envelope to maximize DDR5 performance while maintaining safe operating temperatures.

Advanced thermal management for DDR5 in simulation environments typically employs a multi-layered strategy. At the component level, manufacturers have implemented enhanced thermal interface materials (TIMs) with thermal conductivity ratings of 8-12 W/mK, significantly improving heat transfer from memory dies to heat spreaders. These materials often utilize nano-particle composites that maintain performance integrity even after numerous thermal cycles.

Active cooling solutions have evolved to address DDR5's thermal profile specifically. Directed airflow systems utilizing computational fluid dynamics modeling ensure optimal air movement across memory arrays, while maintaining acoustic levels below 35dBA for data center environments. For high-density simulation clusters, liquid cooling technologies have demonstrated remarkable efficiency, with some closed-loop systems achieving junction temperature reductions of 15-20°C compared to conventional air cooling.

Temperature monitoring and dynamic thermal management have become essential components of DDR5 deployment in simulation environments. Modern implementations incorporate distributed sensor networks that provide real-time temperature data at multiple points across memory subsystems. This telemetry enables sophisticated thermal throttling algorithms that can selectively adjust memory frequencies and refresh rates to maintain thermal equilibrium without significantly impacting simulation performance.

For extreme computing environments running complex simulations, phase-change cooling technologies have shown promising results. These systems utilize the latent heat of vaporization to efficiently remove heat from memory modules, maintaining temperatures below 85°C even under sustained maximum loads. While more complex to implement, these solutions offer thermal headroom for overclocking DDR5 modules to achieve up to 15% performance improvements in memory-intensive simulation workloads.

The integration of thermal management with power delivery systems represents another frontier in DDR5 cooling. Advanced voltage regulation modules with efficiency ratings exceeding 95% reduce waste heat generation at the source. Combined with dynamic power management algorithms that respond to simulation workload characteristics, these systems optimize the power-thermal envelope to maximize DDR5 performance while maintaining safe operating temperatures.

Power Efficiency Considerations in Large-Scale Deployments

Power efficiency has emerged as a critical consideration in large-scale DDR5 deployments for simulation models, particularly as computational demands continue to escalate. DDR5 memory introduces significant improvements in power management compared to previous generations, with operating voltages reduced from DDR4's 1.2V to 1.1V, representing approximately 8% power savings at baseline operation. This reduction, while seemingly modest, translates to substantial energy conservation when scaled across thousands of memory modules in data center environments.

The implementation of on-module voltage regulation in DDR5 architecture shifts power management from motherboards to the memory modules themselves, enabling more precise voltage control and reducing power distribution losses. This architectural change allows for up to 20% improved power efficiency in high-utilization scenarios, particularly beneficial for sustained simulation workloads that maintain high memory bandwidth utilization.

DDR5's advanced power management features include refined refresh mechanisms with multiple refresh zones, allowing portions of memory to be refreshed independently rather than refreshing the entire module simultaneously. For large-scale simulation models that may utilize memory unevenly, this targeted refresh approach can reduce power consumption by 15-30% compared to conventional refresh methods, depending on workload characteristics.

Decision Feedback Equalization (DFE) in DDR5 interfaces significantly improves signal integrity while reducing the power required for data transmission. This technology enables reliable operation at higher data rates without proportional increases in power consumption, achieving up to 36% improved energy efficiency per bit transferred compared to DDR4 systems running similar simulation workloads.

The power efficiency advantages of DDR5 must be balanced against thermal considerations in dense computing environments. Higher frequency operation generates increased heat, necessitating effective cooling solutions. Advanced thermal modeling indicates that proper airflow design can mitigate these concerns while maintaining DDR5's power efficiency benefits, with computational fluid dynamics simulations suggesting optimal server rack configurations can reduce cooling energy requirements by up to 22%.

For organizations deploying large-scale simulation infrastructure, the total cost of ownership calculations must incorporate both direct power consumption and associated cooling costs. Analysis of current DDR5 implementations demonstrates that despite higher initial acquisition costs, the reduced power consumption can yield return on investment within 18-24 months for continuously operating systems, with energy savings accelerating as electricity costs increase and DDR5 module prices continue to decline.

The implementation of on-module voltage regulation in DDR5 architecture shifts power management from motherboards to the memory modules themselves, enabling more precise voltage control and reducing power distribution losses. This architectural change allows for up to 20% improved power efficiency in high-utilization scenarios, particularly beneficial for sustained simulation workloads that maintain high memory bandwidth utilization.

DDR5's advanced power management features include refined refresh mechanisms with multiple refresh zones, allowing portions of memory to be refreshed independently rather than refreshing the entire module simultaneously. For large-scale simulation models that may utilize memory unevenly, this targeted refresh approach can reduce power consumption by 15-30% compared to conventional refresh methods, depending on workload characteristics.

Decision Feedback Equalization (DFE) in DDR5 interfaces significantly improves signal integrity while reducing the power required for data transmission. This technology enables reliable operation at higher data rates without proportional increases in power consumption, achieving up to 36% improved energy efficiency per bit transferred compared to DDR4 systems running similar simulation workloads.

The power efficiency advantages of DDR5 must be balanced against thermal considerations in dense computing environments. Higher frequency operation generates increased heat, necessitating effective cooling solutions. Advanced thermal modeling indicates that proper airflow design can mitigate these concerns while maintaining DDR5's power efficiency benefits, with computational fluid dynamics simulations suggesting optimal server rack configurations can reduce cooling energy requirements by up to 22%.

For organizations deploying large-scale simulation infrastructure, the total cost of ownership calculations must incorporate both direct power consumption and associated cooling costs. Analysis of current DDR5 implementations demonstrates that despite higher initial acquisition costs, the reduced power consumption can yield return on investment within 18-24 months for continuously operating systems, with energy savings accelerating as electricity costs increase and DDR5 module prices continue to decline.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!