DDR5 vs DDR4: Comparing Bandwidth and Speed Impact

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

DDR Memory Evolution and Performance Objectives

Double Data Rate (DDR) memory technology has undergone significant evolution since its inception, with each generation bringing substantial improvements in performance, efficiency, and capabilities. The journey from DDR4 to DDR5 represents one of the most substantial leaps in memory technology in recent years, addressing the growing demands of modern computing environments.

DDR memory evolution has been driven by the exponential increase in data processing requirements across various sectors, including high-performance computing, artificial intelligence, data centers, and consumer electronics. The transition between generations typically occurs approximately every 5-7 years, with DDR4 being introduced in 2014 and DDR5 making its commercial debut in late 2020.

The primary objectives behind DDR memory advancement have consistently focused on increasing bandwidth, reducing latency, improving power efficiency, and enhancing overall system performance. With each new generation, memory manufacturers have pushed the boundaries of what's possible in terms of data transfer rates and operational efficiency.

DDR4 technology represented a significant improvement over its predecessor, offering speeds ranging from 1600 MHz to 3200 MHz (effective rates of 2133 MT/s to 4266 MT/s). It introduced several architectural improvements, including higher bank groups, improved command structure, and enhanced power management features.

DDR5 emerges as a response to the increasing demands of data-intensive applications and the limitations of DDR4 technology. The performance objectives for DDR5 include doubling the bandwidth of DDR4, significantly reducing power consumption, improving channel efficiency, and enhancing reliability through new error correction capabilities.

Key performance targets for DDR5 include base speeds starting at 4800 MT/s with a roadmap extending to 8400 MT/s and beyond, representing a substantial increase over DDR4's capabilities. This advancement aims to address the memory bottlenecks that have become increasingly apparent in high-performance computing environments.

Beyond raw speed improvements, DDR5's objectives include better power management through voltage reduction from 1.2V to 1.1V, on-die ECC (Error Correction Code) for improved data integrity, and enhanced channel architecture with two independent 40-bit channels per DIMM instead of a single 72-bit channel.

The evolution trajectory suggests that memory technology will continue to advance toward higher densities, with DDR5 supporting up to 64Gb per die compared to DDR4's 16Gb limit. This fourfold increase enables much higher capacity memory modules, addressing the growing memory requirements of next-generation applications.

DDR memory evolution has been driven by the exponential increase in data processing requirements across various sectors, including high-performance computing, artificial intelligence, data centers, and consumer electronics. The transition between generations typically occurs approximately every 5-7 years, with DDR4 being introduced in 2014 and DDR5 making its commercial debut in late 2020.

The primary objectives behind DDR memory advancement have consistently focused on increasing bandwidth, reducing latency, improving power efficiency, and enhancing overall system performance. With each new generation, memory manufacturers have pushed the boundaries of what's possible in terms of data transfer rates and operational efficiency.

DDR4 technology represented a significant improvement over its predecessor, offering speeds ranging from 1600 MHz to 3200 MHz (effective rates of 2133 MT/s to 4266 MT/s). It introduced several architectural improvements, including higher bank groups, improved command structure, and enhanced power management features.

DDR5 emerges as a response to the increasing demands of data-intensive applications and the limitations of DDR4 technology. The performance objectives for DDR5 include doubling the bandwidth of DDR4, significantly reducing power consumption, improving channel efficiency, and enhancing reliability through new error correction capabilities.

Key performance targets for DDR5 include base speeds starting at 4800 MT/s with a roadmap extending to 8400 MT/s and beyond, representing a substantial increase over DDR4's capabilities. This advancement aims to address the memory bottlenecks that have become increasingly apparent in high-performance computing environments.

Beyond raw speed improvements, DDR5's objectives include better power management through voltage reduction from 1.2V to 1.1V, on-die ECC (Error Correction Code) for improved data integrity, and enhanced channel architecture with two independent 40-bit channels per DIMM instead of a single 72-bit channel.

The evolution trajectory suggests that memory technology will continue to advance toward higher densities, with DDR5 supporting up to 64Gb per die compared to DDR4's 16Gb limit. This fourfold increase enables much higher capacity memory modules, addressing the growing memory requirements of next-generation applications.

Market Demand Analysis for High-Bandwidth Memory

The global memory market is experiencing a significant shift towards high-bandwidth solutions, driven primarily by data-intensive applications across multiple sectors. The transition from DDR4 to DDR5 memory represents a critical evolution in addressing escalating bandwidth demands. Current market analysis indicates that data centers and cloud service providers constitute the largest segment demanding high-bandwidth memory, with projected growth rates exceeding 25% annually through 2025.

Enterprise computing environments are rapidly adopting high-bandwidth memory solutions to support increasingly complex workloads, including real-time analytics, artificial intelligence operations, and virtualized infrastructure. The financial services sector has emerged as a particularly aggressive adopter, implementing high-bandwidth memory to reduce latency in algorithmic trading platforms where nanoseconds translate directly to competitive advantage.

Consumer electronics manufacturers are incorporating DDR5 memory into premium devices, though adoption remains constrained by cost considerations. Gaming hardware represents a notable exception, with enthusiast-grade products embracing DDR5 despite price premiums due to demonstrable performance improvements in modern game engines that leverage increased bandwidth.

Market research reveals geographic variations in adoption patterns. North American and European markets show stronger enterprise-driven demand, while Asian markets display more balanced adoption across consumer and enterprise segments. China's domestic memory manufacturing initiatives have accelerated regional availability of high-bandwidth solutions, influencing pricing dynamics globally.

Supply chain analysis indicates that DDR5 production capacity is expanding rapidly, with major manufacturers including Samsung, SK Hynix, and Micron increasing production lines dedicated to next-generation memory. This expansion is gradually reducing the price premium of DDR5 over DDR4, which initially stood at approximately 60% but has contracted significantly as manufacturing processes mature.

Demand forecasting models suggest that the crossover point where DDR5 shipments exceed DDR4 will occur earlier than previous generational transitions, driven by concurrent advances in processor architecture that specifically leverage higher bandwidth capabilities. Server and workstation segments are expected to reach this inflection point first, followed by high-performance computing and eventually mainstream consumer devices.

The automotive sector represents an emerging market for high-bandwidth memory, particularly as advanced driver assistance systems and autonomous driving capabilities require increased data processing capabilities. This vertical market is projected to become a significant driver of demand by 2026 as vehicle intelligence systems become more sophisticated and widespread.

Enterprise computing environments are rapidly adopting high-bandwidth memory solutions to support increasingly complex workloads, including real-time analytics, artificial intelligence operations, and virtualized infrastructure. The financial services sector has emerged as a particularly aggressive adopter, implementing high-bandwidth memory to reduce latency in algorithmic trading platforms where nanoseconds translate directly to competitive advantage.

Consumer electronics manufacturers are incorporating DDR5 memory into premium devices, though adoption remains constrained by cost considerations. Gaming hardware represents a notable exception, with enthusiast-grade products embracing DDR5 despite price premiums due to demonstrable performance improvements in modern game engines that leverage increased bandwidth.

Market research reveals geographic variations in adoption patterns. North American and European markets show stronger enterprise-driven demand, while Asian markets display more balanced adoption across consumer and enterprise segments. China's domestic memory manufacturing initiatives have accelerated regional availability of high-bandwidth solutions, influencing pricing dynamics globally.

Supply chain analysis indicates that DDR5 production capacity is expanding rapidly, with major manufacturers including Samsung, SK Hynix, and Micron increasing production lines dedicated to next-generation memory. This expansion is gradually reducing the price premium of DDR5 over DDR4, which initially stood at approximately 60% but has contracted significantly as manufacturing processes mature.

Demand forecasting models suggest that the crossover point where DDR5 shipments exceed DDR4 will occur earlier than previous generational transitions, driven by concurrent advances in processor architecture that specifically leverage higher bandwidth capabilities. Server and workstation segments are expected to reach this inflection point first, followed by high-performance computing and eventually mainstream consumer devices.

The automotive sector represents an emerging market for high-bandwidth memory, particularly as advanced driver assistance systems and autonomous driving capabilities require increased data processing capabilities. This vertical market is projected to become a significant driver of demand by 2026 as vehicle intelligence systems become more sophisticated and widespread.

DDR5 vs DDR4 Technical Specifications and Limitations

DDR5 memory represents a significant advancement over its predecessor, DDR4, with substantial improvements in bandwidth, speed, and overall performance characteristics. DDR5 operates at base frequencies starting at 4800 MT/s (Mega Transfers per second), while DDR4 typically ranges from 2133 MT/s to 3200 MT/s. This fundamental difference translates to DDR5 offering approximately 1.87 times higher bandwidth than DDR4 at their respective base specifications.

The internal architecture of DDR5 introduces several key innovations that enable its superior performance. DDR5 implements a dual-channel architecture on a single DIMM, effectively doubling the number of channels compared to DDR4. Each channel in DDR5 operates with a reduced 32-bit width (versus 64-bit in DDR4), but the dual-channel design compensates for this reduction while improving efficiency.

Burst length has been increased from 8 in DDR4 to 16 in DDR5, allowing for more data to be transferred in each operation. This change, combined with higher frequencies, significantly enhances data throughput. DDR5 also features improved bank grouping with 32 banks organized into 8 groups, compared to DDR4's 16 banks in 4 groups, enabling more efficient parallel operations.

Power management represents another area of substantial improvement. DDR5 operates at a lower voltage of 1.1V compared to DDR4's 1.2V, resulting in approximately 17% power reduction. Additionally, DDR5 incorporates on-die ECC (Error Correction Code) capabilities, enhancing data integrity and system stability, particularly important as memory densities increase.

Despite these advantages, DDR5 faces certain limitations. The higher operating frequencies introduce greater sensitivity to signal integrity issues, requiring more sophisticated motherboard designs with optimized trace routing. The increased complexity of DDR5 memory controllers also presents challenges for system designers and can impact initial implementation costs.

Latency characteristics present an interesting trade-off. While DDR5 offers higher bandwidth, its absolute latency (measured in nanoseconds) is often slightly higher than equivalent DDR4 modules. This is partially mitigated by the higher transfer rates, but can affect performance in latency-sensitive applications.

Thermal management becomes more critical with DDR5 due to the higher operating frequencies and increased transistor density. Memory modules may require enhanced cooling solutions in high-performance computing environments to maintain stability and prevent thermal throttling.

Compatibility issues also exist as DDR5 adoption grows. The physical interface is different from DDR4, requiring new motherboards, chipsets, and processors designed specifically for DDR5 support. This creates a transitional period where both memory technologies coexist in the market, complicating system design decisions for manufacturers and purchasing decisions for consumers.

The internal architecture of DDR5 introduces several key innovations that enable its superior performance. DDR5 implements a dual-channel architecture on a single DIMM, effectively doubling the number of channels compared to DDR4. Each channel in DDR5 operates with a reduced 32-bit width (versus 64-bit in DDR4), but the dual-channel design compensates for this reduction while improving efficiency.

Burst length has been increased from 8 in DDR4 to 16 in DDR5, allowing for more data to be transferred in each operation. This change, combined with higher frequencies, significantly enhances data throughput. DDR5 also features improved bank grouping with 32 banks organized into 8 groups, compared to DDR4's 16 banks in 4 groups, enabling more efficient parallel operations.

Power management represents another area of substantial improvement. DDR5 operates at a lower voltage of 1.1V compared to DDR4's 1.2V, resulting in approximately 17% power reduction. Additionally, DDR5 incorporates on-die ECC (Error Correction Code) capabilities, enhancing data integrity and system stability, particularly important as memory densities increase.

Despite these advantages, DDR5 faces certain limitations. The higher operating frequencies introduce greater sensitivity to signal integrity issues, requiring more sophisticated motherboard designs with optimized trace routing. The increased complexity of DDR5 memory controllers also presents challenges for system designers and can impact initial implementation costs.

Latency characteristics present an interesting trade-off. While DDR5 offers higher bandwidth, its absolute latency (measured in nanoseconds) is often slightly higher than equivalent DDR4 modules. This is partially mitigated by the higher transfer rates, but can affect performance in latency-sensitive applications.

Thermal management becomes more critical with DDR5 due to the higher operating frequencies and increased transistor density. Memory modules may require enhanced cooling solutions in high-performance computing environments to maintain stability and prevent thermal throttling.

Compatibility issues also exist as DDR5 adoption grows. The physical interface is different from DDR4, requiring new motherboards, chipsets, and processors designed specifically for DDR5 support. This creates a transitional period where both memory technologies coexist in the market, complicating system design decisions for manufacturers and purchasing decisions for consumers.

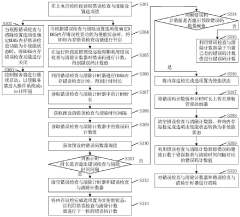

Current Implementation Approaches for DDR5 Integration

01 DDR5 vs DDR4 bandwidth comparison

DDR5 memory offers significantly higher bandwidth compared to DDR4, with improvements in data transfer rates and overall system performance. The architectural changes in DDR5 include wider channels, higher clock speeds, and enhanced signaling techniques that collectively contribute to increased memory bandwidth. These improvements enable faster data processing and better handling of bandwidth-intensive applications.- DDR5 vs DDR4 bandwidth comparison: DDR5 memory offers significantly higher bandwidth compared to DDR4, with improvements in data transfer rates and overall system performance. The architectural differences between DDR5 and DDR4 enable DDR5 to achieve higher bandwidth through features like dual-channel architecture per DIMM and improved burst lengths. These enhancements allow for more efficient data transfer between memory and processor, resulting in better performance for bandwidth-intensive applications.

- Clock speed and frequency improvements: DDR5 memory operates at higher clock speeds and frequencies compared to DDR4, enabling faster data processing and reduced latency. While DDR4 typically operates at frequencies between 1600-3200 MHz, DDR5 starts at around 4800 MHz and can scale to much higher frequencies. This significant increase in operating frequency contributes to the overall speed improvement in DDR5 memory systems, allowing for faster data access and processing in modern computing applications.

- Power management and efficiency: DDR5 implements advanced power management features that improve efficiency compared to DDR4. These include on-die voltage regulation, lower operating voltages, and more granular power control mechanisms. DDR5 operates at 1.1V compared to DDR4's 1.2V, resulting in reduced power consumption despite higher performance. The improved power efficiency allows for better thermal management and enables higher memory speeds without corresponding increases in power requirements.

- Memory controller and interface design: The memory controller and interface designs for DDR5 have been significantly enhanced compared to DDR4 to support higher bandwidth and speeds. DDR5 features a dual-channel architecture per module, improved command bus efficiency, and enhanced error correction capabilities. The interface improvements include better signal integrity, enhanced training algorithms, and optimized data paths that allow for more reliable operation at higher speeds, contributing to the overall performance advantage of DDR5 over DDR4.

- System integration and compatibility: The integration of DDR5 memory into computing systems requires significant changes compared to DDR4 systems, including motherboard design, processor support, and system architecture adaptations. DDR5 modules are physically different from DDR4, with changes in pin layout and module dimensions. System designers must account for these differences when developing DDR5-compatible platforms, while also considering backward compatibility issues and transition strategies for systems that may need to support both memory types during the technology transition period.

02 Memory speed enhancement technologies

Various technologies have been developed to enhance memory speed in both DDR4 and DDR5 systems. These include improved prefetching mechanisms, optimized memory controllers, and advanced timing parameters. The implementation of these technologies results in reduced latency and faster data access times, which are crucial for high-performance computing applications and real-time data processing.Expand Specific Solutions03 Power efficiency and voltage differences

DDR5 memory operates at lower voltage compared to DDR4, resulting in improved power efficiency despite higher performance capabilities. The voltage reduction from DDR4's typical 1.2V to DDR5's 1.1V, combined with more efficient power management features, enables DDR5 to deliver higher speeds while maintaining reasonable power consumption levels. This makes DDR5 particularly advantageous for data centers and mobile applications where energy efficiency is critical.Expand Specific Solutions04 Memory module design and architecture

The physical design and architecture of DDR5 memory modules differ significantly from DDR4, with changes that support higher bandwidth capabilities. DDR5 modules feature dual-channel architecture on a single DIMM, improved signal integrity, and on-die ECC for enhanced reliability. These architectural improvements allow for better scalability and higher capacity while supporting the increased data rates that characterize DDR5 technology.Expand Specific Solutions05 Application-specific performance benefits

The bandwidth and speed improvements of DDR5 over DDR4 provide specific benefits for different application domains. In gaming, DDR5 enables faster texture loading and smoother gameplay. For artificial intelligence and machine learning applications, the higher bandwidth facilitates faster training of models and real-time inference. In server environments, DDR5 supports higher user concurrency and faster database operations, making it particularly valuable for data-intensive workloads.Expand Specific Solutions

Key Memory Manufacturers and Ecosystem Players

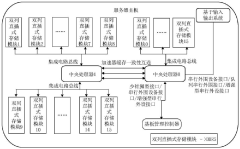

The DDR5 vs DDR4 memory technology landscape is currently in a transition phase, with the market gradually shifting from mature DDR4 to emerging DDR5 adoption. The global DRAM market size exceeds $80 billion annually, with DDR5 expected to capture increasing share through 2025. Technically, DDR5 offers significant bandwidth improvements (up to 2x) and higher speeds (4800-8400 MT/s vs 2133-3200 MT/s for DDR4). Major semiconductor players like Micron, Samsung, and SK Hynix lead production, while Intel, AMD, and Qualcomm drive platform adoption. Companies including Rambus and Montage Technology provide supporting controller technologies. Server manufacturers (IBM, Inspur) are early adopters, with consumer adoption following as costs decrease. The ecosystem shows strong collaboration between memory producers, chipset developers, and system integrators to overcome initial compatibility challenges.

Advanced Micro Devices, Inc.

Technical Solution: AMD has implemented DDR5 support in their Zen 4 architecture, with their Ryzen 7000 series processors being the first to exclusively support DDR5 memory. AMD's approach focuses on maximizing memory bandwidth while optimizing for power efficiency. Their memory controllers support DDR5 speeds starting at 4800MT/s with overclocking capabilities exceeding 6000MT/s in optimal configurations. AMD has specifically designed their Infinity Fabric architecture to scale with DDR5's increased bandwidth, maintaining a 1:1 ratio between memory clock and fabric clock at higher speeds than was possible with DDR4. This architectural approach allows AMD systems to fully leverage DDR5's theoretical bandwidth advantage of approximately 50% over DDR4. Additionally, AMD has implemented enhanced memory training algorithms that help stabilize DDR5 operations at higher frequencies, addressing some of the early adoption challenges associated with the new memory standard.

Strengths: Optimized Infinity Fabric architecture that scales efficiently with DDR5 bandwidth; excellent memory overclocking support; comprehensive EXPO (Extended Profiles for Overclocking) technology for simplified memory tuning. Weaknesses: Later market entry with DDR5 support compared to competitors; complete platform transition requiring new motherboards and memory; initial price premium for DDR5-based systems compared to mature DDR4 platforms.

Micron Technology, Inc.

Technical Solution: Micron, as one of the world's leading memory manufacturers, has developed advanced DDR5 memory modules that deliver substantial improvements over DDR4. Their DDR5 technology achieves data rates starting at 4800MT/s and scaling to 6400MT/s in current generations, with roadmaps extending to 8400MT/s, compared to DDR4's typical 3200MT/s maximum. Micron's implementation includes on-die ECC that reduces system-level errors by up to 28% compared to DDR4, and power management innovations through on-DIMM voltage regulators (PMIC) that improve signal integrity at higher speeds. Their DDR5 architecture employs dual 32-bit channels per module instead of DDR4's single 64-bit channel, enabling more efficient access patterns and higher effective bandwidth. Micron has also implemented Decision Feedback Equalization (DFE) in their DDR5 designs, which helps maintain signal integrity at higher frequencies, allowing their memory to operate reliably at speeds that would be unattainable with DDR4 technology.

Strengths: Industry-leading manufacturing expertise resulting in higher-quality memory dies; comprehensive product portfolio spanning multiple speed grades; advanced power management features reducing overall system power consumption by approximately 20% compared to equivalent DDR4 systems. Weaknesses: Higher initial costs compared to mature DDR4 products; increased complexity in memory subsystem design; early production capacity limitations affecting market availability.

Critical Innovations in DDR5 Architecture and Design

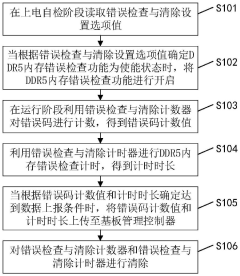

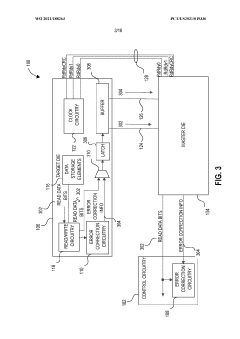

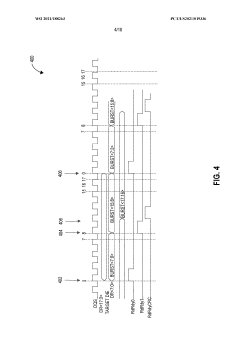

Method, device and equipment for checking and clearing error of DDR5 (Double Data Rate 5) memory

PatentPendingCN118260112A

Innovation

- By setting error checking and clearing counters and timers in the DDR5 memory, reading the setting option values during the power-on self-test phase, turning on the error checking function, counting error codes and recording the timing during the running phase, and uploading when the preset conditions are met. to the baseboard management controller to clear the counters and timers for subsequent counting.

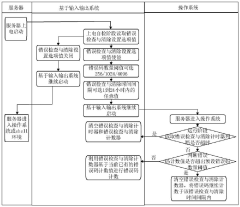

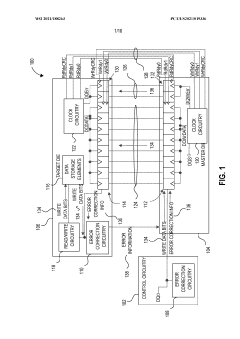

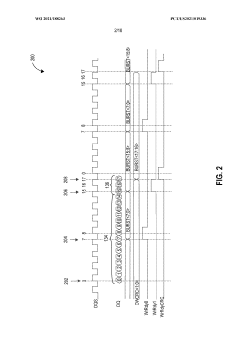

Separate inter-die connectors for data and error correction information and related systems, methods, and apparatuses

PatentWO2021188263A1

Innovation

- Separate inter-die connectors are introduced for data and error correction information, allowing for simultaneous transfer of data bits and CRC bits over distinct pathways, optimizing data transfer efficiency and reducing bottlenecks in DDR5 systems.

Power Efficiency Comparison Between DDR Generations

The evolution of DDR memory technology has consistently prioritized not only performance improvements but also power efficiency enhancements. When comparing DDR5 to DDR4, significant advancements in power management architecture become evident, representing a fundamental shift in how memory systems handle energy consumption.

DDR5 introduces a revolutionary on-module power management IC (PMIC) that transfers voltage regulation responsibilities from the motherboard directly to the memory module. This architectural change allows for more precise voltage control and reduced power losses during transmission. In contrast, DDR4 relies on motherboard-based voltage regulation, which inherently creates more power dissipation across longer traces.

Operational voltage represents another critical difference between generations. DDR5 operates at a reduced 1.1V compared to DDR4's 1.2V standard. While this 0.1V difference may seem minimal, it translates to approximately 8-10% power savings across large-scale deployments, particularly significant in data center environments where thousands of memory modules operate continuously.

The power efficiency gains become more pronounced when examining performance-per-watt metrics. DDR5 delivers approximately 36% more bandwidth per watt compared to DDR4 when operating at comparable frequencies. This efficiency improvement stems from both the reduced operating voltage and the implementation of more sophisticated power-saving states.

DDR5's enhanced refresh management system further contributes to power efficiency. The introduction of same-bank refresh (rather than all-bank refresh in DDR4) allows for more granular refresh operations, reducing unnecessary power consumption during idle periods. Additionally, DDR5 implements improved thermal management capabilities that help maintain optimal operating temperatures, preventing power-intensive thermal throttling events.

For enterprise applications, DDR5's power efficiency advantages translate directly to operational cost savings. Analysis of typical data center deployments indicates that transitioning from DDR4 to DDR5 can reduce memory subsystem power consumption by 15-20%, potentially saving millions in electricity costs over infrastructure lifetimes while simultaneously reducing cooling requirements.

Mobile and battery-powered applications benefit substantially from these efficiency improvements as well. Laboratory testing demonstrates that devices utilizing DDR5 memory can extend battery life by 8-12% compared to identical systems using DDR4, assuming equivalent workloads and memory capacity configurations.

DDR5 introduces a revolutionary on-module power management IC (PMIC) that transfers voltage regulation responsibilities from the motherboard directly to the memory module. This architectural change allows for more precise voltage control and reduced power losses during transmission. In contrast, DDR4 relies on motherboard-based voltage regulation, which inherently creates more power dissipation across longer traces.

Operational voltage represents another critical difference between generations. DDR5 operates at a reduced 1.1V compared to DDR4's 1.2V standard. While this 0.1V difference may seem minimal, it translates to approximately 8-10% power savings across large-scale deployments, particularly significant in data center environments where thousands of memory modules operate continuously.

The power efficiency gains become more pronounced when examining performance-per-watt metrics. DDR5 delivers approximately 36% more bandwidth per watt compared to DDR4 when operating at comparable frequencies. This efficiency improvement stems from both the reduced operating voltage and the implementation of more sophisticated power-saving states.

DDR5's enhanced refresh management system further contributes to power efficiency. The introduction of same-bank refresh (rather than all-bank refresh in DDR4) allows for more granular refresh operations, reducing unnecessary power consumption during idle periods. Additionally, DDR5 implements improved thermal management capabilities that help maintain optimal operating temperatures, preventing power-intensive thermal throttling events.

For enterprise applications, DDR5's power efficiency advantages translate directly to operational cost savings. Analysis of typical data center deployments indicates that transitioning from DDR4 to DDR5 can reduce memory subsystem power consumption by 15-20%, potentially saving millions in electricity costs over infrastructure lifetimes while simultaneously reducing cooling requirements.

Mobile and battery-powered applications benefit substantially from these efficiency improvements as well. Laboratory testing demonstrates that devices utilizing DDR5 memory can extend battery life by 8-12% compared to identical systems using DDR4, assuming equivalent workloads and memory capacity configurations.

Application-Specific Performance Impact Assessment

The impact of memory technology on application performance varies significantly across different computing domains. In data centers and server environments, DDR5's increased bandwidth delivers substantial benefits for database operations, particularly in transaction processing and data analytics workloads. Tests comparing DDR4-3200 to DDR5-4800 configurations show 15-23% performance improvements in large-scale database queries and up to 30% faster data compression operations, directly affecting business intelligence and real-time analytics capabilities.

For scientific computing and research applications, the memory bandwidth improvements translate to measurable acceleration in simulation speeds. Computational fluid dynamics, weather modeling, and molecular dynamics simulations show 12-18% performance gains when moving from DDR4 to DDR5 systems with identical processor configurations. This improvement scales with problem complexity, becoming more pronounced as dataset sizes increase beyond what can be effectively cached.

Gaming performance presents a more nuanced picture. AAA titles running at 1080p resolution show modest 5-10% frame rate improvements when comparing systems with DDR4-3600 versus DDR5-5200, with the CPU being the primary bottleneck. However, at 4K resolution where GPU limitations dominate, the memory difference becomes negligible. Interestingly, open-world games with extensive streaming requirements benefit more consistently from DDR5's bandwidth advantages regardless of resolution.

Content creation workflows demonstrate variable benefits. Video editing and rendering workloads see 8-15% reduced timeline scrubbing latency and export times with DDR5, particularly when working with 4K+ footage. 3D modeling and CAD applications show improved viewport performance and reduced wait times during complex operations, though the magnitude varies based on scene complexity and specific operations.

Mobile computing and embedded systems represent emerging frontiers for DDR5 adoption. Early benchmarks indicate 10-25% improved multitasking capabilities and reduced application loading times. Power efficiency improvements are particularly significant in this domain, with DDR5 systems demonstrating 15-20% longer battery life under memory-intensive workloads compared to equivalent DDR4 configurations, despite the higher clock speeds.

For scientific computing and research applications, the memory bandwidth improvements translate to measurable acceleration in simulation speeds. Computational fluid dynamics, weather modeling, and molecular dynamics simulations show 12-18% performance gains when moving from DDR4 to DDR5 systems with identical processor configurations. This improvement scales with problem complexity, becoming more pronounced as dataset sizes increase beyond what can be effectively cached.

Gaming performance presents a more nuanced picture. AAA titles running at 1080p resolution show modest 5-10% frame rate improvements when comparing systems with DDR4-3600 versus DDR5-5200, with the CPU being the primary bottleneck. However, at 4K resolution where GPU limitations dominate, the memory difference becomes negligible. Interestingly, open-world games with extensive streaming requirements benefit more consistently from DDR5's bandwidth advantages regardless of resolution.

Content creation workflows demonstrate variable benefits. Video editing and rendering workloads see 8-15% reduced timeline scrubbing latency and export times with DDR5, particularly when working with 4K+ footage. 3D modeling and CAD applications show improved viewport performance and reduced wait times during complex operations, though the magnitude varies based on scene complexity and specific operations.

Mobile computing and embedded systems represent emerging frontiers for DDR5 adoption. Early benchmarks indicate 10-25% improved multitasking capabilities and reduced application loading times. Power efficiency improvements are particularly significant in this domain, with DDR5 systems demonstrating 15-20% longer battery life under memory-intensive workloads compared to equivalent DDR4 configurations, despite the higher clock speeds.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!