DDR5 vs Flash Memory: Data Storage Performance

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Memory Technology Evolution and Objectives

The evolution of memory technologies has been a cornerstone of computing advancement since the inception of digital systems. From the early magnetic core memory to today's high-performance solutions, memory technology has continuously evolved to meet increasing demands for speed, capacity, and energy efficiency. DDR (Double Data Rate) memory has progressed through multiple generations, with DDR5 representing the latest significant advancement in volatile memory technology, offering substantial improvements in bandwidth, density, and power efficiency compared to its predecessors.

Flash memory, conversely, emerged as a revolutionary non-volatile storage solution in the 1980s, transforming from simple storage chips to sophisticated NAND and NOR architectures that power today's SSDs and portable storage devices. The technological trajectories of these memory types reflect different priorities: DDR focusing on speed and immediate data access, while Flash emphasizing persistence and capacity.

The current technological landscape presents a fascinating convergence point where DDR5 and Flash memory technologies are being evaluated not as competing solutions but as complementary components in tiered storage architectures. DDR5 delivers unprecedented data transfer rates exceeding 6400 MT/s, while modern Flash memory offers persistence with increasingly competitive access speeds through innovations like NVMe interfaces.

The primary objective in comparing DDR5 and Flash memory performance is to establish optimal data storage hierarchies that balance speed, capacity, persistence, and cost-effectiveness. This evaluation must consider workload characteristics, from latency-sensitive applications requiring DDR5's sub-nanosecond response times to data-intensive operations benefiting from Flash memory's higher density and non-volatility.

Future technological objectives include reducing the performance gap between volatile and non-volatile memory, potentially through emerging technologies like Storage Class Memory (SCM). The industry is also pursuing increased density in both technologies, with DDR5 modules now reaching 128GB capacities and Flash memory pushing toward higher layer counts in 3D NAND structures.

Energy efficiency represents another critical objective, with DDR5 introducing voltage regulation on-module to improve power management, while Flash memory continues to optimize read/write operations to minimize energy consumption. These advancements align with broader computing trends toward green IT and sustainable data center operations.

The convergence of performance metrics between these technologies suggests a future where the traditional memory-storage dichotomy may blur, potentially leading to unified memory architectures that combine the advantages of both technologies. This evolution trajectory will significantly impact system design philosophies and application performance optimization strategies across computing platforms.

Flash memory, conversely, emerged as a revolutionary non-volatile storage solution in the 1980s, transforming from simple storage chips to sophisticated NAND and NOR architectures that power today's SSDs and portable storage devices. The technological trajectories of these memory types reflect different priorities: DDR focusing on speed and immediate data access, while Flash emphasizing persistence and capacity.

The current technological landscape presents a fascinating convergence point where DDR5 and Flash memory technologies are being evaluated not as competing solutions but as complementary components in tiered storage architectures. DDR5 delivers unprecedented data transfer rates exceeding 6400 MT/s, while modern Flash memory offers persistence with increasingly competitive access speeds through innovations like NVMe interfaces.

The primary objective in comparing DDR5 and Flash memory performance is to establish optimal data storage hierarchies that balance speed, capacity, persistence, and cost-effectiveness. This evaluation must consider workload characteristics, from latency-sensitive applications requiring DDR5's sub-nanosecond response times to data-intensive operations benefiting from Flash memory's higher density and non-volatility.

Future technological objectives include reducing the performance gap between volatile and non-volatile memory, potentially through emerging technologies like Storage Class Memory (SCM). The industry is also pursuing increased density in both technologies, with DDR5 modules now reaching 128GB capacities and Flash memory pushing toward higher layer counts in 3D NAND structures.

Energy efficiency represents another critical objective, with DDR5 introducing voltage regulation on-module to improve power management, while Flash memory continues to optimize read/write operations to minimize energy consumption. These advancements align with broader computing trends toward green IT and sustainable data center operations.

The convergence of performance metrics between these technologies suggests a future where the traditional memory-storage dichotomy may blur, potentially leading to unified memory architectures that combine the advantages of both technologies. This evolution trajectory will significantly impact system design philosophies and application performance optimization strategies across computing platforms.

Market Demand Analysis for High-Performance Storage

The global market for high-performance storage solutions is experiencing unprecedented growth, driven primarily by data-intensive applications across various sectors. Enterprise data centers represent the largest segment, with annual storage capacity requirements increasing by 35-40% as organizations manage expanding volumes of business intelligence, customer data, and operational metrics. Cloud service providers follow closely, deploying massive storage infrastructures to support the migration of corporate workloads to hosted environments.

Financial services and healthcare sectors demonstrate particularly strong demand for high-performance storage, with requirements for sub-millisecond access times and sustained throughput exceeding 10GB/s for critical applications. The gaming industry has emerged as a significant market driver, with modern AAA game titles requiring storage solutions capable of loading multi-gigabyte assets within seconds to maintain immersive experiences.

Consumer electronics manufacturers are increasingly differentiating their premium devices through storage performance, with flagship smartphones and laptops advertising storage read speeds exceeding 3000MB/s as key selling points. This trend has expanded the high-performance storage market beyond traditional enterprise boundaries into mainstream consumer segments.

Geographically, North America continues to lead market demand, accounting for approximately 42% of global high-performance storage consumption. However, the Asia-Pacific region shows the fastest growth trajectory, with annual market expansion rates of 28-30% driven by rapid digital transformation initiatives across China, India, and Southeast Asian economies.

The demand landscape is further shaped by emerging technologies like artificial intelligence and machine learning workloads, which require storage architectures capable of feeding massive datasets to computational resources with minimal latency. This has created a specialized market segment for AI-optimized storage solutions growing at 45-50% annually.

Industry analysts project the total addressable market for high-performance storage to reach $89 billion by 2026, representing a compound annual growth rate of 19.7% from current levels. This growth is underpinned by the increasing value proposition of faster storage in enabling competitive advantages across industries - from accelerating financial transactions to improving patient outcomes through faster medical image processing.

The market demonstrates clear price sensitivity thresholds, with enterprise customers willing to pay premium prices for performance gains in mission-critical applications, while consumer markets show elasticity at specific price points that align with device upgrade cycles. This bifurcation creates distinct market opportunities for DDR5 and advanced Flash memory technologies depending on their performance-to-cost ratios in different application contexts.

Financial services and healthcare sectors demonstrate particularly strong demand for high-performance storage, with requirements for sub-millisecond access times and sustained throughput exceeding 10GB/s for critical applications. The gaming industry has emerged as a significant market driver, with modern AAA game titles requiring storage solutions capable of loading multi-gigabyte assets within seconds to maintain immersive experiences.

Consumer electronics manufacturers are increasingly differentiating their premium devices through storage performance, with flagship smartphones and laptops advertising storage read speeds exceeding 3000MB/s as key selling points. This trend has expanded the high-performance storage market beyond traditional enterprise boundaries into mainstream consumer segments.

Geographically, North America continues to lead market demand, accounting for approximately 42% of global high-performance storage consumption. However, the Asia-Pacific region shows the fastest growth trajectory, with annual market expansion rates of 28-30% driven by rapid digital transformation initiatives across China, India, and Southeast Asian economies.

The demand landscape is further shaped by emerging technologies like artificial intelligence and machine learning workloads, which require storage architectures capable of feeding massive datasets to computational resources with minimal latency. This has created a specialized market segment for AI-optimized storage solutions growing at 45-50% annually.

Industry analysts project the total addressable market for high-performance storage to reach $89 billion by 2026, representing a compound annual growth rate of 19.7% from current levels. This growth is underpinned by the increasing value proposition of faster storage in enabling competitive advantages across industries - from accelerating financial transactions to improving patient outcomes through faster medical image processing.

The market demonstrates clear price sensitivity thresholds, with enterprise customers willing to pay premium prices for performance gains in mission-critical applications, while consumer markets show elasticity at specific price points that align with device upgrade cycles. This bifurcation creates distinct market opportunities for DDR5 and advanced Flash memory technologies depending on their performance-to-cost ratios in different application contexts.

DDR5 and Flash Memory Technical Challenges

Despite significant advancements in both technologies, DDR5 and Flash Memory face distinct technical challenges that impact their performance in data storage applications. DDR5 memory confronts power management issues as higher frequencies and densities increase thermal output, requiring sophisticated cooling solutions. The signal integrity at speeds exceeding 6400 MT/s becomes problematic, with increased crosstalk and electromagnetic interference necessitating advanced PCB designs and shielding techniques.

DDR5's on-die ECC implementation, while improving reliability, introduces latency penalties that can affect time-sensitive applications. Additionally, the complex power architecture with voltage regulation moved to the DIMM creates integration challenges for system designers and increases manufacturing complexity. The dual-channel architecture within a single module requires more sophisticated memory controllers capable of managing parallel operations efficiently.

Flash memory technologies face their own set of obstacles. NAND Flash confronts endurance limitations with decreasing write cycles as density increases, particularly in TLC and QLC implementations. The cell-to-cell interference becomes more pronounced at smaller process nodes, leading to data retention issues and requiring more complex error correction algorithms that consume additional controller resources.

The write amplification effect in Flash memory systems continues to be a significant challenge, where the mismatch between host write sizes and Flash erase block sizes results in excessive write operations that degrade performance and lifespan. This is exacerbated in high-density implementations where garbage collection processes become more frequent and resource-intensive.

Both technologies struggle with scaling limitations. DDR5 faces physical constraints in further reducing die size while maintaining signal integrity, while Flash memory confronts quantum effects at sub-20nm nodes that increase error rates and leakage currents. The 3D stacking approach in Flash memory introduces thermal management challenges as heat dissipation becomes more difficult with increased layers.

From a manufacturing perspective, both technologies require increasingly sophisticated fabrication processes. DDR5 production demands extremely precise lithography for high-speed signal paths, while 3D NAND Flash requires precise etching of high aspect ratio holes through multiple layers, significantly increasing production complexity and cost.

The performance gap between compute capabilities and storage access speeds remains a fundamental challenge. While DDR5 offers substantial bandwidth improvements, its latency reductions are incremental compared to computational speed increases. Similarly, Flash memory bandwidth improvements through parallelism and interface enhancements still leave it orders of magnitude slower than DRAM technologies, creating system bottlenecks.

DDR5's on-die ECC implementation, while improving reliability, introduces latency penalties that can affect time-sensitive applications. Additionally, the complex power architecture with voltage regulation moved to the DIMM creates integration challenges for system designers and increases manufacturing complexity. The dual-channel architecture within a single module requires more sophisticated memory controllers capable of managing parallel operations efficiently.

Flash memory technologies face their own set of obstacles. NAND Flash confronts endurance limitations with decreasing write cycles as density increases, particularly in TLC and QLC implementations. The cell-to-cell interference becomes more pronounced at smaller process nodes, leading to data retention issues and requiring more complex error correction algorithms that consume additional controller resources.

The write amplification effect in Flash memory systems continues to be a significant challenge, where the mismatch between host write sizes and Flash erase block sizes results in excessive write operations that degrade performance and lifespan. This is exacerbated in high-density implementations where garbage collection processes become more frequent and resource-intensive.

Both technologies struggle with scaling limitations. DDR5 faces physical constraints in further reducing die size while maintaining signal integrity, while Flash memory confronts quantum effects at sub-20nm nodes that increase error rates and leakage currents. The 3D stacking approach in Flash memory introduces thermal management challenges as heat dissipation becomes more difficult with increased layers.

From a manufacturing perspective, both technologies require increasingly sophisticated fabrication processes. DDR5 production demands extremely precise lithography for high-speed signal paths, while 3D NAND Flash requires precise etching of high aspect ratio holes through multiple layers, significantly increasing production complexity and cost.

The performance gap between compute capabilities and storage access speeds remains a fundamental challenge. While DDR5 offers substantial bandwidth improvements, its latency reductions are incremental compared to computational speed increases. Similarly, Flash memory bandwidth improvements through parallelism and interface enhancements still leave it orders of magnitude slower than DRAM technologies, creating system bottlenecks.

Current DDR5 and Flash Memory Solutions

01 DDR5 memory architecture and performance enhancements

DDR5 memory architecture introduces significant performance improvements over previous generations, including higher data rates, improved power efficiency, and enhanced reliability. These advancements are achieved through architectural changes such as dual-channel architecture, improved command and addressing schemes, and enhanced error correction capabilities. The implementation of these features results in higher bandwidth and reduced latency, making DDR5 particularly suitable for data-intensive applications.- DDR5 Memory Architecture and Performance Enhancements: DDR5 memory architecture introduces significant performance improvements over previous generations, including higher data transfer rates, improved power efficiency, and enhanced reliability. These advancements are achieved through architectural changes such as dual-channel architecture, improved command and addressing schemes, and enhanced error correction capabilities. The implementation of these features results in higher bandwidth and reduced latency, making DDR5 particularly suitable for data-intensive applications.

- Flash Memory Controller Optimization for High-Speed Interfaces: Flash memory controllers designed for high-speed interfaces like DDR5 implement specialized algorithms and hardware to optimize data transfer between flash memory and system memory. These controllers feature advanced buffer management, parallel processing capabilities, and optimized command scheduling to reduce latency and maximize throughput. The controllers also implement specific timing adjustments and signal integrity enhancements to ensure reliable operation at the high clock speeds required for DDR5 compatibility.

- Memory System Integration of DDR5 and Flash Technologies: Integration of DDR5 DRAM and flash memory in hybrid memory systems leverages the strengths of both technologies to achieve optimal performance. These systems use DDR5 as high-speed cache or buffer memory while utilizing flash memory for persistent storage. Advanced memory management techniques, including intelligent caching algorithms, predictive data prefetching, and dynamic resource allocation, enable seamless data movement between the different memory types. This integration results in systems that combine the speed of DDR5 with the non-volatility and capacity of flash memory.

- Power Management and Thermal Considerations: Power management techniques are crucial for optimizing the performance of systems using DDR5 and flash memory. These include dynamic voltage and frequency scaling, selective power-down of unused components, and intelligent thermal management. Advanced power states and fine-grained control mechanisms help balance performance requirements with power consumption constraints. Thermal management solutions address the heat generation associated with high-performance memory operations, ensuring stable operation and preventing performance throttling due to overheating.

- Error Detection and Correction Mechanisms: Enhanced error detection and correction mechanisms are implemented in DDR5 and flash memory systems to maintain data integrity at higher operating speeds. These include advanced ECC (Error-Correcting Code) algorithms, on-die ECC for DDR5, and specialized error management for flash memory to address issues like read disturb and wear leveling. The systems also implement runtime error monitoring, predictive failure analysis, and automatic recovery procedures to minimize the impact of errors on system performance and reliability.

02 Flash memory performance optimization techniques

Various techniques are employed to optimize flash memory performance, including advanced wear-leveling algorithms, multi-level cell technology, and optimized controller designs. These methods help to extend the lifespan of flash memory while improving read and write speeds. Additionally, innovations in flash memory architecture, such as 3D NAND technology, contribute to higher density storage with improved performance characteristics.Expand Specific Solutions03 Integration of DDR5 and flash memory systems

The integration of DDR5 and flash memory systems creates hybrid memory solutions that leverage the strengths of both technologies. These integrated systems utilize DDR5's high-speed access capabilities alongside flash memory's non-volatile storage capacity. Memory controllers are designed to manage data flow between these different memory types, optimizing for both performance and power efficiency. This integration is particularly beneficial for applications requiring both high-speed processing and persistent storage.Expand Specific Solutions04 Memory controller designs for optimized performance

Advanced memory controller designs play a crucial role in maximizing the performance of both DDR5 and flash memory systems. These controllers implement sophisticated algorithms for command scheduling, data buffering, and interface management. Features such as predictive read/write operations, intelligent caching mechanisms, and adaptive timing adjustments help to reduce latency and improve throughput. The controllers also manage power states efficiently to balance performance requirements with energy consumption.Expand Specific Solutions05 Error detection and correction mechanisms

Robust error detection and correction mechanisms are essential for maintaining data integrity in high-performance memory systems. Both DDR5 and flash memory implementations incorporate advanced error correction code (ECC) techniques to detect and recover from bit errors. These mechanisms include on-die ECC for DDR5 and more complex algorithms for flash memory to address its unique error characteristics. Additionally, system-level redundancy and recovery features provide protection against larger-scale failures, ensuring reliable operation even at higher data rates.Expand Specific Solutions

Key Memory Manufacturers and Ecosystem

The DDR5 vs Flash Memory market is currently in a growth phase, with increasing demand for high-performance data storage solutions driving innovation. The global market size for these technologies is expanding rapidly, expected to reach significant valuation as data-intensive applications proliferate. Technologically, DDR5 offers superior speed while flash memory provides non-volatile storage advantages. Leading players like Samsung Electronics, SK hynix, and Micron dominate the DDR5 segment, while Western Digital, Intel, and Phison Electronics are prominent in flash memory development. IBM and Samsung are investing heavily in hybrid solutions that leverage both technologies. The competitive landscape shows established semiconductor giants competing with specialized storage technology firms like Macronix and ADATA, with innovation focused on improving speed, power efficiency, and storage density for next-generation computing applications.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has pioneered significant advancements in both DDR5 and Flash Memory technologies. For DDR5, Samsung has developed modules reaching speeds up to 7200MT/s with capacities up to 512GB per module, utilizing their proprietary extreme die-stacking technology. Their DDR5 implements on-die ECC, decision feedback equalization, and improved power management with integrated voltage regulators reducing power consumption by approximately 30% compared to DDR4. In Flash Memory, Samsung's V-NAND technology employs vertical stacking of up to 176 layers, achieving read/write speeds of 7,000MB/s in their latest NVMe SSDs. Samsung has also developed computational storage solutions that integrate processing capabilities directly into storage devices, reducing data movement and improving overall system efficiency for data-intensive applications.

Strengths: Vertical integration allowing control over entire manufacturing process; industry-leading capacity and performance metrics; advanced power efficiency features. Weaknesses: Premium pricing compared to competitors; DDR5 adoption still facing platform compatibility challenges; higher initial implementation costs for system designers.

Phison Electronics Corp.

Technical Solution: Phison has established itself as a leading controller designer for Flash Memory technologies while developing compatibility solutions for DDR5 systems. Their E18 PCIe 4.0 controller achieves sequential read/write speeds of 7,000/6,900MB/s with advanced features including SmartECC and AES 256-bit encryption. Phison's upcoming E26 controller for PCIe 5.0 promises to double these performance metrics while maintaining backward compatibility. Their controllers implement proprietary CoXProcessor 2.0 architecture with dedicated cores for host commands, flash management, and background operations, enabling more efficient parallel processing. For DDR5 integration, Phison has developed bridge solutions that optimize data transfer between volatile and non-volatile memory, reducing latency in hybrid memory systems. Their controllers feature adaptive thermal management that dynamically adjusts performance based on temperature conditions, preventing throttling while maintaining data integrity.

Strengths: Industry-leading controller technology; strong partnerships with NAND manufacturers; agile development cycle for new standards. Weaknesses: Dependent on partnerships for memory production; limited direct presence in DRAM market; smaller scale compared to fully integrated manufacturers.

Critical Performance Benchmarks and Patents

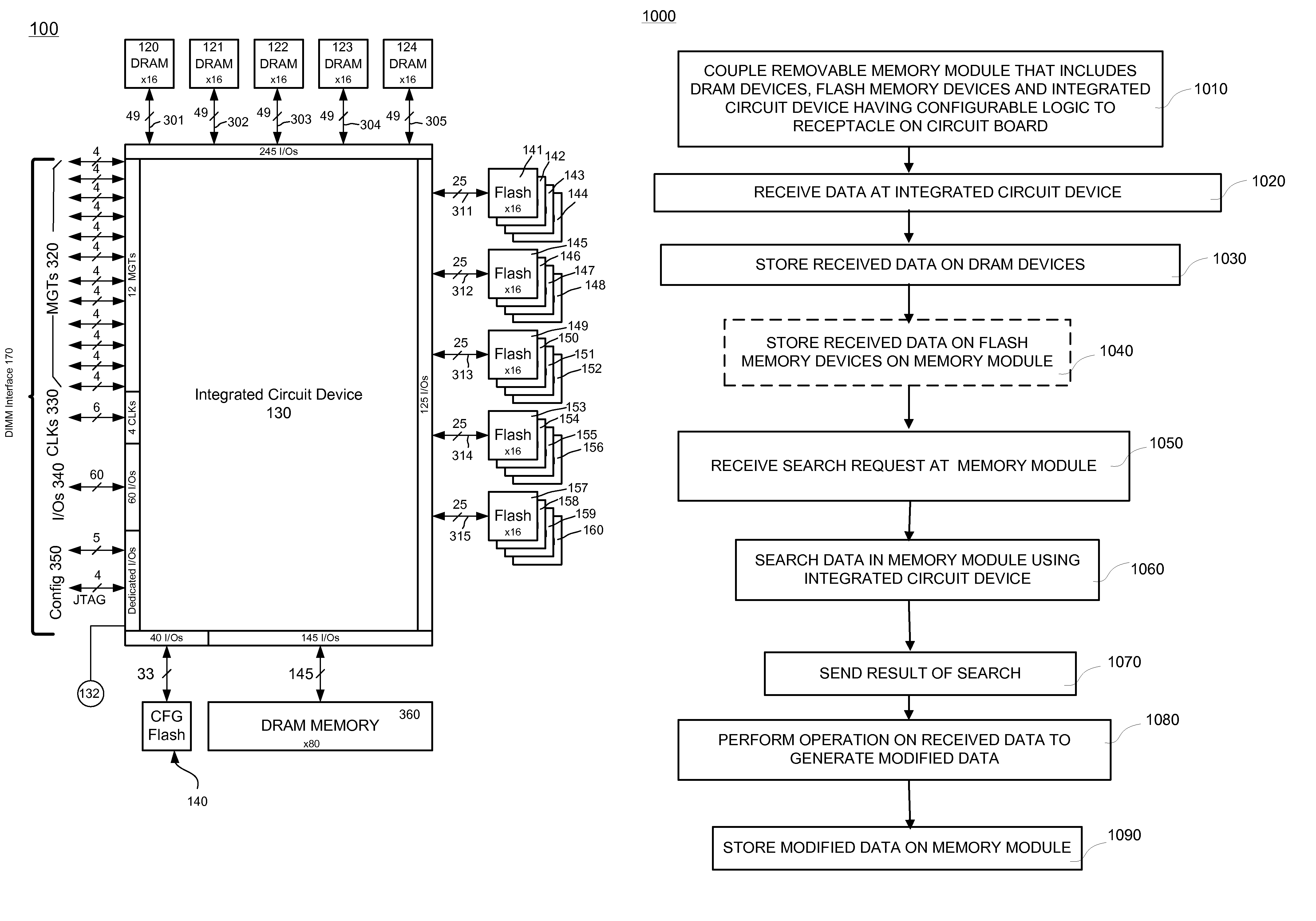

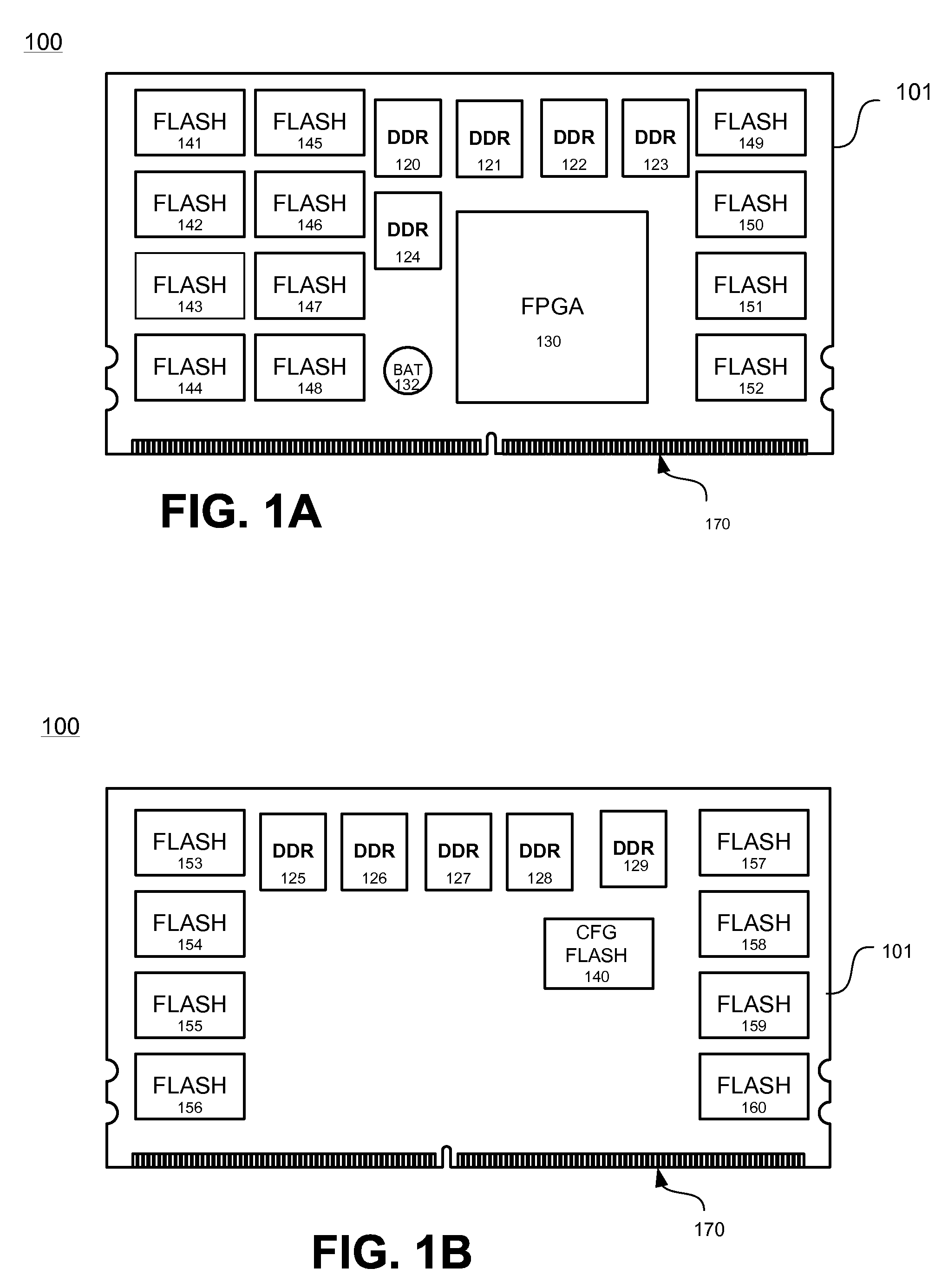

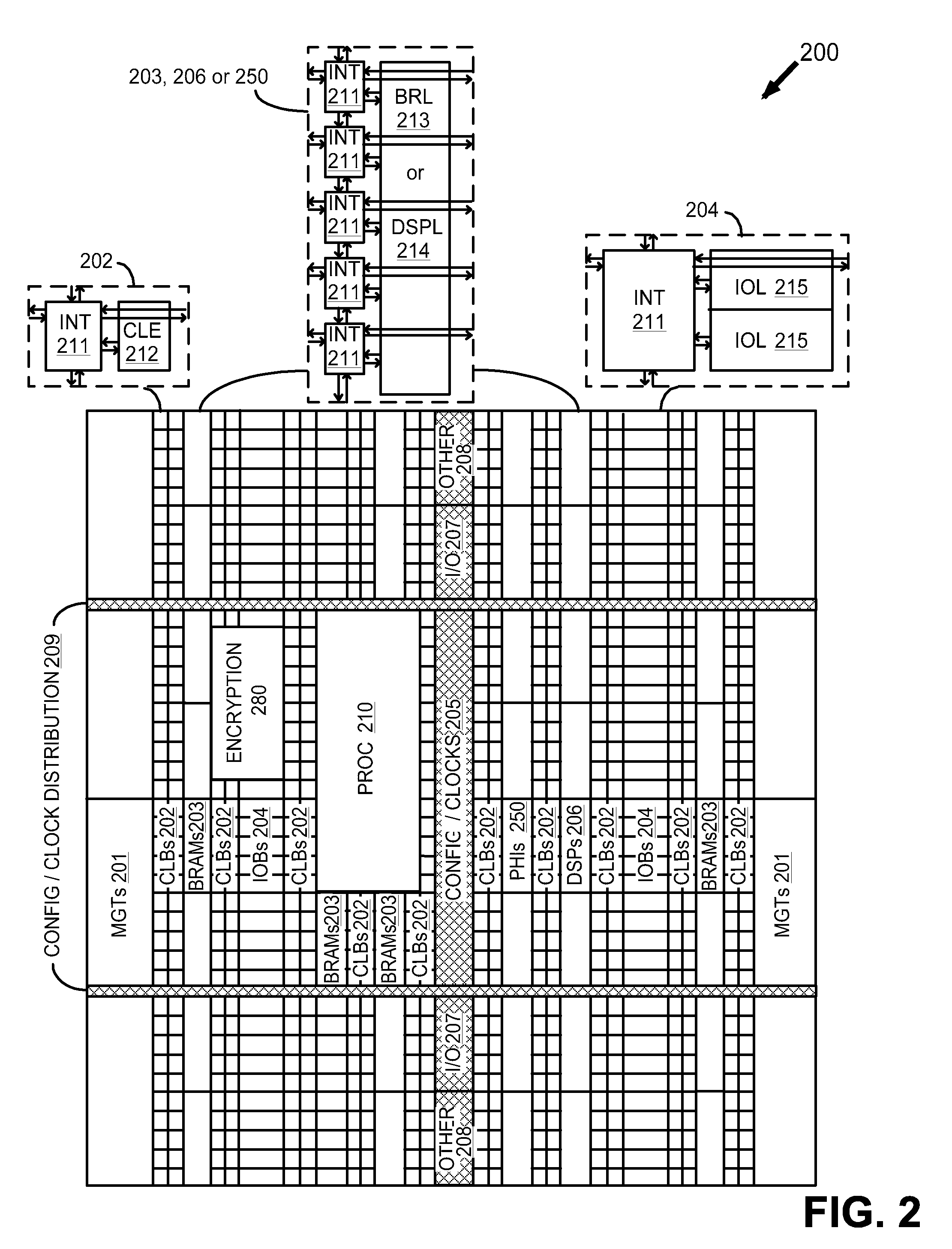

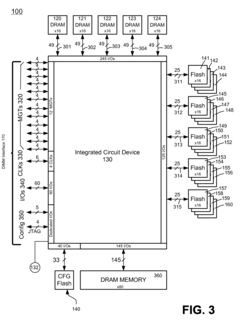

Data storage system with removable memory module having parallel channels of DRAM memory and flash memory

PatentActiveUS8134875B2

Innovation

- A memory module with a circuit board, integrated circuit device having configurable logic, and both DRAM and flash memory devices, allowing for easy updates of wear leveling algorithms and implementation of new flash technologies, reducing physical volume and infrastructure needs.

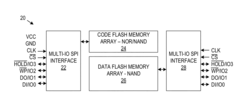

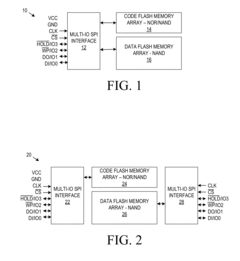

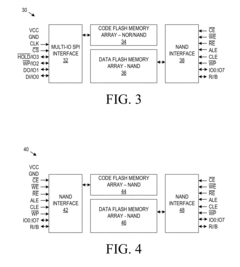

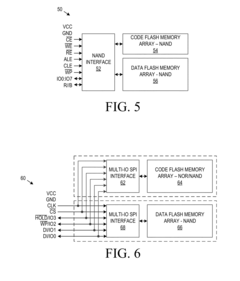

Flash Memory for Code and Data Storage

PatentInactiveUS20150199128A1

Innovation

- A single flash memory solution incorporating a code flash memory array and a data flash memory array with a multi-IO serial interface or NAND memory interface, allowing for random access and configurable as single, dual, or quad SPI, implemented in a single chip or multi-chip package to reduce pin count and cost.

Power Efficiency Considerations

Power consumption has become a critical factor in data storage system design, particularly when comparing DDR5 and Flash memory technologies. DDR5 memory, while offering superior performance in terms of data transfer rates, typically consumes significantly more power than Flash memory during active operations. This power differential stems from DDR5's architecture requiring constant refreshing to maintain data integrity, even when not actively performing read/write operations.

Flash memory demonstrates remarkable power efficiency advantages, particularly in idle states. When not actively accessed, Flash memory cells can maintain stored data with minimal to no power consumption, making it ideal for applications where devices frequently enter low-power states. This characteristic has positioned Flash memory as the preferred solution for mobile devices, IoT applications, and other power-constrained environments.

Recent advancements in DDR5 technology have introduced several power-saving features to address historical inefficiencies. These include improved voltage regulation with on-DIMM voltage regulators, more granular refresh controls, and enhanced power management states. The latest DDR5 modules can operate at lower voltages (1.1V compared to DDR4's 1.2V), representing approximately 8-10% power reduction while delivering higher performance.

Thermal management considerations also factor into the power efficiency equation. DDR5's higher operating temperatures during intensive workloads necessitate additional cooling solutions, which may indirectly increase system power requirements. Conversely, Flash memory operates at lower temperatures, reducing cooling demands and associated power costs in large-scale deployments.

When evaluating total cost of ownership, power efficiency translates directly to operational expenses. Data centers implementing Flash-based storage solutions often report significant reductions in electricity consumption compared to DRAM-based alternatives. Industry analyses suggest that for large-scale deployments, power-related savings from Flash memory can offset its higher initial acquisition costs within 18-24 months of operation.

The environmental impact of power consumption has also become increasingly important in technology evaluation. Organizations with sustainability initiatives are increasingly factoring power efficiency into their storage technology decisions, giving Flash memory an advantage in green computing applications despite its performance limitations compared to DDR5.

Flash memory demonstrates remarkable power efficiency advantages, particularly in idle states. When not actively accessed, Flash memory cells can maintain stored data with minimal to no power consumption, making it ideal for applications where devices frequently enter low-power states. This characteristic has positioned Flash memory as the preferred solution for mobile devices, IoT applications, and other power-constrained environments.

Recent advancements in DDR5 technology have introduced several power-saving features to address historical inefficiencies. These include improved voltage regulation with on-DIMM voltage regulators, more granular refresh controls, and enhanced power management states. The latest DDR5 modules can operate at lower voltages (1.1V compared to DDR4's 1.2V), representing approximately 8-10% power reduction while delivering higher performance.

Thermal management considerations also factor into the power efficiency equation. DDR5's higher operating temperatures during intensive workloads necessitate additional cooling solutions, which may indirectly increase system power requirements. Conversely, Flash memory operates at lower temperatures, reducing cooling demands and associated power costs in large-scale deployments.

When evaluating total cost of ownership, power efficiency translates directly to operational expenses. Data centers implementing Flash-based storage solutions often report significant reductions in electricity consumption compared to DRAM-based alternatives. Industry analyses suggest that for large-scale deployments, power-related savings from Flash memory can offset its higher initial acquisition costs within 18-24 months of operation.

The environmental impact of power consumption has also become increasingly important in technology evaluation. Organizations with sustainability initiatives are increasingly factoring power efficiency into their storage technology decisions, giving Flash memory an advantage in green computing applications despite its performance limitations compared to DDR5.

Cost-Performance Trade-offs

When evaluating DDR5 and Flash Memory technologies for data storage applications, cost-performance trade-offs represent a critical decision factor for system architects and enterprise planners. DDR5 memory commands a significant price premium compared to Flash storage solutions, with cost-per-gigabyte ratios often exceeding 10:1. This substantial price differential necessitates careful consideration of workload requirements and performance needs.

The higher acquisition cost of DDR5 can be justified in latency-sensitive applications where microsecond-level response times directly impact business outcomes. Financial trading platforms, real-time analytics systems, and high-frequency transaction processing environments typically realize sufficient operational benefits to offset the premium investment in DRAM-based solutions.

Flash memory presents a compelling middle ground in the storage hierarchy, offering substantially better performance than traditional hard disk drives while maintaining reasonable cost structures. The introduction of NVMe protocols has further enhanced Flash performance capabilities, narrowing the practical gap with DRAM for many workloads while maintaining significant cost advantages.

Total Cost of Ownership (TCO) calculations reveal additional considerations beyond acquisition costs. DDR5 implementations typically consume more power per capacity unit than Flash storage, resulting in higher operational expenses over system lifetimes. However, this power differential must be balanced against the potential need for additional Flash capacity to achieve comparable application performance.

Tiered storage architectures represent an optimal approach for many organizations, strategically deploying limited DDR5 resources for performance-critical data while leveraging Flash storage for the majority of working datasets. This hybrid approach enables cost-effective scaling while maintaining acceptable performance characteristics across diverse workloads.

Emerging technologies like Storage Class Memory (SCM) are beginning to bridge the price-performance gap between DDR5 and Flash, potentially altering this cost-performance equation in coming years. These solutions offer DRAM-like performance characteristics with pricing models closer to premium Flash storage options.

Market trends indicate gradual price normalization for DDR5 as manufacturing processes mature, while Flash memory continues to benefit from density improvements that drive down per-gigabyte costs. Organizations should consider these trajectories when planning long-term storage infrastructure investments.

The higher acquisition cost of DDR5 can be justified in latency-sensitive applications where microsecond-level response times directly impact business outcomes. Financial trading platforms, real-time analytics systems, and high-frequency transaction processing environments typically realize sufficient operational benefits to offset the premium investment in DRAM-based solutions.

Flash memory presents a compelling middle ground in the storage hierarchy, offering substantially better performance than traditional hard disk drives while maintaining reasonable cost structures. The introduction of NVMe protocols has further enhanced Flash performance capabilities, narrowing the practical gap with DRAM for many workloads while maintaining significant cost advantages.

Total Cost of Ownership (TCO) calculations reveal additional considerations beyond acquisition costs. DDR5 implementations typically consume more power per capacity unit than Flash storage, resulting in higher operational expenses over system lifetimes. However, this power differential must be balanced against the potential need for additional Flash capacity to achieve comparable application performance.

Tiered storage architectures represent an optimal approach for many organizations, strategically deploying limited DDR5 resources for performance-critical data while leveraging Flash storage for the majority of working datasets. This hybrid approach enables cost-effective scaling while maintaining acceptable performance characteristics across diverse workloads.

Emerging technologies like Storage Class Memory (SCM) are beginning to bridge the price-performance gap between DDR5 and Flash, potentially altering this cost-performance equation in coming years. These solutions offer DRAM-like performance characteristics with pricing models closer to premium Flash storage options.

Market trends indicate gradual price normalization for DDR5 as manufacturing processes mature, while Flash memory continues to benefit from density improvements that drive down per-gigabyte costs. Organizations should consider these trajectories when planning long-term storage infrastructure investments.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!