DDR5 vs Non-Volatile Memory: Latency Comparison

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Memory Technology Evolution and Objectives

Memory technology has undergone significant evolution since the introduction of the first dynamic random-access memory (DRAM) in the late 1960s. This progression has been primarily driven by the increasing demands of computing systems for higher bandwidth, greater capacity, and improved energy efficiency. The journey from DDR (Double Data Rate) to DDR5 represents a continuous refinement of volatile memory technology, with each generation offering substantial improvements in performance metrics.

Concurrently, non-volatile memory (NVM) technologies have been developing along a separate but increasingly convergent path. Traditional NVM solutions like Flash memory have been complemented by emerging technologies such as Phase-Change Memory (PCM), Resistive RAM (ReRAM), and Magnetoresistive RAM (MRAM). These technologies aim to bridge the performance gap between volatile memory and storage, offering persistence without power while approaching DRAM-like access speeds.

The comparison between DDR5 and non-volatile memory technologies, particularly regarding latency characteristics, represents a critical juncture in memory system design. DDR5, the latest standard in DRAM technology, offers significant improvements over its predecessors with data rates up to 6400 MT/s and reduced power consumption. However, it remains fundamentally volatile, requiring constant power to maintain stored data.

Non-volatile memory technologies, while preserving data without power, have traditionally suffered from higher latency compared to DRAM. Recent advancements in NVM, however, have substantially reduced this performance gap. Technologies like Intel's Optane (based on 3D XPoint) have demonstrated latencies that, while still higher than DRAM, are significantly lower than conventional storage solutions.

The technical objective of this analysis is to provide a comprehensive comparison of latency characteristics between DDR5 and current non-volatile memory technologies. This includes examining read/write latencies under various workloads, understanding the architectural differences that contribute to these performance disparities, and identifying potential convergence points where these technologies might meet specific application requirements.

Furthermore, this investigation aims to forecast the evolution trajectory of both memory types, considering technological innovations that might further reduce NVM latency or enhance DDR performance. Understanding these trends is crucial for system architects and hardware designers making decisions about memory hierarchies in next-generation computing systems, particularly as workloads become increasingly data-intensive and energy constraints more stringent.

Concurrently, non-volatile memory (NVM) technologies have been developing along a separate but increasingly convergent path. Traditional NVM solutions like Flash memory have been complemented by emerging technologies such as Phase-Change Memory (PCM), Resistive RAM (ReRAM), and Magnetoresistive RAM (MRAM). These technologies aim to bridge the performance gap between volatile memory and storage, offering persistence without power while approaching DRAM-like access speeds.

The comparison between DDR5 and non-volatile memory technologies, particularly regarding latency characteristics, represents a critical juncture in memory system design. DDR5, the latest standard in DRAM technology, offers significant improvements over its predecessors with data rates up to 6400 MT/s and reduced power consumption. However, it remains fundamentally volatile, requiring constant power to maintain stored data.

Non-volatile memory technologies, while preserving data without power, have traditionally suffered from higher latency compared to DRAM. Recent advancements in NVM, however, have substantially reduced this performance gap. Technologies like Intel's Optane (based on 3D XPoint) have demonstrated latencies that, while still higher than DRAM, are significantly lower than conventional storage solutions.

The technical objective of this analysis is to provide a comprehensive comparison of latency characteristics between DDR5 and current non-volatile memory technologies. This includes examining read/write latencies under various workloads, understanding the architectural differences that contribute to these performance disparities, and identifying potential convergence points where these technologies might meet specific application requirements.

Furthermore, this investigation aims to forecast the evolution trajectory of both memory types, considering technological innovations that might further reduce NVM latency or enhance DDR performance. Understanding these trends is crucial for system architects and hardware designers making decisions about memory hierarchies in next-generation computing systems, particularly as workloads become increasingly data-intensive and energy constraints more stringent.

Market Demand Analysis for Low-Latency Memory

The demand for low-latency memory solutions has been growing exponentially across multiple sectors, driven primarily by data-intensive applications requiring real-time processing capabilities. Financial services, particularly high-frequency trading platforms, represent one of the most latency-sensitive markets, where nanosecond advantages translate directly into competitive edges and revenue opportunities. Research indicates that trading firms invest millions annually in memory infrastructure that can reduce transaction latency by even microseconds.

Healthcare applications, especially those involving real-time patient monitoring and diagnostic imaging, constitute another significant market segment demanding ultra-low latency memory. The increasing adoption of AI-assisted diagnostics and surgical procedures requires memory systems capable of processing large datasets with minimal delay, directly impacting patient outcomes in time-critical scenarios.

The gaming industry has evolved into a major driver for low-latency memory adoption, with competitive gaming and eSports creating demand for systems that can render complex environments with imperceptible delay. Consumer expectations for responsive gaming experiences have pushed manufacturers to prioritize memory latency alongside traditional performance metrics like bandwidth and capacity.

Enterprise data centers face mounting pressure to support real-time analytics and decision-making processes. The shift toward edge computing architectures has amplified this need, as processing increasingly occurs closer to data sources rather than in centralized facilities. This architectural evolution demands memory solutions that can deliver data with minimal latency to distributed processing nodes.

Market research projects the global low-latency memory market to grow at a compound annual rate exceeding 15% through 2028, with particularly strong demand in AI/ML workloads where training and inference operations benefit significantly from reduced memory access times. The emergence of autonomous systems across transportation, manufacturing, and smart city applications further expands this market, as these systems require instantaneous data access for safe and effective operation.

The comparison between DDR5 and Non-Volatile Memory solutions represents a critical decision point for system architects. While DDR5 offers improved latency over previous DRAM generations, persistent memory technologies are narrowing this gap while offering additional benefits in power consumption and data persistence. This convergence is reshaping buying patterns, with many organizations adopting hybrid memory architectures that strategically deploy both technologies based on workload characteristics.

Healthcare applications, especially those involving real-time patient monitoring and diagnostic imaging, constitute another significant market segment demanding ultra-low latency memory. The increasing adoption of AI-assisted diagnostics and surgical procedures requires memory systems capable of processing large datasets with minimal delay, directly impacting patient outcomes in time-critical scenarios.

The gaming industry has evolved into a major driver for low-latency memory adoption, with competitive gaming and eSports creating demand for systems that can render complex environments with imperceptible delay. Consumer expectations for responsive gaming experiences have pushed manufacturers to prioritize memory latency alongside traditional performance metrics like bandwidth and capacity.

Enterprise data centers face mounting pressure to support real-time analytics and decision-making processes. The shift toward edge computing architectures has amplified this need, as processing increasingly occurs closer to data sources rather than in centralized facilities. This architectural evolution demands memory solutions that can deliver data with minimal latency to distributed processing nodes.

Market research projects the global low-latency memory market to grow at a compound annual rate exceeding 15% through 2028, with particularly strong demand in AI/ML workloads where training and inference operations benefit significantly from reduced memory access times. The emergence of autonomous systems across transportation, manufacturing, and smart city applications further expands this market, as these systems require instantaneous data access for safe and effective operation.

The comparison between DDR5 and Non-Volatile Memory solutions represents a critical decision point for system architects. While DDR5 offers improved latency over previous DRAM generations, persistent memory technologies are narrowing this gap while offering additional benefits in power consumption and data persistence. This convergence is reshaping buying patterns, with many organizations adopting hybrid memory architectures that strategically deploy both technologies based on workload characteristics.

DDR5 and NVM Technical Challenges

Despite significant advancements in memory technologies, both DDR5 and Non-Volatile Memory (NVM) face substantial technical challenges that impact their performance, particularly regarding latency characteristics. These challenges represent critical barriers to achieving optimal system performance in various computing environments.

DDR5 memory, while offering improved bandwidth over its predecessors, continues to struggle with fundamental latency limitations. The physical architecture of DRAM cells requires constant refreshing, creating inherent access delays. As DDR5 pushes toward higher frequencies (4800-8400 MHz), signal integrity issues become increasingly problematic, requiring more sophisticated equalization techniques and complex timing parameters that can paradoxically increase effective latency in certain operations.

The manufacturing process for DDR5 presents additional challenges, as shrinking process nodes (currently at 10-14nm) leads to increased electrical interference between memory cells. This interference necessitates stronger error correction mechanisms, which introduce additional computational overhead and latency penalties. The power delivery architecture in DDR5, while more efficient overall, requires on-DIMM voltage regulation that introduces new potential points of failure and performance variability.

For Non-Volatile Memory technologies, the primary technical challenge remains the fundamental read/write asymmetry. While NVM offers persistence advantages, the physical mechanisms for writing data (whether phase change, resistive switching, or other technologies) typically require significantly more time and energy than read operations. This asymmetry creates complex performance profiles that are difficult to optimize for varied workloads.

Endurance limitations represent another significant challenge for NVM technologies. The physical stress of write operations gradually degrades cell reliability, necessitating wear-leveling algorithms and error correction techniques that introduce additional latency overhead. This degradation accelerates at smaller process nodes, creating a difficult engineering tradeoff between density, performance, and longevity.

Interface standardization remains problematic across the NVM ecosystem. While technologies like CXL (Compute Express Link) are emerging to provide coherent memory access, the diversity of NVM implementations creates integration challenges. System architects must navigate complex tradeoffs between using NVM as block storage (with associated file system overhead) or as memory-mapped resources (requiring specialized hardware and software support).

Thermal management presents challenges for both technologies but manifests differently. DDR5's higher operating frequencies generate increased heat that must be dissipated effectively to maintain stability. NVM technologies often require precise temperature control during write operations to ensure reliable cell programming, with performance characteristics that can vary significantly across their operating temperature range.

DDR5 memory, while offering improved bandwidth over its predecessors, continues to struggle with fundamental latency limitations. The physical architecture of DRAM cells requires constant refreshing, creating inherent access delays. As DDR5 pushes toward higher frequencies (4800-8400 MHz), signal integrity issues become increasingly problematic, requiring more sophisticated equalization techniques and complex timing parameters that can paradoxically increase effective latency in certain operations.

The manufacturing process for DDR5 presents additional challenges, as shrinking process nodes (currently at 10-14nm) leads to increased electrical interference between memory cells. This interference necessitates stronger error correction mechanisms, which introduce additional computational overhead and latency penalties. The power delivery architecture in DDR5, while more efficient overall, requires on-DIMM voltage regulation that introduces new potential points of failure and performance variability.

For Non-Volatile Memory technologies, the primary technical challenge remains the fundamental read/write asymmetry. While NVM offers persistence advantages, the physical mechanisms for writing data (whether phase change, resistive switching, or other technologies) typically require significantly more time and energy than read operations. This asymmetry creates complex performance profiles that are difficult to optimize for varied workloads.

Endurance limitations represent another significant challenge for NVM technologies. The physical stress of write operations gradually degrades cell reliability, necessitating wear-leveling algorithms and error correction techniques that introduce additional latency overhead. This degradation accelerates at smaller process nodes, creating a difficult engineering tradeoff between density, performance, and longevity.

Interface standardization remains problematic across the NVM ecosystem. While technologies like CXL (Compute Express Link) are emerging to provide coherent memory access, the diversity of NVM implementations creates integration challenges. System architects must navigate complex tradeoffs between using NVM as block storage (with associated file system overhead) or as memory-mapped resources (requiring specialized hardware and software support).

Thermal management presents challenges for both technologies but manifests differently. DDR5's higher operating frequencies generate increased heat that must be dissipated effectively to maintain stability. NVM technologies often require precise temperature control during write operations to ensure reliable cell programming, with performance characteristics that can vary significantly across their operating temperature range.

Current Latency Optimization Solutions

01 DDR5 memory architecture and latency optimization

DDR5 memory architecture introduces improvements to reduce latency through enhanced command protocols, higher data rates, and optimized memory controller designs. These advancements include better bank grouping, improved refresh mechanisms, and more efficient command scheduling that collectively reduce memory access times. The architecture also supports features like Decision Feedback Equalization (DFE) and improved power management that contribute to overall latency reduction while maintaining system stability.- DDR5 memory architecture and latency optimization: DDR5 memory architecture introduces improvements to reduce latency through enhanced command and addressing schemes. These architectures implement optimized refresh operations, improved bank grouping, and advanced timing parameters that allow for more efficient memory access. The technology includes features like Decision Feedback Equalization (DFE) and improved power management that contribute to reduced latency while maintaining data integrity during high-speed operations.

- Non-volatile memory integration with DDR interfaces: Integration of non-volatile memory with DDR interfaces addresses the latency gap between volatile and non-volatile memory technologies. This approach combines the persistence of non-volatile memory with the speed of DDR interfaces, creating hybrid memory systems that optimize for both performance and data retention. The integration includes specialized controllers and buffer systems that manage the different timing requirements of both memory types while maintaining compatibility with existing memory protocols.

- Latency reduction techniques in memory controllers: Advanced memory controllers implement various techniques to reduce latency in both DDR5 and non-volatile memory systems. These include predictive algorithms for data prefetching, intelligent scheduling of memory operations, and specialized caching mechanisms. The controllers dynamically adjust timing parameters based on workload characteristics and implement parallel processing of memory requests to hide latency. Some controllers also feature adaptive training sequences that optimize signal integrity for reduced access times.

- Memory subsystem architecture for latency management: Memory subsystem architectures specifically designed for latency management incorporate buffer components, hierarchical memory organizations, and specialized interconnects. These architectures implement multi-level caching strategies and memory interleaving techniques to reduce effective access times. Some designs feature on-die termination adjustments and impedance matching circuits that minimize signal reflections, thereby reducing latency. Advanced subsystems also include thermal management features that maintain optimal operating conditions for consistent performance.

- Low-latency memory access protocols and signaling: Specialized memory access protocols and signaling techniques are developed to minimize latency in both DDR5 and non-volatile memory systems. These include optimized command sequences, reduced-latency read/write operations, and enhanced signaling methods that improve data transfer rates. Some protocols implement variable burst lengths and fine-grained access controls that allow for more efficient memory utilization. Advanced signaling techniques include equalization methods and timing calibration procedures that compensate for channel impairments and reduce overall system latency.

02 Non-volatile memory latency reduction techniques

Various techniques are employed to reduce latency in non-volatile memory systems, including advanced caching mechanisms, predictive read/write operations, and optimized memory controllers. These approaches involve implementing buffer designs that prioritize frequently accessed data, utilizing parallel access methods, and employing specialized algorithms that minimize the inherent latency disadvantages of non-volatile memory compared to volatile memory systems. Hardware-level optimizations also include improved signal processing and enhanced error correction capabilities.Expand Specific Solutions03 Hybrid memory systems combining DDR5 and non-volatile memory

Hybrid memory architectures integrate DDR5 DRAM with non-volatile memory to balance performance, capacity, and persistence requirements. These systems employ intelligent data placement algorithms that store frequently accessed data in low-latency DDR5 memory while keeping persistent data in non-volatile storage. Memory controllers in these hybrid systems dynamically manage data migration between the different memory types based on access patterns, criticality of data, and system load to optimize overall latency while benefiting from the persistence of non-volatile memory.Expand Specific Solutions04 Memory controller designs for latency management

Advanced memory controller designs specifically address latency challenges in both DDR5 and non-volatile memory systems. These controllers implement sophisticated scheduling algorithms, request queuing mechanisms, and command reordering techniques to minimize wait times and optimize memory access patterns. Features such as speculative reads, prioritized command execution, and adaptive timing parameters allow the controllers to dynamically adjust operations based on workload characteristics, thereby reducing effective memory latency across diverse application scenarios.Expand Specific Solutions05 System-level approaches to memory latency reduction

System-level strategies for reducing memory latency involve architectural innovations beyond the memory components themselves. These include optimized cache hierarchies, memory-aware task scheduling, and hardware-software co-design approaches that consider the unique characteristics of DDR5 and non-volatile memory. Advanced prefetching mechanisms, memory-side processing capabilities, and specialized interconnects between processing units and memory subsystems collectively contribute to minimizing the impact of memory latency on overall system performance.Expand Specific Solutions

Key Memory Manufacturers and Ecosystem

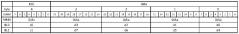

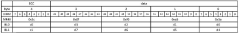

The DDR5 vs Non-Volatile Memory latency comparison market is in a transitional growth phase, with major semiconductor players actively competing to address the performance gap between volatile and non-volatile memory technologies. The global memory market is projected to exceed $200 billion by 2025, driven by data center expansion and AI applications. Samsung Electronics, Micron Technology, and SK hynix lead in DDR5 development, while Intel, Western Digital, and KIOXIA are advancing non-volatile solutions. Research institutions like KAIST and Huazhong University are contributing breakthrough technologies to reduce NVM latency. Companies like Rambus and Netlist are developing hybrid solutions that combine DDR5's speed with NVM's persistence, potentially disrupting traditional memory hierarchies as the industry moves toward computational storage architectures.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed comprehensive solutions comparing DDR5 and Non-Volatile Memory technologies, with particular focus on their Z-NAND technology that bridges the latency gap between DRAM and NAND. Their technical approach involves architectural innovations in both memory types: for DDR5, implementing Decision Feedback Equalization (DFE) and optimized On-Die Termination (ODT) to achieve data rates up to 7.2 Gbps with reduced latency; for NVM, developing Z-NAND with SLC architecture achieving read latencies of approximately 12-20 microseconds compared to DDR5's nanosecond-level latencies. Samsung's comparative analysis demonstrates that while DDR5 maintains superior random access latency (approximately 50-80ns), their Z-NAND significantly narrows the performance gap for specific workloads with 1/10th the latency of conventional NAND.

Strengths: Comprehensive portfolio spanning both DDR5 and various NVM technologies allows for optimized system-level solutions. Samsung's vertical integration enables coordinated advancement across memory types. Weaknesses: Z-NAND still cannot match DDR5's absolute latency performance, limiting applications requiring nanosecond-level response times. Higher cost structure for specialized NVM solutions compared to standard offerings.

Micron Technology, Inc.

Technical Solution: Micron has developed a detailed technical framework for comparing DDR5 and Non-Volatile Memory latency characteristics, particularly through their 3D XPoint technology (previously co-developed with Intel). Their approach quantifies the fundamental latency differences: DDR5 operating at approximately 50-85ns access latency while their 3D XPoint technology achieves 100-340ns for reads - significantly faster than conventional NAND (which operates in microseconds). Micron's technical solution includes architectural optimizations in their DDR5 implementation, such as same-bank refresh operations that allow other banks to remain accessible during refresh cycles, reducing effective latency by up to 16% in high-load scenarios. For NVM comparison, Micron employs a tiered memory architecture that strategically positions different memory types based on latency requirements, with their NVDIMM-P technology serving as a bridge between DDR5 and pure storage-class memory, offering persistent storage with latencies approaching DRAM performance.

Strengths: Micron's 3D XPoint technology provides the lowest latency among non-volatile memories, approaching DRAM-like performance for certain workloads. Their comprehensive understanding of both memory types enables optimal hybrid memory solutions. Weaknesses: Higher cost per bit compared to conventional NAND limits widespread adoption of their lowest-latency NVM solutions. Power consumption remains higher than ideal for some edge computing applications.

Critical Patents in Memory Latency Reduction

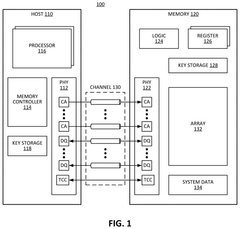

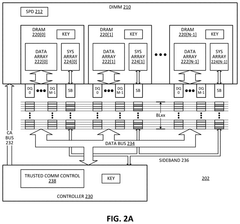

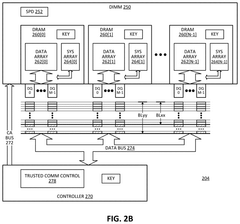

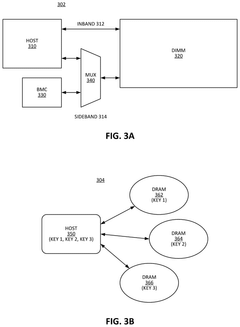

Host-memory certificate exchange for secure access to memory storage and register space

PatentPendingUS20240320347A1

Innovation

- A memory subsystem that establishes a trusted communication channel between the memory controller and memory using certificate exchange for secure key verification, enabling encrypted or scrambled data transmission, which reduces the possibility of hacking and allows access to secure mode registers and error correction features.

Memory system and data processing method

PatentPendingCN118245272A

Innovation

- By introducing a write mode command generation circuit and a mode register in the memory controller, it can determine whether the write data is in the preset mode and generate a write mode command, thereby reducing data transmission power consumption and expanding the application scope of the write mode function.

Power Efficiency vs Latency Trade-offs

The fundamental trade-off between power efficiency and latency in memory technologies represents a critical consideration when comparing DDR5 and Non-Volatile Memory solutions. DDR5 memory operates with significantly lower latency, typically in the nanosecond range (15-30ns), but requires constant power to maintain stored data, resulting in higher overall power consumption, particularly in idle states.

Non-Volatile Memory technologies such as 3D XPoint, MRAM, and NAND-based solutions demonstrate substantially better power efficiency profiles, consuming virtually zero power during idle states since they retain data without requiring power refreshes. However, this power advantage comes at the cost of increased access latencies, with most NVM technologies operating in the microsecond range—approximately 100-1000 times slower than DDR5.

System architects must carefully balance these competing characteristics based on application requirements. For high-performance computing environments where processing speed is paramount, the latency advantage of DDR5 often outweighs power considerations. Conversely, in edge computing, IoT devices, and mobile applications where battery life and thermal management are critical constraints, the superior power efficiency of NVM may justify the latency penalty.

Recent technological advancements have begun addressing this trade-off through hybrid memory architectures. These systems strategically combine DDR5 and NVM technologies, using DDR5 for latency-sensitive operations while leveraging NVM for data persistence and power-efficient storage. Intel's Optane DC Persistent Memory represents one commercial implementation of this approach, positioning NVM alongside DRAM to optimize both performance and power consumption.

The energy-per-bit metric provides a useful framework for quantifying this trade-off. While DDR5 demonstrates excellent performance in active operations (approximately 2-5 pJ/bit), its idle power consumption significantly impacts overall efficiency. NVM technologies typically require more energy per active operation (10-50 pJ/bit) but achieve near-zero idle power, resulting in potentially better efficiency for workloads with intermittent access patterns.

As workload characteristics continue evolving toward more distributed and intermittent computing models, the importance of optimizing this power-latency trade-off grows increasingly significant. Future memory subsystems will likely implement more sophisticated power management techniques, including dynamic switching between memory technologies based on real-time workload demands and power constraints.

Non-Volatile Memory technologies such as 3D XPoint, MRAM, and NAND-based solutions demonstrate substantially better power efficiency profiles, consuming virtually zero power during idle states since they retain data without requiring power refreshes. However, this power advantage comes at the cost of increased access latencies, with most NVM technologies operating in the microsecond range—approximately 100-1000 times slower than DDR5.

System architects must carefully balance these competing characteristics based on application requirements. For high-performance computing environments where processing speed is paramount, the latency advantage of DDR5 often outweighs power considerations. Conversely, in edge computing, IoT devices, and mobile applications where battery life and thermal management are critical constraints, the superior power efficiency of NVM may justify the latency penalty.

Recent technological advancements have begun addressing this trade-off through hybrid memory architectures. These systems strategically combine DDR5 and NVM technologies, using DDR5 for latency-sensitive operations while leveraging NVM for data persistence and power-efficient storage. Intel's Optane DC Persistent Memory represents one commercial implementation of this approach, positioning NVM alongside DRAM to optimize both performance and power consumption.

The energy-per-bit metric provides a useful framework for quantifying this trade-off. While DDR5 demonstrates excellent performance in active operations (approximately 2-5 pJ/bit), its idle power consumption significantly impacts overall efficiency. NVM technologies typically require more energy per active operation (10-50 pJ/bit) but achieve near-zero idle power, resulting in potentially better efficiency for workloads with intermittent access patterns.

As workload characteristics continue evolving toward more distributed and intermittent computing models, the importance of optimizing this power-latency trade-off grows increasingly significant. Future memory subsystems will likely implement more sophisticated power management techniques, including dynamic switching between memory technologies based on real-time workload demands and power constraints.

Data Center Implementation Considerations

When implementing DDR5 and Non-Volatile Memory (NVM) technologies in data center environments, several critical considerations must be addressed to optimize performance, cost-efficiency, and reliability. The latency comparison between these memory technologies directly impacts architectural decisions and deployment strategies.

Data center workloads exhibit diverse memory access patterns, requiring careful evaluation of memory subsystem design. DDR5 offers superior random access performance with latencies typically in the 10-70 nanosecond range, making it ideal for latency-sensitive applications like in-memory databases, real-time analytics, and high-frequency trading platforms. However, implementing DDR5 at scale requires substantial power infrastructure investments due to its higher operating voltages and cooling requirements.

Non-Volatile Memory solutions present compelling alternatives for specific workloads, particularly those involving large datasets with predictable access patterns. Despite higher read latencies (100-300 nanoseconds) and significantly higher write latencies (1-5 microseconds), NVM's persistence capabilities enable innovative architectural approaches like memory-centric computing and reduced recovery times following power events.

Power consumption metrics reveal important implementation considerations. DDR5 typically consumes 1.1V during operation with power spikes during refresh cycles, while NVM technologies generally operate at lower steady-state power levels but experience higher energy consumption during write operations. This differential impacts data center power distribution units (PDUs) and cooling system designs.

Physical infrastructure requirements also differ substantially. DDR5 deployments benefit from proximity to processors to minimize signal integrity issues, whereas many NVM solutions can be deployed with greater physical separation, offering more flexible data center layout options. This flexibility must be balanced against the increased latency that results from greater physical distances.

Total cost of ownership calculations must account for both acquisition costs and operational expenses. While DDR5 modules currently present lower per-gigabyte costs, their volatility necessitates continuous power consumption. NVM solutions, despite higher initial investment, may deliver superior long-term economics through reduced power consumption, simplified backup architectures, and extended replacement cycles.

Hybrid memory architectures, combining both technologies, represent an emerging implementation strategy. These designs utilize DDR5 as a high-speed cache layer with NVM providing capacity-optimized persistent storage, effectively balancing performance requirements with cost constraints while addressing the inherent latency differences between memory technologies.

Data center workloads exhibit diverse memory access patterns, requiring careful evaluation of memory subsystem design. DDR5 offers superior random access performance with latencies typically in the 10-70 nanosecond range, making it ideal for latency-sensitive applications like in-memory databases, real-time analytics, and high-frequency trading platforms. However, implementing DDR5 at scale requires substantial power infrastructure investments due to its higher operating voltages and cooling requirements.

Non-Volatile Memory solutions present compelling alternatives for specific workloads, particularly those involving large datasets with predictable access patterns. Despite higher read latencies (100-300 nanoseconds) and significantly higher write latencies (1-5 microseconds), NVM's persistence capabilities enable innovative architectural approaches like memory-centric computing and reduced recovery times following power events.

Power consumption metrics reveal important implementation considerations. DDR5 typically consumes 1.1V during operation with power spikes during refresh cycles, while NVM technologies generally operate at lower steady-state power levels but experience higher energy consumption during write operations. This differential impacts data center power distribution units (PDUs) and cooling system designs.

Physical infrastructure requirements also differ substantially. DDR5 deployments benefit from proximity to processors to minimize signal integrity issues, whereas many NVM solutions can be deployed with greater physical separation, offering more flexible data center layout options. This flexibility must be balanced against the increased latency that results from greater physical distances.

Total cost of ownership calculations must account for both acquisition costs and operational expenses. While DDR5 modules currently present lower per-gigabyte costs, their volatility necessitates continuous power consumption. NVM solutions, despite higher initial investment, may deliver superior long-term economics through reduced power consumption, simplified backup architectures, and extended replacement cycles.

Hybrid memory architectures, combining both technologies, represent an emerging implementation strategy. These designs utilize DDR5 as a high-speed cache layer with NVM providing capacity-optimized persistent storage, effectively balancing performance requirements with cost constraints while addressing the inherent latency differences between memory technologies.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!