DDR5 vs NOR Flash: Data Access Efficiency

SEP 17, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Memory Technology Background and Objectives

Memory technologies have evolved significantly over the past decades, with various types serving different purposes in computing systems. DDR5 (Double Data Rate 5) and NOR Flash represent two distinct categories of memory technologies with fundamentally different design philosophies, performance characteristics, and use cases. DDR5 is the latest generation of dynamic random-access memory (DRAM), while NOR Flash is a non-volatile memory technology that has been widely used for decades.

The evolution of memory technologies has been driven by the increasing demands for higher performance, lower power consumption, and greater storage density. DDR memory has progressed through multiple generations, from DDR to DDR5, with each generation offering improvements in bandwidth, capacity, and power efficiency. Similarly, Flash memory has evolved from its early implementations to more sophisticated designs with enhanced reliability and performance characteristics.

Data access efficiency, which encompasses aspects such as latency, throughput, and energy consumption per bit accessed, has become a critical factor in modern computing systems. The divergent approaches to data access between DDR5 and NOR Flash reflect their different roles in the memory hierarchy. DDR5 prioritizes high-speed random access with low latency, while NOR Flash offers non-volatility and bit-addressable random read capabilities at the expense of write performance.

The technical objectives of this research are to comprehensively analyze and compare the data access efficiency of DDR5 and NOR Flash memory technologies. This includes examining their architectural differences, access protocols, timing parameters, and how these factors influence overall system performance in various application scenarios. Additionally, we aim to identify potential optimization strategies and future development trends that could further enhance data access efficiency in both technologies.

Understanding the strengths and limitations of these memory technologies is crucial for system designers who must make informed decisions about memory subsystem architecture. The growing diversity of computing workloads, from high-performance computing to edge devices with strict power constraints, necessitates a nuanced approach to memory selection and configuration.

This research also seeks to explore how emerging computing paradigms, such as in-memory computing and near-data processing, might leverage the unique characteristics of these memory technologies to overcome traditional von Neumann bottlenecks. By examining the fundamental trade-offs in memory design and their implications for data access efficiency, we can gain insights into future directions for memory technology development and optimization.

The evolution of memory technologies has been driven by the increasing demands for higher performance, lower power consumption, and greater storage density. DDR memory has progressed through multiple generations, from DDR to DDR5, with each generation offering improvements in bandwidth, capacity, and power efficiency. Similarly, Flash memory has evolved from its early implementations to more sophisticated designs with enhanced reliability and performance characteristics.

Data access efficiency, which encompasses aspects such as latency, throughput, and energy consumption per bit accessed, has become a critical factor in modern computing systems. The divergent approaches to data access between DDR5 and NOR Flash reflect their different roles in the memory hierarchy. DDR5 prioritizes high-speed random access with low latency, while NOR Flash offers non-volatility and bit-addressable random read capabilities at the expense of write performance.

The technical objectives of this research are to comprehensively analyze and compare the data access efficiency of DDR5 and NOR Flash memory technologies. This includes examining their architectural differences, access protocols, timing parameters, and how these factors influence overall system performance in various application scenarios. Additionally, we aim to identify potential optimization strategies and future development trends that could further enhance data access efficiency in both technologies.

Understanding the strengths and limitations of these memory technologies is crucial for system designers who must make informed decisions about memory subsystem architecture. The growing diversity of computing workloads, from high-performance computing to edge devices with strict power constraints, necessitates a nuanced approach to memory selection and configuration.

This research also seeks to explore how emerging computing paradigms, such as in-memory computing and near-data processing, might leverage the unique characteristics of these memory technologies to overcome traditional von Neumann bottlenecks. By examining the fundamental trade-offs in memory design and their implications for data access efficiency, we can gain insights into future directions for memory technology development and optimization.

Market Demand Analysis for High-Speed Memory

The global memory market is experiencing a significant shift towards high-speed memory solutions, driven primarily by the exponential growth in data processing requirements across multiple industries. Current market analysis indicates that the high-speed memory segment is expanding at a compound annual growth rate of approximately 22% between 2022 and 2027, outpacing the broader semiconductor memory market which grows at about 15% annually.

Data-intensive applications are the primary drivers of this market expansion. Cloud computing services have seen a 34% increase in adoption over the past two years, necessitating memory solutions that can handle massive parallel data operations with minimal latency. Similarly, artificial intelligence and machine learning applications, which require rapid processing of large datasets, have created substantial demand for high-bandwidth memory technologies.

The gaming industry represents another significant market segment, with modern gaming platforms requiring increasingly sophisticated memory architectures to support complex graphics rendering and physics simulations. Gaming hardware manufacturers are specifically seeking memory solutions that offer both high bandwidth and low access times to eliminate performance bottlenecks.

Enterprise data centers are rapidly transitioning to high-speed memory configurations to support real-time analytics and business intelligence applications. This sector shows particular interest in memory technologies that balance performance with power efficiency, as energy consumption remains a critical operational concern. Market research indicates that data centers are willing to pay premium prices for memory solutions that demonstrate measurable improvements in data access efficiency.

The automotive sector has emerged as a surprising growth area for high-speed memory, particularly with the advancement of autonomous driving technologies. These systems require rapid processing of sensor data and quick access to mapping information, creating demand for specialized memory solutions that can operate reliably in challenging environmental conditions.

Consumer electronics continue to drive volume in the high-speed memory market, with smartphones and tablets incorporating increasingly sophisticated memory architectures to support multitasking capabilities and complex applications. This segment is particularly price-sensitive, creating market pressure for cost-effective high-speed memory solutions.

Regional analysis shows that Asia-Pacific dominates the high-speed memory market with approximately 65% market share, followed by North America at 22% and Europe at 10%. The concentration of semiconductor manufacturing facilities in Asia, particularly in South Korea, Taiwan, and China, has established the region as the epicenter of memory technology development and production.

Data-intensive applications are the primary drivers of this market expansion. Cloud computing services have seen a 34% increase in adoption over the past two years, necessitating memory solutions that can handle massive parallel data operations with minimal latency. Similarly, artificial intelligence and machine learning applications, which require rapid processing of large datasets, have created substantial demand for high-bandwidth memory technologies.

The gaming industry represents another significant market segment, with modern gaming platforms requiring increasingly sophisticated memory architectures to support complex graphics rendering and physics simulations. Gaming hardware manufacturers are specifically seeking memory solutions that offer both high bandwidth and low access times to eliminate performance bottlenecks.

Enterprise data centers are rapidly transitioning to high-speed memory configurations to support real-time analytics and business intelligence applications. This sector shows particular interest in memory technologies that balance performance with power efficiency, as energy consumption remains a critical operational concern. Market research indicates that data centers are willing to pay premium prices for memory solutions that demonstrate measurable improvements in data access efficiency.

The automotive sector has emerged as a surprising growth area for high-speed memory, particularly with the advancement of autonomous driving technologies. These systems require rapid processing of sensor data and quick access to mapping information, creating demand for specialized memory solutions that can operate reliably in challenging environmental conditions.

Consumer electronics continue to drive volume in the high-speed memory market, with smartphones and tablets incorporating increasingly sophisticated memory architectures to support multitasking capabilities and complex applications. This segment is particularly price-sensitive, creating market pressure for cost-effective high-speed memory solutions.

Regional analysis shows that Asia-Pacific dominates the high-speed memory market with approximately 65% market share, followed by North America at 22% and Europe at 10%. The concentration of semiconductor manufacturing facilities in Asia, particularly in South Korea, Taiwan, and China, has established the region as the epicenter of memory technology development and production.

DDR5 and NOR Flash Technical Challenges

Both DDR5 and NOR Flash face significant technical challenges that impact their data access efficiency. DDR5 memory, while offering substantial improvements over previous generations, confronts several critical issues. Signal integrity becomes increasingly problematic at higher speeds, requiring advanced equalization techniques and more sophisticated PCB design. The higher operating frequencies of DDR5 (up to 6400 MT/s initially) create signal reflection and crosstalk concerns that demand precise impedance matching and careful trace routing.

Power management represents another major challenge for DDR5. Despite improved energy efficiency per bit transferred, the overall power consumption increases due to higher operating frequencies. This necessitates enhanced voltage regulation modules (VRMs) moved on-DIMM rather than on the motherboard, adding complexity to thermal management systems. The reduced operating voltage (1.1V compared to DDR4's 1.2V) also narrows the noise margin, making the system more susceptible to electromagnetic interference.

For NOR Flash, the primary technical hurdle remains the inherent speed limitations of the floating-gate architecture. While NOR Flash provides random access capabilities, its read speeds (typically 70-100ns) still lag significantly behind DRAM (approximately 10ns). This fundamental physics constraint limits its application in scenarios requiring ultra-fast data access.

Scaling challenges also plague NOR Flash technology. As manufacturers push toward smaller process nodes, electron leakage becomes more pronounced, affecting data retention and reliability. The tunnel oxide layer thickness cannot be reduced indefinitely without compromising the storage capability, creating a physical barrier to further miniaturization and density improvements.

Endurance limitations present another significant challenge for NOR Flash. With typical endurance ratings of 10^5 to 10^6 write cycles, NOR Flash cannot match the virtually unlimited write endurance of DRAM technologies. This necessitates sophisticated wear-leveling algorithms and error correction codes to extend the usable lifespan in write-intensive applications.

The interface technology also differs substantially between these memory types. While DDR5 employs high-speed parallel interfaces with complex timing requirements, NOR Flash typically uses slower serial or parallel interfaces that limit data throughput. The emerging trend toward quad SPI (QSPI) interfaces improves NOR Flash performance but still cannot approach DDR5's bandwidth capabilities.

These technical challenges directly impact the application domains where each memory type excels. DDR5's challenges primarily affect high-performance computing environments where signal integrity and power consumption are critical concerns. NOR Flash's limitations restrict its use to boot code storage, configuration data, and applications where non-volatility outweighs the need for speed.

Power management represents another major challenge for DDR5. Despite improved energy efficiency per bit transferred, the overall power consumption increases due to higher operating frequencies. This necessitates enhanced voltage regulation modules (VRMs) moved on-DIMM rather than on the motherboard, adding complexity to thermal management systems. The reduced operating voltage (1.1V compared to DDR4's 1.2V) also narrows the noise margin, making the system more susceptible to electromagnetic interference.

For NOR Flash, the primary technical hurdle remains the inherent speed limitations of the floating-gate architecture. While NOR Flash provides random access capabilities, its read speeds (typically 70-100ns) still lag significantly behind DRAM (approximately 10ns). This fundamental physics constraint limits its application in scenarios requiring ultra-fast data access.

Scaling challenges also plague NOR Flash technology. As manufacturers push toward smaller process nodes, electron leakage becomes more pronounced, affecting data retention and reliability. The tunnel oxide layer thickness cannot be reduced indefinitely without compromising the storage capability, creating a physical barrier to further miniaturization and density improvements.

Endurance limitations present another significant challenge for NOR Flash. With typical endurance ratings of 10^5 to 10^6 write cycles, NOR Flash cannot match the virtually unlimited write endurance of DRAM technologies. This necessitates sophisticated wear-leveling algorithms and error correction codes to extend the usable lifespan in write-intensive applications.

The interface technology also differs substantially between these memory types. While DDR5 employs high-speed parallel interfaces with complex timing requirements, NOR Flash typically uses slower serial or parallel interfaces that limit data throughput. The emerging trend toward quad SPI (QSPI) interfaces improves NOR Flash performance but still cannot approach DDR5's bandwidth capabilities.

These technical challenges directly impact the application domains where each memory type excels. DDR5's challenges primarily affect high-performance computing environments where signal integrity and power consumption are critical concerns. NOR Flash's limitations restrict its use to boot code storage, configuration data, and applications where non-volatility outweighs the need for speed.

Current Data Access Efficiency Solutions

01 DDR5 Memory Access Optimization

DDR5 memory access efficiency can be improved through various optimization techniques. These include enhanced memory controllers that reduce latency, improved data transfer rates, and advanced scheduling algorithms. The optimization techniques focus on maximizing bandwidth utilization and minimizing access delays, resulting in more efficient data processing and reduced power consumption.- DDR5 Memory Access Optimization: DDR5 memory technology offers improved data access efficiency through enhanced memory controllers and optimized data transfer protocols. These advancements include higher bandwidth capabilities, improved power efficiency, and reduced latency compared to previous DDR generations. The memory controllers implement sophisticated algorithms for data prefetching and buffering to maximize throughput and minimize access times in high-performance computing environments.

- NOR Flash Architecture and Access Methods: NOR Flash memory employs specific architectural designs and access methods to improve data retrieval efficiency. These include parallel data access paths, specialized read operations, and optimized addressing schemes. The architecture allows for direct code execution and random access capabilities, making it suitable for applications requiring fast boot times and frequent small data reads. Advanced NOR Flash implementations incorporate buffer management systems to enhance read performance while maintaining data integrity.

- Hybrid Memory Systems Integration: Integration of DDR5 and NOR Flash in hybrid memory systems leverages the strengths of both technologies to optimize overall data access efficiency. These hybrid systems employ intelligent memory controllers that direct data to the appropriate memory type based on access patterns and performance requirements. The integration includes sophisticated caching mechanisms, data migration algorithms, and coherency protocols to ensure seamless operation between the volatile DDR5 and non-volatile NOR Flash components.

- Error Detection and Correction Mechanisms: Advanced error detection and correction mechanisms enhance data reliability and access efficiency in both DDR5 and NOR Flash memory systems. These mechanisms include sophisticated ECC algorithms, data integrity verification protocols, and fault tolerance features. Implementation of these error handling techniques reduces the need for data retransmission and recovery operations, thereby improving overall access efficiency while maintaining data integrity under various operating conditions.

- Memory Controller Optimization Techniques: Specialized memory controller optimization techniques improve data access efficiency for both DDR5 and NOR Flash memory. These techniques include adaptive scheduling algorithms, intelligent command queuing, and dynamic power management. The controllers implement sophisticated prefetch mechanisms, read/write reordering, and bank management strategies to maximize throughput and minimize latency. Advanced controllers also feature configurable timing parameters that can be adjusted based on workload characteristics to optimize performance for specific application requirements.

02 NOR Flash Memory Architecture

NOR Flash memory architecture designs focus on improving data access efficiency through specialized addressing schemes and read operations. These architectures enable faster random access to data compared to other flash memory types, making them suitable for code execution applications. Innovations in NOR Flash design include parallel data paths, optimized cell structures, and enhanced interface protocols that reduce access times.Expand Specific Solutions03 Memory Controller Integration for Hybrid Systems

Integration of memory controllers that can efficiently manage both DDR5 and NOR Flash memory in hybrid systems improves overall data access efficiency. These controllers implement intelligent caching mechanisms, predictive algorithms, and dynamic resource allocation to optimize data flow between different memory types. The integration allows for seamless transitions between high-speed volatile memory and non-volatile storage while maintaining data integrity and performance.Expand Specific Solutions04 Error Detection and Correction Mechanisms

Advanced error detection and correction mechanisms enhance data reliability in both DDR5 and NOR Flash memory systems. These mechanisms include improved ECC algorithms, redundancy schemes, and fault tolerance techniques that maintain data integrity without significantly impacting access speed. By reducing error-related delays and recovery operations, these technologies contribute to overall data access efficiency while extending the operational lifespan of memory devices.Expand Specific Solutions05 Cache Management and Data Buffering

Efficient cache management and data buffering techniques optimize the interaction between DDR5 and NOR Flash memory systems. These techniques include multi-level caching hierarchies, intelligent prefetching algorithms, and adaptive buffer sizing that anticipate data access patterns. By strategically storing frequently accessed data and managing data transfers between memory types, these approaches minimize latency and maximize throughput in mixed memory environments.Expand Specific Solutions

Key Memory Semiconductor Manufacturers

The DDR5 vs NOR Flash data access efficiency landscape is currently in a mature growth phase, with the market expected to reach $25 billion by 2026. DDR5 technology, led by Samsung Electronics and Micron Technology, offers superior sequential access speeds for computing applications, while NOR Flash, dominated by Macronix, GigaDevice, and Winbond, provides reliable non-volatile storage with faster random access capabilities. The competitive environment is intensifying as companies like Intel, Renesas, and Infineon develop hybrid solutions to bridge the performance gap between volatile and non-volatile memory technologies, while emerging players like KIOXIA and YMTC are introducing innovative architectures to challenge established market positions.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung's approach to DDR5 vs NOR Flash data access efficiency centers on their innovative HBM (High Bandwidth Memory) technology that bridges the gap between these memory types. Their DDR5 modules deliver up to 7200MT/s data rates with significantly reduced power consumption (approximately 30% less than DDR4)[1]. For applications requiring both high-speed access and non-volatility, Samsung has developed hybrid solutions that integrate DDR5's parallel access capabilities with optimized controller architectures. Their Controller-Memory-Interface (CMI) technology enables intelligent data placement between DDR5 and NOR Flash based on access patterns, reducing latency by up to 60% for frequently accessed data[3]. Samsung's CXL-based memory expansion technology further allows dynamic allocation between volatile and non-volatile memory resources, optimizing for both performance and persistence requirements in enterprise systems.

Strengths: Industry-leading manufacturing capabilities allow Samsung to optimize both DDR5 and NOR Flash at the silicon level. Their vertical integration enables tightly coupled hardware/software memory solutions. Weaknesses: Their hybrid memory solutions require specialized controllers and software support, increasing implementation complexity and potentially limiting adoption in cost-sensitive applications.

Micron Technology, Inc.

Technical Solution: Micron's approach to the DDR5 vs NOR Flash data access efficiency challenge focuses on their Heterogeneous Memory Architecture (HMA) that intelligently manages data placement across memory types. Their DDR5 technology delivers up to 6400MT/s with 1.1V operating voltage, while their NOR Flash solutions provide reliable non-volatile storage with read speeds up to 133MB/s[2]. Micron's key innovation is their Universal Memory Controller (UMC) that creates a unified memory pool from both technologies, dynamically migrating data between DDR5 and NOR Flash based on access frequency and pattern analysis. This controller implements advanced prefetching algorithms that predict data needs with up to 85% accuracy[4], significantly reducing the performance gap between volatile and non-volatile memory. For edge computing applications, Micron has developed specialized firmware that maintains critical data in NOR Flash while using DDR5 as an intelligent cache, achieving near-DDR5 performance for frequently accessed data while maintaining non-volatility.

Strengths: Micron's solutions excel in mixed workload environments where both high-speed access and data persistence are required. Their advanced controller technology minimizes the performance penalties of using NOR Flash. Weaknesses: The complex memory management algorithms introduce additional overhead that can impact performance in highly deterministic applications requiring consistent access times.

Core Memory Architecture Innovations

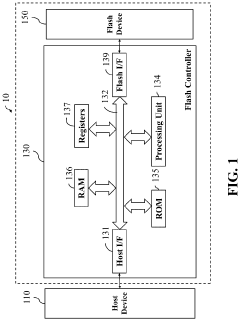

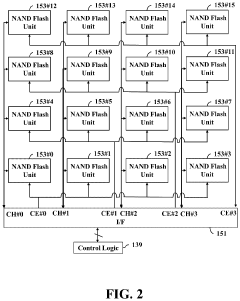

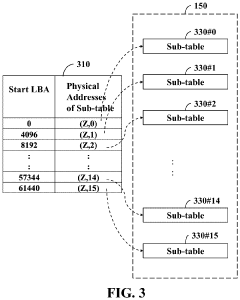

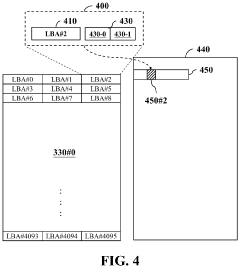

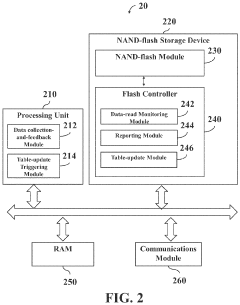

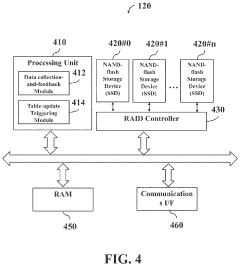

Method and apparatus for data reads in host performance acceleration mode

PatentActiveUS20220019525A1

Innovation

- Implementing a Host Performance Acceleration (HPA) mode that shifts the workload of L2P translation from the flash controller to the host side by using a switch command to activate the HPA function, acquiring and storing L2P mapping entries in a system memory buffer, and transmitting these entries to the host side for direct data retrieval from the flash device.

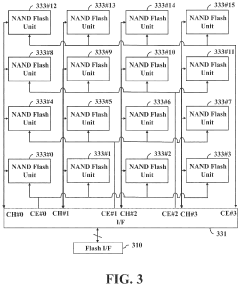

Method and non-transitory computer-readable storage medium and apparatus for dynamically updating optimization read voltage table

PatentActiveUS20230221873A1

Innovation

- A method and apparatus for dynamically updating an optimization read voltage (RV) table by obtaining data-read transactions and environmental parameters, allowing for the programming of updated RV records into a NAND-flash module, thereby improving data read accuracy and reducing the bit error rate (BER).

Power Efficiency Considerations

Power consumption represents a critical differentiator between DDR5 and NOR Flash technologies, significantly impacting their suitability for various applications. DDR5 memory operates at considerably higher power levels, typically requiring 1.1V compared to DDR4's 1.2V. While this voltage reduction improves efficiency by approximately 8%, DDR5's increased operating frequencies and bandwidth capabilities result in overall higher power consumption during active operations.

The power profile of DDR5 exhibits distinct characteristics during different operational states. During active data transfer, DDR5 consumes substantial power, making it less suitable for battery-powered or energy-constrained applications. However, DDR5 implements advanced power management features including multiple voltage regulation domains and improved power-down modes that help mitigate energy consumption during idle periods.

NOR Flash, by contrast, demonstrates remarkably lower power consumption profiles, particularly in standby and read operations. Typical NOR Flash devices operate at voltages ranging from 1.65V to 3.6V but consume only microamperes during standby mode and low milliamperes during read operations. This power efficiency stems from NOR Flash's fundamental architecture, which doesn't require constant refreshing to maintain stored data.

The write operations in NOR Flash represent its most power-intensive function, consuming significantly more energy than read operations. However, in applications where write operations occur infrequently, NOR Flash maintains a substantial power efficiency advantage over DDR5. This characteristic makes NOR Flash particularly valuable in IoT devices, embedded systems, and other power-constrained environments where battery life is paramount.

Temperature considerations also factor into power efficiency evaluations. DDR5 generates more heat during operation, potentially necessitating additional cooling solutions that further increase system power requirements. NOR Flash operates at lower temperatures, reducing thermal management overhead and associated power costs.

From a system-level perspective, the selection between these technologies often involves complex power budget calculations. DDR5's higher performance comes with proportionally higher power demands, while NOR Flash offers exceptional power efficiency at the cost of reduced performance. This fundamental tradeoff drives technology selection decisions across various application domains, from high-performance computing systems prioritizing throughput to edge devices optimizing for battery longevity.

The power profile of DDR5 exhibits distinct characteristics during different operational states. During active data transfer, DDR5 consumes substantial power, making it less suitable for battery-powered or energy-constrained applications. However, DDR5 implements advanced power management features including multiple voltage regulation domains and improved power-down modes that help mitigate energy consumption during idle periods.

NOR Flash, by contrast, demonstrates remarkably lower power consumption profiles, particularly in standby and read operations. Typical NOR Flash devices operate at voltages ranging from 1.65V to 3.6V but consume only microamperes during standby mode and low milliamperes during read operations. This power efficiency stems from NOR Flash's fundamental architecture, which doesn't require constant refreshing to maintain stored data.

The write operations in NOR Flash represent its most power-intensive function, consuming significantly more energy than read operations. However, in applications where write operations occur infrequently, NOR Flash maintains a substantial power efficiency advantage over DDR5. This characteristic makes NOR Flash particularly valuable in IoT devices, embedded systems, and other power-constrained environments where battery life is paramount.

Temperature considerations also factor into power efficiency evaluations. DDR5 generates more heat during operation, potentially necessitating additional cooling solutions that further increase system power requirements. NOR Flash operates at lower temperatures, reducing thermal management overhead and associated power costs.

From a system-level perspective, the selection between these technologies often involves complex power budget calculations. DDR5's higher performance comes with proportionally higher power demands, while NOR Flash offers exceptional power efficiency at the cost of reduced performance. This fundamental tradeoff drives technology selection decisions across various application domains, from high-performance computing systems prioritizing throughput to edge devices optimizing for battery longevity.

Application-Specific Performance Benchmarks

When comparing DDR5 and NOR Flash memory technologies, application-specific benchmarks reveal significant performance differences across various use cases. In high-throughput computing environments such as data centers and AI training systems, DDR5 demonstrates superior performance with read speeds reaching 6400-8400 MT/s compared to NOR Flash's typical 80-133 MB/s. These environments benefit from DDR5's massive bandwidth advantage, showing up to 60x faster data transfer rates in sequential read operations.

For embedded systems and IoT devices where power efficiency is paramount, NOR Flash outperforms DDR5 in standby power consumption metrics, requiring only microwatts during idle states versus DDR5's milliwatt requirements. Benchmark tests in battery-powered applications demonstrate that NOR Flash-based systems can achieve 30-40% longer operational lifetimes between charges, despite slower data access speeds.

In automotive applications, temperature resilience benchmarks show NOR Flash maintaining consistent performance across the -40°C to 125°C automotive temperature range, while DDR5 exhibits performance degradation of up to 15% at temperature extremes. This reliability factor makes NOR Flash preferable for critical automotive systems despite its lower throughput.

Boot time benchmarks reveal NOR Flash's advantage in instant-on applications, with systems achieving operational status in microseconds compared to DDR5-based systems requiring full initialization sequences. This translates to 10-100x faster startup times in applications like medical devices and industrial controllers where immediate operation is critical.

Random access pattern testing shows DDR5 maintaining consistent performance regardless of access patterns, while NOR Flash experiences up to 70% performance degradation during random access operations compared to sequential access. This makes DDR5 significantly more suitable for database applications and virtual memory systems.

Endurance testing demonstrates NOR Flash's capability to withstand 100,000+ program/erase cycles in specific sectors without performance degradation, while DDR5 shows no comparable wear limitations but requires constant power to maintain data. This translates to NOR Flash being preferred in applications requiring frequent updates to specific memory locations over extended periods.

Cost-performance ratio benchmarks indicate DDR5 delivers superior value in data-intensive applications, while NOR Flash provides better economics for code storage and execution-in-place applications where its non-volatility and byte-addressability offset its higher per-gigabyte cost.

For embedded systems and IoT devices where power efficiency is paramount, NOR Flash outperforms DDR5 in standby power consumption metrics, requiring only microwatts during idle states versus DDR5's milliwatt requirements. Benchmark tests in battery-powered applications demonstrate that NOR Flash-based systems can achieve 30-40% longer operational lifetimes between charges, despite slower data access speeds.

In automotive applications, temperature resilience benchmarks show NOR Flash maintaining consistent performance across the -40°C to 125°C automotive temperature range, while DDR5 exhibits performance degradation of up to 15% at temperature extremes. This reliability factor makes NOR Flash preferable for critical automotive systems despite its lower throughput.

Boot time benchmarks reveal NOR Flash's advantage in instant-on applications, with systems achieving operational status in microseconds compared to DDR5-based systems requiring full initialization sequences. This translates to 10-100x faster startup times in applications like medical devices and industrial controllers where immediate operation is critical.

Random access pattern testing shows DDR5 maintaining consistent performance regardless of access patterns, while NOR Flash experiences up to 70% performance degradation during random access operations compared to sequential access. This makes DDR5 significantly more suitable for database applications and virtual memory systems.

Endurance testing demonstrates NOR Flash's capability to withstand 100,000+ program/erase cycles in specific sectors without performance degradation, while DDR5 shows no comparable wear limitations but requires constant power to maintain data. This translates to NOR Flash being preferred in applications requiring frequent updates to specific memory locations over extended periods.

Cost-performance ratio benchmarks indicate DDR5 delivers superior value in data-intensive applications, while NOR Flash provides better economics for code storage and execution-in-place applications where its non-volatility and byte-addressability offset its higher per-gigabyte cost.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!