How Chiplet-Based Systems Optimize Energy Efficiency Metrics?

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Technology Evolution and Objectives

Chiplet technology has emerged as a revolutionary approach in semiconductor design, offering a paradigm shift in how integrated circuits are conceived and manufactured. The evolution of chiplets can be traced back to the early 2010s when the limitations of monolithic chip designs became increasingly apparent. As Moore's Law began to slow down, chiplets presented a viable solution to continue scaling performance and efficiency.

The primary objective of chiplet technology is to overcome the challenges associated with traditional monolithic chip designs. These challenges include increased manufacturing costs, reduced yield rates, and limitations in integrating diverse functionalities on a single die. By disaggregating complex systems into smaller, more manageable components, chiplets aim to enhance overall system performance, improve manufacturing yields, and reduce costs.

One of the key drivers behind chiplet technology is the pursuit of improved energy efficiency. As data centers and high-performance computing systems face growing demands for processing power, the need for more energy-efficient solutions has become paramount. Chiplets offer a promising avenue to optimize energy efficiency metrics by allowing for more precise power management and thermal control at a granular level.

The evolution of chiplet technology has been marked by several significant milestones. Initially, the focus was on developing standardized interfaces and protocols to enable seamless communication between different chiplets. This led to the creation of industry standards such as Advanced Interface Bus (AIB) and Universal Chiplet Interconnect Express (UCIe), which have played crucial roles in fostering interoperability and accelerating adoption.

As the technology matured, attention shifted towards refining packaging techniques to support high-density interconnects between chiplets. Advanced packaging technologies like 2.5D and 3D integration have been instrumental in realizing the full potential of chiplet-based designs, enabling tighter integration and improved performance characteristics.

The objectives of chiplet technology extend beyond mere performance gains. They encompass a broader vision of creating more flexible, scalable, and cost-effective semiconductor solutions. By enabling the mix-and-match of different functional blocks, chiplets offer unprecedented design flexibility, allowing manufacturers to tailor solutions to specific application requirements more efficiently.

Looking ahead, the goals of chiplet technology include further miniaturization, enhanced power efficiency, and improved thermal management. Research efforts are focused on developing novel interconnect technologies, exploring new materials for chiplet substrates, and optimizing system-level integration strategies. These advancements aim to push the boundaries of what's possible in terms of computing power, energy efficiency, and overall system performance.

The primary objective of chiplet technology is to overcome the challenges associated with traditional monolithic chip designs. These challenges include increased manufacturing costs, reduced yield rates, and limitations in integrating diverse functionalities on a single die. By disaggregating complex systems into smaller, more manageable components, chiplets aim to enhance overall system performance, improve manufacturing yields, and reduce costs.

One of the key drivers behind chiplet technology is the pursuit of improved energy efficiency. As data centers and high-performance computing systems face growing demands for processing power, the need for more energy-efficient solutions has become paramount. Chiplets offer a promising avenue to optimize energy efficiency metrics by allowing for more precise power management and thermal control at a granular level.

The evolution of chiplet technology has been marked by several significant milestones. Initially, the focus was on developing standardized interfaces and protocols to enable seamless communication between different chiplets. This led to the creation of industry standards such as Advanced Interface Bus (AIB) and Universal Chiplet Interconnect Express (UCIe), which have played crucial roles in fostering interoperability and accelerating adoption.

As the technology matured, attention shifted towards refining packaging techniques to support high-density interconnects between chiplets. Advanced packaging technologies like 2.5D and 3D integration have been instrumental in realizing the full potential of chiplet-based designs, enabling tighter integration and improved performance characteristics.

The objectives of chiplet technology extend beyond mere performance gains. They encompass a broader vision of creating more flexible, scalable, and cost-effective semiconductor solutions. By enabling the mix-and-match of different functional blocks, chiplets offer unprecedented design flexibility, allowing manufacturers to tailor solutions to specific application requirements more efficiently.

Looking ahead, the goals of chiplet technology include further miniaturization, enhanced power efficiency, and improved thermal management. Research efforts are focused on developing novel interconnect technologies, exploring new materials for chiplet substrates, and optimizing system-level integration strategies. These advancements aim to push the boundaries of what's possible in terms of computing power, energy efficiency, and overall system performance.

Energy Efficiency Market Drivers

The energy efficiency market is experiencing significant growth, driven by several key factors that are shaping the demand for chiplet-based systems. As global energy consumption continues to rise, there is an increasing focus on reducing power consumption and improving energy efficiency across various industries. This trend is particularly pronounced in the data center and high-performance computing sectors, where energy costs represent a substantial portion of operational expenses.

One of the primary drivers for energy-efficient chiplet-based systems is the exponential growth of data processing requirements. With the proliferation of cloud computing, artificial intelligence, and big data analytics, there is an unprecedented demand for computational power. However, this increased processing capability must be balanced with energy consumption to maintain sustainable operations and reduce environmental impact. Chiplet-based systems offer a solution by allowing for more efficient use of silicon and improved thermal management, which directly translates to better energy efficiency metrics.

The rising costs of energy and the implementation of stricter environmental regulations are also pushing organizations to seek more energy-efficient computing solutions. Governments and regulatory bodies worldwide are setting ambitious targets for reducing carbon emissions, which is compelling businesses to adopt greener technologies. Chiplet-based systems, with their potential for optimized energy consumption, align well with these sustainability goals and help companies meet their environmental commitments while potentially reducing operational costs.

Moreover, the mobile and edge computing markets are driving demand for energy-efficient chiplets. As devices become more powerful and feature-rich, there is a growing need for processors that can deliver high performance within tight power envelopes. Chiplet-based designs allow for the integration of specialized components that can be optimized for specific tasks, leading to improved energy efficiency in mobile devices and edge computing nodes.

The Internet of Things (IoT) ecosystem is another significant market driver for energy-efficient chiplets. With billions of connected devices expected to be deployed in the coming years, there is a critical need for low-power, high-performance computing solutions. Chiplet-based systems can offer the flexibility and efficiency required to power a wide range of IoT devices, from simple sensors to complex edge computing platforms, while minimizing energy consumption and extending battery life.

Lastly, the competitive landscape in the semiconductor industry is pushing manufacturers to innovate in energy efficiency. As traditional Moore's Law scaling becomes more challenging and expensive, chiplet-based designs offer a path to continued performance improvements while maintaining or reducing power consumption. This approach allows companies to differentiate their products and gain a competitive edge in markets where energy efficiency is a key selling point.

One of the primary drivers for energy-efficient chiplet-based systems is the exponential growth of data processing requirements. With the proliferation of cloud computing, artificial intelligence, and big data analytics, there is an unprecedented demand for computational power. However, this increased processing capability must be balanced with energy consumption to maintain sustainable operations and reduce environmental impact. Chiplet-based systems offer a solution by allowing for more efficient use of silicon and improved thermal management, which directly translates to better energy efficiency metrics.

The rising costs of energy and the implementation of stricter environmental regulations are also pushing organizations to seek more energy-efficient computing solutions. Governments and regulatory bodies worldwide are setting ambitious targets for reducing carbon emissions, which is compelling businesses to adopt greener technologies. Chiplet-based systems, with their potential for optimized energy consumption, align well with these sustainability goals and help companies meet their environmental commitments while potentially reducing operational costs.

Moreover, the mobile and edge computing markets are driving demand for energy-efficient chiplets. As devices become more powerful and feature-rich, there is a growing need for processors that can deliver high performance within tight power envelopes. Chiplet-based designs allow for the integration of specialized components that can be optimized for specific tasks, leading to improved energy efficiency in mobile devices and edge computing nodes.

The Internet of Things (IoT) ecosystem is another significant market driver for energy-efficient chiplets. With billions of connected devices expected to be deployed in the coming years, there is a critical need for low-power, high-performance computing solutions. Chiplet-based systems can offer the flexibility and efficiency required to power a wide range of IoT devices, from simple sensors to complex edge computing platforms, while minimizing energy consumption and extending battery life.

Lastly, the competitive landscape in the semiconductor industry is pushing manufacturers to innovate in energy efficiency. As traditional Moore's Law scaling becomes more challenging and expensive, chiplet-based designs offer a path to continued performance improvements while maintaining or reducing power consumption. This approach allows companies to differentiate their products and gain a competitive edge in markets where energy efficiency is a key selling point.

Chiplet Integration Challenges

Chiplet integration presents several significant challenges that must be addressed to fully realize the potential of chiplet-based systems in optimizing energy efficiency metrics. One of the primary hurdles is the development of advanced packaging technologies capable of accommodating the high-density interconnects required for chiplet-to-chiplet communication. Current packaging solutions often struggle to provide the necessary bandwidth and signal integrity while maintaining low power consumption.

Another critical challenge lies in the design and implementation of efficient inter-chiplet communication protocols. These protocols must balance the need for high-speed data transfer with minimal power overhead, a task that becomes increasingly complex as the number of chiplets in a system grows. Ensuring low-latency, high-bandwidth communication between chiplets while minimizing energy consumption remains a key area of focus for researchers and engineers.

Thermal management poses yet another significant obstacle in chiplet integration. As multiple chiplets are packed closely together, heat dissipation becomes a critical concern. Ineffective thermal management can lead to reduced performance, increased power consumption, and potential reliability issues. Developing innovative cooling solutions that can efficiently remove heat from densely packed chiplet assemblies is crucial for maintaining optimal energy efficiency.

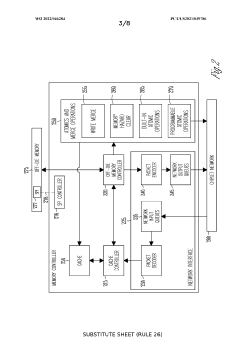

Power distribution and management across multiple chiplets present additional challenges. Ensuring uniform and stable power delivery to each chiplet, while minimizing power loss in the distribution network, requires careful design considerations. Furthermore, implementing effective power gating and dynamic voltage and frequency scaling (DVFS) techniques across multiple chiplets adds another layer of complexity to the power management strategy.

The heterogeneous nature of chiplet-based systems also introduces challenges in system-level optimization. Integrating chiplets with different process technologies, functionalities, and power characteristics requires sophisticated design methodologies and tools. Balancing workload distribution across chiplets to maximize energy efficiency while meeting performance requirements demands advanced scheduling and resource allocation algorithms.

Testing and validation of chiplet-based systems present unique challenges compared to monolithic designs. Ensuring the reliability and performance of inter-chiplet connections, as well as validating the functionality of the entire system, requires new testing methodologies and infrastructure. This complexity can potentially impact time-to-market and overall system cost, factors that must be carefully considered in the context of energy efficiency optimization.

Another critical challenge lies in the design and implementation of efficient inter-chiplet communication protocols. These protocols must balance the need for high-speed data transfer with minimal power overhead, a task that becomes increasingly complex as the number of chiplets in a system grows. Ensuring low-latency, high-bandwidth communication between chiplets while minimizing energy consumption remains a key area of focus for researchers and engineers.

Thermal management poses yet another significant obstacle in chiplet integration. As multiple chiplets are packed closely together, heat dissipation becomes a critical concern. Ineffective thermal management can lead to reduced performance, increased power consumption, and potential reliability issues. Developing innovative cooling solutions that can efficiently remove heat from densely packed chiplet assemblies is crucial for maintaining optimal energy efficiency.

Power distribution and management across multiple chiplets present additional challenges. Ensuring uniform and stable power delivery to each chiplet, while minimizing power loss in the distribution network, requires careful design considerations. Furthermore, implementing effective power gating and dynamic voltage and frequency scaling (DVFS) techniques across multiple chiplets adds another layer of complexity to the power management strategy.

The heterogeneous nature of chiplet-based systems also introduces challenges in system-level optimization. Integrating chiplets with different process technologies, functionalities, and power characteristics requires sophisticated design methodologies and tools. Balancing workload distribution across chiplets to maximize energy efficiency while meeting performance requirements demands advanced scheduling and resource allocation algorithms.

Testing and validation of chiplet-based systems present unique challenges compared to monolithic designs. Ensuring the reliability and performance of inter-chiplet connections, as well as validating the functionality of the entire system, requires new testing methodologies and infrastructure. This complexity can potentially impact time-to-market and overall system cost, factors that must be carefully considered in the context of energy efficiency optimization.

Current Chiplet Energy Optimization Techniques

01 Power management in chiplet-based systems

Chiplet-based systems implement advanced power management techniques to optimize energy efficiency. These include dynamic voltage and frequency scaling, power gating of unused chiplets, and intelligent workload distribution across chiplets to balance power consumption and performance.- Power management in chiplet-based systems: Chiplet-based systems implement advanced power management techniques to optimize energy efficiency. These include dynamic voltage and frequency scaling, power gating of unused chiplets, and intelligent workload distribution across chiplets to balance power consumption and performance.

- Interconnect optimization for energy efficiency: Energy-efficient interconnect technologies are crucial in chiplet-based systems. This includes the use of advanced packaging techniques, high-bandwidth and low-power interfaces between chiplets, and optimized data routing strategies to minimize communication overhead and power consumption.

- Thermal management in chiplet architectures: Effective thermal management is essential for maintaining energy efficiency in chiplet-based systems. This involves innovative cooling solutions, thermal-aware chiplet placement, and dynamic thermal management techniques to optimize performance while minimizing power consumption.

- Heterogeneous integration for task-specific efficiency: Chiplet-based systems leverage heterogeneous integration to combine specialized chiplets optimized for specific tasks. This approach allows for more efficient processing of diverse workloads, resulting in improved overall system energy efficiency compared to monolithic designs.

- AI-driven energy optimization in chiplet systems: Artificial intelligence techniques are employed to dynamically optimize energy efficiency in chiplet-based systems. This includes AI-powered workload prediction, adaptive power management, and intelligent resource allocation across chiplets to maximize performance per watt.

02 Interconnect optimization for chiplet communication

Energy-efficient interconnect technologies are crucial for chiplet-based systems. This includes the use of high-bandwidth, low-power interfaces between chiplets, such as advanced packaging techniques and silicon interposers, to reduce communication overhead and improve overall system efficiency.Expand Specific Solutions03 Thermal management in chiplet designs

Effective thermal management is essential for maintaining energy efficiency in chiplet-based systems. This involves innovative cooling solutions, thermal-aware chiplet placement, and dynamic thermal management techniques to optimize performance while minimizing power consumption.Expand Specific Solutions04 Heterogeneous integration for task-specific efficiency

Chiplet-based systems leverage heterogeneous integration to combine specialized chiplets optimized for specific tasks. This approach allows for more efficient processing by utilizing the most suitable chiplet for each workload, resulting in improved overall system energy efficiency.Expand Specific Solutions05 AI-driven energy optimization in chiplet systems

Artificial intelligence techniques are employed to dynamically optimize energy consumption in chiplet-based systems. This includes AI-powered workload prediction, intelligent resource allocation, and adaptive power management strategies to maximize energy efficiency based on real-time system demands.Expand Specific Solutions

Key Chiplet Technology Players

The chiplet-based systems market is in a growth phase, driven by increasing demand for energy-efficient computing solutions. Major players like Intel, AMD, and Micron are actively developing and commercializing chiplet technologies, indicating a maturing market. The technology's potential for optimizing energy efficiency metrics has attracted significant investment and research efforts from both established semiconductor companies and emerging startups. While the market size is expanding, it's still evolving as companies work to overcome integration challenges and standardize interconnect technologies. The involvement of research institutions like Zhejiang University and the Institute of Microelectronics of Chinese Academy of Sciences suggests ongoing innovation and potential for further advancements in chiplet-based energy efficiency optimization.

Intel Corp.

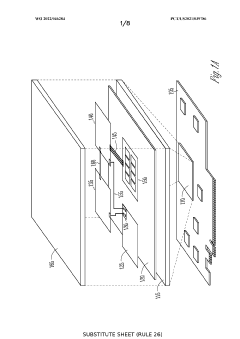

Technical Solution: Intel's chiplet-based approach, exemplified by their Foveros 3D packaging technology, allows for the integration of diverse IP blocks and process nodes on a single package. This modular design enables the combination of high-performance compute tiles with power-efficient I/O and memory tiles. Intel's implementation includes active interposers that facilitate die-to-die connections, reducing power consumption in data movement between chiplets[1]. Their Embedded Multi-die Interconnect Bridge (EMIB) technology further enhances energy efficiency by providing high-bandwidth, short-reach interconnects between chiplets, minimizing signal loss and power consumption[2]. Intel has reported up to 50% power reduction in certain configurations compared to monolithic designs[3].

Strengths: Flexibility in combining different process nodes, reduced time-to-market for new products, and improved yield. Weaknesses: Increased packaging complexity and potential thermal management challenges in 3D stacked configurations.

Advanced Micro Devices, Inc.

Technical Solution: AMD's chiplet strategy, implemented through their Infinity Fabric interconnect, allows for the disaggregation of CPU cores and I/O components. This approach enables AMD to manufacture CPU cores on advanced process nodes for maximum performance and energy efficiency, while producing I/O components on mature nodes for cost-effectiveness. AMD's EPYC server processors, utilizing this chiplet design, have demonstrated up to 40% better energy efficiency compared to competitive monolithic designs[4]. The company's use of through-silicon vias (TSVs) in their 3D V-Cache technology further optimizes energy efficiency by reducing the distance and power required for data transfer between cache and compute cores[5].

Strengths: Scalability of designs, ability to optimize different components independently, and reduced manufacturing costs. Weaknesses: Potential latency issues between chiplets and complexity in managing thermal density.

Innovative Chiplet Interconnect Solutions

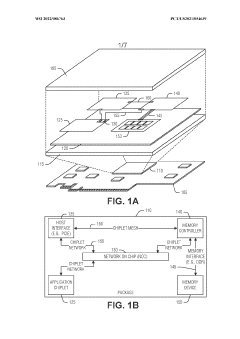

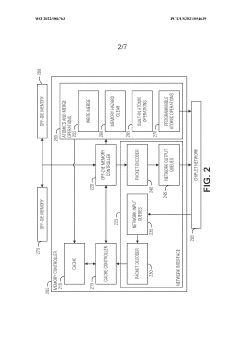

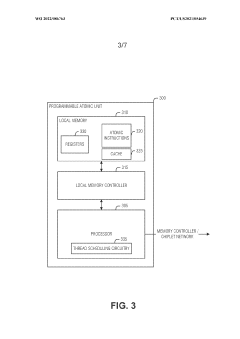

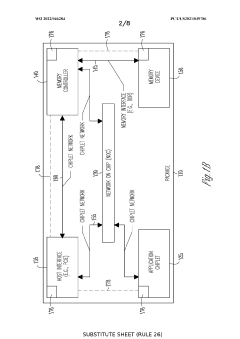

Thread scheduling control and memory splitting in a barrel processor

PatentWO2022086763A1

Innovation

- Implementing a thread scheduling control mechanism that organizes threads into separate groups, each with its own memory device, and alternates between groups for read and write access to reduce memory contention, allowing threads to progress through the pipeline more efficiently and reducing power draw.

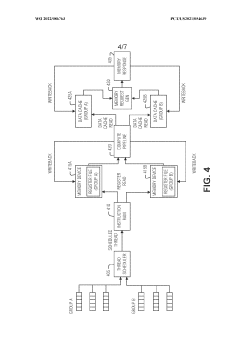

Method for configuring multiple input-output channels

PatentWO2022046284A1

Innovation

- The implementation of a Chiplet Protocol Interface (CPI) network with Advanced Interface Bus (AIB) channels and credit-based flow control, allowing for flexible virtual channel mapping and minimizing latency and energy consumption through packetized protocols and serialization-deserialization (SERDES) hardware, while enabling efficient inter-chiplet communication.

Thermal Management in Chiplet Systems

Thermal management is a critical aspect of chiplet-based systems, directly impacting their energy efficiency and overall performance. As chiplets allow for higher integration density and more complex architectures, managing heat dissipation becomes increasingly challenging. The thermal design of chiplet systems must address several key factors to optimize energy efficiency metrics.

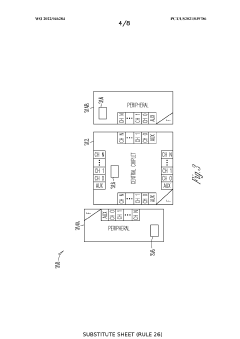

One of the primary considerations in thermal management for chiplet systems is the heterogeneous nature of the components. Different chiplets may have varying thermal characteristics and power densities, requiring a tailored approach to cooling. Advanced thermal interface materials (TIMs) play a crucial role in efficiently transferring heat from the chiplets to the heat spreader or cooling solution. These materials must balance thermal conductivity with mechanical compliance to accommodate the varying heights and surface characteristics of different chiplets.

The integration of chiplets also introduces new thermal challenges related to hotspots and thermal gradients. The compact arrangement of high-performance chiplets can lead to localized areas of intense heat generation. To address this, designers are implementing advanced cooling techniques such as microfluidic cooling channels integrated directly into the interposer or package substrate. These solutions allow for targeted cooling of high-heat areas, maintaining more uniform temperatures across the entire chiplet system.

Another important aspect of thermal management in chiplet systems is the optimization of power distribution. By carefully managing the power delivery to individual chiplets and implementing sophisticated power gating techniques, designers can reduce overall power consumption and, consequently, heat generation. Dynamic thermal management strategies, such as adaptive clock gating and voltage scaling, are being employed to respond to real-time thermal conditions and maintain optimal performance within thermal constraints.

The packaging and system-level design also play a significant role in thermal management. Advanced packaging technologies, such as embedded multi-die interconnect bridge (EMIB) and silicon interposers, not only facilitate high-bandwidth communication between chiplets but also contribute to more efficient heat spreading. At the system level, innovative cooling solutions, including vapor chambers and phase-change materials, are being integrated to enhance heat dissipation from the package to the ambient environment.

As chiplet-based systems continue to evolve, thermal management strategies are becoming more sophisticated and tightly integrated with the overall system design. The use of artificial intelligence and machine learning algorithms for predictive thermal management is an emerging trend, allowing systems to anticipate thermal challenges and proactively adjust performance parameters. This holistic approach to thermal management is essential for maximizing the energy efficiency of chiplet-based systems, enabling higher performance while maintaining reliability and longevity.

One of the primary considerations in thermal management for chiplet systems is the heterogeneous nature of the components. Different chiplets may have varying thermal characteristics and power densities, requiring a tailored approach to cooling. Advanced thermal interface materials (TIMs) play a crucial role in efficiently transferring heat from the chiplets to the heat spreader or cooling solution. These materials must balance thermal conductivity with mechanical compliance to accommodate the varying heights and surface characteristics of different chiplets.

The integration of chiplets also introduces new thermal challenges related to hotspots and thermal gradients. The compact arrangement of high-performance chiplets can lead to localized areas of intense heat generation. To address this, designers are implementing advanced cooling techniques such as microfluidic cooling channels integrated directly into the interposer or package substrate. These solutions allow for targeted cooling of high-heat areas, maintaining more uniform temperatures across the entire chiplet system.

Another important aspect of thermal management in chiplet systems is the optimization of power distribution. By carefully managing the power delivery to individual chiplets and implementing sophisticated power gating techniques, designers can reduce overall power consumption and, consequently, heat generation. Dynamic thermal management strategies, such as adaptive clock gating and voltage scaling, are being employed to respond to real-time thermal conditions and maintain optimal performance within thermal constraints.

The packaging and system-level design also play a significant role in thermal management. Advanced packaging technologies, such as embedded multi-die interconnect bridge (EMIB) and silicon interposers, not only facilitate high-bandwidth communication between chiplets but also contribute to more efficient heat spreading. At the system level, innovative cooling solutions, including vapor chambers and phase-change materials, are being integrated to enhance heat dissipation from the package to the ambient environment.

As chiplet-based systems continue to evolve, thermal management strategies are becoming more sophisticated and tightly integrated with the overall system design. The use of artificial intelligence and machine learning algorithms for predictive thermal management is an emerging trend, allowing systems to anticipate thermal challenges and proactively adjust performance parameters. This holistic approach to thermal management is essential for maximizing the energy efficiency of chiplet-based systems, enabling higher performance while maintaining reliability and longevity.

Chiplet Standardization Efforts

Chiplet standardization efforts have become increasingly crucial in the development of energy-efficient chiplet-based systems. These initiatives aim to establish common interfaces, protocols, and design methodologies that enable seamless integration of chiplets from different manufacturers. The Universal Chiplet Interconnect Express (UCIe) consortium, formed by industry leaders such as Intel, AMD, and TSMC, is at the forefront of these efforts, working to create an open standard for die-to-die interconnects.

The UCIe standard focuses on defining a common physical layer, protocol stack, and software abstraction layer for chiplet-to-chiplet communication. This standardization allows for greater interoperability between chiplets from various vendors, reducing design complexity and time-to-market for chiplet-based systems. By establishing a unified approach to chiplet integration, manufacturers can more easily mix and match components to optimize system performance and energy efficiency.

Another significant standardization effort is the Open Compute Project's (OCP) Chiplet Design Exchange (CDX) initiative. CDX aims to create a standardized format for exchanging chiplet design information, facilitating collaboration between chiplet designers and system integrators. This standardization enables more efficient design processes and promotes the development of energy-optimized chiplet-based systems.

The CHIPS Alliance, an open-source hardware initiative, is also contributing to chiplet standardization efforts. Their work focuses on developing open-source tools and methodologies for chiplet design and integration, which can help reduce the barriers to entry for smaller companies and accelerate innovation in energy-efficient chiplet technologies.

Standardization efforts extend beyond interconnects and design exchanges to include power management protocols. The development of standardized power management interfaces for chiplets allows for more sophisticated power control strategies across heterogeneous components, further enhancing energy efficiency in chiplet-based systems.

As these standardization efforts progress, they are expected to drive down costs, improve compatibility, and accelerate the adoption of chiplet-based architectures. This, in turn, will lead to more energy-efficient computing systems across a wide range of applications, from data centers to edge devices. The collaborative nature of these initiatives ensures that the resulting standards benefit the entire industry, fostering innovation and competition in the development of energy-efficient chiplet solutions.

The UCIe standard focuses on defining a common physical layer, protocol stack, and software abstraction layer for chiplet-to-chiplet communication. This standardization allows for greater interoperability between chiplets from various vendors, reducing design complexity and time-to-market for chiplet-based systems. By establishing a unified approach to chiplet integration, manufacturers can more easily mix and match components to optimize system performance and energy efficiency.

Another significant standardization effort is the Open Compute Project's (OCP) Chiplet Design Exchange (CDX) initiative. CDX aims to create a standardized format for exchanging chiplet design information, facilitating collaboration between chiplet designers and system integrators. This standardization enables more efficient design processes and promotes the development of energy-optimized chiplet-based systems.

The CHIPS Alliance, an open-source hardware initiative, is also contributing to chiplet standardization efforts. Their work focuses on developing open-source tools and methodologies for chiplet design and integration, which can help reduce the barriers to entry for smaller companies and accelerate innovation in energy-efficient chiplet technologies.

Standardization efforts extend beyond interconnects and design exchanges to include power management protocols. The development of standardized power management interfaces for chiplets allows for more sophisticated power control strategies across heterogeneous components, further enhancing energy efficiency in chiplet-based systems.

As these standardization efforts progress, they are expected to drive down costs, improve compatibility, and accelerate the adoption of chiplet-based architectures. This, in turn, will lead to more energy-efficient computing systems across a wide range of applications, from data centers to edge devices. The collaborative nature of these initiatives ensures that the resulting standards benefit the entire industry, fostering innovation and competition in the development of energy-efficient chiplet solutions.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!