How to Implement Chiplet Designs for Next-Gen Robotics?

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Design Evolution and Robotics Goals

Chiplet design has emerged as a revolutionary approach in the semiconductor industry, offering a pathway to overcome the limitations of traditional monolithic chip designs. This evolution in chip architecture has significant implications for the field of robotics, where computational power, energy efficiency, and miniaturization are critical factors. The journey of chiplet design began as a response to the slowing of Moore's Law, which had long been the driving force behind semiconductor advancements.

In the context of robotics, the goals of implementing chiplet designs are multifaceted. Primarily, there is a pressing need for increased processing power to handle complex algorithms for artificial intelligence, machine learning, and real-time decision-making in robotic systems. Chiplets offer the potential to integrate specialized processing units, such as neural processing units (NPUs) and vision processing units (VPUs), alongside general-purpose processors, creating a more versatile and powerful computing platform for robots.

Another crucial objective is to enhance energy efficiency. Robots, especially those designed for mobile or autonomous operations, require optimized power consumption to extend battery life and operational duration. Chiplet designs allow for more granular power management, with the ability to activate or deactivate specific components as needed, potentially leading to significant energy savings.

Miniaturization is a third key goal in robotics, particularly for applications in medical, exploration, and consumer robotics. Chiplets enable the creation of more compact and densely packed computing systems, which is essential for reducing the overall size and weight of robotic platforms without compromising on performance.

The evolution of chiplet design in robotics is closely tied to advancements in packaging technologies, such as 2.5D and 3D integration. These technologies allow for the vertical stacking of chiplets, further reducing the footprint of the computing system. Additionally, the development of high-bandwidth interconnects between chiplets has been crucial in ensuring that the performance benefits of this modular approach are fully realized.

As the field progresses, there is a growing focus on standardization and interoperability of chiplets from different manufacturers. This trend aims to create a more flexible and cost-effective ecosystem for robotic system designers, allowing them to mix and match chiplets to create customized solutions for specific robotic applications. The ultimate goal is to establish a "Lego-like" approach to chip design, where robotics engineers can easily assemble the optimal computing solution for their needs.

In the context of robotics, the goals of implementing chiplet designs are multifaceted. Primarily, there is a pressing need for increased processing power to handle complex algorithms for artificial intelligence, machine learning, and real-time decision-making in robotic systems. Chiplets offer the potential to integrate specialized processing units, such as neural processing units (NPUs) and vision processing units (VPUs), alongside general-purpose processors, creating a more versatile and powerful computing platform for robots.

Another crucial objective is to enhance energy efficiency. Robots, especially those designed for mobile or autonomous operations, require optimized power consumption to extend battery life and operational duration. Chiplet designs allow for more granular power management, with the ability to activate or deactivate specific components as needed, potentially leading to significant energy savings.

Miniaturization is a third key goal in robotics, particularly for applications in medical, exploration, and consumer robotics. Chiplets enable the creation of more compact and densely packed computing systems, which is essential for reducing the overall size and weight of robotic platforms without compromising on performance.

The evolution of chiplet design in robotics is closely tied to advancements in packaging technologies, such as 2.5D and 3D integration. These technologies allow for the vertical stacking of chiplets, further reducing the footprint of the computing system. Additionally, the development of high-bandwidth interconnects between chiplets has been crucial in ensuring that the performance benefits of this modular approach are fully realized.

As the field progresses, there is a growing focus on standardization and interoperability of chiplets from different manufacturers. This trend aims to create a more flexible and cost-effective ecosystem for robotic system designers, allowing them to mix and match chiplets to create customized solutions for specific robotic applications. The ultimate goal is to establish a "Lego-like" approach to chip design, where robotics engineers can easily assemble the optimal computing solution for their needs.

Robotics Market Demand for Chiplet Solutions

The robotics market is experiencing a significant surge in demand for chiplet solutions, driven by the increasing complexity and performance requirements of next-generation robotic systems. As robots become more sophisticated and autonomous, they require advanced computing capabilities to process vast amounts of data in real-time, make complex decisions, and perform intricate tasks. This has created a pressing need for more powerful, efficient, and flexible semiconductor solutions.

Chiplet designs offer a promising approach to address these challenges by enabling modular and scalable architectures. The robotics industry is particularly interested in chiplets due to their ability to integrate diverse functionalities, such as high-performance computing, artificial intelligence accelerators, and sensor processing units, into a single package. This integration is crucial for robots that need to perform multiple tasks simultaneously, such as perception, navigation, and manipulation.

The market demand for chiplet solutions in robotics is further fueled by the need for energy efficiency. As many robotic applications require operation on battery power or in energy-constrained environments, the ability of chiplets to optimize power consumption while maintaining high performance is highly valued. This is especially relevant for mobile robots, drones, and wearable robotic devices.

Another key driver of demand is the flexibility offered by chiplet designs. Robotics companies are seeking customizable solutions that can be tailored to specific application requirements without the need for full custom chip development. Chiplets allow for mix-and-match capabilities, enabling robotics manufacturers to create specialized systems by combining different functional blocks.

The industrial robotics sector, in particular, is showing strong interest in chiplet solutions. As factories move towards Industry 4.0 and smart manufacturing, there is a growing need for robots with advanced sensing, communication, and processing capabilities. Chiplets can provide the necessary computational power for complex tasks such as real-time quality control, predictive maintenance, and collaborative operations with human workers.

In the consumer robotics market, demand for chiplet solutions is being driven by the push for more advanced home automation and personal assistant robots. These applications require sophisticated natural language processing, computer vision, and decision-making capabilities, which can be efficiently implemented using chiplet-based designs.

The healthcare robotics segment is another area where chiplet demand is on the rise. Surgical robots, rehabilitation devices, and diagnostic systems all require high-performance, low-latency computing solutions that can be achieved through chiplet architectures. The ability to integrate specialized accelerators for medical imaging and data analysis is particularly valuable in this field.

As the robotics market continues to expand and diversify, the demand for chiplet solutions is expected to grow significantly. Industry analysts project that the market for specialized chiplets in robotics applications will experience double-digit growth rates over the next five years, outpacing the overall semiconductor market growth.

Chiplet designs offer a promising approach to address these challenges by enabling modular and scalable architectures. The robotics industry is particularly interested in chiplets due to their ability to integrate diverse functionalities, such as high-performance computing, artificial intelligence accelerators, and sensor processing units, into a single package. This integration is crucial for robots that need to perform multiple tasks simultaneously, such as perception, navigation, and manipulation.

The market demand for chiplet solutions in robotics is further fueled by the need for energy efficiency. As many robotic applications require operation on battery power or in energy-constrained environments, the ability of chiplets to optimize power consumption while maintaining high performance is highly valued. This is especially relevant for mobile robots, drones, and wearable robotic devices.

Another key driver of demand is the flexibility offered by chiplet designs. Robotics companies are seeking customizable solutions that can be tailored to specific application requirements without the need for full custom chip development. Chiplets allow for mix-and-match capabilities, enabling robotics manufacturers to create specialized systems by combining different functional blocks.

The industrial robotics sector, in particular, is showing strong interest in chiplet solutions. As factories move towards Industry 4.0 and smart manufacturing, there is a growing need for robots with advanced sensing, communication, and processing capabilities. Chiplets can provide the necessary computational power for complex tasks such as real-time quality control, predictive maintenance, and collaborative operations with human workers.

In the consumer robotics market, demand for chiplet solutions is being driven by the push for more advanced home automation and personal assistant robots. These applications require sophisticated natural language processing, computer vision, and decision-making capabilities, which can be efficiently implemented using chiplet-based designs.

The healthcare robotics segment is another area where chiplet demand is on the rise. Surgical robots, rehabilitation devices, and diagnostic systems all require high-performance, low-latency computing solutions that can be achieved through chiplet architectures. The ability to integrate specialized accelerators for medical imaging and data analysis is particularly valuable in this field.

As the robotics market continues to expand and diversify, the demand for chiplet solutions is expected to grow significantly. Industry analysts project that the market for specialized chiplets in robotics applications will experience double-digit growth rates over the next five years, outpacing the overall semiconductor market growth.

Chiplet Technology Challenges in Robotics

The implementation of chiplet designs in next-generation robotics faces several significant challenges. One of the primary obstacles is the integration of heterogeneous components within a single package. Robotics systems often require a diverse array of functionalities, including sensors, processors, and actuators, each with unique performance requirements. Ensuring seamless communication and coordination between these disparate elements while maintaining optimal performance is a complex task.

Thermal management presents another critical challenge in chiplet-based robotics designs. As robotic systems become more compact and powerful, heat dissipation becomes increasingly problematic. The close proximity of multiple chiplets within a single package can lead to thermal hotspots, potentially compromising system reliability and performance. Developing effective cooling solutions that can address these thermal issues without significantly increasing the overall size or weight of the robotic system is crucial.

Power efficiency is a paramount concern in robotics, particularly for mobile and autonomous systems. Chiplet designs must balance the need for high performance with stringent power constraints. Optimizing power distribution and management across multiple chiplets, each with potentially different voltage and current requirements, adds another layer of complexity to the design process.

Interconnect technology poses a significant hurdle in chiplet implementation for robotics. High-bandwidth, low-latency communication between chiplets is essential for real-time processing and decision-making in robotic systems. Developing advanced interconnect solutions that can support the data transfer rates required for complex robotic operations while minimizing signal degradation and power consumption is a key challenge.

Standardization and interoperability present ongoing challenges in the chiplet ecosystem. The lack of universal standards for chiplet interfaces and protocols can hinder the development of modular, scalable robotic systems. Establishing industry-wide standards that allow for seamless integration of chiplets from different manufacturers would greatly facilitate the adoption of chiplet technology in robotics.

Manufacturing and testing complexities also pose significant challenges. The assembly of multiple chiplets into a single package requires precise manufacturing processes and advanced packaging technologies. Ensuring the reliability and yield of these complex assemblies, particularly in the harsh environments often encountered by robotic systems, is a major concern. Additionally, developing effective testing methodologies for chiplet-based designs, both at the individual chiplet level and for the integrated system, is crucial for quality assurance and performance optimization.

Thermal management presents another critical challenge in chiplet-based robotics designs. As robotic systems become more compact and powerful, heat dissipation becomes increasingly problematic. The close proximity of multiple chiplets within a single package can lead to thermal hotspots, potentially compromising system reliability and performance. Developing effective cooling solutions that can address these thermal issues without significantly increasing the overall size or weight of the robotic system is crucial.

Power efficiency is a paramount concern in robotics, particularly for mobile and autonomous systems. Chiplet designs must balance the need for high performance with stringent power constraints. Optimizing power distribution and management across multiple chiplets, each with potentially different voltage and current requirements, adds another layer of complexity to the design process.

Interconnect technology poses a significant hurdle in chiplet implementation for robotics. High-bandwidth, low-latency communication between chiplets is essential for real-time processing and decision-making in robotic systems. Developing advanced interconnect solutions that can support the data transfer rates required for complex robotic operations while minimizing signal degradation and power consumption is a key challenge.

Standardization and interoperability present ongoing challenges in the chiplet ecosystem. The lack of universal standards for chiplet interfaces and protocols can hinder the development of modular, scalable robotic systems. Establishing industry-wide standards that allow for seamless integration of chiplets from different manufacturers would greatly facilitate the adoption of chiplet technology in robotics.

Manufacturing and testing complexities also pose significant challenges. The assembly of multiple chiplets into a single package requires precise manufacturing processes and advanced packaging technologies. Ensuring the reliability and yield of these complex assemblies, particularly in the harsh environments often encountered by robotic systems, is a major concern. Additionally, developing effective testing methodologies for chiplet-based designs, both at the individual chiplet level and for the integrated system, is crucial for quality assurance and performance optimization.

Current Chiplet Implementation Strategies

01 Interconnect architectures for chiplets

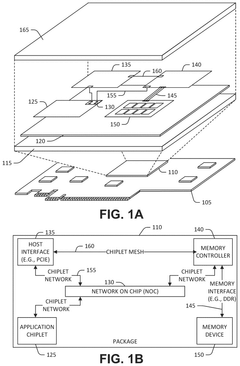

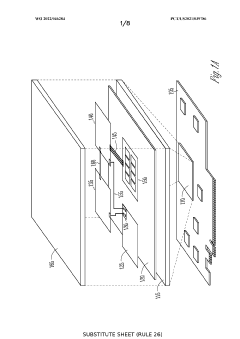

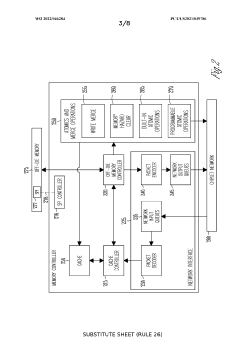

Advanced interconnect architectures are crucial for chiplet designs, enabling high-speed communication between different chiplets. These architectures may include through-silicon vias (TSVs), interposers, and advanced packaging technologies to facilitate efficient data transfer and integration of multiple chiplets into a single system.- Chiplet interconnection and packaging: Chiplet designs focus on innovative interconnection and packaging technologies to integrate multiple smaller chips (chiplets) into a single package. This approach allows for improved performance, power efficiency, and scalability compared to traditional monolithic chip designs. Advanced packaging techniques such as 2.5D and 3D integration are used to connect chiplets, enabling high-bandwidth and low-latency communication between different functional blocks.

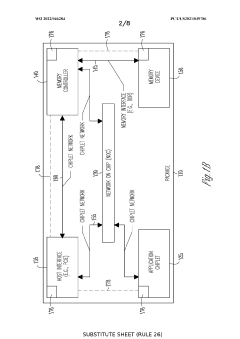

- Chiplet-based system-on-chip (SoC) architectures: Chiplet-based SoC architectures leverage modular design principles to create flexible and customizable chip solutions. By combining different chiplets, each specialized for specific functions (e.g., CPU, GPU, memory, I/O), designers can create tailored SoCs for various applications. This approach allows for faster time-to-market, reduced development costs, and improved yield compared to monolithic designs.

- Chiplet power management and thermal optimization: Efficient power management and thermal optimization are crucial aspects of chiplet designs. Techniques such as dynamic voltage and frequency scaling, power gating, and intelligent thermal management are employed to optimize power consumption and heat dissipation across multiple chiplets. These strategies ensure optimal performance while maintaining thermal stability within the package.

- Chiplet design for artificial intelligence and machine learning: Chiplet designs are increasingly utilized in AI and ML applications, offering scalable and efficient solutions for complex computational tasks. By combining specialized chiplets for neural network processing, memory, and data movement, these designs can deliver high performance and energy efficiency for AI workloads. This approach allows for flexible scaling of AI capabilities across different product lines and application domains.

- Chiplet testing and yield improvement: Effective testing and yield improvement strategies are essential for chiplet-based designs. Advanced testing methodologies, including pre-bond and post-bond testing, are developed to ensure the functionality and performance of individual chiplets and the integrated package. Redundancy and repair techniques are also implemented to improve overall yield and reliability of chiplet-based products.

02 Power management in chiplet designs

Effective power management strategies are essential for chiplet-based systems to optimize performance and energy efficiency. This includes techniques for dynamic voltage and frequency scaling, power gating, and thermal management across multiple chiplets to ensure optimal operation and longevity of the integrated system.Expand Specific Solutions03 Chiplet integration and packaging technologies

Advanced packaging technologies play a critical role in chiplet integration, allowing for the combination of heterogeneous chiplets into a single package. This includes 2.5D and 3D packaging techniques, as well as novel bonding and stacking methods to achieve high-density integration and improved system performance.Expand Specific Solutions04 Chiplet-based memory systems

Memory chiplets are a key component in modular chip designs, allowing for flexible and scalable memory configurations. This includes high-bandwidth memory (HBM) chiplets, cache coherency protocols for multi-chiplet systems, and innovative memory architectures optimized for specific application domains.Expand Specific Solutions05 Design and verification methodologies for chiplet-based systems

Specialized design and verification methodologies are required for chiplet-based systems to ensure compatibility, performance, and reliability. This includes tools and techniques for system-level simulation, interface standardization, and design-for-test strategies tailored to multi-chiplet architectures.Expand Specific Solutions

Key Players in Chiplet and Robotics Industries

The implementation of chiplet designs for next-generation robotics is in an early development stage, with a rapidly growing market driven by the demand for more powerful and efficient computing in robotics. The technology is still maturing, with varying levels of adoption across companies. Key players like AMD and Micron Technology are at the forefront, leveraging their expertise in semiconductor design and manufacturing. Universities such as Xidian University and Harbin Institute of Technology are contributing to research and development. Emerging companies like Xiamen Runchip and Hygon Information Technology are also entering the field, focusing on specialized chiplet solutions for robotics applications. The competitive landscape is dynamic, with both established semiconductor giants and innovative startups vying for market share in this promising sector.

Micron Technology, Inc.

Technical Solution: Micron's approach to chiplet designs for next-gen robotics focuses on memory-centric architectures. They are developing high-bandwidth, low-latency memory solutions that can be integrated as separate chiplets within a multi-chip module. Micron's HBM3 technology, with bandwidth up to 900 GB/s, is being tailored for robotic applications requiring real-time processing of large datasets[4]. The company is also working on 3D-stacked memory chiplets that can be directly integrated with processing elements, reducing data movement and improving energy efficiency. Micron's advanced packaging technologies, such as silicon interposers and through-silicon vias (TSVs), enable tight integration of memory chiplets with other components[5]. Additionally, they are exploring the use of compute-in-memory (CIM) architectures within their chiplets to perform certain AI operations directly in the memory subsystem, further enhancing performance for robotic applications[6].

Strengths: High memory bandwidth, reduced data movement, and potential for in-memory computing. Weaknesses: Complexity in thermal management and potential cost increases due to advanced packaging technologies.

Advanced Micro Devices, Inc.

Technical Solution: AMD has been at the forefront of chiplet design implementation for next-gen robotics. Their approach involves using multiple smaller dies (chiplets) interconnected on a single package, allowing for more efficient manufacturing and better yield. For robotics applications, AMD's chiplet design incorporates high-performance CPU cores, GPU units, and specialized AI accelerators. The company utilizes its Infinity Fabric interconnect technology to ensure high-bandwidth, low-latency communication between chiplets[1]. AMD's 3D V-Cache technology, which stacks additional cache memory directly on top of the compute dies, significantly enhances performance for data-intensive robotic applications[2]. The company is also exploring the integration of HBM (High Bandwidth Memory) directly into the chiplet package to further boost memory bandwidth for complex robotic tasks[3].

Strengths: Scalability, improved yield, and ability to mix-and-match different process nodes. Weaknesses: Potential for increased latency between chiplets and higher power consumption due to inter-chiplet communication.

Innovative Chiplet Architectures for Robotics

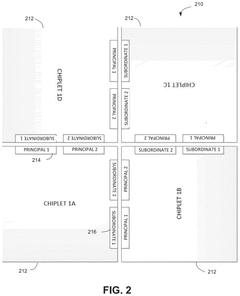

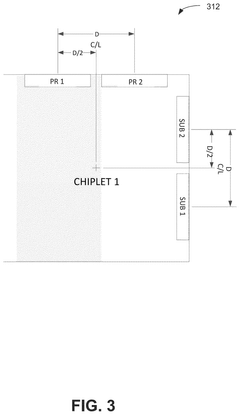

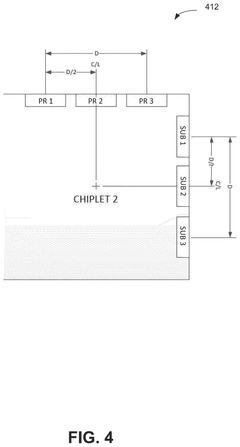

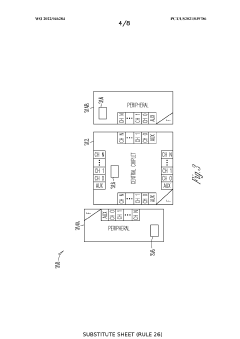

Edge interface placements to enable chiplet rotation into multi-chiplet cluster

PatentPendingUS20240332257A1

Innovation

- The implementation of a chiplet architecture that uses a network-on-chip (NOC) with a chiplet protocol interface (CPI) to facilitate high-speed, flexible inter-chiplet communication, combined with a tightly packed matrix arrangement of chiplets and I/O micro-bumps for close-coupled interconnects, allowing for proper alignment and minimal footprint.

Method for configuring multiple input-output channels

PatentWO2022046284A1

Innovation

- The implementation of a Chiplet Protocol Interface (CPI) network with Advanced Interface Bus (AIB) channels and credit-based flow control, allowing for flexible virtual channel mapping and minimizing latency and energy consumption through packetized protocols and serialization-deserialization (SERDES) hardware, while enabling efficient inter-chiplet communication.

Thermal Management in Robotics Chiplets

Thermal management is a critical aspect of chiplet designs for next-generation robotics. As robotics systems become more complex and powerful, the heat generated by their components increases significantly. Effective thermal management is essential to maintain optimal performance, reliability, and longevity of robotic systems.

In chiplet-based designs for robotics, multiple smaller chips are integrated onto a single package, offering improved performance and flexibility. However, this approach also presents unique thermal challenges. The close proximity of multiple chiplets can lead to localized hot spots and thermal coupling between components, potentially causing performance degradation or even system failure if not properly addressed.

To tackle these challenges, several thermal management strategies are being employed in robotics chiplets. One approach is the use of advanced packaging technologies, such as 2.5D and 3D integration, which allow for better heat dissipation through improved thermal interfaces and shorter interconnects. These packaging techniques can incorporate thermal vias, heat spreaders, and even liquid cooling channels to efficiently remove heat from the chiplets.

Another key strategy is the implementation of dynamic thermal management techniques. These involve real-time monitoring of temperature across the chiplet package and adjusting performance parameters to maintain optimal thermal conditions. Advanced algorithms can predict thermal behavior and proactively manage power distribution among chiplets to prevent overheating.

Material innovations also play a crucial role in thermal management for robotics chiplets. High thermal conductivity materials, such as diamond-based composites or graphene, are being explored for use in heat spreaders and thermal interface materials. These advanced materials can significantly improve heat dissipation from the chiplets to the package and ultimately to the external environment.

Furthermore, the design of the chiplet package itself is evolving to address thermal concerns. Techniques such as through-silicon vias (TSVs) and microbumps are being optimized not only for electrical connectivity but also for their thermal properties. This allows for more efficient heat transfer from the chiplets to the package substrate and external cooling solutions.

As robotics applications continue to demand higher performance and greater miniaturization, innovative cooling solutions are being developed. These include micro-fluidic cooling systems integrated directly into the chiplet package, as well as phase-change materials that can absorb large amounts of heat during peak operation periods.

In chiplet-based designs for robotics, multiple smaller chips are integrated onto a single package, offering improved performance and flexibility. However, this approach also presents unique thermal challenges. The close proximity of multiple chiplets can lead to localized hot spots and thermal coupling between components, potentially causing performance degradation or even system failure if not properly addressed.

To tackle these challenges, several thermal management strategies are being employed in robotics chiplets. One approach is the use of advanced packaging technologies, such as 2.5D and 3D integration, which allow for better heat dissipation through improved thermal interfaces and shorter interconnects. These packaging techniques can incorporate thermal vias, heat spreaders, and even liquid cooling channels to efficiently remove heat from the chiplets.

Another key strategy is the implementation of dynamic thermal management techniques. These involve real-time monitoring of temperature across the chiplet package and adjusting performance parameters to maintain optimal thermal conditions. Advanced algorithms can predict thermal behavior and proactively manage power distribution among chiplets to prevent overheating.

Material innovations also play a crucial role in thermal management for robotics chiplets. High thermal conductivity materials, such as diamond-based composites or graphene, are being explored for use in heat spreaders and thermal interface materials. These advanced materials can significantly improve heat dissipation from the chiplets to the package and ultimately to the external environment.

Furthermore, the design of the chiplet package itself is evolving to address thermal concerns. Techniques such as through-silicon vias (TSVs) and microbumps are being optimized not only for electrical connectivity but also for their thermal properties. This allows for more efficient heat transfer from the chiplets to the package substrate and external cooling solutions.

As robotics applications continue to demand higher performance and greater miniaturization, innovative cooling solutions are being developed. These include micro-fluidic cooling systems integrated directly into the chiplet package, as well as phase-change materials that can absorb large amounts of heat during peak operation periods.

Standardization Efforts for Chiplet Interfaces

The standardization of chiplet interfaces is a critical aspect in the implementation of chiplet designs for next-generation robotics. As the industry moves towards more modular and flexible chip designs, the need for standardized interfaces becomes increasingly important to ensure interoperability and scalability.

Several industry consortia and organizations are actively working on developing and promoting standards for chiplet interfaces. The Universal Chiplet Interconnect Express (UCIe) consortium, formed by major players like Intel, AMD, Arm, and TSMC, is leading the charge in creating a universal interconnect standard for chiplets. UCIe aims to establish a common physical layer, protocol stack, and software model to enable seamless integration of chiplets from different vendors.

Another significant effort is the Open Compute Project's Open Domain-Specific Architecture (ODSA) subproject, which focuses on creating open standards for chiplet-based systems. The ODSA has proposed several interface standards, including the Bunch of Wires (BoW) interface and the Advanced Interface Bus (AIB), which are designed to facilitate high-speed, low-power communication between chiplets.

The JEDEC Solid State Technology Association is also contributing to chiplet standardization efforts through its development of the High Bandwidth Memory (HBM) standard. HBM is particularly relevant for robotics applications that require high-performance memory solutions integrated with processing elements.

In the realm of packaging technologies, the Heterogeneous Integration Roadmap (HIR), sponsored by IEEE, SEMI, and other organizations, is working to define standards and guidelines for advanced packaging solutions that enable chiplet integration. This includes standards for 2.5D and 3D integration technologies, which are crucial for implementing complex chiplet-based designs in robotics systems.

The adoption of these standards is expected to accelerate the development and deployment of chiplet-based designs in next-generation robotics. Standardized interfaces will allow robotics manufacturers to mix and match chiplets from different suppliers, potentially reducing costs and time-to-market while increasing design flexibility and performance optimization.

However, challenges remain in achieving widespread adoption of these standards. Competing interests among industry players, the need for backward compatibility, and the rapid pace of technological advancement all contribute to the complexity of standardization efforts. As the robotics industry continues to evolve, it will be crucial for stakeholders to collaborate and align their efforts to ensure that chiplet interface standards meet the specific requirements of next-generation robotic systems.

Several industry consortia and organizations are actively working on developing and promoting standards for chiplet interfaces. The Universal Chiplet Interconnect Express (UCIe) consortium, formed by major players like Intel, AMD, Arm, and TSMC, is leading the charge in creating a universal interconnect standard for chiplets. UCIe aims to establish a common physical layer, protocol stack, and software model to enable seamless integration of chiplets from different vendors.

Another significant effort is the Open Compute Project's Open Domain-Specific Architecture (ODSA) subproject, which focuses on creating open standards for chiplet-based systems. The ODSA has proposed several interface standards, including the Bunch of Wires (BoW) interface and the Advanced Interface Bus (AIB), which are designed to facilitate high-speed, low-power communication between chiplets.

The JEDEC Solid State Technology Association is also contributing to chiplet standardization efforts through its development of the High Bandwidth Memory (HBM) standard. HBM is particularly relevant for robotics applications that require high-performance memory solutions integrated with processing elements.

In the realm of packaging technologies, the Heterogeneous Integration Roadmap (HIR), sponsored by IEEE, SEMI, and other organizations, is working to define standards and guidelines for advanced packaging solutions that enable chiplet integration. This includes standards for 2.5D and 3D integration technologies, which are crucial for implementing complex chiplet-based designs in robotics systems.

The adoption of these standards is expected to accelerate the development and deployment of chiplet-based designs in next-generation robotics. Standardized interfaces will allow robotics manufacturers to mix and match chiplets from different suppliers, potentially reducing costs and time-to-market while increasing design flexibility and performance optimization.

However, challenges remain in achieving widespread adoption of these standards. Competing interests among industry players, the need for backward compatibility, and the rapid pace of technological advancement all contribute to the complexity of standardization efforts. As the robotics industry continues to evolve, it will be crucial for stakeholders to collaborate and align their efforts to ensure that chiplet interface standards meet the specific requirements of next-generation robotic systems.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!