Chiplet Technologies in Energy Optimization Platforms

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Tech Evolution

Chiplet technology has undergone significant evolution since its inception, marking a paradigm shift in semiconductor design and manufacturing. The journey began in the early 2010s when the concept of disaggregating large monolithic chips into smaller, more manageable pieces gained traction. This approach was driven by the need to overcome the limitations of traditional chip scaling and improve yield rates in advanced process nodes.

The initial phase of chiplet development focused on addressing interconnect challenges. Companies like AMD pioneered the use of interposer technology to connect multiple chiplets, as seen in their Fiji GPU and later in their Zen-based processors. This marked the beginning of heterogeneous integration, allowing different components to be manufactured using optimal process nodes and then combined on a single package.

As the technology matured, the industry saw a shift towards more advanced packaging techniques. Intel introduced its Embedded Multi-die Interconnect Bridge (EMIB) in 2017, offering a cost-effective alternative to silicon interposers for high-bandwidth connections between chiplets. This was followed by their Foveros technology in 2018, which enabled 3D stacking of chiplets, further increasing integration density and performance.

The evolution of chiplet technology also saw advancements in standardization efforts. The Open Compute Project's Universal Chiplet Interconnect Express (UCIe) specification, released in 2022, aimed to create a common interface for chiplets from different vendors. This move towards standardization has been crucial in fostering a more open and collaborative ecosystem for chiplet design and manufacturing.

In the context of energy optimization platforms, chiplet technology has played a pivotal role. The ability to mix and match chiplets with different power characteristics has allowed for more granular control over system-wide power consumption. This has been particularly beneficial in data center applications, where energy efficiency is paramount.

Recent developments have focused on enhancing the energy efficiency of chiplet-to-chiplet communications. Advanced packaging technologies like TSMC's InFO (Integrated Fan-Out) and CoWoS (Chip on Wafer on Substrate) have enabled shorter interconnects, reducing power consumption in data transfers between chiplets. Additionally, the integration of chiplets with different functionalities, such as high-performance compute dies alongside specialized AI accelerators, has allowed for more efficient workload distribution and power management.

Looking forward, the evolution of chiplet technology in energy optimization platforms is likely to continue along several trajectories. These include the development of even more advanced packaging techniques, further improvements in chiplet-to-chiplet communication efficiency, and the integration of novel materials and devices to enhance overall system energy performance.

The initial phase of chiplet development focused on addressing interconnect challenges. Companies like AMD pioneered the use of interposer technology to connect multiple chiplets, as seen in their Fiji GPU and later in their Zen-based processors. This marked the beginning of heterogeneous integration, allowing different components to be manufactured using optimal process nodes and then combined on a single package.

As the technology matured, the industry saw a shift towards more advanced packaging techniques. Intel introduced its Embedded Multi-die Interconnect Bridge (EMIB) in 2017, offering a cost-effective alternative to silicon interposers for high-bandwidth connections between chiplets. This was followed by their Foveros technology in 2018, which enabled 3D stacking of chiplets, further increasing integration density and performance.

The evolution of chiplet technology also saw advancements in standardization efforts. The Open Compute Project's Universal Chiplet Interconnect Express (UCIe) specification, released in 2022, aimed to create a common interface for chiplets from different vendors. This move towards standardization has been crucial in fostering a more open and collaborative ecosystem for chiplet design and manufacturing.

In the context of energy optimization platforms, chiplet technology has played a pivotal role. The ability to mix and match chiplets with different power characteristics has allowed for more granular control over system-wide power consumption. This has been particularly beneficial in data center applications, where energy efficiency is paramount.

Recent developments have focused on enhancing the energy efficiency of chiplet-to-chiplet communications. Advanced packaging technologies like TSMC's InFO (Integrated Fan-Out) and CoWoS (Chip on Wafer on Substrate) have enabled shorter interconnects, reducing power consumption in data transfers between chiplets. Additionally, the integration of chiplets with different functionalities, such as high-performance compute dies alongside specialized AI accelerators, has allowed for more efficient workload distribution and power management.

Looking forward, the evolution of chiplet technology in energy optimization platforms is likely to continue along several trajectories. These include the development of even more advanced packaging techniques, further improvements in chiplet-to-chiplet communication efficiency, and the integration of novel materials and devices to enhance overall system energy performance.

Energy Optimization Demand

The demand for energy optimization in modern computing systems has become increasingly critical as the complexity and scale of these systems continue to grow. This demand is driven by several factors, including the need to reduce operational costs, minimize environmental impact, and improve overall system performance. In the context of chiplet technologies, energy optimization takes on a new dimension, as it involves not only the efficiency of individual components but also the interconnections between them.

One of the primary drivers for energy optimization in chiplet-based platforms is the exponential growth in data center power consumption. As cloud computing and big data applications proliferate, the energy requirements of data centers have skyrocketed, leading to significant environmental and economic concerns. This has prompted a push for more energy-efficient computing solutions, with chiplet technologies emerging as a promising approach to address these challenges.

The adoption of chiplet technologies in energy optimization platforms is also fueled by the increasing demand for high-performance computing in edge devices and IoT applications. These scenarios often involve power-constrained environments where energy efficiency is paramount. Chiplet-based designs offer the potential to deliver high performance while maintaining low power consumption, making them ideal for such applications.

Furthermore, the automotive and industrial sectors are showing growing interest in chiplet technologies for energy optimization. As vehicles become more electrified and autonomous, and as industrial processes become more automated, there is a pressing need for computing solutions that can deliver high performance within strict power budgets. Chiplet-based platforms offer the flexibility and efficiency required to meet these demanding requirements.

The demand for energy optimization in chiplet technologies is also driven by the limitations of traditional monolithic chip designs. As semiconductor manufacturing processes approach their physical limits, it becomes increasingly challenging to improve energy efficiency through traditional scaling methods. Chiplet technologies provide a new avenue for optimization by allowing the integration of heterogeneous components, each manufactured using the most appropriate process technology for its function.

Additionally, the rise of artificial intelligence and machine learning workloads has created a surge in demand for specialized, energy-efficient computing architectures. Chiplet technologies enable the creation of custom-designed solutions that can efficiently handle these computationally intensive tasks while minimizing energy consumption. This is particularly important in scenarios such as edge AI, where power constraints are often a limiting factor.

In conclusion, the demand for energy optimization in chiplet-based platforms is driven by a convergence of technological, economic, and environmental factors. As the computing industry continues to evolve, the need for more efficient, flexible, and scalable solutions will only intensify, positioning chiplet technologies as a key enabler in the quest for energy-optimized computing systems.

One of the primary drivers for energy optimization in chiplet-based platforms is the exponential growth in data center power consumption. As cloud computing and big data applications proliferate, the energy requirements of data centers have skyrocketed, leading to significant environmental and economic concerns. This has prompted a push for more energy-efficient computing solutions, with chiplet technologies emerging as a promising approach to address these challenges.

The adoption of chiplet technologies in energy optimization platforms is also fueled by the increasing demand for high-performance computing in edge devices and IoT applications. These scenarios often involve power-constrained environments where energy efficiency is paramount. Chiplet-based designs offer the potential to deliver high performance while maintaining low power consumption, making them ideal for such applications.

Furthermore, the automotive and industrial sectors are showing growing interest in chiplet technologies for energy optimization. As vehicles become more electrified and autonomous, and as industrial processes become more automated, there is a pressing need for computing solutions that can deliver high performance within strict power budgets. Chiplet-based platforms offer the flexibility and efficiency required to meet these demanding requirements.

The demand for energy optimization in chiplet technologies is also driven by the limitations of traditional monolithic chip designs. As semiconductor manufacturing processes approach their physical limits, it becomes increasingly challenging to improve energy efficiency through traditional scaling methods. Chiplet technologies provide a new avenue for optimization by allowing the integration of heterogeneous components, each manufactured using the most appropriate process technology for its function.

Additionally, the rise of artificial intelligence and machine learning workloads has created a surge in demand for specialized, energy-efficient computing architectures. Chiplet technologies enable the creation of custom-designed solutions that can efficiently handle these computationally intensive tasks while minimizing energy consumption. This is particularly important in scenarios such as edge AI, where power constraints are often a limiting factor.

In conclusion, the demand for energy optimization in chiplet-based platforms is driven by a convergence of technological, economic, and environmental factors. As the computing industry continues to evolve, the need for more efficient, flexible, and scalable solutions will only intensify, positioning chiplet technologies as a key enabler in the quest for energy-optimized computing systems.

Chiplet Challenges

The adoption of chiplet technologies in energy optimization platforms presents several significant challenges that need to be addressed for successful implementation. One of the primary obstacles is the complexity of integrating multiple chiplets into a single package. This integration process requires advanced packaging technologies and precise interconnect solutions to ensure seamless communication between different chiplets.

Thermal management poses another critical challenge in chiplet-based designs for energy optimization platforms. As multiple chiplets are packed closely together, heat dissipation becomes a major concern. Efficient cooling solutions and thermal design considerations are essential to maintain optimal performance and prevent thermal-induced failures.

Power distribution and management across multiple chiplets present unique challenges in energy optimization platforms. Ensuring uniform power delivery to each chiplet and managing power consumption across the entire system requires sophisticated power management techniques and advanced power delivery networks.

The design and verification of chiplet-based systems introduce additional complexities. Ensuring compatibility and interoperability between chiplets from different vendors or with varying process nodes can be challenging. Comprehensive testing and validation procedures are necessary to guarantee system-wide functionality and reliability.

Manufacturing and yield issues also pose challenges in chiplet technologies. The production of high-quality chiplets and their subsequent integration into a single package require advanced manufacturing processes and stringent quality control measures. Yield management becomes crucial to ensure cost-effectiveness in chiplet-based designs.

Standardization and ecosystem development remain ongoing challenges in the chiplet industry. The lack of widely adopted standards for chiplet interfaces and protocols can hinder interoperability and limit the potential for mix-and-match chiplet designs. Establishing industry-wide standards and fostering a robust ecosystem of chiplet suppliers and integrators is essential for widespread adoption.

Security considerations in chiplet-based systems present unique challenges, particularly in energy optimization platforms where sensitive data may be processed. Ensuring secure communication between chiplets and implementing robust security measures to protect against potential vulnerabilities in multi-chiplet designs is crucial.

Finally, the economic viability of chiplet technologies in energy optimization platforms remains a challenge. While chiplets offer potential cost savings through improved yield and flexibility, the initial investment in design, manufacturing, and testing infrastructure can be substantial. Balancing the benefits of chiplet technologies with their associated costs is essential for their successful adoption in energy optimization applications.

Thermal management poses another critical challenge in chiplet-based designs for energy optimization platforms. As multiple chiplets are packed closely together, heat dissipation becomes a major concern. Efficient cooling solutions and thermal design considerations are essential to maintain optimal performance and prevent thermal-induced failures.

Power distribution and management across multiple chiplets present unique challenges in energy optimization platforms. Ensuring uniform power delivery to each chiplet and managing power consumption across the entire system requires sophisticated power management techniques and advanced power delivery networks.

The design and verification of chiplet-based systems introduce additional complexities. Ensuring compatibility and interoperability between chiplets from different vendors or with varying process nodes can be challenging. Comprehensive testing and validation procedures are necessary to guarantee system-wide functionality and reliability.

Manufacturing and yield issues also pose challenges in chiplet technologies. The production of high-quality chiplets and their subsequent integration into a single package require advanced manufacturing processes and stringent quality control measures. Yield management becomes crucial to ensure cost-effectiveness in chiplet-based designs.

Standardization and ecosystem development remain ongoing challenges in the chiplet industry. The lack of widely adopted standards for chiplet interfaces and protocols can hinder interoperability and limit the potential for mix-and-match chiplet designs. Establishing industry-wide standards and fostering a robust ecosystem of chiplet suppliers and integrators is essential for widespread adoption.

Security considerations in chiplet-based systems present unique challenges, particularly in energy optimization platforms where sensitive data may be processed. Ensuring secure communication between chiplets and implementing robust security measures to protect against potential vulnerabilities in multi-chiplet designs is crucial.

Finally, the economic viability of chiplet technologies in energy optimization platforms remains a challenge. While chiplets offer potential cost savings through improved yield and flexibility, the initial investment in design, manufacturing, and testing infrastructure can be substantial. Balancing the benefits of chiplet technologies with their associated costs is essential for their successful adoption in energy optimization applications.

Current Chiplet Solutions

01 Power management in chiplet architectures

Implementing advanced power management techniques in chiplet-based systems to optimize energy consumption. This includes dynamic voltage and frequency scaling, power gating, and intelligent power distribution among chiplets based on workload requirements.- Power management in chiplet architectures: Implementing advanced power management techniques in chiplet-based designs to optimize energy consumption. This includes dynamic voltage and frequency scaling, power gating, and intelligent power distribution among chiplets based on workload requirements.

- Thermal optimization for chiplet systems: Developing thermal management solutions specifically tailored for chiplet architectures. This involves innovative cooling techniques, thermal-aware chiplet placement, and the use of advanced materials to improve heat dissipation and overall energy efficiency.

- Inter-chiplet communication optimization: Enhancing the energy efficiency of data transfer between chiplets through optimized interconnect technologies, low-power signaling protocols, and intelligent data routing algorithms to minimize communication-related power consumption.

- AI-driven energy optimization for chiplets: Utilizing artificial intelligence and machine learning techniques to dynamically optimize chiplet performance and power consumption. This includes predictive power management, workload-based chiplet activation, and adaptive resource allocation.

- 3D integration for chiplet energy efficiency: Exploring three-dimensional integration techniques for chiplets to reduce interconnect lengths, improve thermal management, and enhance overall system energy efficiency. This includes through-silicon vias (TSVs) and advanced packaging technologies.

02 Thermal optimization for chiplet designs

Developing thermal management solutions specifically tailored for chiplet architectures. This involves efficient heat dissipation techniques, thermal-aware chiplet placement, and adaptive cooling mechanisms to maintain optimal operating temperatures and reduce energy waste.Expand Specific Solutions03 Inter-chiplet communication efficiency

Enhancing the energy efficiency of data transfer between chiplets. This includes optimizing interconnect technologies, implementing low-power signaling protocols, and developing intelligent data routing algorithms to minimize communication-related power consumption.Expand Specific Solutions04 Chiplet-specific clock and power domain management

Implementing fine-grained clock and power domain control for individual chiplets. This allows for selective activation and deactivation of chiplet components based on computational needs, leading to improved overall energy efficiency of the system.Expand Specific Solutions05 AI-driven energy optimization for chiplet systems

Utilizing artificial intelligence and machine learning techniques to dynamically optimize energy consumption in chiplet-based architectures. This includes predictive power management, workload-aware resource allocation, and adaptive performance tuning to maximize energy efficiency.Expand Specific Solutions

Key Chiplet Players

The research on chiplet technologies in energy optimization platforms is currently in a dynamic and competitive phase, with the market showing significant growth potential. The industry is transitioning from early-stage development to more mature applications, driven by increasing demand for energy-efficient computing solutions. Key players like Intel, Micron Technology, and AMD are at the forefront, leveraging their expertise in semiconductor design and manufacturing. The technology's maturity varies, with established companies having a head start, but innovative startups like AvicenaTech are also making strides. Academic institutions such as Carnegie Mellon University and the University of Electronic Science & Technology of China are contributing to research advancements, fostering a collaborative ecosystem that spans industry and academia.

Micron Technology, Inc.

Technical Solution: Micron's approach to chiplet technologies in energy optimization platforms centers on their Hybrid Memory Cube (HMC) and High Bandwidth Memory (HBM) solutions. These technologies utilize 3D stacking of memory dies, which significantly reduces power consumption and improves bandwidth. Micron's HBM2 technology demonstrates up to 50% lower power consumption per bit compared to GDDR5 memory[5]. The company is also exploring the integration of processing-in-memory (PIM) capabilities within their chiplet-based memory solutions, which can reduce data movement and further improve energy efficiency. Micron's 3D NAND technology, which stacks multiple layers of memory cells, has shown up to 40% improvement in energy efficiency compared to planar NAND[6]. Additionally, Micron is investing in advanced packaging technologies to enable closer integration of memory chiplets with processors, potentially reducing system-level power consumption.

Strengths: Expertise in memory technologies, advanced 3D stacking capabilities, and integration of processing-in-memory features. Weaknesses: Limited experience in non-memory chiplet integration and potential cost challenges for high-bandwidth solutions.

Intel Corp.

Technical Solution: Intel's approach to chiplet technologies in energy optimization platforms focuses on their Foveros 3D packaging technology. This advanced packaging solution allows for the vertical stacking of multiple chiplets, enabling higher performance and lower power consumption. Intel has demonstrated up to 50% area reduction compared to traditional 2D designs[1]. The company has also introduced their EMIB (Embedded Multi-die Interconnect Bridge) technology, which provides high-bandwidth, low-power connections between chiplets. Intel's Ponte Vecchio GPU, built using chiplet technology, achieves over 45 TFLOPS of FP32 performance while maintaining energy efficiency[2]. Additionally, Intel is exploring the use of advanced materials and heterogeneous integration to further optimize power consumption in their chiplet designs.

Strengths: Advanced 3D packaging expertise, high-performance interconnect technologies, and a strong ecosystem for chiplet integration. Weaknesses: Higher manufacturing complexity and potential thermal management challenges in densely packed 3D structures.

Chiplet Innovations

Optimizing energy consumption of production lines using intelligent digital twins

PatentActiveUS11880250B2

Innovation

- A Production Line Optimization (PLO) platform is introduced, which uses a Process Aware Energy Consumption (PAEC) digital twin to analyze and optimize energy usage by generating knowledge graphs, executing advanced analytics, and providing energy-saving recommendations, adjusting machine configurations within specified constraints.

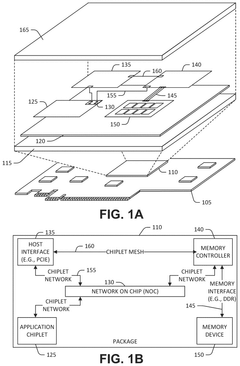

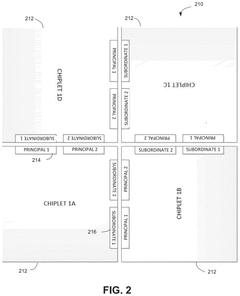

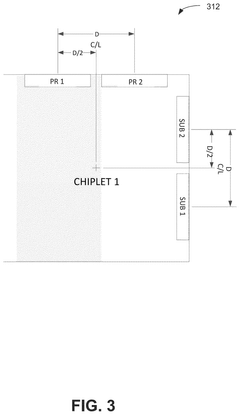

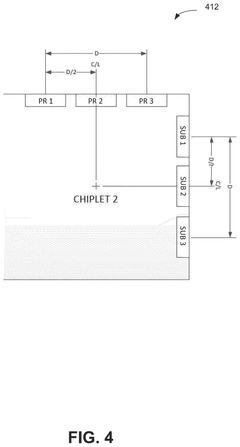

Edge interface placements to enable chiplet rotation into multi-chiplet cluster

PatentPendingUS20240332257A1

Innovation

- The implementation of a chiplet architecture that uses a network-on-chip (NOC) with a chiplet protocol interface (CPI) to facilitate high-speed, flexible inter-chiplet communication, combined with a tightly packed matrix arrangement of chiplets and I/O micro-bumps for close-coupled interconnects, allowing for proper alignment and minimal footprint.

Chiplet Supply Chain

The chiplet supply chain plays a crucial role in the development and implementation of energy optimization platforms utilizing chiplet technologies. This complex ecosystem involves multiple stakeholders, each contributing to the production and integration of chiplets into final products.

At the core of the chiplet supply chain are the foundries, which manufacture the individual chiplets using advanced semiconductor processes. These foundries, such as TSMC, Samsung, and Intel, invest heavily in cutting-edge manufacturing technologies to produce high-performance, energy-efficient chiplets. Their capabilities and capacity significantly influence the availability and cost of chiplets in the market.

Design houses and intellectual property (IP) providers form another critical link in the chain. They develop the architectures and designs for various chiplets, focusing on specific functionalities or performance characteristics. Companies like ARM, Synopsys, and Cadence provide essential IP blocks that can be integrated into chiplet designs, enabling rapid innovation and customization.

Packaging and integration specialists play a vital role in assembling multiple chiplets into a cohesive system. Advanced packaging technologies, such as 2.5D and 3D integration, are essential for realizing the full potential of chiplet-based designs. Companies like ASE Group, Amkor, and JCET specialize in these advanced packaging solutions, which are crucial for optimizing energy efficiency and performance in multi-chiplet systems.

Testing and validation services are indispensable in ensuring the quality and reliability of chiplet-based products. Specialized equipment and methodologies are required to test individual chiplets as well as the integrated systems. Companies like Advantest and Teradyne provide advanced testing solutions tailored for chiplet technologies.

The supply chain also includes providers of essential materials and components, such as substrates, interposers, and thermal management solutions. These elements are critical for the proper functioning and energy efficiency of chiplet-based systems. Companies like Ibiden, Unimicron, and Shinko Electric Industries are key players in this segment.

System integrators and OEMs represent the final stage of the chiplet supply chain, incorporating chiplet-based solutions into end products for various applications, including energy optimization platforms. These companies work closely with chiplet suppliers and packaging specialists to design and manufacture products that leverage the benefits of chiplet technologies.

The complexity of the chiplet supply chain necessitates close collaboration and coordination among all participants. Standardization efforts, such as those led by the Open Compute Project and CHIPS Alliance, aim to streamline interoperability and reduce fragmentation in the ecosystem. As chiplet technologies continue to evolve, the supply chain is expected to adapt, with potential consolidation and specialization among players to meet the growing demand for energy-efficient, high-performance computing solutions.

At the core of the chiplet supply chain are the foundries, which manufacture the individual chiplets using advanced semiconductor processes. These foundries, such as TSMC, Samsung, and Intel, invest heavily in cutting-edge manufacturing technologies to produce high-performance, energy-efficient chiplets. Their capabilities and capacity significantly influence the availability and cost of chiplets in the market.

Design houses and intellectual property (IP) providers form another critical link in the chain. They develop the architectures and designs for various chiplets, focusing on specific functionalities or performance characteristics. Companies like ARM, Synopsys, and Cadence provide essential IP blocks that can be integrated into chiplet designs, enabling rapid innovation and customization.

Packaging and integration specialists play a vital role in assembling multiple chiplets into a cohesive system. Advanced packaging technologies, such as 2.5D and 3D integration, are essential for realizing the full potential of chiplet-based designs. Companies like ASE Group, Amkor, and JCET specialize in these advanced packaging solutions, which are crucial for optimizing energy efficiency and performance in multi-chiplet systems.

Testing and validation services are indispensable in ensuring the quality and reliability of chiplet-based products. Specialized equipment and methodologies are required to test individual chiplets as well as the integrated systems. Companies like Advantest and Teradyne provide advanced testing solutions tailored for chiplet technologies.

The supply chain also includes providers of essential materials and components, such as substrates, interposers, and thermal management solutions. These elements are critical for the proper functioning and energy efficiency of chiplet-based systems. Companies like Ibiden, Unimicron, and Shinko Electric Industries are key players in this segment.

System integrators and OEMs represent the final stage of the chiplet supply chain, incorporating chiplet-based solutions into end products for various applications, including energy optimization platforms. These companies work closely with chiplet suppliers and packaging specialists to design and manufacture products that leverage the benefits of chiplet technologies.

The complexity of the chiplet supply chain necessitates close collaboration and coordination among all participants. Standardization efforts, such as those led by the Open Compute Project and CHIPS Alliance, aim to streamline interoperability and reduce fragmentation in the ecosystem. As chiplet technologies continue to evolve, the supply chain is expected to adapt, with potential consolidation and specialization among players to meet the growing demand for energy-efficient, high-performance computing solutions.

Chiplet Standardization

Chiplet standardization is a critical aspect of advancing energy optimization platforms in the semiconductor industry. As chiplet technologies continue to evolve, the need for standardized interfaces, protocols, and design methodologies becomes increasingly important. The development of industry-wide standards enables interoperability between chiplets from different manufacturers, fostering innovation and reducing time-to-market for complex system-on-chip (SoC) designs.

One of the key initiatives in chiplet standardization is the Universal Chiplet Interconnect Express (UCIe) specification. UCIe aims to establish a common interconnect standard for chiplets, allowing seamless integration of diverse components from multiple vendors. This standard addresses various aspects of chiplet-to-chiplet communication, including physical layer specifications, protocol layer definitions, and power management features.

Another significant standardization effort is the Open Compute Project's Open Domain-Specific Architecture (ODSA) workgroup. ODSA focuses on developing open specifications for chiplet-based systems, covering areas such as die-to-die interfaces, thermal management, and packaging technologies. These standards aim to create a more open and collaborative ecosystem for chiplet development and integration.

The Advanced Interface Bus (AIB) is another important standard in the chiplet domain. Developed by Intel and now available as an open standard, AIB provides a high-bandwidth, low-power interface for chiplet-to-chiplet communication. This standard has gained traction in the industry and is being adopted by various semiconductor companies for their chiplet designs.

Standardization efforts also extend to packaging technologies, which are crucial for chiplet integration. The development of advanced packaging standards, such as JEDEC's JEP30 for 2.5D and 3D packaging, ensures compatibility and reliability across different chiplet implementations. These standards address critical aspects such as thermal management, signal integrity, and power delivery in multi-chiplet systems.

As energy optimization becomes increasingly important in chiplet-based designs, standardization efforts are also focusing on power management protocols. The development of common power control interfaces and energy-aware communication standards enables more efficient power distribution and management across chiplets, contributing to overall system energy optimization.

The ongoing collaboration between industry leaders, research institutions, and standards organizations is driving the evolution of chiplet standards. These efforts are essential for creating a robust ecosystem that supports the widespread adoption of chiplet technologies in energy-efficient computing platforms.

One of the key initiatives in chiplet standardization is the Universal Chiplet Interconnect Express (UCIe) specification. UCIe aims to establish a common interconnect standard for chiplets, allowing seamless integration of diverse components from multiple vendors. This standard addresses various aspects of chiplet-to-chiplet communication, including physical layer specifications, protocol layer definitions, and power management features.

Another significant standardization effort is the Open Compute Project's Open Domain-Specific Architecture (ODSA) workgroup. ODSA focuses on developing open specifications for chiplet-based systems, covering areas such as die-to-die interfaces, thermal management, and packaging technologies. These standards aim to create a more open and collaborative ecosystem for chiplet development and integration.

The Advanced Interface Bus (AIB) is another important standard in the chiplet domain. Developed by Intel and now available as an open standard, AIB provides a high-bandwidth, low-power interface for chiplet-to-chiplet communication. This standard has gained traction in the industry and is being adopted by various semiconductor companies for their chiplet designs.

Standardization efforts also extend to packaging technologies, which are crucial for chiplet integration. The development of advanced packaging standards, such as JEDEC's JEP30 for 2.5D and 3D packaging, ensures compatibility and reliability across different chiplet implementations. These standards address critical aspects such as thermal management, signal integrity, and power delivery in multi-chiplet systems.

As energy optimization becomes increasingly important in chiplet-based designs, standardization efforts are also focusing on power management protocols. The development of common power control interfaces and energy-aware communication standards enables more efficient power distribution and management across chiplets, contributing to overall system energy optimization.

The ongoing collaboration between industry leaders, research institutions, and standards organizations is driving the evolution of chiplet standards. These efforts are essential for creating a robust ecosystem that supports the widespread adoption of chiplet technologies in energy-efficient computing platforms.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!