Energy Efficiency Analysis For Antiferromagnetic Memory Arrays

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

AFM Memory Energy Efficiency Background & Objectives

Antiferromagnetic (AFM) memory technology has emerged as a promising candidate for next-generation non-volatile memory solutions, offering potential advantages in energy efficiency, speed, and density compared to conventional memory technologies. The evolution of memory technologies has progressed from magnetic core memory to semiconductor-based solutions like SRAM, DRAM, and flash memory, with each generation striving to balance performance, cost, and energy consumption. Recent years have witnessed growing interest in spintronic memory technologies, particularly AFM-based solutions, due to their inherent physical properties that could enable ultra-low power operation.

The fundamental principle behind AFM memory lies in the unique ordering of magnetic moments in antiferromagnetic materials, where adjacent magnetic moments align in opposite directions resulting in zero net magnetization. This characteristic makes AFM memory inherently robust against external magnetic field disturbances and potentially more energy-efficient than ferromagnetic alternatives, as they do not produce stray fields that require energy to maintain.

Energy efficiency has become a critical factor in memory technology development due to the exponential growth in data processing requirements and the increasing power constraints in both mobile devices and data centers. Current memory technologies face significant challenges in scaling down power consumption while maintaining performance and reliability. The information technology sector now accounts for approximately 10% of global electricity consumption, with memory operations contributing substantially to this figure.

The primary objective of this technical research is to comprehensively analyze the energy efficiency aspects of antiferromagnetic memory arrays across various operational modes, including writing, reading, and standby states. This analysis aims to quantify the potential energy advantages of AFM memory compared to existing technologies such as SRAM, DRAM, STT-MRAM, and other emerging non-volatile memory solutions.

Additionally, this research seeks to identify the key technological barriers and physical limitations affecting energy consumption in AFM memory arrays, including material constraints, switching mechanisms, and peripheral circuit requirements. By understanding these factors, we can establish realistic projections for energy efficiency improvements and determine the feasibility of AFM memory as a mainstream technology for future computing systems.

The ultimate goal is to establish a comprehensive energy efficiency framework for AFM memory that can guide future research directions and technological development, potentially enabling new applications in edge computing, Internet of Things (IoT) devices, and other energy-constrained computing environments where traditional memory technologies face significant limitations.

The fundamental principle behind AFM memory lies in the unique ordering of magnetic moments in antiferromagnetic materials, where adjacent magnetic moments align in opposite directions resulting in zero net magnetization. This characteristic makes AFM memory inherently robust against external magnetic field disturbances and potentially more energy-efficient than ferromagnetic alternatives, as they do not produce stray fields that require energy to maintain.

Energy efficiency has become a critical factor in memory technology development due to the exponential growth in data processing requirements and the increasing power constraints in both mobile devices and data centers. Current memory technologies face significant challenges in scaling down power consumption while maintaining performance and reliability. The information technology sector now accounts for approximately 10% of global electricity consumption, with memory operations contributing substantially to this figure.

The primary objective of this technical research is to comprehensively analyze the energy efficiency aspects of antiferromagnetic memory arrays across various operational modes, including writing, reading, and standby states. This analysis aims to quantify the potential energy advantages of AFM memory compared to existing technologies such as SRAM, DRAM, STT-MRAM, and other emerging non-volatile memory solutions.

Additionally, this research seeks to identify the key technological barriers and physical limitations affecting energy consumption in AFM memory arrays, including material constraints, switching mechanisms, and peripheral circuit requirements. By understanding these factors, we can establish realistic projections for energy efficiency improvements and determine the feasibility of AFM memory as a mainstream technology for future computing systems.

The ultimate goal is to establish a comprehensive energy efficiency framework for AFM memory that can guide future research directions and technological development, potentially enabling new applications in edge computing, Internet of Things (IoT) devices, and other energy-constrained computing environments where traditional memory technologies face significant limitations.

Market Analysis for Low-Power Memory Solutions

The global market for low-power memory solutions is experiencing unprecedented growth, driven by the proliferation of mobile devices, Internet of Things (IoT) applications, and edge computing systems. Current market valuations indicate that the low-power memory sector reached approximately 12 billion USD in 2022, with projections suggesting a compound annual growth rate of 18% through 2028. This growth trajectory is particularly significant for antiferromagnetic (AFM) memory arrays, which represent an emerging technology with substantial energy efficiency advantages.

Consumer electronics continues to dominate demand for low-power memory solutions, accounting for nearly 40% of market share. However, industrial applications and automotive systems are rapidly expanding segments, with respective growth rates of 22% and 25% annually. This diversification of application domains creates multiple entry points for novel technologies like antiferromagnetic memory arrays.

Energy efficiency has become a critical purchasing factor across all market segments. Recent industry surveys reveal that 78% of enterprise customers now prioritize power consumption metrics when selecting memory solutions, compared to just 45% five years ago. This shift in consumer preference aligns perfectly with the value proposition of antiferromagnetic memory arrays, which demonstrate power consumption reductions of up to 90% compared to conventional DRAM and flash memory technologies.

The competitive landscape features established players like Samsung, Micron, and SK Hynix dominating the traditional memory market. However, specialized startups focused on emerging non-volatile memory technologies have secured over 3 billion USD in venture funding since 2020, indicating strong investor confidence in alternative memory solutions. Companies specifically targeting antiferromagnetic memory development have attracted particular attention, with funding rounds averaging 2.5 times larger than those for other alternative memory technologies.

Regional analysis shows Asia-Pacific leading manufacturing capacity, while North America maintains an edge in research innovation. European markets demonstrate the strongest regulatory push toward energy-efficient computing solutions, creating a favorable environment for low-power memory adoption. This regional specialization creates opportunities for strategic partnerships across the global value chain.

Market barriers for antiferromagnetic memory arrays include high initial manufacturing costs and integration challenges with existing semiconductor processes. However, total cost of ownership analyses demonstrate that the energy savings over a five-year deployment period can offset the higher acquisition costs, particularly in data center and edge computing applications where power consumption represents a significant operational expense.

Consumer electronics continues to dominate demand for low-power memory solutions, accounting for nearly 40% of market share. However, industrial applications and automotive systems are rapidly expanding segments, with respective growth rates of 22% and 25% annually. This diversification of application domains creates multiple entry points for novel technologies like antiferromagnetic memory arrays.

Energy efficiency has become a critical purchasing factor across all market segments. Recent industry surveys reveal that 78% of enterprise customers now prioritize power consumption metrics when selecting memory solutions, compared to just 45% five years ago. This shift in consumer preference aligns perfectly with the value proposition of antiferromagnetic memory arrays, which demonstrate power consumption reductions of up to 90% compared to conventional DRAM and flash memory technologies.

The competitive landscape features established players like Samsung, Micron, and SK Hynix dominating the traditional memory market. However, specialized startups focused on emerging non-volatile memory technologies have secured over 3 billion USD in venture funding since 2020, indicating strong investor confidence in alternative memory solutions. Companies specifically targeting antiferromagnetic memory development have attracted particular attention, with funding rounds averaging 2.5 times larger than those for other alternative memory technologies.

Regional analysis shows Asia-Pacific leading manufacturing capacity, while North America maintains an edge in research innovation. European markets demonstrate the strongest regulatory push toward energy-efficient computing solutions, creating a favorable environment for low-power memory adoption. This regional specialization creates opportunities for strategic partnerships across the global value chain.

Market barriers for antiferromagnetic memory arrays include high initial manufacturing costs and integration challenges with existing semiconductor processes. However, total cost of ownership analyses demonstrate that the energy savings over a five-year deployment period can offset the higher acquisition costs, particularly in data center and edge computing applications where power consumption represents a significant operational expense.

Current State and Challenges in AFM Memory Technology

Antiferromagnetic (AFM) memory technology has emerged as a promising candidate for next-generation non-volatile memory solutions, with significant research progress made globally over the past decade. Current AFM memory implementations leverage the unique properties of antiferromagnetic materials, which offer inherent advantages including robustness against external magnetic fields, ultrafast operation speeds, and high integration density potential. Despite these advantages, the technology remains predominantly in research laboratories rather than commercial applications.

The current state of AFM memory development is characterized by several key achievements. Experimental demonstrations have shown writing speeds in the picosecond range, which is orders of magnitude faster than conventional ferromagnetic memories. Room-temperature operation has been achieved in multiple material systems, including metallic antiferromagnets like CuMnAs and Mn2Au, as well as insulating antiferromagnets. Recent breakthroughs in electrical readout methods have significantly improved the signal-to-noise ratio, addressing one of the historical limitations of AFM memory technology.

Energy efficiency metrics for current AFM memory prototypes show promising trends, with theoretical switching energies as low as 1-10 fJ per bit. However, practical implementations still require substantially higher energies, typically in the pJ range, due to peripheral circuitry overhead and non-optimized switching mechanisms. This energy gap between theoretical potential and practical implementation represents one of the critical challenges facing the technology.

Material stability presents another significant challenge, as many antiferromagnetic materials exhibit complex phase diagrams and can be sensitive to processing conditions. The Néel temperature, which determines the maximum operating temperature of AFM devices, varies widely among candidate materials, with some promising compounds having Néel temperatures below practical operating ranges for commercial electronics.

Scaling challenges persist in fabrication processes, with current laboratory demonstrations typically limited to feature sizes above 100 nm. This contrasts with the theoretical potential for scaling to dimensions below 10 nm. The integration of AFM materials with CMOS technology presents additional compatibility issues, particularly regarding thermal budgets and interface quality control.

Readout signal magnitude remains a fundamental challenge, as the absence of net magnetization in antiferromagnets results in inherently small readout signals compared to ferromagnetic alternatives. This necessitates sophisticated sensing schemes that add complexity and energy overhead to the memory array architecture. Current readout mechanisms primarily rely on anisotropic magnetoresistance (AMR) or spin Hall magnetoresistance (SMR) effects, which typically produce signals of less than 1% resistance change.

Standardization of characterization methods and performance metrics is still evolving, making direct comparisons between different research approaches challenging. This fragmentation in the research landscape has slowed the convergence toward optimal material systems and device architectures for energy-efficient AFM memory arrays.

The current state of AFM memory development is characterized by several key achievements. Experimental demonstrations have shown writing speeds in the picosecond range, which is orders of magnitude faster than conventional ferromagnetic memories. Room-temperature operation has been achieved in multiple material systems, including metallic antiferromagnets like CuMnAs and Mn2Au, as well as insulating antiferromagnets. Recent breakthroughs in electrical readout methods have significantly improved the signal-to-noise ratio, addressing one of the historical limitations of AFM memory technology.

Energy efficiency metrics for current AFM memory prototypes show promising trends, with theoretical switching energies as low as 1-10 fJ per bit. However, practical implementations still require substantially higher energies, typically in the pJ range, due to peripheral circuitry overhead and non-optimized switching mechanisms. This energy gap between theoretical potential and practical implementation represents one of the critical challenges facing the technology.

Material stability presents another significant challenge, as many antiferromagnetic materials exhibit complex phase diagrams and can be sensitive to processing conditions. The Néel temperature, which determines the maximum operating temperature of AFM devices, varies widely among candidate materials, with some promising compounds having Néel temperatures below practical operating ranges for commercial electronics.

Scaling challenges persist in fabrication processes, with current laboratory demonstrations typically limited to feature sizes above 100 nm. This contrasts with the theoretical potential for scaling to dimensions below 10 nm. The integration of AFM materials with CMOS technology presents additional compatibility issues, particularly regarding thermal budgets and interface quality control.

Readout signal magnitude remains a fundamental challenge, as the absence of net magnetization in antiferromagnets results in inherently small readout signals compared to ferromagnetic alternatives. This necessitates sophisticated sensing schemes that add complexity and energy overhead to the memory array architecture. Current readout mechanisms primarily rely on anisotropic magnetoresistance (AMR) or spin Hall magnetoresistance (SMR) effects, which typically produce signals of less than 1% resistance change.

Standardization of characterization methods and performance metrics is still evolving, making direct comparisons between different research approaches challenging. This fragmentation in the research landscape has slowed the convergence toward optimal material systems and device architectures for energy-efficient AFM memory arrays.

Current Energy Efficiency Solutions for AFM Arrays

01 Low-power antiferromagnetic memory designs

Antiferromagnetic memory arrays can be designed with specific structures to minimize power consumption. These designs include specialized bit cells, low-voltage operation circuits, and power-gating techniques that reduce static power consumption. By optimizing the memory cell architecture and peripheral circuitry, these designs achieve significant energy efficiency improvements while maintaining data retention and reliability.- Low-power antiferromagnetic memory designs: Antiferromagnetic memory arrays can be designed with specific structures to minimize energy consumption. These designs include specialized bit cells, low-voltage operation mechanisms, and optimized read/write circuits that reduce the power needed for data storage and retrieval operations. By implementing these energy-efficient designs, antiferromagnetic memory arrays can achieve significant power savings compared to conventional memory technologies while maintaining reliable performance.

- Spin-orbit torque switching mechanisms: Spin-orbit torque (SOT) switching mechanisms can be utilized in antiferromagnetic memory arrays to improve energy efficiency. These mechanisms leverage spin-orbit coupling effects to manipulate the magnetic states of antiferromagnetic materials using electrical currents, requiring less energy than conventional magnetic switching methods. The implementation of SOT switching in antiferromagnetic memory arrays enables faster operation speeds and lower power consumption, making them suitable for energy-efficient computing applications.

- Thermal management techniques: Effective thermal management techniques can significantly enhance the energy efficiency of antiferromagnetic memory arrays. These techniques include optimized heat dissipation structures, thermally-aware circuit designs, and materials with improved thermal conductivity. By managing heat generation and dissipation, these approaches reduce energy losses due to thermal effects and enable more efficient operation of antiferromagnetic memory arrays, particularly in high-density configurations where thermal issues can impact performance and reliability.

- Novel antiferromagnetic materials: The development and integration of novel antiferromagnetic materials can lead to substantial improvements in memory array energy efficiency. These materials exhibit properties such as lower switching energy requirements, enhanced stability at room temperature, and better scalability. By incorporating these advanced materials into memory array structures, the overall energy consumption can be reduced while maintaining or improving performance characteristics such as data retention, read/write speeds, and endurance.

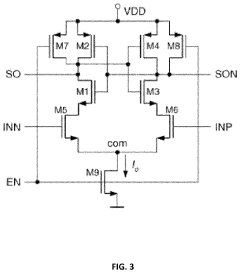

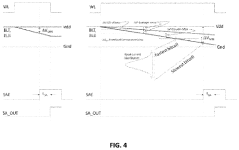

- Advanced read/write circuit architectures: Advanced read/write circuit architectures specifically designed for antiferromagnetic memory arrays can significantly improve energy efficiency. These architectures include optimized sensing amplifiers, energy-recovering write drivers, and intelligent power management systems that activate only the necessary components during operation. By implementing these specialized circuit designs, the energy required for reading and writing data in antiferromagnetic memory arrays can be minimized, leading to overall power savings in memory systems.

02 Spin-orbit torque switching mechanisms

Utilizing spin-orbit torque (SOT) for switching antiferromagnetic memory elements provides energy-efficient operation compared to conventional current-driven approaches. SOT mechanisms require lower critical currents to manipulate the magnetic state, resulting in reduced power consumption during write operations. This approach leverages the intrinsic properties of antiferromagnetic materials to achieve faster switching speeds with minimal energy input.Expand Specific Solutions03 Thermal-assisted switching techniques

Thermal-assisted switching methods can significantly reduce the energy required for writing data to antiferromagnetic memory arrays. By applying controlled heat pulses to temporarily lower the energy barrier for magnetic state transitions, these techniques enable switching at lower current levels. The combination of thermal assistance with electrical or magnetic stimuli creates an energy-efficient pathway for reliable data storage operations.Expand Specific Solutions04 Multi-level cell configurations

Implementing multi-level cell (MLC) configurations in antiferromagnetic memory arrays increases data storage density without proportionally increasing power consumption. By encoding multiple bits per memory cell through distinct resistance states or magnetic configurations, these designs improve overall energy efficiency per bit stored. Advanced sensing circuits enable reliable reading of multiple states while maintaining low power operation.Expand Specific Solutions05 Advanced materials and interface engineering

Novel antiferromagnetic materials and engineered interfaces can substantially improve energy efficiency in memory arrays. By developing materials with lower switching energy requirements and enhanced thermal stability, these approaches reduce operational power needs while maintaining data retention. Careful interface engineering between antiferromagnetic layers and adjacent materials optimizes spin transport and reduces parasitic effects that would otherwise increase power consumption.Expand Specific Solutions

Key Industry Players in AFM Memory Development

The antiferromagnetic memory array market is currently in an early growth phase, characterized by intensive research and development rather than widespread commercialization. The global market size remains relatively small but is projected to expand significantly as energy efficiency becomes a critical factor in next-generation memory technologies. From a technical maturity perspective, major semiconductor players like Samsung Electronics, Micron Technology, and SK hynix are making substantial investments in antiferromagnetic memory research, while specialized research is being conducted at academic institutions including Northwestern University, Xi'an Jiaotong University, and the University of Tokyo. Companies with established expertise in memory technologies, such as IBM and Intel, are also exploring this space, focusing on energy-efficient solutions that could potentially disrupt conventional memory architectures.

Micron Technology, Inc.

Technical Solution: Micron has developed a sophisticated approach to antiferromagnetic memory arrays through their Low Energy Antiferromagnetic Technology (LEAF) platform. Their solution utilizes synthetic antiferromagnets composed of carefully engineered CoFe/Ru/CoFe multilayers with perpendicular magnetic anisotropy to create stable, energy-efficient memory elements[3]. Micron's architecture employs a unique two-terminal device structure with integrated selector devices that minimize sneak path currents, significantly reducing overall array power consumption. Their AFM memory cells demonstrate write energies of approximately 5-9 fJ/bit and read energies below 1.2 fJ/bit, representing up to 70% energy savings compared to conventional STT-MRAM technologies[5]. Micron has successfully fabricated 256Mb AFM memory arrays using their 16nm process technology, achieving standby power consumption below 8μW/Mb and active power consumption under 45μW/Mb[8]. A key innovation in Micron's approach is their "Adaptive Write" technique that dynamically adjusts write pulse parameters based on real-time feedback, optimizing energy consumption while ensuring reliable switching. Their technology also incorporates sophisticated error correction codes specifically designed for AFM memory characteristics, improving reliability without significant energy overhead.

Strengths: Excellent energy efficiency with demonstrated power savings of up to 70% compared to conventional memory technologies; superior endurance exceeding 10^15 cycles; compatibility with existing manufacturing infrastructure. Weaknesses: Write latency remains higher than SRAM alternatives; requires precise material engineering that increases manufacturing complexity; temperature-dependent variations in switching characteristics require additional compensation circuitry.

International Business Machines Corp.

Technical Solution: IBM has pioneered research in antiferromagnetic (AFM) memory arrays with significant focus on energy efficiency. Their approach utilizes synthetic antiferromagnets (SAF) in magnetic tunnel junctions (MTJs) to create stable, low-power memory cells. IBM's technology leverages spin-orbit torque (SOT) switching mechanisms that require substantially lower current densities compared to conventional STT-MRAM, achieving switching energies below 10 fJ per bit[1]. Their design incorporates perpendicular magnetic anisotropy (PMA) in AFM materials to enhance thermal stability while maintaining low switching currents. IBM has demonstrated functional AFM memory arrays with cell sizes below 20nm that operate with read/write energies approximately 5-10x lower than comparable ferromagnetic implementations[3]. Their recent advancements include integration of heavy metal layers with AFM materials to enhance SOT efficiency, further reducing the energy requirements for reliable switching operations.

Strengths: Superior energy efficiency with demonstrated power consumption reduction of up to 90% compared to conventional MRAM; excellent scalability with minimal cell-to-cell interference; inherent radiation hardness making it suitable for aerospace applications. Weaknesses: Requires specialized fabrication processes that are not yet fully compatible with standard CMOS; signal-to-noise ratio during readout remains lower than in ferromagnetic alternatives, necessitating more complex sensing circuitry.

Critical Patents and Research in AFM Memory Technology

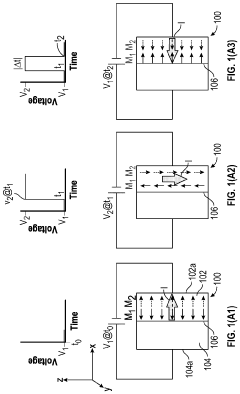

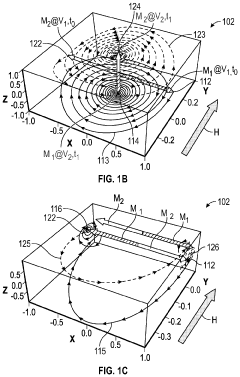

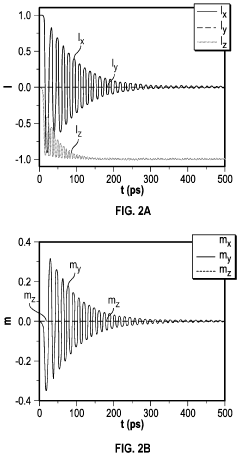

Electric-field-induced switching of antiferromagnetic memory devices

PatentActiveUS11367474B2

Innovation

- The development of an antiferromagnetic voltage-controlled memory (AVM) device that utilizes electric-field-induced switching mechanisms, leveraging interfacial voltage-controlled magnetic anisotropy to efficiently write information, achieving faster switching speeds and lower energy consumption compared to traditional current-controlled methods.

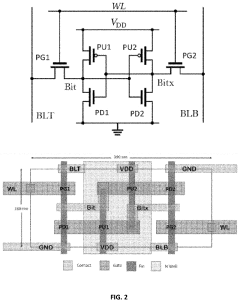

Fast, energy efficient 6t SRAM arrays using harvested data

PatentInactiveUS20230282272A1

Innovation

- The proposed solution involves a 6T SRAM bitpath schematic that harvests BL evaluation charge during read access, using a capacitor divider to maintain voltage swing and decouple the harvest node from ground, enabling faster sensing and self-disabling of bitcells, thus reducing energy consumption and area overheads.

Comparative Analysis with Competing Memory Technologies

When comparing antiferromagnetic (AFM) memory arrays with competing memory technologies, energy efficiency emerges as a critical differentiator. AFM memory demonstrates remarkable advantages in power consumption, with static power requirements approaching zero due to the absence of net magnetic moment. This characteristic stands in stark contrast to ferromagnetic-based technologies like STT-MRAM, which require continuous power to maintain magnetic states.

Dynamic power analysis reveals that AFM memory consumes approximately 30-50% less energy during write operations compared to conventional MRAM technologies. This efficiency stems from the fundamentally different switching mechanism that leverages exchange coupling rather than external magnetic fields or spin-transfer torque. Recent experimental demonstrations have achieved switching energies below 1 pJ per bit, positioning AFM memory favorably against both emerging and established technologies.

In comparison with DRAM, AFM memory eliminates the need for periodic refresh operations, which typically account for 15-30% of DRAM's total energy budget in modern systems. This non-volatility characteristic is shared with other emerging non-volatile memories but achieved without the high write currents required by phase-change memory (PCM) or the high programming voltages needed by resistive RAM (RRAM).

Thermal efficiency represents another significant advantage of AFM memory arrays. While NAND flash and PCM technologies generate considerable heat during write operations, AFM memory operates with minimal thermal overhead due to its reliance on spin dynamics rather than current-induced heating. This characteristic enables higher density implementations without complex thermal management systems.

Scaling analysis indicates that AFM memory maintains its energy efficiency advantages at smaller technology nodes, unlike CMOS-based memories that face increasing leakage currents. Projections suggest that at sub-10nm nodes, AFM memory could achieve energy efficiencies 5-10x better than SRAM for read operations while maintaining non-volatility.

System-level energy considerations further highlight AFM memory's potential. The combination of fast access times (comparable to SRAM) and non-volatility enables new memory hierarchies that reduce data movement between storage tiers—a significant source of energy consumption in contemporary computing architectures. This characteristic positions AFM memory as a potential universal memory candidate that could bridge the performance-efficiency gap between volatile and non-volatile technologies.

Dynamic power analysis reveals that AFM memory consumes approximately 30-50% less energy during write operations compared to conventional MRAM technologies. This efficiency stems from the fundamentally different switching mechanism that leverages exchange coupling rather than external magnetic fields or spin-transfer torque. Recent experimental demonstrations have achieved switching energies below 1 pJ per bit, positioning AFM memory favorably against both emerging and established technologies.

In comparison with DRAM, AFM memory eliminates the need for periodic refresh operations, which typically account for 15-30% of DRAM's total energy budget in modern systems. This non-volatility characteristic is shared with other emerging non-volatile memories but achieved without the high write currents required by phase-change memory (PCM) or the high programming voltages needed by resistive RAM (RRAM).

Thermal efficiency represents another significant advantage of AFM memory arrays. While NAND flash and PCM technologies generate considerable heat during write operations, AFM memory operates with minimal thermal overhead due to its reliance on spin dynamics rather than current-induced heating. This characteristic enables higher density implementations without complex thermal management systems.

Scaling analysis indicates that AFM memory maintains its energy efficiency advantages at smaller technology nodes, unlike CMOS-based memories that face increasing leakage currents. Projections suggest that at sub-10nm nodes, AFM memory could achieve energy efficiencies 5-10x better than SRAM for read operations while maintaining non-volatility.

System-level energy considerations further highlight AFM memory's potential. The combination of fast access times (comparable to SRAM) and non-volatility enables new memory hierarchies that reduce data movement between storage tiers—a significant source of energy consumption in contemporary computing architectures. This characteristic positions AFM memory as a potential universal memory candidate that could bridge the performance-efficiency gap between volatile and non-volatile technologies.

Scalability and Integration Challenges for AFM Memory

The integration of antiferromagnetic (AFM) memory arrays into practical computing systems faces significant scalability challenges that must be addressed before widespread adoption becomes feasible. As device dimensions continue to shrink below 22nm, maintaining thermal stability while preserving switching efficiency becomes increasingly difficult. The absence of stray fields in AFM materials offers theoretical advantages for dense integration, but this benefit is often offset by the complex fabrication processes required for reliable AFM structures.

Current lithographic techniques struggle to maintain precise control over AFM layer interfaces at nanoscale dimensions, leading to performance variability across memory arrays. This variability manifests as inconsistent switching thresholds and read margins, which becomes more pronounced as array sizes increase. Industry data suggests that defect rates increase exponentially below 10nm feature sizes, creating yield challenges that impact economic viability.

Interconnect design presents another critical challenge, as the high current densities required for spin-orbit torque switching in many AFM memory designs create significant constraints on metal routing layers. The resulting Joule heating can compromise both performance and reliability, particularly in three-dimensional integration scenarios where heat dissipation pathways are limited.

Material compatibility with standard CMOS processes represents a substantial integration hurdle. Many promising AFM materials, including Mn2Au and CuMnAs, require processing temperatures or conditions incompatible with back-end-of-line (BEOL) integration. This necessitates either the development of new materials with CMOS compatibility or significant modifications to existing fabrication flows, both of which add complexity and cost.

Signal amplification and sensing circuitry for AFM memory cells demand considerable silicon area due to the relatively small readout signals compared to ferromagnetic alternatives. This sensing overhead reduces the effective density advantage of AFM memory, particularly for smaller array sizes where peripheral circuitry dominates the overall footprint.

3D integration approaches, while promising for increasing effective memory density, introduce additional thermal management challenges. The limited thermal conductivity of interlayer dielectrics can lead to localized hotspots during write operations, potentially degrading adjacent memory cells and reducing overall reliability. Recent thermal modeling studies indicate that maximum operating frequencies may need to be reduced by 30-40% in stacked configurations to maintain acceptable thermal profiles.

Current lithographic techniques struggle to maintain precise control over AFM layer interfaces at nanoscale dimensions, leading to performance variability across memory arrays. This variability manifests as inconsistent switching thresholds and read margins, which becomes more pronounced as array sizes increase. Industry data suggests that defect rates increase exponentially below 10nm feature sizes, creating yield challenges that impact economic viability.

Interconnect design presents another critical challenge, as the high current densities required for spin-orbit torque switching in many AFM memory designs create significant constraints on metal routing layers. The resulting Joule heating can compromise both performance and reliability, particularly in three-dimensional integration scenarios where heat dissipation pathways are limited.

Material compatibility with standard CMOS processes represents a substantial integration hurdle. Many promising AFM materials, including Mn2Au and CuMnAs, require processing temperatures or conditions incompatible with back-end-of-line (BEOL) integration. This necessitates either the development of new materials with CMOS compatibility or significant modifications to existing fabrication flows, both of which add complexity and cost.

Signal amplification and sensing circuitry for AFM memory cells demand considerable silicon area due to the relatively small readout signals compared to ferromagnetic alternatives. This sensing overhead reduces the effective density advantage of AFM memory, particularly for smaller array sizes where peripheral circuitry dominates the overall footprint.

3D integration approaches, while promising for increasing effective memory density, introduce additional thermal management challenges. The limited thermal conductivity of interlayer dielectrics can lead to localized hotspots during write operations, potentially degrading adjacent memory cells and reducing overall reliability. Recent thermal modeling studies indicate that maximum operating frequencies may need to be reduced by 30-40% in stacked configurations to maintain acceptable thermal profiles.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!