How to Reduce Read Disturb in High-Density MRAM Arrays

AUG 27, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

MRAM Technology Evolution and Objectives

Magnetoresistive Random Access Memory (MRAM) has evolved significantly since its conceptualization in the late 1980s. Initially developed as an alternative to conventional memory technologies, MRAM has progressed through several generations, each addressing specific limitations of its predecessors. The first-generation MRAM utilized toggle switching mechanisms, which while innovative, faced scalability challenges at advanced technology nodes.

The introduction of Spin-Transfer Torque MRAM (STT-MRAM) in the early 2000s marked a pivotal advancement, enabling better scalability and reduced power consumption. This was followed by the development of Voltage-Controlled Magnetic Anisotropy (VCMA) and Spin-Orbit Torque (SOT) MRAM, which further enhanced performance metrics and addressed energy efficiency concerns.

Recent years have witnessed the emergence of high-density MRAM arrays, capable of storing vast amounts of data in compact form factors. However, this increased density has introduced new challenges, particularly read disturb phenomena, which occur when reading operations inadvertently affect the magnetic state of adjacent cells, potentially causing data corruption.

The technological trajectory of MRAM has been driven by several key objectives: achieving higher storage densities, reducing power consumption, enhancing data retention, and improving operational reliability. These objectives align with broader industry trends toward more efficient, compact, and reliable memory solutions for diverse applications ranging from IoT devices to data centers.

Current research focuses on mitigating read disturb issues in high-density arrays while maintaining the inherent advantages of MRAM technology, such as non-volatility, high endurance, and fast access times. This involves exploring innovative materials, novel cell architectures, and advanced sensing techniques that can minimize the magnetic field interference during read operations.

The evolution of MRAM technology is also shaped by its potential to bridge the gap between high-speed SRAM and high-density DRAM, potentially revolutionizing memory hierarchy in computing systems. This positions MRAM as a universal memory solution, capable of addressing diverse requirements across the memory spectrum.

Looking forward, the primary technological objectives include developing robust solutions to the read disturb problem in high-density arrays, further scaling down cell size without compromising performance, and enhancing manufacturing processes to improve yield and reduce costs. These advancements are essential for MRAM to achieve widespread adoption and fulfill its promise as a transformative memory technology in the next generation of computing systems.

The introduction of Spin-Transfer Torque MRAM (STT-MRAM) in the early 2000s marked a pivotal advancement, enabling better scalability and reduced power consumption. This was followed by the development of Voltage-Controlled Magnetic Anisotropy (VCMA) and Spin-Orbit Torque (SOT) MRAM, which further enhanced performance metrics and addressed energy efficiency concerns.

Recent years have witnessed the emergence of high-density MRAM arrays, capable of storing vast amounts of data in compact form factors. However, this increased density has introduced new challenges, particularly read disturb phenomena, which occur when reading operations inadvertently affect the magnetic state of adjacent cells, potentially causing data corruption.

The technological trajectory of MRAM has been driven by several key objectives: achieving higher storage densities, reducing power consumption, enhancing data retention, and improving operational reliability. These objectives align with broader industry trends toward more efficient, compact, and reliable memory solutions for diverse applications ranging from IoT devices to data centers.

Current research focuses on mitigating read disturb issues in high-density arrays while maintaining the inherent advantages of MRAM technology, such as non-volatility, high endurance, and fast access times. This involves exploring innovative materials, novel cell architectures, and advanced sensing techniques that can minimize the magnetic field interference during read operations.

The evolution of MRAM technology is also shaped by its potential to bridge the gap between high-speed SRAM and high-density DRAM, potentially revolutionizing memory hierarchy in computing systems. This positions MRAM as a universal memory solution, capable of addressing diverse requirements across the memory spectrum.

Looking forward, the primary technological objectives include developing robust solutions to the read disturb problem in high-density arrays, further scaling down cell size without compromising performance, and enhancing manufacturing processes to improve yield and reduce costs. These advancements are essential for MRAM to achieve widespread adoption and fulfill its promise as a transformative memory technology in the next generation of computing systems.

Market Analysis for High-Density MRAM Solutions

The global MRAM (Magnetoresistive Random Access Memory) market is experiencing robust growth, with projections indicating expansion from $1.1 billion in 2022 to reach approximately $5.3 billion by 2028, representing a compound annual growth rate (CAGR) of 29.7%. This accelerated growth is primarily driven by increasing demand for non-volatile memory solutions that combine the speed of SRAM, the density of DRAM, and the non-volatility of flash memory.

High-density MRAM solutions are particularly gaining traction in several key market segments. The automotive sector represents one of the fastest-growing application areas, with demand for reliable, high-temperature memory solutions for advanced driver assistance systems (ADAS) and autonomous driving technologies. The industrial IoT sector is another significant market, where MRAM's low power consumption and data retention capabilities make it ideal for edge computing devices and sensors.

Enterprise storage systems are increasingly incorporating MRAM as cache memory or buffer storage, leveraging its fast write speeds and endurance. The aerospace and defense sectors value MRAM for its radiation hardness and reliability in extreme environments, creating a premium market segment with specific technical requirements regarding read disturb immunity.

Market research indicates that addressing read disturb issues in high-density arrays could unlock an additional 35% market share in data center applications, where reliability is paramount. Current customer pain points center around the trade-off between density and read disturb vulnerability, with many enterprise customers willing to pay a 15-20% premium for solutions that effectively mitigate this issue.

Regional analysis shows North America leading the MRAM market with approximately 42% share, followed by Asia-Pacific at 38%, which is growing at the fastest rate due to expanding semiconductor manufacturing capabilities in Taiwan, South Korea, and China. Europe accounts for about 17% of the market, with particular strength in automotive and industrial applications.

The competitive landscape features both established semiconductor giants and specialized memory manufacturers. Major players include Samsung Electronics, Everspin Technologies, Honeywell, Avalanche Technology, and Spin Memory. These companies are actively investing in R&D to address technical challenges like read disturb, with patent filings related to this specific issue increasing by 47% over the past three years.

Customer surveys reveal that while performance and density remain primary purchasing factors, reliability metrics including read disturb immunity are becoming increasingly important decision criteria, especially for mission-critical applications. This trend suggests that technical innovations addressing read disturb challenges will likely command market premium and could reshape competitive positioning in the high-density MRAM landscape.

High-density MRAM solutions are particularly gaining traction in several key market segments. The automotive sector represents one of the fastest-growing application areas, with demand for reliable, high-temperature memory solutions for advanced driver assistance systems (ADAS) and autonomous driving technologies. The industrial IoT sector is another significant market, where MRAM's low power consumption and data retention capabilities make it ideal for edge computing devices and sensors.

Enterprise storage systems are increasingly incorporating MRAM as cache memory or buffer storage, leveraging its fast write speeds and endurance. The aerospace and defense sectors value MRAM for its radiation hardness and reliability in extreme environments, creating a premium market segment with specific technical requirements regarding read disturb immunity.

Market research indicates that addressing read disturb issues in high-density arrays could unlock an additional 35% market share in data center applications, where reliability is paramount. Current customer pain points center around the trade-off between density and read disturb vulnerability, with many enterprise customers willing to pay a 15-20% premium for solutions that effectively mitigate this issue.

Regional analysis shows North America leading the MRAM market with approximately 42% share, followed by Asia-Pacific at 38%, which is growing at the fastest rate due to expanding semiconductor manufacturing capabilities in Taiwan, South Korea, and China. Europe accounts for about 17% of the market, with particular strength in automotive and industrial applications.

The competitive landscape features both established semiconductor giants and specialized memory manufacturers. Major players include Samsung Electronics, Everspin Technologies, Honeywell, Avalanche Technology, and Spin Memory. These companies are actively investing in R&D to address technical challenges like read disturb, with patent filings related to this specific issue increasing by 47% over the past three years.

Customer surveys reveal that while performance and density remain primary purchasing factors, reliability metrics including read disturb immunity are becoming increasingly important decision criteria, especially for mission-critical applications. This trend suggests that technical innovations addressing read disturb challenges will likely command market premium and could reshape competitive positioning in the high-density MRAM landscape.

Read Disturb Challenges in Current MRAM Arrays

Read disturb is a critical reliability challenge in high-density MRAM (Magnetoresistive Random Access Memory) arrays that has become increasingly prominent as storage densities continue to scale upward. This phenomenon occurs when repeated read operations to a specific memory cell inadvertently affect the magnetic state of adjacent unselected cells, potentially causing data corruption. The fundamental mechanism behind read disturb involves the application of read currents that generate magnetic fields strong enough to partially switch or destabilize neighboring bit states.

In current high-density MRAM implementations, particularly in STT-MRAM (Spin-Transfer Torque MRAM) and SOT-MRAM (Spin-Orbit Torque MRAM) architectures, the reduction of cell size to achieve higher densities has exacerbated read disturb vulnerabilities. As cell dimensions shrink below 40nm, the thermal stability factor (Δ) of the free layer decreases, making cells more susceptible to thermal fluctuations and external magnetic influences during read operations.

Industry measurements indicate that in advanced MRAM arrays with densities exceeding 4Gb, read disturb error rates can reach 10^-6 after approximately 10^8 read cycles to adjacent cells. This represents a significant reliability concern for applications requiring data retention periods of 10+ years, such as automotive and industrial storage systems.

The physical proximity of cells in high-density arrays creates a complex electromagnetic environment where read currents flowing through bit and word lines generate stray fields that can affect multiple neighboring cells simultaneously. This cross-cell interference becomes more pronounced as the spacing between cells decreases, creating a fundamental scaling challenge for MRAM technology.

Current sensing schemes further compound the read disturb issue. Conventional sensing circuits require relatively high read currents (typically 20-50μA) to achieve acceptable signal-to-noise ratios, but these currents generate proportionally stronger disturb fields. The trade-off between sensing margin and read disturb immunity represents a significant design challenge in modern MRAM arrays.

Material limitations also contribute to read disturb vulnerability. The magnetic materials used in current MRAM cells exhibit variations in coercivity and switching behavior, creating a distribution of cells with different susceptibilities to read disturb effects. This variability complicates mitigation strategies and necessitates conservative design approaches that limit overall array performance.

Temperature effects further intensify read disturb challenges, with elevated operating temperatures (85°C+) reducing the energy barrier for magnetization switching by 15-30%, making cells significantly more vulnerable to disturb events. This temperature sensitivity creates additional reliability concerns for applications in harsh environments or with variable thermal conditions.

In current high-density MRAM implementations, particularly in STT-MRAM (Spin-Transfer Torque MRAM) and SOT-MRAM (Spin-Orbit Torque MRAM) architectures, the reduction of cell size to achieve higher densities has exacerbated read disturb vulnerabilities. As cell dimensions shrink below 40nm, the thermal stability factor (Δ) of the free layer decreases, making cells more susceptible to thermal fluctuations and external magnetic influences during read operations.

Industry measurements indicate that in advanced MRAM arrays with densities exceeding 4Gb, read disturb error rates can reach 10^-6 after approximately 10^8 read cycles to adjacent cells. This represents a significant reliability concern for applications requiring data retention periods of 10+ years, such as automotive and industrial storage systems.

The physical proximity of cells in high-density arrays creates a complex electromagnetic environment where read currents flowing through bit and word lines generate stray fields that can affect multiple neighboring cells simultaneously. This cross-cell interference becomes more pronounced as the spacing between cells decreases, creating a fundamental scaling challenge for MRAM technology.

Current sensing schemes further compound the read disturb issue. Conventional sensing circuits require relatively high read currents (typically 20-50μA) to achieve acceptable signal-to-noise ratios, but these currents generate proportionally stronger disturb fields. The trade-off between sensing margin and read disturb immunity represents a significant design challenge in modern MRAM arrays.

Material limitations also contribute to read disturb vulnerability. The magnetic materials used in current MRAM cells exhibit variations in coercivity and switching behavior, creating a distribution of cells with different susceptibilities to read disturb effects. This variability complicates mitigation strategies and necessitates conservative design approaches that limit overall array performance.

Temperature effects further intensify read disturb challenges, with elevated operating temperatures (85°C+) reducing the energy barrier for magnetization switching by 15-30%, making cells significantly more vulnerable to disturb events. This temperature sensitivity creates additional reliability concerns for applications in harsh environments or with variable thermal conditions.

Current Read Disturb Reduction Approaches

01 Read disturb mitigation techniques in MRAM

Various techniques are employed to mitigate read disturb issues in MRAM devices. These include optimizing read current levels, implementing reference cell designs, and using specialized sensing circuits that minimize stress on memory cells during read operations. These approaches help maintain data integrity by reducing the probability of unintentional state changes during repeated read operations.- Read disturb mitigation techniques in MRAM: Various techniques are employed to mitigate read disturb issues in MRAM devices. These include optimizing read current levels, implementing reference cell designs, and using specialized sensing circuits that minimize stress on memory cells during read operations. These approaches help maintain data integrity by reducing the probability of unintentional bit flipping during repeated read operations.

- MRAM cell structure modifications for read disturb resistance: Structural modifications to MRAM cells can enhance resistance to read disturb effects. These include optimized magnetic tunnel junction (MTJ) designs, improved free layer materials, and enhanced pinning mechanisms. By engineering the physical structure of memory cells, manufacturers can create more robust MRAM devices that maintain data integrity even under frequent read operations.

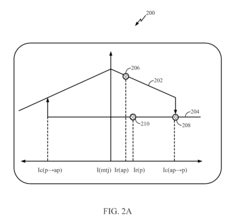

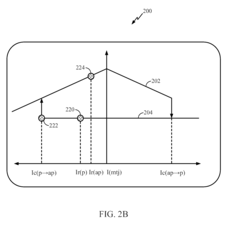

- Read operation control schemes for MRAM: Specialized control schemes for read operations help minimize read disturb effects in MRAM. These include adaptive read timing, variable bias voltage techniques, and intelligent read sequence management. By carefully controlling how read operations are performed, these schemes reduce stress on memory cells while maintaining fast and reliable data access.

- Error detection and correction for MRAM read disturb: Error detection and correction mechanisms are implemented to address read disturb issues in MRAM. These include specialized error correction codes (ECC), parity checking systems, and data refresh protocols that can identify and correct errors caused by read disturb events. These techniques help maintain data integrity in MRAM systems even when physical disturbances occur.

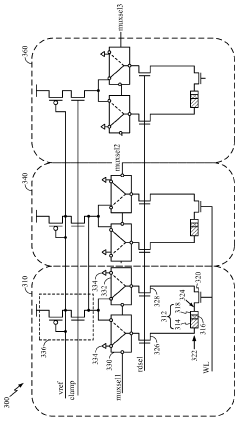

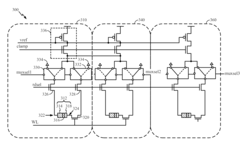

- Circuit-level solutions for MRAM read disturb: Circuit-level innovations help address read disturb challenges in MRAM devices. These include specialized sense amplifiers, reference voltage generators, and read path optimizations that minimize electrical stress on memory cells. By implementing these circuit techniques, MRAM systems can achieve better reliability and endurance while maintaining high-speed operation.

02 MRAM cell structure modifications for read disturb resistance

Structural modifications to MRAM cells can enhance resistance to read disturb effects. These include optimized magnetic tunnel junction (MTJ) designs, improved free layer materials, and enhanced pinning mechanisms. By modifying the physical structure of memory cells, manufacturers can create more robust MRAM devices that maintain data integrity even under frequent read operations.Expand Specific Solutions03 Read operation control schemes for MRAM

Specialized control schemes for read operations help prevent read disturb in MRAM devices. These include adaptive read timing, variable bias voltage techniques, and intelligent read sequence management. By carefully controlling how read operations are performed, these schemes minimize stress on memory cells while maintaining reliable data access.Expand Specific Solutions04 Circuit-level solutions for read disturb prevention

Circuit-level approaches address read disturb issues through specialized sensing amplifiers, reference voltage generators, and compensating circuits. These designs help maintain appropriate read margins while minimizing electrical stress on memory cells. By implementing these circuit solutions, MRAM devices can achieve better reliability during repeated read operations.Expand Specific Solutions05 System-level management of read disturb effects

System-level strategies manage read disturb effects through error correction codes, wear-leveling algorithms, and intelligent memory management. These approaches distribute read operations across the memory array and implement detection and correction mechanisms for potential errors. By addressing read disturb at the system level, these techniques extend the operational lifetime and reliability of MRAM devices.Expand Specific Solutions

Leading MRAM Manufacturers and Research Institutions

The MRAM read disturb reduction market is in an early growth phase, characterized by increasing investments as high-density MRAM emerges as a promising non-volatile memory solution. The market is projected to expand significantly with the growing demand for reliable, high-performance memory in data centers, automotive, and IoT applications. Technologically, solutions are still evolving, with major semiconductor players at different maturity levels. Companies like Samsung, Intel, and TSMC lead in advanced manufacturing processes, while Micron, SK hynix, and KIOXIA are making significant R&D investments. Specialized firms like Everspin Technologies are developing proprietary techniques, while research collaborations between companies like Qualcomm, ARM, and academic institutions are accelerating innovation in circuit design and materials to mitigate read disturb effects in high-density arrays.

Infineon Technologies AG

Technical Solution: Infineon has pioneered a segmented bit-line architecture specifically designed to address read disturb issues in high-density MRAM arrays. Their approach divides the memory array into smaller segments with dedicated sense amplifiers, significantly reducing the parasitic capacitance and resistance of bit lines during read operations. This segmentation allows for lower read currents while maintaining sufficient sensing margins, directly addressing the root cause of read disturb phenomena. Infineon's technology incorporates a proprietary "stepped read" technique that gradually increases sensing current until reliable detection occurs, rather than immediately applying maximum read current. This minimizes unnecessary exposure of cells to high current levels. Their solution also features an adaptive refresh mechanism that tracks read access patterns and proactively refreshes potentially vulnerable cells before disturb effects accumulate to critical levels. Infineon has further enhanced their technology with specialized shielding structures between adjacent cells that reduce magnetic field interference during read operations, providing an additional layer of protection against read disturb in densely packed arrays.

Strengths: Infineon's segmented architecture significantly reduces read disturb without sacrificing access speed, making it ideal for high-performance applications. Their solution demonstrates excellent reliability in high-temperature environments where MRAM read disturb issues typically worsen. Weaknesses: The segmented approach requires additional area overhead for sense amplifiers and control circuitry, potentially limiting the maximum achievable density compared to competing solutions. Implementation complexity is also higher, requiring more sophisticated manufacturing processes.

Micron Technology, Inc.

Technical Solution: Micron has developed a comprehensive approach to reduce read disturb in high-density MRAM arrays through their Spin Transfer Torque MRAM (STT-MRAM) technology. Their solution implements a reference cell architecture that dynamically adjusts reference voltages during read operations to minimize the current passing through non-selected cells. This architecture incorporates specialized sensing circuits that can detect minimal resistance changes while applying lower read voltages, significantly reducing the probability of disturbing adjacent cells. Micron's technology also employs a time-division multiplexing scheme for read operations that limits the duration of read current exposure to any single memory cell, thereby reducing cumulative disturb effects. Additionally, they've implemented advanced error correction code (ECC) algorithms specifically optimized for MRAM error patterns to detect and correct errors caused by read disturb events before they propagate into system-level failures. Their most recent implementations include thermal-assisted writing techniques that improve selectivity during operations, further reducing the likelihood of disturbing neighboring cells during intensive read cycles.

Strengths: Micron's approach offers excellent scalability for high-density arrays while maintaining data integrity. Their solution requires minimal additional circuitry compared to competitors, resulting in smaller die size and lower manufacturing costs. Weaknesses: The dynamic reference voltage adjustment introduces additional latency to read operations, potentially impacting performance in time-sensitive applications. The solution also requires more complex control logic, increasing power consumption during read operations.

Key Patents and Innovations in MRAM Read Stability

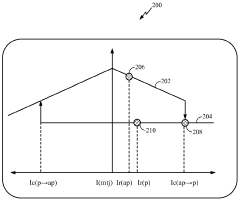

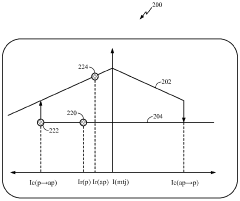

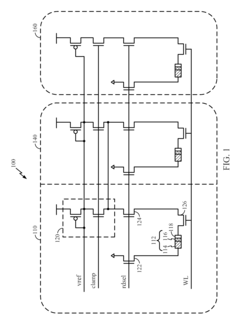

Magnetic random access memory (MRAM) read with reduced disturb failure

PatentWO2012116375A1

Innovation

- The implementation of multiplexers to control the direction of current flow through magnetic tunnel junctions, alternating or selecting the direction based on the orientation of the free and fixed layers, reduces the occurrence of read disturb events by minimizing the number of times current flows through the junction in a direction that causes disturbance.

Magnetic random access memory (MRAM) read with reduced disturb failure

PatentActiveUS8570797B2

Innovation

- The implementation of multiplexers to control the direction of current flow through magnetic tunnel junctions, alternating the direction of current flow based on the orientation of the free and fixed layers in reference and data MTJs, reduces the occurrence of read disturb events by minimizing the number of times current flows through the junction in directions that cause disturbances.

Material Science Advancements for MRAM Stability

Recent advancements in material science have opened promising pathways to address read disturb issues in high-density MRAM arrays. The development of novel magnetic materials with enhanced thermal stability and reduced susceptibility to stray magnetic fields represents a significant breakthrough. Specifically, synthetic antiferromagnetic (SAF) structures have demonstrated superior resistance to read disturb phenomena by minimizing the impact of thermal fluctuations on the magnetic tunnel junction (MTJ) elements.

Perpendicular magnetic anisotropy (PMA) materials have emerged as particularly valuable for MRAM stability. These materials enable the magnetic moment to orient perpendicular to the film plane, resulting in higher thermal stability factors and improved resistance to read disturb effects. Recent research has shown that CoFeB-MgO interfaces with carefully engineered thickness ratios can achieve PMA values exceeding 107 erg/cm³, substantially enhancing the robustness of MRAM cells against read disturb.

The incorporation of rare earth elements such as Tb and Gd into magnetic layers has demonstrated promising results in laboratory settings. These elements contribute to increased magnetic damping, which reduces susceptibility to spin-transfer torque effects during read operations. Studies indicate that Tb-doped CoFeB free layers exhibit up to 40% improvement in read disturb immunity compared to conventional compositions.

Multilayer heterostructures represent another significant advancement, where alternating ultra-thin layers of different materials create quantum confinement effects that enhance magnetic stability. For instance, [Co/Pt]n and [Co/Pd]n multilayers have shown exceptional PMA properties and resistance to thermal fluctuations, making them excellent candidates for next-generation MRAM technologies.

Interface engineering has proven critical in improving MRAM stability. Recent developments in atomic layer deposition techniques allow for precise control of the MgO tunnel barrier thickness and crystallinity, resulting in more uniform resistance distributions across MRAM arrays and reduced susceptibility to read disturb events. The introduction of insertion layers, such as Ta or Ru, between the magnetic layers and the tunnel barrier has been shown to enhance the quality of the interfaces and improve overall device performance.

Emerging materials such as Heusler alloys (particularly Co2FeAl and Co2MnSi) show promise due to their high spin polarization and intrinsic stability. These materials could potentially enable MRAM devices with significantly reduced read current requirements, thereby minimizing the risk of read disturb while maintaining reliable sensing margins.

Perpendicular magnetic anisotropy (PMA) materials have emerged as particularly valuable for MRAM stability. These materials enable the magnetic moment to orient perpendicular to the film plane, resulting in higher thermal stability factors and improved resistance to read disturb effects. Recent research has shown that CoFeB-MgO interfaces with carefully engineered thickness ratios can achieve PMA values exceeding 107 erg/cm³, substantially enhancing the robustness of MRAM cells against read disturb.

The incorporation of rare earth elements such as Tb and Gd into magnetic layers has demonstrated promising results in laboratory settings. These elements contribute to increased magnetic damping, which reduces susceptibility to spin-transfer torque effects during read operations. Studies indicate that Tb-doped CoFeB free layers exhibit up to 40% improvement in read disturb immunity compared to conventional compositions.

Multilayer heterostructures represent another significant advancement, where alternating ultra-thin layers of different materials create quantum confinement effects that enhance magnetic stability. For instance, [Co/Pt]n and [Co/Pd]n multilayers have shown exceptional PMA properties and resistance to thermal fluctuations, making them excellent candidates for next-generation MRAM technologies.

Interface engineering has proven critical in improving MRAM stability. Recent developments in atomic layer deposition techniques allow for precise control of the MgO tunnel barrier thickness and crystallinity, resulting in more uniform resistance distributions across MRAM arrays and reduced susceptibility to read disturb events. The introduction of insertion layers, such as Ta or Ru, between the magnetic layers and the tunnel barrier has been shown to enhance the quality of the interfaces and improve overall device performance.

Emerging materials such as Heusler alloys (particularly Co2FeAl and Co2MnSi) show promise due to their high spin polarization and intrinsic stability. These materials could potentially enable MRAM devices with significantly reduced read current requirements, thereby minimizing the risk of read disturb while maintaining reliable sensing margins.

Reliability Testing Methodologies for MRAM Arrays

Reliability testing for MRAM arrays requires comprehensive methodologies to ensure robust performance in high-density configurations. Standard testing protocols include endurance cycling, data retention testing, and read disturb evaluation, which must be conducted under various environmental conditions to simulate real-world operational scenarios.

The read disturb phenomenon in MRAM presents unique testing challenges that necessitate specialized approaches. Accelerated testing methods involve applying elevated voltages or currents during read operations to induce potential failures more rapidly than would occur under normal operating conditions. These tests typically employ statistical sampling across multiple array locations to ensure comprehensive coverage of potential vulnerability points.

Temperature-dependent testing forms a critical component of MRAM reliability assessment. Tests conducted across temperature ranges from -40°C to 125°C help identify thermal sensitivity in read operations and potential exacerbation of read disturb effects at temperature extremes. This data enables the development of temperature compensation mechanisms in sensing circuits.

Radiation testing has emerged as an essential methodology for applications in aerospace and other radiation-exposed environments. Single-event upset (SEU) and total ionizing dose (TID) tests evaluate MRAM's susceptibility to radiation-induced read errors and disturb events, providing crucial data for hardening designs against these environmental factors.

Advanced statistical analysis techniques are employed to process test results, including Weibull distribution analysis for failure prediction and Monte Carlo simulations to model read disturb propagation through arrays. These analytical approaches help establish meaningful metrics for comparing different MRAM designs and manufacturing processes.

Industry-standard test equipment configurations typically include specialized MRAM testers with precise current control capabilities, environmental chambers for temperature variation, and custom test boards designed to isolate read disturb effects from other potential failure mechanisms. The testing setup must be capable of detecting subtle changes in resistance values that may indicate the early onset of read disturb issues.

Correlation studies between accelerated testing and real-time aging tests are essential for validating the predictive value of reliability models. These studies typically involve long-term monitoring of reference arrays under normal operating conditions compared against arrays subjected to accelerated stress testing, establishing conversion factors between accelerated and real-time failure rates.

The read disturb phenomenon in MRAM presents unique testing challenges that necessitate specialized approaches. Accelerated testing methods involve applying elevated voltages or currents during read operations to induce potential failures more rapidly than would occur under normal operating conditions. These tests typically employ statistical sampling across multiple array locations to ensure comprehensive coverage of potential vulnerability points.

Temperature-dependent testing forms a critical component of MRAM reliability assessment. Tests conducted across temperature ranges from -40°C to 125°C help identify thermal sensitivity in read operations and potential exacerbation of read disturb effects at temperature extremes. This data enables the development of temperature compensation mechanisms in sensing circuits.

Radiation testing has emerged as an essential methodology for applications in aerospace and other radiation-exposed environments. Single-event upset (SEU) and total ionizing dose (TID) tests evaluate MRAM's susceptibility to radiation-induced read errors and disturb events, providing crucial data for hardening designs against these environmental factors.

Advanced statistical analysis techniques are employed to process test results, including Weibull distribution analysis for failure prediction and Monte Carlo simulations to model read disturb propagation through arrays. These analytical approaches help establish meaningful metrics for comparing different MRAM designs and manufacturing processes.

Industry-standard test equipment configurations typically include specialized MRAM testers with precise current control capabilities, environmental chambers for temperature variation, and custom test boards designed to isolate read disturb effects from other potential failure mechanisms. The testing setup must be capable of detecting subtle changes in resistance values that may indicate the early onset of read disturb issues.

Correlation studies between accelerated testing and real-time aging tests are essential for validating the predictive value of reliability models. These studies typically involve long-term monitoring of reference arrays under normal operating conditions compared against arrays subjected to accelerated stress testing, establishing conversion factors between accelerated and real-time failure rates.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!