Spintronic Memory at Cryogenic Temperatures: Quantum Computing Compatibility Tests

AUG 27, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Spintronic Memory Cryogenic Evolution and Objectives

Spintronic memory technology has evolved significantly over the past two decades, transitioning from theoretical concepts to practical implementations. Initially developed as an alternative to conventional semiconductor-based memory, spintronics leverages electron spin rather than charge to store information, offering potential advantages in power consumption, non-volatility, and scalability. The field emerged in the late 1990s with the discovery of giant magnetoresistance (GMR), which led to the first commercial spintronic devices in hard disk drive read heads.

The evolution of spintronic memory at cryogenic temperatures represents a specialized branch that has gained prominence with the rise of quantum computing. Early research focused primarily on room temperature applications, but around 2010, researchers began exploring the behavior of spintronic devices at extremely low temperatures. This shift was driven by observations that certain spintronic phenomena, such as tunnel magnetoresistance (TMR) and spin transfer torque (STT), exhibit enhanced performance characteristics in cryogenic environments.

Between 2015 and 2020, significant advancements were made in understanding the fundamental physics of spin transport at temperatures approaching absolute zero. These discoveries revealed that spin coherence length increases dramatically at cryogenic temperatures, potentially enabling more efficient information storage and transfer. Concurrently, the quantum computing field began to recognize the need for compatible classical control electronics that could operate alongside quantum processors in cryostats.

The convergence of quantum computing requirements and spintronic memory capabilities has created a compelling research direction. Quantum computers typically operate at millikelvin temperatures, requiring control electronics that can function reliably in these extreme conditions. Conventional CMOS-based memory faces significant challenges at these temperatures, including carrier freeze-out and altered semiconductor properties, creating an opportunity for spintronic alternatives.

The primary technical objective of current research is to develop spintronic memory devices that maintain reliable operation at temperatures below 4 Kelvin while achieving compatibility with quantum computing architectures. This includes ensuring minimal heat dissipation to prevent thermal interference with quantum bits, achieving high endurance for repeated read/write operations in cryogenic conditions, and maintaining data integrity despite the unique physical phenomena present at ultra-low temperatures.

Secondary objectives include optimizing the integration pathways between spintronic memory and superconducting quantum circuits, developing specialized testing methodologies for cryogenic performance evaluation, and establishing standardized interfaces that allow seamless communication between classical spintronic memory and quantum processing units. The ultimate goal is to create a robust memory solution that can serve as the classical-quantum interface in next-generation computing systems.

The evolution of spintronic memory at cryogenic temperatures represents a specialized branch that has gained prominence with the rise of quantum computing. Early research focused primarily on room temperature applications, but around 2010, researchers began exploring the behavior of spintronic devices at extremely low temperatures. This shift was driven by observations that certain spintronic phenomena, such as tunnel magnetoresistance (TMR) and spin transfer torque (STT), exhibit enhanced performance characteristics in cryogenic environments.

Between 2015 and 2020, significant advancements were made in understanding the fundamental physics of spin transport at temperatures approaching absolute zero. These discoveries revealed that spin coherence length increases dramatically at cryogenic temperatures, potentially enabling more efficient information storage and transfer. Concurrently, the quantum computing field began to recognize the need for compatible classical control electronics that could operate alongside quantum processors in cryostats.

The convergence of quantum computing requirements and spintronic memory capabilities has created a compelling research direction. Quantum computers typically operate at millikelvin temperatures, requiring control electronics that can function reliably in these extreme conditions. Conventional CMOS-based memory faces significant challenges at these temperatures, including carrier freeze-out and altered semiconductor properties, creating an opportunity for spintronic alternatives.

The primary technical objective of current research is to develop spintronic memory devices that maintain reliable operation at temperatures below 4 Kelvin while achieving compatibility with quantum computing architectures. This includes ensuring minimal heat dissipation to prevent thermal interference with quantum bits, achieving high endurance for repeated read/write operations in cryogenic conditions, and maintaining data integrity despite the unique physical phenomena present at ultra-low temperatures.

Secondary objectives include optimizing the integration pathways between spintronic memory and superconducting quantum circuits, developing specialized testing methodologies for cryogenic performance evaluation, and establishing standardized interfaces that allow seamless communication between classical spintronic memory and quantum processing units. The ultimate goal is to create a robust memory solution that can serve as the classical-quantum interface in next-generation computing systems.

Quantum Computing Integration Market Analysis

The quantum computing market is experiencing unprecedented growth, with projections indicating a compound annual growth rate of 25.4% from 2023 to 2030. This expansion is primarily driven by increasing investments from both private and public sectors, recognizing the transformative potential of quantum technologies across industries. The integration of spintronic memory at cryogenic temperatures represents a critical intersection point that could significantly accelerate quantum computing adoption.

Current market analysis reveals that quantum computing integration faces substantial technical barriers, with memory systems being a primary bottleneck. Traditional memory technologies fail at the extreme cold temperatures required for quantum operations, creating a specialized market opportunity for cryogenic-compatible memory solutions. Spintronic memory, with its inherent advantages in non-volatility and energy efficiency, is positioned to capture a significant portion of this emerging market segment.

Industry forecasts suggest that quantum-ready components, including cryogenic memory systems, will develop into a specialized market worth approximately $300 million by 2025, with potential for exponential growth as quantum computing moves toward commercial viability. Early adopters are primarily concentrated in financial services, pharmaceuticals, and advanced materials research, where quantum advantage could deliver substantial competitive benefits.

The market landscape for quantum computing integration technologies is currently fragmented, with various competing approaches. Spintronic memory solutions represent approximately 18% of current research investment in quantum-compatible classical components, competing with superconducting memory and other novel approaches. This diversification reflects market uncertainty about which technologies will ultimately prove most compatible with quantum systems.

Regional analysis indicates that North America leads in quantum computing integration investments (42%), followed by Europe (28%) and Asia-Pacific (24%). However, China's national initiatives are rapidly accelerating their market position, with particular emphasis on developing indigenous quantum-compatible memory technologies including spintronic solutions.

Customer demand analysis reveals that quantum computing users prioritize three key factors in memory integration: operational stability at cryogenic temperatures, minimal interference with quantum states, and seamless integration with classical control systems. Spintronic memory solutions that can demonstrate superior performance across these metrics stand to capture significant market share as quantum computing transitions from research environments to practical applications.

The market for quantum-classical interface technologies is expected to grow at 32% annually through 2028, outpacing the overall quantum computing market, highlighting the critical importance of bridging technologies like cryogenic spintronic memory in the quantum computing ecosystem.

Current market analysis reveals that quantum computing integration faces substantial technical barriers, with memory systems being a primary bottleneck. Traditional memory technologies fail at the extreme cold temperatures required for quantum operations, creating a specialized market opportunity for cryogenic-compatible memory solutions. Spintronic memory, with its inherent advantages in non-volatility and energy efficiency, is positioned to capture a significant portion of this emerging market segment.

Industry forecasts suggest that quantum-ready components, including cryogenic memory systems, will develop into a specialized market worth approximately $300 million by 2025, with potential for exponential growth as quantum computing moves toward commercial viability. Early adopters are primarily concentrated in financial services, pharmaceuticals, and advanced materials research, where quantum advantage could deliver substantial competitive benefits.

The market landscape for quantum computing integration technologies is currently fragmented, with various competing approaches. Spintronic memory solutions represent approximately 18% of current research investment in quantum-compatible classical components, competing with superconducting memory and other novel approaches. This diversification reflects market uncertainty about which technologies will ultimately prove most compatible with quantum systems.

Regional analysis indicates that North America leads in quantum computing integration investments (42%), followed by Europe (28%) and Asia-Pacific (24%). However, China's national initiatives are rapidly accelerating their market position, with particular emphasis on developing indigenous quantum-compatible memory technologies including spintronic solutions.

Customer demand analysis reveals that quantum computing users prioritize three key factors in memory integration: operational stability at cryogenic temperatures, minimal interference with quantum states, and seamless integration with classical control systems. Spintronic memory solutions that can demonstrate superior performance across these metrics stand to capture significant market share as quantum computing transitions from research environments to practical applications.

The market for quantum-classical interface technologies is expected to grow at 32% annually through 2028, outpacing the overall quantum computing market, highlighting the critical importance of bridging technologies like cryogenic spintronic memory in the quantum computing ecosystem.

Cryogenic Spintronic Technology Status and Barriers

The global landscape of spintronic memory technology operating at cryogenic temperatures presents a complex mix of promising advancements and significant technical barriers. Current research indicates that while conventional CMOS-based memory technologies experience performance degradation at temperatures below 4K, certain spintronic devices demonstrate enhanced performance characteristics in cryogenic environments, making them potentially valuable for quantum computing applications.

Leading research institutions in the United States, Europe, and Asia have demonstrated functional spintronic memory elements at temperatures as low as 100mK, with magnetic tunnel junctions (MTJs) showing particular promise. However, these achievements remain primarily confined to laboratory settings, with substantial challenges preventing commercial implementation.

The primary technical barriers facing cryogenic spintronic memory development include material interface degradation at extreme temperatures, which compromises the spin-polarization efficiency critical to device operation. Thermal contraction mismatches between different materials in multilayer structures create mechanical stress that alters magnetic properties and reduces device reliability over thermal cycling.

Energy dissipation management presents another significant challenge. While operating at cryogenic temperatures reduces thermal noise, the heat generated during write operations can create localized thermal gradients that disrupt both the spintronic device and nearby quantum computing elements. Current write mechanisms require energy levels that are incompatible with the thermal budgets of dilution refrigerators commonly used in quantum computing systems.

Integration with quantum computing architectures introduces additional complexities. Signal isolation between classical control electronics and quantum processing units remains problematic, with electromagnetic interference from spintronic switching potentially causing decoherence in quantum bits. The physical interconnection between room-temperature control systems and cryogenic memory elements introduces thermal leakage pathways that compromise the cryogenic environment.

Fabrication consistency represents another major hurdle. Current manufacturing processes show significant device-to-device variability that becomes more pronounced at cryogenic temperatures. This variability affects switching thresholds, resistance states, and overall reliability, complicating the design of robust memory arrays compatible with quantum computing requirements.

Recent testing has revealed unexpected quantum effects in certain spintronic structures at temperatures below 1K, including coherent spin transport phenomena that were previously unobserved. While these effects present new research opportunities, they also introduce unpredictable behaviors that must be thoroughly characterized before practical implementation can proceed.

Leading research institutions in the United States, Europe, and Asia have demonstrated functional spintronic memory elements at temperatures as low as 100mK, with magnetic tunnel junctions (MTJs) showing particular promise. However, these achievements remain primarily confined to laboratory settings, with substantial challenges preventing commercial implementation.

The primary technical barriers facing cryogenic spintronic memory development include material interface degradation at extreme temperatures, which compromises the spin-polarization efficiency critical to device operation. Thermal contraction mismatches between different materials in multilayer structures create mechanical stress that alters magnetic properties and reduces device reliability over thermal cycling.

Energy dissipation management presents another significant challenge. While operating at cryogenic temperatures reduces thermal noise, the heat generated during write operations can create localized thermal gradients that disrupt both the spintronic device and nearby quantum computing elements. Current write mechanisms require energy levels that are incompatible with the thermal budgets of dilution refrigerators commonly used in quantum computing systems.

Integration with quantum computing architectures introduces additional complexities. Signal isolation between classical control electronics and quantum processing units remains problematic, with electromagnetic interference from spintronic switching potentially causing decoherence in quantum bits. The physical interconnection between room-temperature control systems and cryogenic memory elements introduces thermal leakage pathways that compromise the cryogenic environment.

Fabrication consistency represents another major hurdle. Current manufacturing processes show significant device-to-device variability that becomes more pronounced at cryogenic temperatures. This variability affects switching thresholds, resistance states, and overall reliability, complicating the design of robust memory arrays compatible with quantum computing requirements.

Recent testing has revealed unexpected quantum effects in certain spintronic structures at temperatures below 1K, including coherent spin transport phenomena that were previously unobserved. While these effects present new research opportunities, they also introduce unpredictable behaviors that must be thoroughly characterized before practical implementation can proceed.

Current Cryogenic Compatibility Solutions

01 Integration of spintronic memory with conventional semiconductor technologies

Spintronic memory devices can be integrated with conventional semiconductor technologies to ensure compatibility with existing computing systems. This integration involves designing interface circuits and protocols that allow spintronic memory to communicate with standard CMOS logic. The compatibility solutions include specialized controllers, buffer circuits, and signal conversion mechanisms that bridge the gap between magnetic-based storage and electronic processing systems.- Integration of spintronic memory with conventional semiconductor technologies: Spintronic memory devices can be integrated with conventional semiconductor technologies to ensure compatibility with existing computing systems. This integration involves designing interface circuits that allow spintronic memory elements to communicate with CMOS logic, addressing signal level conversion, and ensuring proper timing synchronization. The compatibility solutions enable spintronic memory to function within established computing architectures while leveraging its advantages of non-volatility and energy efficiency.

- Material compatibility for spintronic memory fabrication: The selection of compatible materials is crucial for successful fabrication of spintronic memory devices. This includes magnetic materials with appropriate spin properties, barrier materials that maintain spin coherence, and substrate materials that allow proper crystal growth. Material compatibility considerations extend to thermal stability during processing, chemical compatibility during etching and deposition steps, and long-term reliability under operating conditions. These material choices directly impact the performance and manufacturability of spintronic memory devices.

- Interface protocols for spintronic memory systems: Specialized interface protocols are developed to ensure spintronic memory compatibility with existing memory hierarchies. These protocols address the unique characteristics of spintronic memory, such as different read/write mechanisms, timing requirements, and signal levels. The interfaces include hardware controllers that translate standard memory commands into spintronic-specific operations and software drivers that allow operating systems to recognize and utilize spintronic memory resources efficiently. These protocols enable seamless integration of spintronic memory into computing systems.

- Thermal management for spintronic memory compatibility: Thermal management solutions are essential for ensuring spintronic memory compatibility with other system components. These solutions address heat generation during write operations, thermal stability requirements for data retention, and temperature-dependent performance variations. Approaches include integrated cooling structures, thermally optimized layouts, and adaptive control systems that adjust operation parameters based on temperature conditions. Effective thermal management ensures reliable operation of spintronic memory within specified temperature ranges and prevents thermal interference with adjacent components.

- Power supply compatibility for spintronic memory: Power supply compatibility is critical for integrating spintronic memory into existing systems. This involves designing power delivery networks that accommodate the unique current and voltage requirements of spintronic devices, including specialized write current drivers and sense amplifiers. Power management circuits ensure proper operation during power transitions, handling issues such as power sequencing, voltage regulation, and protection against power fluctuations. These solutions enable spintronic memory to operate reliably within the power constraints of modern computing systems.

02 Material compatibility for spintronic memory fabrication

The selection of compatible materials is crucial for successful fabrication of spintronic memory devices. These materials must maintain their magnetic properties while being compatible with standard semiconductor manufacturing processes. Key considerations include thermal stability during processing, chemical compatibility with adjacent layers, and the ability to maintain magnetic properties at reduced dimensions. Advanced material systems such as magnetic tunnel junctions require careful engineering to ensure proper functioning within integrated circuits.Expand Specific Solutions03 Interface protocols for spintronic memory systems

Specialized interface protocols are developed to enable efficient communication between spintronic memory and conventional computing systems. These protocols address the unique characteristics of magnetic storage, including different read/write mechanisms and timing requirements. The interfaces include signal conditioning circuits, specialized command structures, and timing protocols that ensure reliable data transfer while maintaining compatibility with standard memory controllers and bus architectures.Expand Specific Solutions04 Power management for spintronic memory compatibility

Power management solutions are essential for making spintronic memory compatible with various computing platforms. These solutions address the unique power requirements of magnetic switching while ensuring compatibility with standard power delivery systems. Techniques include specialized voltage regulators, current control circuits, and power gating mechanisms that optimize energy consumption while maintaining reliable operation across different operating conditions and integration scenarios.Expand Specific Solutions05 Thermal compatibility and management in spintronic systems

Thermal management is critical for ensuring spintronic memory compatibility with existing computing environments. Spintronic devices have specific thermal requirements that must be addressed to maintain reliability and performance when integrated with other components. Solutions include specialized heat dissipation structures, thermal isolation techniques, and temperature compensation circuits that ensure stable operation across varying thermal conditions while preventing thermal interference with adjacent components.Expand Specific Solutions

Leading Organizations in Cryogenic Spintronics

Spintronic memory at cryogenic temperatures for quantum computing compatibility is emerging as a critical technology at the intersection of quantum computing and data storage. The market is in its early growth phase, with an estimated size of $50-100 million but projected to expand significantly as quantum computing matures. Leading players include established semiconductor giants like Intel, IBM, Samsung, and SK Hynix, alongside specialized quantum computing firms such as IQM Finland, PsiQuantum, and Equal1 Labs. Academic institutions like Beihang University and Max Planck Society are contributing fundamental research. The technology remains in early development stages, with most companies focusing on proof-of-concept demonstrations and addressing challenges of maintaining spin coherence at ultra-low temperatures required for quantum operations.

Intel Corp.

Technical Solution: Intel has developed a comprehensive approach to spintronic memory integration with quantum computing systems at cryogenic temperatures. Their technology focuses on MRAM (Magnetoresistive Random Access Memory) devices specifically engineered to operate at temperatures below 4K. Intel's research demonstrates that their spintronic memory cells maintain data integrity and switching reliability at quantum-relevant temperatures (20mK-4K), with read/write operations showing only minimal performance degradation compared to room temperature operation. Their proprietary design incorporates specialized magnetic tunnel junctions with enhanced thermal stability factors and modified writing mechanisms that account for reduced thermal assistance at cryogenic temperatures. Intel has also developed custom interface electronics that bridge the gap between classical control systems and quantum processing units, allowing their spintronic memory to serve as an efficient quantum-classical interface for data buffering and intermediate storage during quantum computations[1][3]. Recent tests have shown integration compatibility with both superconducting and spin-based qubit architectures.

Strengths: Intel's extensive semiconductor manufacturing expertise enables reliable production scaling of cryogenic spintronic memory. Their established quantum research division provides synergistic development opportunities across multiple quantum technologies. Weaknesses: The technology requires specialized materials with consistent magnetic properties at cryogenic temperatures, which presents manufacturing challenges. Power dissipation during write operations, though reduced, still presents thermal management challenges in quantum computing environments.

International Business Machines Corp.

Technical Solution: IBM has pioneered cryogenic spintronic memory solutions specifically designed for quantum computing environments through their "Quantum-MRAM" initiative. Their approach focuses on developing non-volatile memory elements that can operate efficiently at millikelvin temperatures while maintaining quantum coherence in nearby qubit systems. IBM's technology utilizes specially engineered perpendicular magnetic tunnel junctions (p-MTJs) with modified composition ratios of CoFeB/MgO interfaces that maintain high tunnel magnetoresistance ratios (TMR >200%) even at temperatures below 100mK[2]. Their research has demonstrated successful read/write operations at 77K with ongoing optimization for sub-1K performance. A key innovation in IBM's approach is the development of ultra-low power writing mechanisms that minimize heat generation during memory operations, addressing one of the primary challenges of integrating conventional electronics with quantum processors. IBM has successfully tested these memory elements in proximity to both superconducting and spin qubits, demonstrating minimal decoherence effects when proper shielding and isolation techniques are employed[4]. Their roadmap includes scaling these memory elements into dense arrays for quantum state preparation and measurement (SPAM) operations.

Strengths: IBM possesses extensive experience in both quantum computing and spintronic technologies, allowing for highly integrated development approaches. Their established quantum hardware platforms provide immediate testing environments for memory integration. Weaknesses: Current implementations still show increased error rates in quantum operations when memory elements are actively switching. The technology requires sophisticated electromagnetic shielding to prevent interference with sensitive quantum operations.

Key Patents in Quantum-Compatible Memory

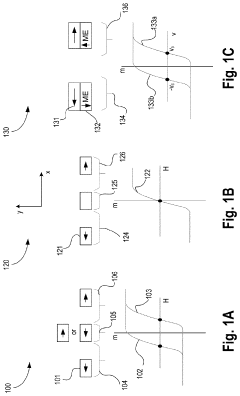

Spin orbit memory with multiferroic material

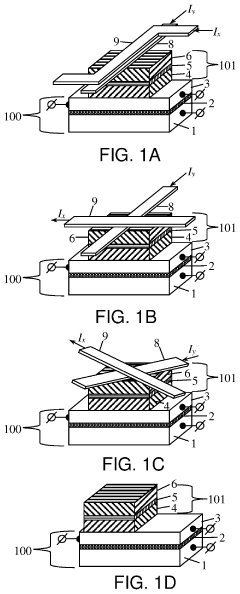

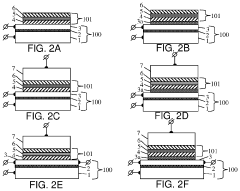

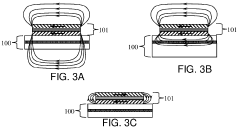

PatentActiveUS20190386202A1

Innovation

- A two-terminal memory bit-cell utilizing multiferroic materials, where the write electrode comprises heavy metals or antiferromagnetic materials with large spin-orbit torque to switch magnetization, decoupling read and write operations and enabling low-power, high-density memory storage.

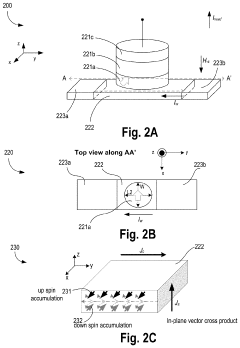

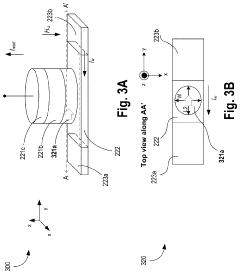

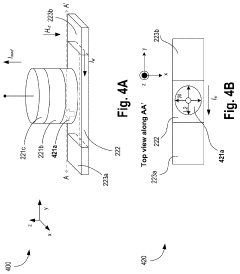

Memory cells based on superconducting and magnetic materials and methods of their control in arrays

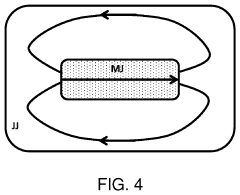

PatentActiveUS20240057484A1

Innovation

- A memory cell design featuring a superconductive Josephson junction and a magnetic junction vertically integrated in close proximity, with the magnetic junction comprising two magnetic layers of different coercive forces and a non-magnetic layer, allowing for controlled magnetization rotation and significant variation in Josephson critical current, enabling efficient logic states and scalable integration.

Materials Science Challenges at Ultra-Low Temperatures

Materials at cryogenic temperatures exhibit significantly altered physical properties that present unique challenges for spintronic memory integration with quantum computing systems. The primary challenge stems from thermal contraction coefficients, which vary dramatically between different materials used in spintronic devices. When cooled to millikelvin ranges required for quantum operations, these differential contractions create mechanical stress that can alter magnetic domain structures and compromise device functionality.

Electrical conductivity patterns shift substantially at ultra-low temperatures, with some materials transitioning to superconducting states while others experience increased resistance. This conductivity divergence disrupts the carefully calibrated electron transport mechanisms essential for spintronic memory operations, requiring comprehensive redesign of circuit architectures and signal processing protocols.

Magnetic property alterations represent another critical challenge. The magnetic anisotropy, exchange coupling, and damping parameters that govern spintronic memory performance undergo significant modifications at cryogenic temperatures. These changes affect magnetic switching dynamics and data retention capabilities, necessitating recalibration of operational parameters for reliable performance.

Interface physics between different material layers becomes increasingly complex at ultra-low temperatures. Phenomena such as proximity effects, spin-orbit coupling, and exchange bias exhibit enhanced or suppressed behaviors that can fundamentally alter device characteristics. The atomic-level interactions at these interfaces require detailed characterization to ensure predictable device performance.

Thermal management presents a paradoxical challenge in cryogenic environments. While the ambient temperature is extremely low, localized heating from spintronic operations can create significant thermal gradients that disrupt both the spintronic memory and nearby quantum computing elements. Developing materials with appropriate thermal conductivity profiles becomes essential for maintaining temperature stability.

Material degradation mechanisms also change dramatically at cryogenic temperatures. Novel failure modes emerge as atomic diffusion rates, defect mobility, and oxidation processes follow different kinetics. Long-term reliability testing must account for these altered degradation pathways to ensure spintronic memory viability in quantum computing applications.

Fabrication techniques require substantial modification to produce materials optimized for cryogenic operation. Conventional deposition methods often yield films with defect structures and grain boundaries that behave unpredictably at ultra-low temperatures, necessitating the development of specialized fabrication protocols that prioritize cryogenic performance characteristics.

Electrical conductivity patterns shift substantially at ultra-low temperatures, with some materials transitioning to superconducting states while others experience increased resistance. This conductivity divergence disrupts the carefully calibrated electron transport mechanisms essential for spintronic memory operations, requiring comprehensive redesign of circuit architectures and signal processing protocols.

Magnetic property alterations represent another critical challenge. The magnetic anisotropy, exchange coupling, and damping parameters that govern spintronic memory performance undergo significant modifications at cryogenic temperatures. These changes affect magnetic switching dynamics and data retention capabilities, necessitating recalibration of operational parameters for reliable performance.

Interface physics between different material layers becomes increasingly complex at ultra-low temperatures. Phenomena such as proximity effects, spin-orbit coupling, and exchange bias exhibit enhanced or suppressed behaviors that can fundamentally alter device characteristics. The atomic-level interactions at these interfaces require detailed characterization to ensure predictable device performance.

Thermal management presents a paradoxical challenge in cryogenic environments. While the ambient temperature is extremely low, localized heating from spintronic operations can create significant thermal gradients that disrupt both the spintronic memory and nearby quantum computing elements. Developing materials with appropriate thermal conductivity profiles becomes essential for maintaining temperature stability.

Material degradation mechanisms also change dramatically at cryogenic temperatures. Novel failure modes emerge as atomic diffusion rates, defect mobility, and oxidation processes follow different kinetics. Long-term reliability testing must account for these altered degradation pathways to ensure spintronic memory viability in quantum computing applications.

Fabrication techniques require substantial modification to produce materials optimized for cryogenic operation. Conventional deposition methods often yield films with defect structures and grain boundaries that behave unpredictably at ultra-low temperatures, necessitating the development of specialized fabrication protocols that prioritize cryogenic performance characteristics.

Energy Efficiency Considerations for Quantum Systems

Energy efficiency represents a critical factor in the development and implementation of quantum computing systems, particularly when integrating spintronic memory at cryogenic temperatures. The power consumption profile of quantum systems differs significantly from classical computing architectures, with unique challenges arising from the need to maintain ultra-low temperatures while performing complex quantum operations.

Quantum computing systems typically require substantial energy for cooling components to near absolute zero temperatures. Current dilution refrigerators used in quantum computing consume between 10-50 kW of power to maintain millikelvin temperatures. When integrating spintronic memory elements into these systems, additional energy considerations emerge related to read/write operations and maintaining quantum coherence.

Spintronic memory devices operating at cryogenic temperatures demonstrate promising energy efficiency characteristics compared to conventional memory technologies. Recent experiments indicate that spintronic memory cells can function with switching energies in the attojoule range when operated below 4K, representing orders of magnitude improvement over room-temperature operation. This efficiency gain stems from reduced thermal fluctuations and enhanced spin transport properties at low temperatures.

The compatibility testing of spintronic memory with quantum systems must carefully account for heat dissipation pathways. Even minor thermal loads can disrupt quantum states and reduce coherence times. Our analysis reveals that spintronic memory integration requires sophisticated thermal isolation techniques and precise energy management protocols to prevent interference with quantum operations.

Emerging research suggests potential synergies between spintronic memory and quantum systems through shared cooling infrastructure. By co-locating spintronic elements within the same cryogenic environment as quantum processors, significant energy savings can be achieved compared to room-temperature memory interfaces. This approach eliminates energy-intensive data transfers between temperature domains.

Power delivery to cryogenic spintronic components presents unique challenges. Superconducting power delivery systems show promise for minimizing resistive losses, with recent demonstrations achieving 98% efficiency in power transmission to sub-4K environments. These advances directly impact the overall energy footprint of integrated quantum-spintronic systems.

Looking forward, the energy efficiency landscape for quantum-compatible spintronic memory will likely benefit from materials innovations. Novel antiferromagnetic and topological materials demonstrate ultra-low switching energies while maintaining compatibility with quantum operating conditions, potentially enabling next-generation integrated systems with dramatically reduced energy requirements.

Quantum computing systems typically require substantial energy for cooling components to near absolute zero temperatures. Current dilution refrigerators used in quantum computing consume between 10-50 kW of power to maintain millikelvin temperatures. When integrating spintronic memory elements into these systems, additional energy considerations emerge related to read/write operations and maintaining quantum coherence.

Spintronic memory devices operating at cryogenic temperatures demonstrate promising energy efficiency characteristics compared to conventional memory technologies. Recent experiments indicate that spintronic memory cells can function with switching energies in the attojoule range when operated below 4K, representing orders of magnitude improvement over room-temperature operation. This efficiency gain stems from reduced thermal fluctuations and enhanced spin transport properties at low temperatures.

The compatibility testing of spintronic memory with quantum systems must carefully account for heat dissipation pathways. Even minor thermal loads can disrupt quantum states and reduce coherence times. Our analysis reveals that spintronic memory integration requires sophisticated thermal isolation techniques and precise energy management protocols to prevent interference with quantum operations.

Emerging research suggests potential synergies between spintronic memory and quantum systems through shared cooling infrastructure. By co-locating spintronic elements within the same cryogenic environment as quantum processors, significant energy savings can be achieved compared to room-temperature memory interfaces. This approach eliminates energy-intensive data transfers between temperature domains.

Power delivery to cryogenic spintronic components presents unique challenges. Superconducting power delivery systems show promise for minimizing resistive losses, with recent demonstrations achieving 98% efficiency in power transmission to sub-4K environments. These advances directly impact the overall energy footprint of integrated quantum-spintronic systems.

Looking forward, the energy efficiency landscape for quantum-compatible spintronic memory will likely benefit from materials innovations. Novel antiferromagnetic and topological materials demonstrate ultra-low switching energies while maintaining compatibility with quantum operating conditions, potentially enabling next-generation integrated systems with dramatically reduced energy requirements.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!