How Will PU Memristive Devices Shape Neuromorphic Circuits?

JUN 25, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

PU Memristors: Background and Objectives

Polyurethane (PU) memristive devices have emerged as a promising technology in the field of neuromorphic computing, offering potential solutions to the limitations of traditional von Neumann architecture. The development of PU memristors can be traced back to the early 2010s when researchers began exploring organic materials for resistive switching applications. Since then, significant progress has been made in understanding the underlying mechanisms and improving device performance.

The primary objective of PU memristor research is to create bio-inspired computing systems that can mimic the efficiency and adaptability of the human brain. These devices aim to bridge the gap between artificial neural networks and biological synapses, potentially revolutionizing the way we approach machine learning and artificial intelligence.

PU memristors offer several advantages over their inorganic counterparts, including flexibility, low-cost fabrication, and biocompatibility. These properties make them particularly attractive for applications in wearable electronics, implantable medical devices, and large-area sensor arrays. The ability to tune the electrical characteristics of PU memristors through chemical modification of the polymer structure provides a wide range of design possibilities for neuromorphic circuits.

The evolution of PU memristor technology has been driven by advancements in materials science, nanotechnology, and neuroscience. Researchers have focused on optimizing the device structure, improving switching characteristics, and enhancing long-term stability. Key milestones include the development of multi-level resistive switching, demonstration of spike-timing-dependent plasticity (STDP), and integration with CMOS technology.

Current technical challenges in PU memristor development include reducing variability between devices, improving retention time, and scaling down device dimensions while maintaining performance. Overcoming these obstacles is crucial for the widespread adoption of PU memristors in practical neuromorphic systems.

Looking ahead, the field of PU memristive devices is expected to continue its rapid growth, with a focus on developing more complex neuromorphic architectures and exploring novel applications. The convergence of PU memristors with other emerging technologies, such as flexible electronics and bioelectronics, may lead to groundbreaking innovations in human-machine interfaces and brain-inspired computing paradigms.

The primary objective of PU memristor research is to create bio-inspired computing systems that can mimic the efficiency and adaptability of the human brain. These devices aim to bridge the gap between artificial neural networks and biological synapses, potentially revolutionizing the way we approach machine learning and artificial intelligence.

PU memristors offer several advantages over their inorganic counterparts, including flexibility, low-cost fabrication, and biocompatibility. These properties make them particularly attractive for applications in wearable electronics, implantable medical devices, and large-area sensor arrays. The ability to tune the electrical characteristics of PU memristors through chemical modification of the polymer structure provides a wide range of design possibilities for neuromorphic circuits.

The evolution of PU memristor technology has been driven by advancements in materials science, nanotechnology, and neuroscience. Researchers have focused on optimizing the device structure, improving switching characteristics, and enhancing long-term stability. Key milestones include the development of multi-level resistive switching, demonstration of spike-timing-dependent plasticity (STDP), and integration with CMOS technology.

Current technical challenges in PU memristor development include reducing variability between devices, improving retention time, and scaling down device dimensions while maintaining performance. Overcoming these obstacles is crucial for the widespread adoption of PU memristors in practical neuromorphic systems.

Looking ahead, the field of PU memristive devices is expected to continue its rapid growth, with a focus on developing more complex neuromorphic architectures and exploring novel applications. The convergence of PU memristors with other emerging technologies, such as flexible electronics and bioelectronics, may lead to groundbreaking innovations in human-machine interfaces and brain-inspired computing paradigms.

Neuromorphic Computing Market Analysis

The neuromorphic computing market is experiencing rapid growth, driven by the increasing demand for artificial intelligence (AI) and machine learning applications across various industries. This market segment is expected to witness significant expansion in the coming years, as neuromorphic computing offers potential solutions to the limitations of traditional von Neumann architecture in handling complex AI tasks.

The global neuromorphic computing market is primarily segmented into hardware and software components. The hardware segment, which includes memristive devices such as PU-based systems, is anticipated to dominate the market due to the growing adoption of neuromorphic chips in edge computing and IoT devices. These chips offer advantages in terms of power efficiency, speed, and adaptability, making them particularly attractive for applications in autonomous vehicles, robotics, and smart sensors.

Key market players in the neuromorphic computing space include Intel Corporation, IBM Corporation, BrainChip Holdings Ltd., and Qualcomm Technologies, Inc. These companies are investing heavily in research and development to advance neuromorphic technologies and gain a competitive edge in the market. Collaborations between academic institutions and industry leaders are also driving innovation in this field.

The adoption of neuromorphic computing is expected to be particularly strong in North America and Europe, where there is a high concentration of technology companies and research institutions. However, the Asia-Pacific region is projected to witness the fastest growth rate, fueled by increasing investments in AI and robotics in countries like China, Japan, and South Korea.

Several factors are contributing to the market's growth potential. The rising need for energy-efficient computing solutions in data centers and edge devices is a significant driver. Additionally, the increasing complexity of AI algorithms and the demand for real-time processing capabilities are pushing the development of neuromorphic systems.

Despite the promising outlook, the neuromorphic computing market faces challenges such as the high initial costs of hardware development and the need for specialized programming paradigms. However, ongoing research in materials science and circuit design, particularly in the area of PU memristive devices, is expected to address these challenges and further accelerate market growth.

As the technology matures, neuromorphic computing is poised to disrupt various industries, including healthcare, finance, and telecommunications. The ability of these systems to process complex sensory data and perform cognitive tasks with high efficiency opens up new possibilities for applications such as advanced prosthetics, financial fraud detection, and natural language processing.

The global neuromorphic computing market is primarily segmented into hardware and software components. The hardware segment, which includes memristive devices such as PU-based systems, is anticipated to dominate the market due to the growing adoption of neuromorphic chips in edge computing and IoT devices. These chips offer advantages in terms of power efficiency, speed, and adaptability, making them particularly attractive for applications in autonomous vehicles, robotics, and smart sensors.

Key market players in the neuromorphic computing space include Intel Corporation, IBM Corporation, BrainChip Holdings Ltd., and Qualcomm Technologies, Inc. These companies are investing heavily in research and development to advance neuromorphic technologies and gain a competitive edge in the market. Collaborations between academic institutions and industry leaders are also driving innovation in this field.

The adoption of neuromorphic computing is expected to be particularly strong in North America and Europe, where there is a high concentration of technology companies and research institutions. However, the Asia-Pacific region is projected to witness the fastest growth rate, fueled by increasing investments in AI and robotics in countries like China, Japan, and South Korea.

Several factors are contributing to the market's growth potential. The rising need for energy-efficient computing solutions in data centers and edge devices is a significant driver. Additionally, the increasing complexity of AI algorithms and the demand for real-time processing capabilities are pushing the development of neuromorphic systems.

Despite the promising outlook, the neuromorphic computing market faces challenges such as the high initial costs of hardware development and the need for specialized programming paradigms. However, ongoing research in materials science and circuit design, particularly in the area of PU memristive devices, is expected to address these challenges and further accelerate market growth.

As the technology matures, neuromorphic computing is poised to disrupt various industries, including healthcare, finance, and telecommunications. The ability of these systems to process complex sensory data and perform cognitive tasks with high efficiency opens up new possibilities for applications such as advanced prosthetics, financial fraud detection, and natural language processing.

PU Memristive Devices: Current State and Challenges

Polyurethane (PU) memristive devices have emerged as a promising technology in the field of neuromorphic computing, offering potential advantages in terms of energy efficiency, scalability, and bio-inspired functionality. However, the current state of PU memristive devices presents both significant advancements and notable challenges that need to be addressed for their widespread adoption in neuromorphic circuits.

One of the primary advantages of PU memristive devices is their ability to emulate synaptic behavior, making them ideal candidates for neuromorphic computing applications. These devices exhibit non-volatile memory characteristics and can be programmed to different conductance states, mimicking the plasticity of biological synapses. This property allows for the implementation of learning algorithms and adaptive behavior in artificial neural networks.

Despite these promising features, PU memristive devices face several technical challenges. One of the most significant issues is the variability in device performance, both between different devices and within the same device over time. This variability can lead to inconsistent behavior in neuromorphic circuits, affecting their reliability and accuracy. Researchers are actively working on improving the uniformity of device characteristics through advanced fabrication techniques and materials engineering.

Another challenge is the limited endurance of PU memristive devices. While they can undergo multiple switching cycles, the number of reliable write operations is still lower than what is required for long-term operation in complex neuromorphic systems. Enhancing the endurance of these devices without compromising their other desirable properties remains an active area of research.

The scalability of PU memristive devices is also a critical consideration. As neuromorphic circuits grow in complexity, the ability to fabricate and integrate large arrays of memristive devices becomes increasingly important. Current fabrication processes need further refinement to achieve the high density and yield required for large-scale neuromorphic systems.

Power consumption is another area where improvements are needed. While PU memristive devices offer advantages in terms of energy efficiency compared to traditional CMOS-based solutions, further reductions in power consumption are necessary to make them viable for widespread use in edge computing and IoT applications.

Lastly, the integration of PU memristive devices with conventional CMOS circuitry presents both opportunities and challenges. Developing efficient interfacing techniques and addressing issues related to signal conversion and amplification are crucial for realizing hybrid neuromorphic systems that can leverage the strengths of both technologies.

In conclusion, while PU memristive devices show great promise for shaping the future of neuromorphic circuits, significant research and development efforts are required to overcome the current challenges and fully realize their potential in practical applications.

One of the primary advantages of PU memristive devices is their ability to emulate synaptic behavior, making them ideal candidates for neuromorphic computing applications. These devices exhibit non-volatile memory characteristics and can be programmed to different conductance states, mimicking the plasticity of biological synapses. This property allows for the implementation of learning algorithms and adaptive behavior in artificial neural networks.

Despite these promising features, PU memristive devices face several technical challenges. One of the most significant issues is the variability in device performance, both between different devices and within the same device over time. This variability can lead to inconsistent behavior in neuromorphic circuits, affecting their reliability and accuracy. Researchers are actively working on improving the uniformity of device characteristics through advanced fabrication techniques and materials engineering.

Another challenge is the limited endurance of PU memristive devices. While they can undergo multiple switching cycles, the number of reliable write operations is still lower than what is required for long-term operation in complex neuromorphic systems. Enhancing the endurance of these devices without compromising their other desirable properties remains an active area of research.

The scalability of PU memristive devices is also a critical consideration. As neuromorphic circuits grow in complexity, the ability to fabricate and integrate large arrays of memristive devices becomes increasingly important. Current fabrication processes need further refinement to achieve the high density and yield required for large-scale neuromorphic systems.

Power consumption is another area where improvements are needed. While PU memristive devices offer advantages in terms of energy efficiency compared to traditional CMOS-based solutions, further reductions in power consumption are necessary to make them viable for widespread use in edge computing and IoT applications.

Lastly, the integration of PU memristive devices with conventional CMOS circuitry presents both opportunities and challenges. Developing efficient interfacing techniques and addressing issues related to signal conversion and amplification are crucial for realizing hybrid neuromorphic systems that can leverage the strengths of both technologies.

In conclusion, while PU memristive devices show great promise for shaping the future of neuromorphic circuits, significant research and development efforts are required to overcome the current challenges and fully realize their potential in practical applications.

Existing PU Memristor-based Neuromorphic Solutions

01 Memristive device structures and materials

PU (Polyurethane) memristive devices utilize specific structures and materials to achieve their functionality. These devices may incorporate various layers, including electrodes, active memristive layers, and insulating layers. The choice of materials and their arrangement plays a crucial role in determining the device's performance characteristics, such as switching behavior and retention.- Memristive device structures and materials: PU memristive devices utilize specific structures and materials to achieve their functionality. These may include novel electrode configurations, active layer compositions, or interface designs that enhance the memristive properties. The devices often incorporate materials that exhibit resistive switching behavior, allowing for controllable and reversible changes in resistance.

- Neuromorphic computing applications: PU memristive devices are being developed for neuromorphic computing applications, mimicking the behavior of biological synapses. These devices can be used to create artificial neural networks, enabling efficient and low-power cognitive computing systems. The ability to continuously adjust their resistance makes them suitable for implementing learning algorithms and pattern recognition tasks.

- Memory and storage applications: PU memristive devices are explored for use in non-volatile memory and data storage applications. Their ability to retain information without power and their potential for high-density integration make them attractive for next-generation memory technologies. These devices can offer faster write speeds, lower power consumption, and improved scalability compared to traditional memory solutions.

- Circuit design and integration: The integration of PU memristive devices into electronic circuits requires specialized design techniques. This includes developing appropriate read and write circuits, addressing schemes, and signal conditioning methods. Researchers are working on optimizing the integration of these devices with conventional CMOS technology to create hybrid systems that leverage the advantages of both technologies.

- Characterization and modeling techniques: Accurate characterization and modeling of PU memristive devices are crucial for their development and application. This involves developing techniques to measure and analyze their electrical characteristics, switching behavior, and reliability. Advanced modeling approaches, including physics-based models and machine learning techniques, are being employed to predict device performance and optimize their design.

02 Neuromorphic computing applications

PU memristive devices are being explored for neuromorphic computing applications. These devices can mimic the behavior of biological synapses, making them suitable for artificial neural networks and brain-inspired computing systems. Their ability to store and process information in a manner similar to biological neurons makes them promising candidates for advanced AI and machine learning hardware.Expand Specific Solutions03 Memory and storage applications

PU memristive devices show potential in memory and storage applications. They can be used to create non-volatile memory cells with high density and low power consumption. These devices offer advantages such as multi-level storage capabilities and resistance to radiation effects, making them suitable for both conventional and specialized memory applications.Expand Specific Solutions04 Circuit design and integration

Integrating PU memristive devices into circuits requires specialized design techniques. This includes developing appropriate read and write circuits, addressing schemes, and signal conditioning circuitry. The unique properties of memristive devices necessitate novel circuit architectures to fully exploit their capabilities and overcome potential challenges such as sneak currents and device variability.Expand Specific Solutions05 Fabrication and manufacturing techniques

The fabrication of PU memristive devices involves specific manufacturing techniques. This may include deposition methods for the various layers, patterning processes, and post-fabrication treatments. Ensuring consistency and reliability in the manufacturing process is crucial for the widespread adoption of these devices in commercial applications.Expand Specific Solutions

Key Players in PU Memristor Development

The development of PU memristive devices for neuromorphic circuits is in its early stages, with significant potential for growth. The market size is expanding as research intensifies, driven by the need for more efficient AI hardware. Companies like IBM, Samsung, and HP are at the forefront of this technology, demonstrating varying levels of technical maturity. IBM has shown advanced capabilities in neuromorphic chip design, while Samsung and SK hynix are leveraging their semiconductor expertise to develop memristive devices. Universities and research institutions, such as Nanjing University of Posts & Telecommunications and Arizona State University, are also contributing to the field's advancement, indicating a collaborative ecosystem that spans academia and industry.

International Business Machines Corp.

Technical Solution: IBM has developed a neuromorphic computing architecture using PU memristive devices. Their approach involves creating artificial synapses and neurons using these devices, which can mimic the behavior of biological neural networks. IBM's system utilizes a crossbar array structure of memristors to perform matrix-vector multiplications efficiently, a key operation in neural network computations. They have also implemented spike-timing-dependent plasticity (STDP) learning rules directly in hardware, allowing for on-chip learning and adaptation.

Strengths: High energy efficiency, potential for scalability, and ability to perform both computation and memory storage in the same device. Weaknesses: Challenges in device variability and long-term stability, complexity in programming and control.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has been working on PU memristive devices for neuromorphic computing, focusing on developing high-density, low-power memory arrays. Their approach involves using metal-oxide based memristors in a crossbar architecture. Samsung has demonstrated the ability to perform in-memory computing using these arrays, where computations are carried out directly within the memory, reducing the need for data movement. They have also explored the use of multi-level cell (MLC) memristors to increase the storage density and computational capabilities of their neuromorphic circuits.

Strengths: Advanced manufacturing capabilities, potential for integration with existing semiconductor technologies. Weaknesses: Challenges in scaling down device size while maintaining performance, need for complex control circuitry.

Core Innovations in PU Memristive Technologies

A novel circuit-based synaptic memristor for neuromorphic computing

PatentPendingIN202141057233A

Innovation

- A simple model of an electronic memristor device with high switching ratio and frequency range is designed, emulating biological synapse behavior through tunable synaptic weight modulation, enabling large-scale, cost-effective fabrication for neuromorphic computing and crossbar architecture.

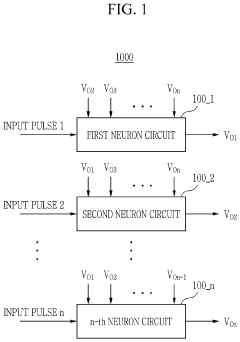

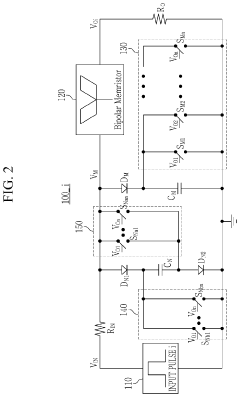

Neuron circuit and operating method thereof

PatentActiveUS11977973B2

Innovation

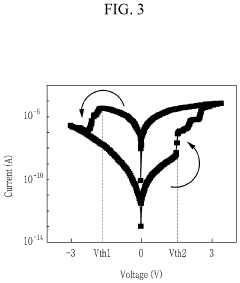

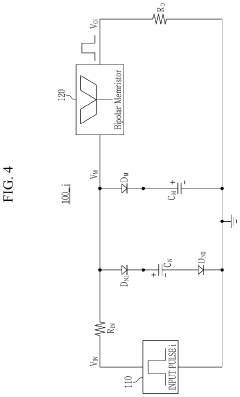

- A neuron circuit design incorporating a bipolar memristor with a positive and negative threshold voltage, utilizing capacitors and switches to apply negative voltage for reset operations, allowing for the implementation of a reset method applicable to both unipolar and bipolar memristors.

Energy Efficiency Impact of PU Memristors

The integration of polyurethane (PU) memristors into neuromorphic circuits represents a significant leap forward in energy efficiency for artificial neural networks. These devices offer a unique combination of low power consumption and high-density storage, making them ideal for emulating synaptic functions in hardware-based neural networks.

PU memristors exhibit remarkably low energy requirements for both read and write operations. Compared to traditional CMOS-based memory technologies, PU memristors can operate at voltages as low as 0.5V, significantly reducing power consumption. This low-voltage operation is particularly crucial in portable and edge computing devices, where battery life is a primary concern.

The non-volatile nature of PU memristors further enhances their energy efficiency. Unlike conventional memory technologies that require constant power to maintain stored information, PU memristors retain their state without the need for continuous refreshing. This characteristic dramatically reduces standby power consumption, a critical factor in always-on neuromorphic systems.

In neuromorphic circuits, PU memristors can implement synaptic weights with analog precision, allowing for more efficient information processing compared to digital implementations. This analog computation capability reduces the energy overhead associated with analog-to-digital and digital-to-analog conversions, which are often necessary in traditional neural network hardware.

The scalability of PU memristors also contributes to their energy efficiency impact. As these devices can be fabricated at extremely small scales, they enable the creation of high-density neural networks with minimal area requirements. This increased density translates to shorter interconnects, reducing signal propagation delays and associated energy losses.

Moreover, the ability of PU memristors to perform in-memory computing eliminates the need for constant data transfer between memory and processing units. This reduction in data movement significantly decreases energy consumption, as data transfer is often one of the most energy-intensive operations in computing systems.

The integration of PU memristors in neuromorphic circuits also enables more efficient implementation of spike-based neural networks. These networks, which more closely mimic biological neural systems, can operate with sparse, event-driven computations, further reducing energy consumption compared to traditional artificial neural networks that require continuous processing.

PU memristors exhibit remarkably low energy requirements for both read and write operations. Compared to traditional CMOS-based memory technologies, PU memristors can operate at voltages as low as 0.5V, significantly reducing power consumption. This low-voltage operation is particularly crucial in portable and edge computing devices, where battery life is a primary concern.

The non-volatile nature of PU memristors further enhances their energy efficiency. Unlike conventional memory technologies that require constant power to maintain stored information, PU memristors retain their state without the need for continuous refreshing. This characteristic dramatically reduces standby power consumption, a critical factor in always-on neuromorphic systems.

In neuromorphic circuits, PU memristors can implement synaptic weights with analog precision, allowing for more efficient information processing compared to digital implementations. This analog computation capability reduces the energy overhead associated with analog-to-digital and digital-to-analog conversions, which are often necessary in traditional neural network hardware.

The scalability of PU memristors also contributes to their energy efficiency impact. As these devices can be fabricated at extremely small scales, they enable the creation of high-density neural networks with minimal area requirements. This increased density translates to shorter interconnects, reducing signal propagation delays and associated energy losses.

Moreover, the ability of PU memristors to perform in-memory computing eliminates the need for constant data transfer between memory and processing units. This reduction in data movement significantly decreases energy consumption, as data transfer is often one of the most energy-intensive operations in computing systems.

The integration of PU memristors in neuromorphic circuits also enables more efficient implementation of spike-based neural networks. These networks, which more closely mimic biological neural systems, can operate with sparse, event-driven computations, further reducing energy consumption compared to traditional artificial neural networks that require continuous processing.

Scalability and Integration Challenges

The scalability and integration of PU memristive devices into neuromorphic circuits present significant challenges that must be addressed for their widespread adoption. One of the primary concerns is the ability to fabricate these devices at scale while maintaining consistent performance across large arrays. The variability in device characteristics, such as switching thresholds and resistance states, can lead to unpredictable behavior in neural networks, potentially compromising their reliability and accuracy.

Integration challenges also arise from the need to interface PU memristive devices with conventional CMOS circuitry. The development of hybrid CMOS-memristor architectures requires careful consideration of signal conditioning, level shifting, and impedance matching to ensure seamless operation. Moreover, the design of efficient read and write circuits that can handle the unique properties of PU memristors without compromising their performance or endurance is crucial.

Power consumption and heat dissipation become increasingly critical as the scale of neuromorphic systems grows. While PU memristive devices offer potential energy savings compared to traditional computing paradigms, optimizing their operation to minimize power usage while maintaining computational efficiency remains a challenge. This is particularly important for edge computing applications where power constraints are stringent.

The three-dimensional integration of PU memristive devices presents both opportunities and challenges. While 3D stacking can significantly increase device density and reduce interconnect delays, it also introduces complexities in fabrication, thermal management, and signal integrity. Developing reliable through-silicon vias (TSVs) and addressing issues related to crosstalk and electromagnetic interference in densely packed 3D structures are ongoing areas of research.

Scaling up neuromorphic circuits based on PU memristive devices also requires advancements in design tools and methodologies. Current electronic design automation (EDA) tools are not fully equipped to handle the unique characteristics of memristive devices, necessitating the development of new simulation models and design verification techniques. This includes creating accurate compact models that capture the non-linear and time-dependent behavior of PU memristors for circuit-level simulations.

Lastly, the long-term reliability and endurance of PU memristive devices in large-scale neuromorphic systems remain areas of concern. Understanding and mitigating mechanisms of device degradation, such as resistance drift and switching fatigue, are crucial for ensuring the longevity and stability of neuromorphic circuits. This requires extensive testing and characterization under various operating conditions and over extended periods to validate their suitability for deployment in real-world applications.

Integration challenges also arise from the need to interface PU memristive devices with conventional CMOS circuitry. The development of hybrid CMOS-memristor architectures requires careful consideration of signal conditioning, level shifting, and impedance matching to ensure seamless operation. Moreover, the design of efficient read and write circuits that can handle the unique properties of PU memristors without compromising their performance or endurance is crucial.

Power consumption and heat dissipation become increasingly critical as the scale of neuromorphic systems grows. While PU memristive devices offer potential energy savings compared to traditional computing paradigms, optimizing their operation to minimize power usage while maintaining computational efficiency remains a challenge. This is particularly important for edge computing applications where power constraints are stringent.

The three-dimensional integration of PU memristive devices presents both opportunities and challenges. While 3D stacking can significantly increase device density and reduce interconnect delays, it also introduces complexities in fabrication, thermal management, and signal integrity. Developing reliable through-silicon vias (TSVs) and addressing issues related to crosstalk and electromagnetic interference in densely packed 3D structures are ongoing areas of research.

Scaling up neuromorphic circuits based on PU memristive devices also requires advancements in design tools and methodologies. Current electronic design automation (EDA) tools are not fully equipped to handle the unique characteristics of memristive devices, necessitating the development of new simulation models and design verification techniques. This includes creating accurate compact models that capture the non-linear and time-dependent behavior of PU memristors for circuit-level simulations.

Lastly, the long-term reliability and endurance of PU memristive devices in large-scale neuromorphic systems remain areas of concern. Understanding and mitigating mechanisms of device degradation, such as resistance drift and switching fatigue, are crucial for ensuring the longevity and stability of neuromorphic circuits. This requires extensive testing and characterization under various operating conditions and over extended periods to validate their suitability for deployment in real-world applications.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!