Reliability Qualification Matrix For UCIe Chiplet Interconnect

SEP 1, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Background and Objectives

Universal Chiplet Interconnect Express (UCIe) represents a significant advancement in semiconductor integration technology, emerging as a response to the increasing challenges of traditional monolithic chip scaling. The evolution of semiconductor technology has historically followed Moore's Law, but as physical limitations have become more pronounced, the industry has shifted towards chiplet-based architectures. UCIe was developed as an open industry standard to facilitate high-performance, power-efficient die-to-die interconnects for chiplet-based designs.

The development of UCIe can be traced back to the growing need for modular chip design approaches that could overcome the limitations of traditional semiconductor scaling. As process nodes continued to shrink below 7nm, manufacturing costs and complexity increased exponentially, while performance gains diminished. This technological inflection point necessitated a paradigm shift in chip design philosophy, leading to the emergence of chiplet-based architectures.

UCIe was officially introduced in March 2022 by a consortium of leading semiconductor companies, including Intel, AMD, Arm, ASE, Google, Meta, Microsoft, Qualcomm, Samsung, and TSMC. The standard aims to establish a unified interconnect technology that enables seamless integration of chiplets from different vendors, fabricated using different process technologies, into a single package.

The primary objective of UCIe is to create an open ecosystem for chiplet-based designs, allowing for greater flexibility, scalability, and cost-effectiveness in semiconductor manufacturing. By standardizing the interconnect interface, UCIe seeks to enable a "mix-and-match" approach to chiplet integration, where components from different suppliers can be combined to create customized system-on-chip (SoC) solutions.

From a technical perspective, UCIe defines both the physical layer and protocol stack for die-to-die communication. It supports two primary modes of operation: a standard package substrate mode and an advanced silicon interposer mode, offering flexibility for different performance and cost requirements. The standard encompasses multiple data rates, from 16 GT/s to 32 GT/s in its initial specification, with a roadmap for future enhancements.

The reliability qualification of UCIe interconnects represents a critical aspect of the standard's implementation. As chiplet-based designs become more prevalent in high-performance computing, data centers, artificial intelligence, and other demanding applications, ensuring the long-term reliability of die-to-die interconnects becomes paramount. This necessitates the development of comprehensive reliability qualification matrices that can validate the robustness of UCIe implementations across various operational conditions and use cases.

The ultimate goal of UCIe reliability qualification is to establish industry-wide confidence in chiplet-based architectures, accelerating their adoption across diverse application domains and fostering innovation in semiconductor design and manufacturing. This will enable the continuation of performance scaling beyond the limitations of traditional monolithic approaches, while simultaneously addressing cost, power, and time-to-market considerations.

The development of UCIe can be traced back to the growing need for modular chip design approaches that could overcome the limitations of traditional semiconductor scaling. As process nodes continued to shrink below 7nm, manufacturing costs and complexity increased exponentially, while performance gains diminished. This technological inflection point necessitated a paradigm shift in chip design philosophy, leading to the emergence of chiplet-based architectures.

UCIe was officially introduced in March 2022 by a consortium of leading semiconductor companies, including Intel, AMD, Arm, ASE, Google, Meta, Microsoft, Qualcomm, Samsung, and TSMC. The standard aims to establish a unified interconnect technology that enables seamless integration of chiplets from different vendors, fabricated using different process technologies, into a single package.

The primary objective of UCIe is to create an open ecosystem for chiplet-based designs, allowing for greater flexibility, scalability, and cost-effectiveness in semiconductor manufacturing. By standardizing the interconnect interface, UCIe seeks to enable a "mix-and-match" approach to chiplet integration, where components from different suppliers can be combined to create customized system-on-chip (SoC) solutions.

From a technical perspective, UCIe defines both the physical layer and protocol stack for die-to-die communication. It supports two primary modes of operation: a standard package substrate mode and an advanced silicon interposer mode, offering flexibility for different performance and cost requirements. The standard encompasses multiple data rates, from 16 GT/s to 32 GT/s in its initial specification, with a roadmap for future enhancements.

The reliability qualification of UCIe interconnects represents a critical aspect of the standard's implementation. As chiplet-based designs become more prevalent in high-performance computing, data centers, artificial intelligence, and other demanding applications, ensuring the long-term reliability of die-to-die interconnects becomes paramount. This necessitates the development of comprehensive reliability qualification matrices that can validate the robustness of UCIe implementations across various operational conditions and use cases.

The ultimate goal of UCIe reliability qualification is to establish industry-wide confidence in chiplet-based architectures, accelerating their adoption across diverse application domains and fostering innovation in semiconductor design and manufacturing. This will enable the continuation of performance scaling beyond the limitations of traditional monolithic approaches, while simultaneously addressing cost, power, and time-to-market considerations.

Market Demand Analysis for Chiplet Technology

The chiplet market is experiencing unprecedented growth, driven by the increasing demand for high-performance computing solutions across various industries. As traditional monolithic chip designs reach their physical and economic limits, chiplet technology has emerged as a promising alternative, offering improved performance, cost efficiency, and design flexibility. The Universal Chiplet Interconnect Express (UCIe) standard represents a significant advancement in this domain, providing a standardized approach to chiplet integration.

Market research indicates that the global chiplet market is projected to grow at a compound annual growth rate of over 40% from 2023 to 2030. This explosive growth is primarily fueled by data centers, artificial intelligence applications, and high-performance computing sectors, which collectively demand more powerful and energy-efficient computing solutions. The need for reliable chiplet interconnects has become particularly critical as these applications require seamless communication between different chiplet components.

The enterprise server market has been at the forefront of chiplet adoption, with major players like AMD, Intel, and TSMC implementing chiplet-based architectures in their latest product offerings. These companies recognize the potential of chiplet technology to overcome the limitations of traditional monolithic designs, particularly in terms of manufacturing yield, cost, and performance scaling. The UCIe standard addresses a crucial market need for interoperability between chiplets from different vendors, potentially opening up new business models and supply chain dynamics.

Consumer electronics manufacturers are also showing increasing interest in chiplet technology, particularly for applications requiring high computational power in compact form factors. The smartphone, automotive, and IoT sectors represent significant growth opportunities for chiplet technology, with the market demand expected to accelerate as the technology matures and becomes more accessible to a broader range of applications.

From a geographical perspective, North America currently leads the chiplet market, followed by Asia-Pacific and Europe. However, Asia-Pacific is expected to witness the highest growth rate due to the strong presence of semiconductor manufacturing facilities and increasing investments in advanced packaging technologies. Countries like Taiwan, South Korea, and China are positioning themselves as key players in the chiplet ecosystem.

The market demand for reliable qualification standards for UCIe chiplet interconnects is particularly strong, as system integrators and OEMs require assurance that chiplets from different vendors will function reliably when integrated into a single package. This demand is driving the development of comprehensive reliability qualification matrices that can standardize testing methodologies and acceptance criteria across the industry, ultimately accelerating the adoption of chiplet technology in mission-critical applications.

Market research indicates that the global chiplet market is projected to grow at a compound annual growth rate of over 40% from 2023 to 2030. This explosive growth is primarily fueled by data centers, artificial intelligence applications, and high-performance computing sectors, which collectively demand more powerful and energy-efficient computing solutions. The need for reliable chiplet interconnects has become particularly critical as these applications require seamless communication between different chiplet components.

The enterprise server market has been at the forefront of chiplet adoption, with major players like AMD, Intel, and TSMC implementing chiplet-based architectures in their latest product offerings. These companies recognize the potential of chiplet technology to overcome the limitations of traditional monolithic designs, particularly in terms of manufacturing yield, cost, and performance scaling. The UCIe standard addresses a crucial market need for interoperability between chiplets from different vendors, potentially opening up new business models and supply chain dynamics.

Consumer electronics manufacturers are also showing increasing interest in chiplet technology, particularly for applications requiring high computational power in compact form factors. The smartphone, automotive, and IoT sectors represent significant growth opportunities for chiplet technology, with the market demand expected to accelerate as the technology matures and becomes more accessible to a broader range of applications.

From a geographical perspective, North America currently leads the chiplet market, followed by Asia-Pacific and Europe. However, Asia-Pacific is expected to witness the highest growth rate due to the strong presence of semiconductor manufacturing facilities and increasing investments in advanced packaging technologies. Countries like Taiwan, South Korea, and China are positioning themselves as key players in the chiplet ecosystem.

The market demand for reliable qualification standards for UCIe chiplet interconnects is particularly strong, as system integrators and OEMs require assurance that chiplets from different vendors will function reliably when integrated into a single package. This demand is driving the development of comprehensive reliability qualification matrices that can standardize testing methodologies and acceptance criteria across the industry, ultimately accelerating the adoption of chiplet technology in mission-critical applications.

Current Reliability Challenges in UCIe Implementation

The implementation of Universal Chiplet Interconnect Express (UCIe) faces several significant reliability challenges that must be addressed to ensure robust performance in heterogeneous integration scenarios. The primary concern revolves around the high-density, fine-pitch interconnects that characterize UCIe interfaces, which are particularly susceptible to mechanical stress, thermal cycling, and electromigration effects.

Thermal management presents a formidable challenge as chiplets from different process nodes and manufacturers may exhibit varying thermal characteristics. The differential thermal expansion between adjacent chiplets can induce mechanical stress at interconnect boundaries, potentially leading to solder joint fatigue, delamination, or microcracks in the interconnect structure. These thermal-mechanical stresses are exacerbated during power cycling events, where rapid temperature fluctuations accelerate wear mechanisms.

Signal integrity issues constitute another critical reliability concern. As UCIe pushes data rates beyond 16 GT/s, maintaining signal integrity across the interconnect becomes increasingly difficult. Cross-talk, impedance mismatches, and power supply noise can all degrade signal quality, leading to increased bit error rates and system instability. The challenge is compounded when integrating chiplets with different I/O characteristics and power domains.

Electromigration represents a significant long-term reliability threat for UCIe implementations. The high current densities flowing through the fine-pitch interconnects can cause metal ion migration, eventually leading to void formation or shorts. This phenomenon accelerates with increasing temperature and current density, making it particularly relevant for high-performance computing applications where UCIe is likely to be deployed.

Manufacturing process variations introduce additional reliability concerns. The tight alignment tolerances required for UCIe bump connections (typically <10μm) mean that even minor manufacturing deviations can impact interconnect reliability. Variations in bump height, coplanarity issues, or underfill voids can create localized stress concentrations that become failure points under operational conditions.

Environmental factors also play a crucial role in UCIe reliability. Moisture sensitivity, corrosion resistance, and susceptibility to electrostatic discharge must all be carefully evaluated, particularly for applications in harsh environments or those requiring extended operational lifetimes.

Testing and qualification methodologies for UCIe present unique challenges due to the heterogeneous nature of chiplet integration. Traditional qualification approaches may not adequately capture the complex interaction between different chiplets, necessitating the development of new test methods and reliability models specifically tailored to multi-die packages with UCIe interconnects.

Thermal management presents a formidable challenge as chiplets from different process nodes and manufacturers may exhibit varying thermal characteristics. The differential thermal expansion between adjacent chiplets can induce mechanical stress at interconnect boundaries, potentially leading to solder joint fatigue, delamination, or microcracks in the interconnect structure. These thermal-mechanical stresses are exacerbated during power cycling events, where rapid temperature fluctuations accelerate wear mechanisms.

Signal integrity issues constitute another critical reliability concern. As UCIe pushes data rates beyond 16 GT/s, maintaining signal integrity across the interconnect becomes increasingly difficult. Cross-talk, impedance mismatches, and power supply noise can all degrade signal quality, leading to increased bit error rates and system instability. The challenge is compounded when integrating chiplets with different I/O characteristics and power domains.

Electromigration represents a significant long-term reliability threat for UCIe implementations. The high current densities flowing through the fine-pitch interconnects can cause metal ion migration, eventually leading to void formation or shorts. This phenomenon accelerates with increasing temperature and current density, making it particularly relevant for high-performance computing applications where UCIe is likely to be deployed.

Manufacturing process variations introduce additional reliability concerns. The tight alignment tolerances required for UCIe bump connections (typically <10μm) mean that even minor manufacturing deviations can impact interconnect reliability. Variations in bump height, coplanarity issues, or underfill voids can create localized stress concentrations that become failure points under operational conditions.

Environmental factors also play a crucial role in UCIe reliability. Moisture sensitivity, corrosion resistance, and susceptibility to electrostatic discharge must all be carefully evaluated, particularly for applications in harsh environments or those requiring extended operational lifetimes.

Testing and qualification methodologies for UCIe present unique challenges due to the heterogeneous nature of chiplet integration. Traditional qualification approaches may not adequately capture the complex interaction between different chiplets, necessitating the development of new test methods and reliability models specifically tailored to multi-die packages with UCIe interconnects.

Current Reliability Qualification Methodologies

01 Reliability testing methods for UCIe chiplet interconnects

Various testing methodologies are employed to qualify the reliability of UCIe chiplet interconnects. These include thermal cycling tests, mechanical stress tests, and electrical performance verification under different operating conditions. Advanced testing protocols help identify potential failure modes and ensure the interconnects meet industry standards for reliability and durability in diverse application environments.- Thermal reliability testing for UCIe chiplet interconnects: Thermal reliability testing is crucial for UCIe chiplet interconnects to ensure they can withstand temperature variations during operation. This involves subjecting the interconnects to thermal cycling tests, thermal shock tests, and high-temperature operating life tests. These tests evaluate the reliability of the interconnects under different thermal conditions and help identify potential failure modes. Advanced thermal management techniques are also implemented to enhance the reliability of UCIe chiplet interconnects.

- Mechanical stress testing for UCIe chiplet interconnects: Mechanical stress testing is essential for qualifying UCIe chiplet interconnects. This includes bend testing, vibration testing, and drop testing to evaluate the mechanical robustness of the interconnects. The testing procedures assess the ability of the interconnects to withstand mechanical stresses that may occur during manufacturing, assembly, and operation. Advanced techniques are used to simulate real-world mechanical stresses and evaluate the reliability of the interconnects under these conditions.

- Electrical performance qualification for UCIe chiplet interconnects: Electrical performance qualification involves testing the electrical characteristics of UCIe chiplet interconnects to ensure they meet the required specifications. This includes testing for signal integrity, power integrity, and electromagnetic compatibility. Advanced measurement techniques are used to evaluate parameters such as impedance, crosstalk, and insertion loss. The qualification process also includes testing under various operating conditions to ensure reliable electrical performance throughout the lifecycle of the interconnects.

- Environmental reliability testing for UCIe chiplet interconnects: Environmental reliability testing assesses the ability of UCIe chiplet interconnects to withstand various environmental conditions. This includes humidity testing, salt spray testing, and corrosion testing. The testing procedures evaluate the reliability of the interconnects under different environmental conditions and help identify potential failure modes. Advanced environmental chambers are used to simulate various environmental conditions and evaluate the long-term reliability of the interconnects.

- Reliability qualification methodologies and standards for UCIe chiplet interconnects: Reliability qualification methodologies and standards provide a systematic approach to qualifying UCIe chiplet interconnects. This includes defining test conditions, acceptance criteria, and statistical analysis methods. Industry standards such as JEDEC and IPC are often used as a basis for developing qualification methodologies. Advanced statistical techniques are used to analyze test data and predict the long-term reliability of the interconnects. The qualification process also includes failure analysis to identify root causes of failures and implement corrective actions.

02 Thermal management solutions for UCIe interconnect reliability

Thermal management is critical for ensuring UCIe chiplet interconnect reliability. Solutions include specialized heat dissipation structures, thermal interface materials, and cooling systems designed specifically for chiplet architectures. These approaches help maintain optimal operating temperatures across the interconnect interfaces, preventing thermal-induced failures and ensuring consistent performance during high-processing workloads.Expand Specific Solutions03 Signal integrity and power delivery optimization for UCIe reliability

Maintaining signal integrity and optimizing power delivery are essential aspects of UCIe chiplet interconnect reliability qualification. Advanced techniques include impedance matching, crosstalk reduction, power distribution network design, and noise mitigation strategies. These methods ensure reliable data transmission across chiplet boundaries while maintaining power integrity, which is crucial for the overall system reliability and performance.Expand Specific Solutions04 Manufacturing process controls for UCIe interconnect quality

Stringent manufacturing process controls are implemented to ensure UCIe chiplet interconnect reliability. These include precision alignment techniques, advanced bonding methods, contamination prevention protocols, and statistical process control. Quality assurance measures throughout the manufacturing workflow help minimize defects in the interconnect structures, ensuring consistent electrical and mechanical properties across production batches.Expand Specific Solutions05 Failure analysis and qualification standards for UCIe interconnects

Comprehensive failure analysis methodologies and qualification standards have been developed specifically for UCIe chiplet interconnects. These include accelerated life testing, failure mode and effects analysis, and standardized qualification protocols. The establishment of industry-wide reliability standards ensures consistent evaluation criteria across different manufacturers and applications, facilitating broader adoption of chiplet-based architectures.Expand Specific Solutions

Key Industry Players in Chiplet Ecosystem

The UCIe chiplet interconnect reliability qualification matrix is currently in an emerging growth phase, with the market expected to expand significantly as chiplet technology gains traction. The competitive landscape features established semiconductor giants like Intel, Qualcomm, Samsung, and AMD (formerly ATI) leading technical development, with Intel being particularly prominent in establishing standards. Chinese players including Huawei and ZTE are rapidly advancing their capabilities, while Apple represents a potential major adopter. The technology is approaching early maturity with standardization efforts underway, though full industry-wide implementation remains in development. This market is characterized by strategic positioning among major semiconductor manufacturers seeking to establish dominance in the increasingly important chiplet ecosystem that promises to revolutionize chip design and manufacturing.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed a specialized reliability qualification matrix for UCIe implementation in mobile and edge computing applications. Their approach focuses on low-power, high-bandwidth chiplet interconnects suitable for battery-powered devices. Qualcomm's qualification methodology emphasizes thermal management challenges unique to compact mobile form factors, with particular attention to hotspot mitigation at chiplet interfaces. Their matrix includes specialized testing for power state transitions that occur frequently in mobile scenarios, evaluating interconnect reliability during rapid power cycling. Qualcomm has implemented enhanced ESD protection schemes specifically designed for UCIe interfaces and developed qualification procedures to validate their effectiveness. Their reliability testing includes environmental stress screening optimized for consumer electronics use cases, including humidity, temperature cycling, and mechanical shock testing relevant to mobile device operation.

Strengths: Qualcomm's qualification methodology excels in addressing mobile-specific reliability concerns, particularly power efficiency and thermal management in space-constrained designs. Weaknesses: Their approach may be overly specialized for mobile applications, potentially limiting applicability to high-performance computing or data center environments where different reliability parameters take precedence.

Intel Corp.

Technical Solution: Intel has pioneered the Universal Chiplet Interconnect Express (UCIe) standard and leads the reliability qualification matrix development. Their approach involves comprehensive testing methodologies across physical, protocol, and system levels. Intel's reliability qualification matrix for UCIe includes die-to-die (D2D) interface testing, thermal cycling reliability assessment, and electromigration analysis. They've implemented specific test vectors to validate signal integrity across chiplet boundaries and developed specialized test chips to characterize UCIe PHY layer reliability. Intel's matrix incorporates accelerated stress testing protocols that simulate years of operational conditions to validate long-term reliability of chiplet interconnects. Their qualification process includes evaluation of mechanical stress factors affecting package-level reliability and assessment of power integrity across the interconnect interface.

Strengths: As a founding member of the UCIe consortium, Intel possesses extensive experience in chiplet integration and has established comprehensive testing infrastructure. Their reliability qualification methodology benefits from years of advanced packaging experience. Weaknesses: Their qualification standards may be optimized for their own manufacturing processes, potentially creating challenges for broader ecosystem adoption and interoperability with other vendors' chiplets.

Critical Patents and Standards for UCIe Reliability

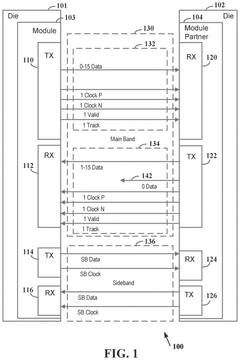

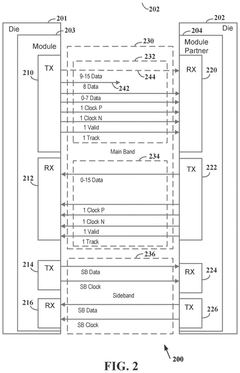

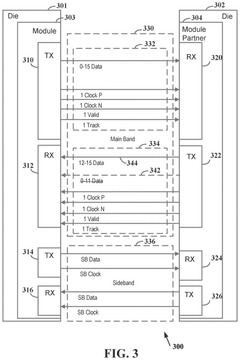

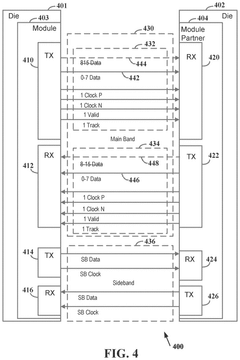

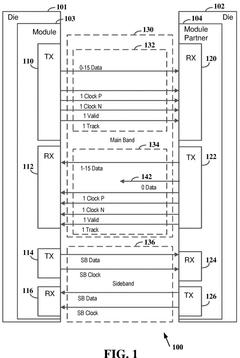

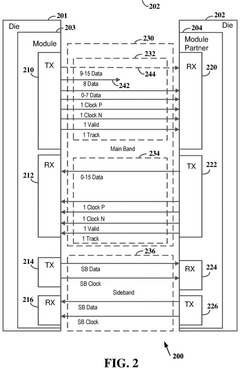

Variable link width in two directions for main band chip module connection

PatentPendingUS20240354279A1

Innovation

- Implementing a method to establish a die-to-die connection with a variable link width, allowing for independent configuration of transmit and receive data lanes through a sideband communication, enabling operation with different numbers of active data lanes in each direction to optimize power usage and data rates, and supporting fault tolerance by excluding faulty lines.

Variable link width in two directions for main band chip module connection

PatentWO2024226177A1

Innovation

- Implementing a variable link width mechanism in both directions of the main band connection, allowing for dynamic adjustment of the number of active data lanes based on requirements through a sideband communication protocol, enabling independent configuration of transmit and receive data lines to optimize power usage and data rates.

Supply Chain Implications for UCIe Adoption

The adoption of UCIe (Universal Chiplet Interconnect Express) technology introduces significant implications for global semiconductor supply chains. As chiplet-based designs gain momentum, traditional monolithic chip manufacturing paradigms are being restructured toward more distributed and specialized production networks. This transformation necessitates new coordination mechanisms between foundries, OSAT (Outsourced Semiconductor Assembly and Test) providers, and design houses.

The reliability qualification matrix for UCIe interconnects directly impacts supply chain configurations by establishing standardized testing protocols that suppliers must adhere to. These requirements create entry barriers for smaller suppliers while simultaneously opening opportunities for specialized testing service providers. Companies that can efficiently validate UCIe interconnect reliability will gain competitive advantages in the emerging chiplet ecosystem.

Geographic diversification of UCIe-compatible manufacturing capabilities is becoming increasingly important as geopolitical tensions affect semiconductor supply security. Currently, advanced packaging facilities capable of implementing UCIe standards are concentrated in East Asia, creating potential bottlenecks. Organizations adopting UCIe technology must consider developing redundant supply sources across different regions to mitigate concentration risks.

The standardization of chiplet interfaces through UCIe is gradually reducing customization requirements between suppliers, potentially enabling more flexible sourcing strategies. This standardization may eventually lead to a "chiplet marketplace" where pre-qualified components from various vendors can be integrated with reduced compatibility concerns. However, this vision remains constrained by the current reliability qualification challenges that limit interoperability between chiplets from different manufacturers.

Material supply considerations for UCIe implementation include specialized substrate requirements and advanced packaging materials that may face supply constraints as adoption accelerates. The microbump density and fine-pitch interconnects central to UCIe technology demand high-precision manufacturing capabilities that are not universally available across the supply base.

Inventory management strategies must evolve to accommodate the modular nature of chiplet-based designs. Rather than managing monolithic chip inventories, companies will need to balance inventories of various chiplet components while considering their different reliability characteristics and qualification timelines. This shift may initially increase supply chain complexity before standardization matures.

The reliability qualification matrix for UCIe interconnects directly impacts supply chain configurations by establishing standardized testing protocols that suppliers must adhere to. These requirements create entry barriers for smaller suppliers while simultaneously opening opportunities for specialized testing service providers. Companies that can efficiently validate UCIe interconnect reliability will gain competitive advantages in the emerging chiplet ecosystem.

Geographic diversification of UCIe-compatible manufacturing capabilities is becoming increasingly important as geopolitical tensions affect semiconductor supply security. Currently, advanced packaging facilities capable of implementing UCIe standards are concentrated in East Asia, creating potential bottlenecks. Organizations adopting UCIe technology must consider developing redundant supply sources across different regions to mitigate concentration risks.

The standardization of chiplet interfaces through UCIe is gradually reducing customization requirements between suppliers, potentially enabling more flexible sourcing strategies. This standardization may eventually lead to a "chiplet marketplace" where pre-qualified components from various vendors can be integrated with reduced compatibility concerns. However, this vision remains constrained by the current reliability qualification challenges that limit interoperability between chiplets from different manufacturers.

Material supply considerations for UCIe implementation include specialized substrate requirements and advanced packaging materials that may face supply constraints as adoption accelerates. The microbump density and fine-pitch interconnects central to UCIe technology demand high-precision manufacturing capabilities that are not universally available across the supply base.

Inventory management strategies must evolve to accommodate the modular nature of chiplet-based designs. Rather than managing monolithic chip inventories, companies will need to balance inventories of various chiplet components while considering their different reliability characteristics and qualification timelines. This shift may initially increase supply chain complexity before standardization matures.

Thermal Management Considerations in Chiplet Design

Thermal management has emerged as a critical consideration in chiplet-based designs, particularly for UCIe (Universal Chiplet Interconnect Express) implementations. As chiplet technology enables higher integration densities and performance levels, the resulting thermal challenges become increasingly complex and demanding. The thermal characteristics of chiplet interconnects directly impact the reliability qualification matrix for UCIe implementations.

The thermal density in chiplet designs frequently exceeds that of traditional monolithic architectures due to the concentration of high-performance components in close proximity. UCIe interconnects, operating at high frequencies with dense signal routing, generate significant heat that must be effectively managed to maintain signal integrity and prevent premature aging of the interconnect structures.

Thermal gradients across chiplet interfaces present particular challenges for reliability qualification. These gradients can induce mechanical stress at the interconnect boundaries due to coefficient of thermal expansion (CTE) mismatches between different materials. For UCIe implementations, this stress directly affects the reliability of micro-bumps, through-silicon vias (TSVs), and other interconnect structures that form the physical foundation of the chiplet-to-chiplet communication channels.

Advanced cooling solutions specifically designed for chiplet architectures have become essential components of the reliability qualification process. These include integrated liquid cooling channels, phase-change materials at critical thermal interfaces, and thermally optimized substrate designs that facilitate heat spreading away from sensitive interconnect regions. The effectiveness of these cooling solutions must be validated as part of the UCIe reliability qualification matrix.

Thermal cycling represents a significant reliability concern for chiplet interconnects. The qualification matrix must include accelerated thermal cycling tests that simulate the operational conditions and potential thermal excursions experienced throughout the product lifecycle. For UCIe implementations, these tests must account for the unique thermal characteristics of high-bandwidth, low-latency interconnects operating across chiplet boundaries.

Computational fluid dynamics (CFD) modeling has become an indispensable tool in predicting thermal behavior and informing the reliability qualification process. These models must accurately represent the complex three-dimensional structures of chiplet designs, including the detailed geometry of UCIe interconnects, to provide meaningful insights into potential thermal bottlenecks and reliability concerns.

The reliability qualification matrix must also consider the impact of thermal management solutions on electrical performance parameters. Thermal interface materials, heat spreaders, and other cooling components can affect signal integrity, latency, and power consumption of UCIe interconnects. Comprehensive qualification testing must therefore evaluate the interaction between thermal management approaches and electrical performance metrics to ensure optimal system-level reliability.

The thermal density in chiplet designs frequently exceeds that of traditional monolithic architectures due to the concentration of high-performance components in close proximity. UCIe interconnects, operating at high frequencies with dense signal routing, generate significant heat that must be effectively managed to maintain signal integrity and prevent premature aging of the interconnect structures.

Thermal gradients across chiplet interfaces present particular challenges for reliability qualification. These gradients can induce mechanical stress at the interconnect boundaries due to coefficient of thermal expansion (CTE) mismatches between different materials. For UCIe implementations, this stress directly affects the reliability of micro-bumps, through-silicon vias (TSVs), and other interconnect structures that form the physical foundation of the chiplet-to-chiplet communication channels.

Advanced cooling solutions specifically designed for chiplet architectures have become essential components of the reliability qualification process. These include integrated liquid cooling channels, phase-change materials at critical thermal interfaces, and thermally optimized substrate designs that facilitate heat spreading away from sensitive interconnect regions. The effectiveness of these cooling solutions must be validated as part of the UCIe reliability qualification matrix.

Thermal cycling represents a significant reliability concern for chiplet interconnects. The qualification matrix must include accelerated thermal cycling tests that simulate the operational conditions and potential thermal excursions experienced throughout the product lifecycle. For UCIe implementations, these tests must account for the unique thermal characteristics of high-bandwidth, low-latency interconnects operating across chiplet boundaries.

Computational fluid dynamics (CFD) modeling has become an indispensable tool in predicting thermal behavior and informing the reliability qualification process. These models must accurately represent the complex three-dimensional structures of chiplet designs, including the detailed geometry of UCIe interconnects, to provide meaningful insights into potential thermal bottlenecks and reliability concerns.

The reliability qualification matrix must also consider the impact of thermal management solutions on electrical performance parameters. Thermal interface materials, heat spreaders, and other cooling components can affect signal integrity, latency, and power consumption of UCIe interconnects. Comprehensive qualification testing must therefore evaluate the interaction between thermal management approaches and electrical performance metrics to ensure optimal system-level reliability.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!