UCIe Chiplet Interconnect Reliability Physics Mechanisms Analysis

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Evolution and Objectives

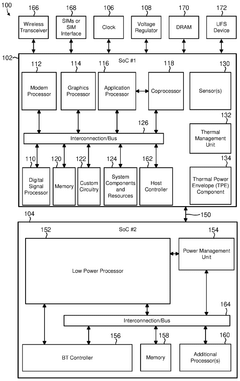

The Universal Chiplet Interconnect Express (UCIe) represents a significant evolution in semiconductor integration technology, emerging as a response to the limitations of traditional monolithic chip designs. The development of UCIe can be traced back to the fundamental challenges in semiconductor scaling, where Moore's Law began encountering physical and economic barriers in the mid-2010s. As transistor densities approached atomic limits, the industry recognized the need for alternative approaches to continue performance improvements and cost reductions.

The chiplet paradigm, which UCIe standardizes, began gaining traction around 2017-2018 when major semiconductor companies started exploring disaggregated chip designs. This approach allows different functional blocks to be manufactured separately using optimal process nodes, then integrated into a single package. Early proprietary implementations by companies like AMD (Infinity Fabric) and Intel (EMIB) demonstrated the viability of this approach but highlighted the need for standardization.

UCIe 1.0 was officially announced in March 2022, marking a watershed moment in the industry's collaborative approach to chiplet interconnect standardization. The consortium behind UCIe includes industry giants such as Intel, AMD, Arm, TSMC, Samsung, and Google, representing an unprecedented level of cooperation across traditionally competitive boundaries. This broad industry support underscores the strategic importance of chiplet technology to the future of computing.

The technical evolution of UCIe builds upon previous interconnect technologies, incorporating lessons from PCI Express, HBM interfaces, and proprietary die-to-die interconnects. The standard defines both die-to-die and package-to-package interconnects, supporting both standard and advanced packaging technologies. UCIe's physical layer supports data rates from 16 GT/s to 32 GT/s in its first iteration, with a roadmap extending to 64 GT/s and beyond.

The primary objectives of UCIe development include establishing an open ecosystem for chiplet-based designs, enabling mix-and-match integration of chiplets from different vendors, reducing development costs through standardization, and improving overall system performance while reducing power consumption. Additionally, UCIe aims to address reliability concerns inherent in multi-die packages by standardizing testing methodologies and reliability requirements.

Looking forward, UCIe's evolution targets increasingly heterogeneous computing architectures, with specialized accelerators, memory systems, and I/O components integrated through standardized interfaces. The roadmap includes enhanced support for optical interconnects, increased bandwidth density, and improved power efficiency metrics. These advancements are critical for next-generation computing applications in AI, high-performance computing, and data-intensive workloads.

The chiplet paradigm, which UCIe standardizes, began gaining traction around 2017-2018 when major semiconductor companies started exploring disaggregated chip designs. This approach allows different functional blocks to be manufactured separately using optimal process nodes, then integrated into a single package. Early proprietary implementations by companies like AMD (Infinity Fabric) and Intel (EMIB) demonstrated the viability of this approach but highlighted the need for standardization.

UCIe 1.0 was officially announced in March 2022, marking a watershed moment in the industry's collaborative approach to chiplet interconnect standardization. The consortium behind UCIe includes industry giants such as Intel, AMD, Arm, TSMC, Samsung, and Google, representing an unprecedented level of cooperation across traditionally competitive boundaries. This broad industry support underscores the strategic importance of chiplet technology to the future of computing.

The technical evolution of UCIe builds upon previous interconnect technologies, incorporating lessons from PCI Express, HBM interfaces, and proprietary die-to-die interconnects. The standard defines both die-to-die and package-to-package interconnects, supporting both standard and advanced packaging technologies. UCIe's physical layer supports data rates from 16 GT/s to 32 GT/s in its first iteration, with a roadmap extending to 64 GT/s and beyond.

The primary objectives of UCIe development include establishing an open ecosystem for chiplet-based designs, enabling mix-and-match integration of chiplets from different vendors, reducing development costs through standardization, and improving overall system performance while reducing power consumption. Additionally, UCIe aims to address reliability concerns inherent in multi-die packages by standardizing testing methodologies and reliability requirements.

Looking forward, UCIe's evolution targets increasingly heterogeneous computing architectures, with specialized accelerators, memory systems, and I/O components integrated through standardized interfaces. The roadmap includes enhanced support for optical interconnects, increased bandwidth density, and improved power efficiency metrics. These advancements are critical for next-generation computing applications in AI, high-performance computing, and data-intensive workloads.

Market Demand Analysis for Chiplet Integration

The chiplet integration market is experiencing unprecedented growth, driven by the semiconductor industry's shift from monolithic designs to disaggregated architectures. As traditional Moore's Law scaling faces physical and economic limitations, chiplet technology has emerged as a viable path forward, with the market expected to reach $57 billion by 2035, representing a compound annual growth rate of approximately 40% from 2023.

This explosive growth is primarily fueled by data centers and high-performance computing sectors, where the demand for increased computational power, memory bandwidth, and specialized accelerators continues to surge. Cloud service providers are particularly interested in chiplet solutions that can deliver customized performance profiles while maintaining power efficiency, a critical factor as data centers approach power delivery limitations.

Consumer electronics manufacturers are also driving market demand, seeking chiplet-based solutions to differentiate their products through enhanced performance and power efficiency. The automotive sector represents another significant growth area, with advanced driver assistance systems and autonomous driving technologies requiring sophisticated heterogeneous computing platforms that can be efficiently implemented using chiplet architectures.

From a supply chain perspective, chiplet integration offers compelling advantages. The ability to mix and match components from different process nodes allows manufacturers to optimize cost structures and mitigate supply chain risks. This flexibility is particularly valuable given recent global semiconductor shortages and geopolitical tensions affecting technology supply chains.

The reliability of chiplet interconnects, particularly those based on the Universal Chiplet Interconnect Express (UCIe) standard, has become a critical market requirement. Enterprise customers are demanding comprehensive reliability data and physics of failure understanding before committing to chiplet-based architectures for mission-critical applications. This has created a market pull for advanced reliability physics analysis of UCIe interconnects.

Geographically, North America leads the chiplet integration market, driven by hyperscalers and semiconductor giants. However, Asia-Pacific represents the fastest-growing region, with significant investments in chiplet technology from China, Taiwan, South Korea, and Japan. European demand is primarily concentrated in automotive and industrial applications, where reliability requirements are exceptionally stringent.

The market is increasingly demanding standardized approaches to chiplet integration, with UCIe emerging as the leading contender for broad industry adoption. This standardization is expected to accelerate market growth by enabling a more diverse ecosystem of chiplet suppliers and integrators, potentially transforming the semiconductor industry's structure toward greater specialization and collaboration.

This explosive growth is primarily fueled by data centers and high-performance computing sectors, where the demand for increased computational power, memory bandwidth, and specialized accelerators continues to surge. Cloud service providers are particularly interested in chiplet solutions that can deliver customized performance profiles while maintaining power efficiency, a critical factor as data centers approach power delivery limitations.

Consumer electronics manufacturers are also driving market demand, seeking chiplet-based solutions to differentiate their products through enhanced performance and power efficiency. The automotive sector represents another significant growth area, with advanced driver assistance systems and autonomous driving technologies requiring sophisticated heterogeneous computing platforms that can be efficiently implemented using chiplet architectures.

From a supply chain perspective, chiplet integration offers compelling advantages. The ability to mix and match components from different process nodes allows manufacturers to optimize cost structures and mitigate supply chain risks. This flexibility is particularly valuable given recent global semiconductor shortages and geopolitical tensions affecting technology supply chains.

The reliability of chiplet interconnects, particularly those based on the Universal Chiplet Interconnect Express (UCIe) standard, has become a critical market requirement. Enterprise customers are demanding comprehensive reliability data and physics of failure understanding before committing to chiplet-based architectures for mission-critical applications. This has created a market pull for advanced reliability physics analysis of UCIe interconnects.

Geographically, North America leads the chiplet integration market, driven by hyperscalers and semiconductor giants. However, Asia-Pacific represents the fastest-growing region, with significant investments in chiplet technology from China, Taiwan, South Korea, and Japan. European demand is primarily concentrated in automotive and industrial applications, where reliability requirements are exceptionally stringent.

The market is increasingly demanding standardized approaches to chiplet integration, with UCIe emerging as the leading contender for broad industry adoption. This standardization is expected to accelerate market growth by enabling a more diverse ecosystem of chiplet suppliers and integrators, potentially transforming the semiconductor industry's structure toward greater specialization and collaboration.

Current Challenges in UCIe Reliability Physics

Despite the promising advancements in UCIe (Universal Chiplet Interconnect Express) technology, several significant reliability physics challenges persist that impede its widespread adoption and optimal performance. The miniaturization of interconnects in chiplet designs has introduced complex reliability concerns related to electromigration at the die-to-die interfaces. As current densities increase in these narrow interconnect pathways, metal ion migration accelerates, potentially creating voids and ultimately leading to connection failures over time.

Thermal management presents another critical challenge for UCIe implementations. The dense packaging of multiple chiplets creates thermal hotspots and significant temperature gradients across the package. These thermal variations induce mechanical stresses due to coefficient of thermal expansion (CTE) mismatches between different materials, potentially causing delamination, cracking, or solder joint fatigue. Current thermal solutions struggle to efficiently dissipate heat from the internal chiplet interfaces where conventional cooling techniques cannot directly access.

Signal integrity degradation represents a substantial reliability concern as UCIe pushes toward higher data rates. As frequencies increase, phenomena such as crosstalk, impedance mismatches, and electromagnetic interference become more pronounced. The physical proximity of multiple high-speed channels in the compact UCIe form factor exacerbates these issues, potentially leading to bit error rate increases and communication failures between chiplets.

Material interface reliability at the microbump and C4 bump connections presents unique challenges. The repeated thermal cycling during normal operation induces stress at these critical junctions, potentially leading to crack initiation and propagation. Additionally, intermetallic compound formation at these interfaces can alter electrical and mechanical properties over time, affecting long-term reliability.

Power delivery network (PDN) stability is increasingly challenging as chiplets demand more power in smaller areas. Voltage droops and power supply noise can compromise signal integrity and timing margins. The limited space for decoupling capacitors in the UCIe architecture makes it difficult to maintain stable power delivery across all operating conditions.

Moisture sensitivity and corrosion mechanisms pose reliability risks, particularly at the fine-pitch interconnects where protective measures are constrained by dimensional limitations. Environmental factors can accelerate degradation mechanisms, especially in applications exposed to harsh conditions or wide temperature variations.

Testing and qualification methodologies for UCIe implementations remain underdeveloped, with limited industry consensus on acceleration factors and failure criteria specific to chiplet architectures. This gap complicates reliability predictions and lifetime estimations for UCIe-based products.

Thermal management presents another critical challenge for UCIe implementations. The dense packaging of multiple chiplets creates thermal hotspots and significant temperature gradients across the package. These thermal variations induce mechanical stresses due to coefficient of thermal expansion (CTE) mismatches between different materials, potentially causing delamination, cracking, or solder joint fatigue. Current thermal solutions struggle to efficiently dissipate heat from the internal chiplet interfaces where conventional cooling techniques cannot directly access.

Signal integrity degradation represents a substantial reliability concern as UCIe pushes toward higher data rates. As frequencies increase, phenomena such as crosstalk, impedance mismatches, and electromagnetic interference become more pronounced. The physical proximity of multiple high-speed channels in the compact UCIe form factor exacerbates these issues, potentially leading to bit error rate increases and communication failures between chiplets.

Material interface reliability at the microbump and C4 bump connections presents unique challenges. The repeated thermal cycling during normal operation induces stress at these critical junctions, potentially leading to crack initiation and propagation. Additionally, intermetallic compound formation at these interfaces can alter electrical and mechanical properties over time, affecting long-term reliability.

Power delivery network (PDN) stability is increasingly challenging as chiplets demand more power in smaller areas. Voltage droops and power supply noise can compromise signal integrity and timing margins. The limited space for decoupling capacitors in the UCIe architecture makes it difficult to maintain stable power delivery across all operating conditions.

Moisture sensitivity and corrosion mechanisms pose reliability risks, particularly at the fine-pitch interconnects where protective measures are constrained by dimensional limitations. Environmental factors can accelerate degradation mechanisms, especially in applications exposed to harsh conditions or wide temperature variations.

Testing and qualification methodologies for UCIe implementations remain underdeveloped, with limited industry consensus on acceleration factors and failure criteria specific to chiplet architectures. This gap complicates reliability predictions and lifetime estimations for UCIe-based products.

Current Reliability Solutions for Chiplet Interconnects

01 Thermal reliability mechanisms in UCIe chiplet interconnects

Thermal reliability is a critical aspect of UCIe chiplet interconnects. The thermal cycling and heat dissipation between interconnected chiplets can lead to various failure mechanisms including thermal expansion mismatch, solder joint fatigue, and thermal interface degradation. Advanced thermal management solutions and materials are implemented to mitigate these issues, ensuring stable electrical connections between chiplets under varying thermal conditions. Thermal modeling and simulation techniques are used to predict and prevent thermal-related failures in UCIe implementations.- Thermal reliability mechanisms in UCIe chiplet interconnects: Thermal reliability is a critical aspect of UCIe chiplet interconnects, focusing on how temperature fluctuations and thermal cycling affect the physical integrity of interconnect structures. These mechanisms include thermal expansion mismatch between different materials, thermal stress accumulation at interface boundaries, and thermally-induced fatigue in bump connections. Advanced thermal management techniques and materials with compatible coefficients of thermal expansion are employed to mitigate these issues and enhance the overall reliability of chiplet interconnects under varying thermal conditions.

- Mechanical stress and strain reliability in UCIe interconnects: Mechanical stress and strain represent significant reliability concerns in UCIe chiplet interconnects. These physical mechanisms include warpage-induced stress, mechanical fatigue during assembly and operation, and strain accumulation at die-to-die interfaces. The reliability physics involves understanding how mechanical forces propagate through heterogeneous material stacks and identifying potential failure points. Solutions include optimized underfill materials, strategic bump placement, and advanced package designs that distribute mechanical stress more evenly across the interconnect structure.

- Electromigration and current density effects in UCIe interconnects: Electromigration represents a critical reliability physics mechanism in UCIe chiplet interconnects, particularly as dimensions shrink and current densities increase. This phenomenon involves the gradual displacement of metal atoms due to momentum transfer from conducting electrons, leading to void formation and eventual interconnect failure. The reliability physics focuses on current crowding at interface transitions, material transport mechanisms, and accelerated degradation under high-current conditions. Mitigation strategies include optimized metallization schemes, current-spreading designs, and redundant interconnect pathways.

- Interfacial reliability and material interaction mechanisms: Interfacial reliability in UCIe chiplet interconnects involves the complex interactions between different materials at connection boundaries. These mechanisms include intermetallic compound formation, diffusion-related degradation, and interfacial delamination under stress conditions. The reliability physics focuses on understanding atomic migration between dissimilar materials, chemical reactions at elevated temperatures, and adhesion strength under various environmental conditions. Advanced solutions include barrier layers to prevent unwanted diffusion, optimized bonding processes, and interface engineering to enhance long-term stability of the interconnect structures.

- Environmental and moisture-related reliability mechanisms: Environmental factors significantly impact UCIe chiplet interconnect reliability, with moisture being a primary concern. These mechanisms include moisture-induced corrosion, hygroscopic swelling of polymeric materials, and galvanic reactions in the presence of contaminants. The reliability physics involves understanding how environmental stressors penetrate package boundaries and affect interconnect integrity over time. Protective strategies include advanced encapsulation materials, hermetic sealing techniques, and corrosion-resistant metallization schemes to shield sensitive interconnect structures from environmental degradation.

02 Mechanical stress and strain reliability in UCIe interconnects

Mechanical stress and strain significantly impact the reliability of UCIe chiplet interconnects. These stresses can arise from coefficient of thermal expansion (CTE) mismatches, package warpage, assembly processes, and operational vibrations. The mechanical reliability mechanisms include microbump cracking, delamination at interfaces, and substrate warping. Advanced materials and structural designs are employed to distribute stress more evenly and enhance the mechanical robustness of the interconnects, ensuring long-term reliability under various mechanical loads and environmental conditions.Expand Specific Solutions03 Electrical reliability physics in UCIe chiplet connections

Electrical reliability of UCIe chiplet interconnects involves mechanisms such as electromigration, signal integrity degradation, and electrical overstress. These phenomena can lead to increased resistance, signal distortion, and eventual interconnect failure. The physics behind these mechanisms includes electron flow-induced material transport, impedance mismatches, and electrical field concentrations. Advanced design techniques incorporate redundant pathways, optimized trace geometries, and improved materials to enhance electrical reliability and ensure consistent performance across varying operational conditions and over the product lifetime.Expand Specific Solutions04 Environmental and chemical reliability factors in UCIe technology

Environmental and chemical factors significantly impact UCIe chiplet interconnect reliability. These include moisture ingress, corrosion, oxidation, and contamination at the interconnect interfaces. The reliability physics involves chemical reactions at material interfaces, diffusion processes, and environmental stress-induced degradation. Protective coatings, hermetic sealing techniques, and moisture-resistant materials are employed to mitigate these effects. Testing protocols simulate accelerated environmental conditions to predict and improve the long-term reliability of UCIe interconnects under various environmental stresses.Expand Specific Solutions05 Testing and monitoring methodologies for UCIe reliability

Advanced testing and monitoring methodologies are essential for ensuring UCIe chiplet interconnect reliability. These include in-situ monitoring systems, accelerated life testing, failure analysis techniques, and predictive reliability modeling. The physics-based approaches involve understanding failure mechanisms through techniques such as electron microscopy, X-ray tomography, and electrical characterization. Real-time monitoring during operation helps detect early signs of degradation, while comprehensive reliability models incorporate multiple physics domains to predict lifetime performance under various operational conditions.Expand Specific Solutions

Key Industry Players in UCIe Ecosystem

The UCIe Chiplet Interconnect Reliability Physics Mechanisms market is currently in an early growth phase, characterized by increasing adoption as the semiconductor industry shifts toward chiplet-based architectures. The market is projected to expand significantly, driven by demands for higher performance computing and AI applications. From a technical maturity perspective, industry leaders like Intel, TSMC, and Qualcomm are making substantial investments in reliability physics research, focusing on electromigration, thermal cycling effects, and mechanical stress mechanisms. IBM and GlobalFoundries are advancing testing methodologies, while Samsung and Huawei are developing proprietary solutions. The competitive landscape shows established semiconductor manufacturers collaborating with specialized interconnect technology providers like Avicena, creating a dynamic ecosystem where reliability physics understanding will be a key differentiator in the evolving chiplet interconnect market.

Intel Corp.

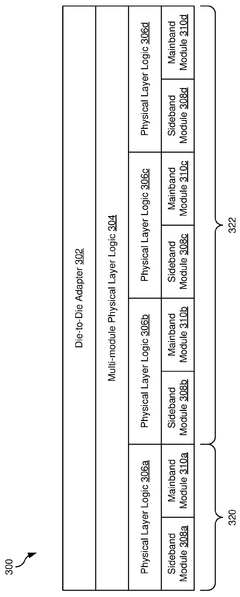

Technical Solution: Intel is a founding member and leading contributor to the UCIe standard, focusing on reliability physics mechanisms for chiplet interconnects. Their approach involves comprehensive physical layer design with advanced signal integrity analysis and robust error correction mechanisms. Intel's UCIe implementation features die-to-die (D2D) PHY technology that supports both standard and advanced modes with data rates up to 32 GT/s. Their reliability physics analysis includes thermal cycling stress modeling, electromigration assessment, and time-dependent dielectric breakdown (TDDB) characterization for microbump and hybrid bonding interfaces. Intel has developed specialized test structures to evaluate mechanical stress distribution across chiplet interfaces and implements adaptive voltage scaling to compensate for process variations that could affect interconnect reliability[1][3]. Their UCIe reliability framework incorporates real-time monitoring systems that detect early signs of degradation through specialized sensors embedded within the interconnect fabric.

Strengths: Industry-leading expertise in chiplet integration; extensive manufacturing infrastructure; comprehensive reliability testing capabilities; established ecosystem partnerships. Weaknesses: Proprietary aspects may limit interoperability with some third-party chiplets; higher implementation costs compared to simpler interconnect solutions; complex validation requirements for heterogeneous integration scenarios.

IBM Corp.

Technical Solution: IBM has developed advanced reliability physics mechanisms for UCIe chiplet interconnects focusing on their unique silicon interposer technology. Their approach integrates multi-physics modeling with experimental validation to address reliability challenges in high-density interconnects. IBM's reliability analysis framework examines electromigration effects at the microbump level, stress-induced voiding, and thermal cycling impacts on interconnect integrity. They've pioneered non-destructive testing methodologies including acoustic microscopy and X-ray tomography to detect early failure indicators in chiplet interfaces. IBM's UCIe implementation incorporates redundant routing paths and adaptive error correction to maintain signal integrity under varying stress conditions. Their reliability physics models account for material interface interactions, particularly at the boundary between different chiplet substrates and interconnect metals[2]. IBM has also developed specialized reliability enhancement techniques for their 2.5D and 3D integration platforms that are compatible with the UCIe standard, including stress-relieving underfill materials and optimized thermal management solutions for high-density interconnects.

Strengths: Extensive experience in heterogeneous integration; advanced materials science expertise; sophisticated multi-physics modeling capabilities; proven track record in high-reliability computing systems. Weaknesses: Solutions may be optimized for high-performance computing rather than broader market applications; potentially higher cost structure; complex implementation requirements for system integrators.

Critical Physics Mechanisms in UCIe Failure Modes

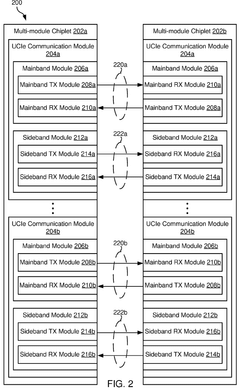

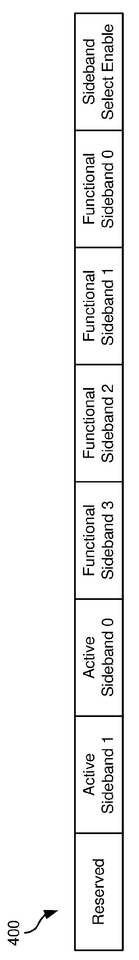

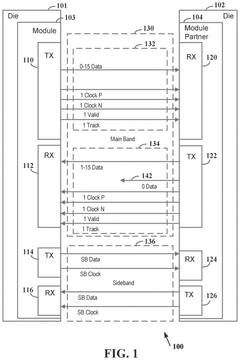

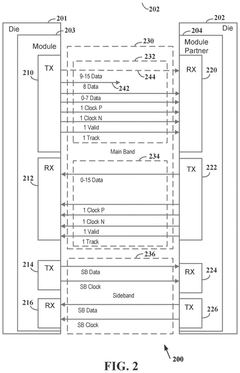

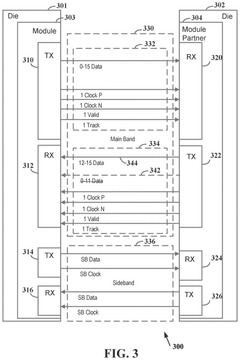

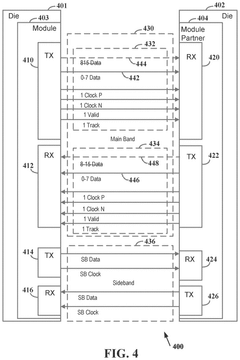

Mechanism to improve the reliability of sideband in chiplets

PatentWO2025058796A1

Innovation

- The method involves configuring UCIe links between multi-module chiplets to enable runtime selection and aggregation of sidebands, allowing for the use of different or additional sidebands beyond the initially active one, thereby reducing hardware stress and enhancing communication reliability.

Variable link width in two directions for main band chip module connection

PatentPendingUS20240354279A1

Innovation

- Implementing a method to establish a die-to-die connection with a variable link width, allowing for independent configuration of transmit and receive data lanes through a sideband communication, enabling operation with different numbers of active data lanes in each direction to optimize power usage and data rates, and supporting fault tolerance by excluding faulty lines.

Standardization Efforts in Chiplet Interconnect Technology

The standardization of chiplet interconnect technologies has become a critical focus area in the semiconductor industry, with UCIe (Universal Chiplet Interconnect Express) emerging as a leading standard. The formation of the UCIe Consortium in March 2022 marked a significant milestone, bringing together industry giants including Intel, AMD, Arm, TSMC, Samsung, and Google to establish a unified approach to chiplet integration.

UCIe 1.0 specification, released in 2022, defines both the physical layer and protocol stack for die-to-die interconnection, addressing key reliability concerns through standardized testing methodologies and failure criteria. This specification covers essential aspects such as electrical parameters, mechanical specifications, and thermal management requirements that directly impact interconnect reliability physics mechanisms.

Beyond UCIe, other notable standardization efforts include JEDEC's development of JEP30: "Guideline for Measuring and Reporting Die-to-Die Interface Characteristics" which provides standardized methodologies for evaluating chiplet interconnect reliability. The Open Compute Project (OCP) has also contributed through its Chiplet Design Exchange (CDX) framework, focusing on standardizing chiplet design and verification processes.

The IEEE Standards Association has established working groups specifically addressing chiplet interconnect reliability testing and qualification procedures. These groups are developing standards for accelerated stress testing that can accurately predict long-term reliability of die-to-die interfaces under various environmental conditions and operational stresses.

Industry consortiums like SEMI have created task forces dedicated to standardizing materials and manufacturing processes for chiplet interconnects, with particular emphasis on reliability physics mechanisms such as electromigration, thermal cycling effects, and mechanical stress impacts on microbumps and hybrid bonding interfaces.

Standardization efforts are increasingly focusing on reliability modeling frameworks that can predict failure mechanisms across different chiplet interconnect technologies. These frameworks aim to establish common reliability metrics and qualification methodologies that enable apples-to-apples comparisons between different interconnect solutions.

The Heterogeneous Integration Roadmap (HIR), sponsored by IEEE, SEMI, and other organizations, provides a comprehensive technology roadmap that includes standardization targets for chiplet interconnect reliability. This roadmap identifies key reliability challenges and standardization needs for emerging interconnect technologies, guiding future research and development efforts in the industry.

UCIe 1.0 specification, released in 2022, defines both the physical layer and protocol stack for die-to-die interconnection, addressing key reliability concerns through standardized testing methodologies and failure criteria. This specification covers essential aspects such as electrical parameters, mechanical specifications, and thermal management requirements that directly impact interconnect reliability physics mechanisms.

Beyond UCIe, other notable standardization efforts include JEDEC's development of JEP30: "Guideline for Measuring and Reporting Die-to-Die Interface Characteristics" which provides standardized methodologies for evaluating chiplet interconnect reliability. The Open Compute Project (OCP) has also contributed through its Chiplet Design Exchange (CDX) framework, focusing on standardizing chiplet design and verification processes.

The IEEE Standards Association has established working groups specifically addressing chiplet interconnect reliability testing and qualification procedures. These groups are developing standards for accelerated stress testing that can accurately predict long-term reliability of die-to-die interfaces under various environmental conditions and operational stresses.

Industry consortiums like SEMI have created task forces dedicated to standardizing materials and manufacturing processes for chiplet interconnects, with particular emphasis on reliability physics mechanisms such as electromigration, thermal cycling effects, and mechanical stress impacts on microbumps and hybrid bonding interfaces.

Standardization efforts are increasingly focusing on reliability modeling frameworks that can predict failure mechanisms across different chiplet interconnect technologies. These frameworks aim to establish common reliability metrics and qualification methodologies that enable apples-to-apples comparisons between different interconnect solutions.

The Heterogeneous Integration Roadmap (HIR), sponsored by IEEE, SEMI, and other organizations, provides a comprehensive technology roadmap that includes standardization targets for chiplet interconnect reliability. This roadmap identifies key reliability challenges and standardization needs for emerging interconnect technologies, guiding future research and development efforts in the industry.

Thermal Management Considerations for UCIe Implementation

Thermal management represents a critical challenge in the implementation of Universal Chiplet Interconnect Express (UCIe) technology. As chiplet-based designs increase in complexity and density, heat dissipation becomes a significant reliability concern that directly impacts the performance and lifespan of interconnects. The thermal characteristics of UCIe implementations are influenced by multiple factors including die-to-die (D2D) interface density, power consumption patterns, and package design constraints.

The thermal profile across UCIe interfaces exhibits significant non-uniformity, with hotspots frequently occurring at high-traffic interconnect regions. These thermal gradients can accelerate various degradation mechanisms, particularly at the micro-bump interfaces where coefficient of thermal expansion (CTE) mismatches between different materials create mechanical stress during thermal cycling. Recent thermal modeling studies indicate that temperature differentials of 20-30°C can develop across a single chiplet assembly under heavy computational loads.

Advanced cooling solutions specifically tailored for UCIe implementations have emerged as essential components of reliable system design. These include integrated liquid cooling channels, phase-change materials at critical thermal interfaces, and thermally optimized substrate materials with enhanced heat spreading capabilities. The industry has observed a 15-25% improvement in thermal performance through the strategic placement of thermal vias and optimized heat sink designs that account for the unique thermal characteristics of chiplet-based architectures.

Power management techniques play a crucial role in thermal control for UCIe implementations. Dynamic frequency scaling and workload distribution algorithms that consider thermal constraints have demonstrated effectiveness in preventing thermal runaway conditions. Thermal-aware routing of high-speed signals within the UCIe interface can reduce localized heating by distributing power dissipation more evenly across the interconnect structure.

Testing protocols for thermal reliability have evolved to address the specific challenges of UCIe implementations. Accelerated thermal cycling tests that simulate operational conditions have revealed that thermal fatigue at interconnect points typically manifests after 1000-2000 cycles under extreme temperature differentials. Infrared thermography and embedded thermal sensors provide real-time monitoring capabilities that enable adaptive thermal management strategies during operation.

The relationship between thermal management and signal integrity presents another dimension of complexity in UCIe implementations. Temperature-induced changes in electrical characteristics, including resistance variations and timing shifts, can compromise the high-speed data transfer capabilities that make UCIe attractive. Compensation mechanisms such as adaptive equalization and temperature-calibrated timing adjustments have become standard features in robust UCIe designs.

The thermal profile across UCIe interfaces exhibits significant non-uniformity, with hotspots frequently occurring at high-traffic interconnect regions. These thermal gradients can accelerate various degradation mechanisms, particularly at the micro-bump interfaces where coefficient of thermal expansion (CTE) mismatches between different materials create mechanical stress during thermal cycling. Recent thermal modeling studies indicate that temperature differentials of 20-30°C can develop across a single chiplet assembly under heavy computational loads.

Advanced cooling solutions specifically tailored for UCIe implementations have emerged as essential components of reliable system design. These include integrated liquid cooling channels, phase-change materials at critical thermal interfaces, and thermally optimized substrate materials with enhanced heat spreading capabilities. The industry has observed a 15-25% improvement in thermal performance through the strategic placement of thermal vias and optimized heat sink designs that account for the unique thermal characteristics of chiplet-based architectures.

Power management techniques play a crucial role in thermal control for UCIe implementations. Dynamic frequency scaling and workload distribution algorithms that consider thermal constraints have demonstrated effectiveness in preventing thermal runaway conditions. Thermal-aware routing of high-speed signals within the UCIe interface can reduce localized heating by distributing power dissipation more evenly across the interconnect structure.

Testing protocols for thermal reliability have evolved to address the specific challenges of UCIe implementations. Accelerated thermal cycling tests that simulate operational conditions have revealed that thermal fatigue at interconnect points typically manifests after 1000-2000 cycles under extreme temperature differentials. Infrared thermography and embedded thermal sensors provide real-time monitoring capabilities that enable adaptive thermal management strategies during operation.

The relationship between thermal management and signal integrity presents another dimension of complexity in UCIe implementations. Temperature-induced changes in electrical characteristics, including resistance variations and timing shifts, can compromise the high-speed data transfer capabilities that make UCIe attractive. Compensation mechanisms such as adaptive equalization and temperature-calibrated timing adjustments have become standard features in robust UCIe designs.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!