Retimer And Equalization Techniques For UCIe Chiplet Interconnect

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Background and Objectives

Universal Chiplet Interconnect Express (UCIe) represents a transformative approach to semiconductor design and integration, emerging as a response to the increasing challenges in traditional monolithic chip scaling. Developed as an open industry standard, UCIe addresses the growing need for modular chip design in an era where Moore's Law faces physical and economic limitations. The technology enables the disaggregation of system-on-chip (SoC) designs into smaller functional blocks called chiplets, which can be manufactured separately and then integrated into a single package.

The evolution of UCIe stems from the semiconductor industry's recognition that traditional scaling approaches were becoming increasingly difficult to sustain. As process nodes shrink below 5nm, manufacturing costs and technical challenges have escalated dramatically. UCIe offers a paradigm shift by allowing different functional components to be fabricated using optimal process technologies and then combined, optimizing both performance and cost.

The primary objective of UCIe is to establish a standardized die-to-die interconnect that facilitates high-bandwidth, low-latency, and energy-efficient communication between chiplets. This standardization aims to create an ecosystem where chiplets from different vendors can interoperate seamlessly, fostering innovation and competition while reducing development cycles and costs.

UCIe technology encompasses both physical layer specifications and protocol mappings. The physical layer defines parameters such as signaling rates, channel characteristics, and electrical specifications, while protocol mappings enable compatibility with existing interfaces like PCIe, CXL, and memory protocols. This comprehensive approach ensures that UCIe can support diverse application requirements across computing, networking, storage, and specialized accelerators.

The development of UCIe has been driven by a consortium of industry leaders including Intel, AMD, Arm, TSMC, Samsung, and others, highlighting its significance as a cross-industry initiative. The first specification, UCIe 1.0, was released in March 2022, establishing the foundation for chiplet-based designs with standardized interconnects.

Looking at the technical trajectory, UCIe builds upon previous interconnect technologies while addressing their limitations. It incorporates advanced features such as adaptive equalization, forward error correction, and sophisticated power management to meet the demands of next-generation computing systems. The standard is designed to scale from current data rates of 16-32 GT/s to future implementations exceeding 64 GT/s.

As computing workloads become increasingly diverse and specialized, UCIe aims to enable a more flexible and efficient approach to system design. By facilitating the integration of heterogeneous chiplets, it supports the development of customized solutions for emerging applications in artificial intelligence, high-performance computing, and edge computing, while maintaining compatibility with established ecosystem components.

The evolution of UCIe stems from the semiconductor industry's recognition that traditional scaling approaches were becoming increasingly difficult to sustain. As process nodes shrink below 5nm, manufacturing costs and technical challenges have escalated dramatically. UCIe offers a paradigm shift by allowing different functional components to be fabricated using optimal process technologies and then combined, optimizing both performance and cost.

The primary objective of UCIe is to establish a standardized die-to-die interconnect that facilitates high-bandwidth, low-latency, and energy-efficient communication between chiplets. This standardization aims to create an ecosystem where chiplets from different vendors can interoperate seamlessly, fostering innovation and competition while reducing development cycles and costs.

UCIe technology encompasses both physical layer specifications and protocol mappings. The physical layer defines parameters such as signaling rates, channel characteristics, and electrical specifications, while protocol mappings enable compatibility with existing interfaces like PCIe, CXL, and memory protocols. This comprehensive approach ensures that UCIe can support diverse application requirements across computing, networking, storage, and specialized accelerators.

The development of UCIe has been driven by a consortium of industry leaders including Intel, AMD, Arm, TSMC, Samsung, and others, highlighting its significance as a cross-industry initiative. The first specification, UCIe 1.0, was released in March 2022, establishing the foundation for chiplet-based designs with standardized interconnects.

Looking at the technical trajectory, UCIe builds upon previous interconnect technologies while addressing their limitations. It incorporates advanced features such as adaptive equalization, forward error correction, and sophisticated power management to meet the demands of next-generation computing systems. The standard is designed to scale from current data rates of 16-32 GT/s to future implementations exceeding 64 GT/s.

As computing workloads become increasingly diverse and specialized, UCIe aims to enable a more flexible and efficient approach to system design. By facilitating the integration of heterogeneous chiplets, it supports the development of customized solutions for emerging applications in artificial intelligence, high-performance computing, and edge computing, while maintaining compatibility with established ecosystem components.

Market Analysis for Chiplet-Based Computing Solutions

The chiplet-based computing solutions market is experiencing unprecedented growth, driven by the increasing demand for high-performance computing systems that can overcome the limitations of traditional monolithic chip designs. As Moore's Law faces physical constraints, the industry is pivoting toward disaggregated architectures that allow for more specialized and efficient computing solutions. The global chiplet market is projected to grow at a CAGR of 40% from 2023 to 2028, reaching approximately $50 billion by the end of the forecast period.

Data centers and cloud service providers represent the largest market segment, accounting for nearly 45% of the total chiplet market. These entities require increasingly powerful and energy-efficient computing solutions to handle the exponential growth in data processing demands. The adoption of UCIe (Universal Chiplet Interconnect Express) standards is accelerating this market segment's growth by enabling interoperability between chiplets from different vendors.

Consumer electronics constitutes the second-largest market segment, with high-end smartphones, tablets, and gaming consoles increasingly incorporating chiplet-based designs to deliver enhanced performance while managing thermal constraints. This segment is expected to grow significantly as manufacturers seek to differentiate their products through superior computing capabilities.

The automotive sector represents an emerging but rapidly growing market for chiplet-based solutions, particularly for advanced driver-assistance systems (ADAS) and autonomous driving platforms. These applications require high-performance, low-latency computing capabilities that can be efficiently delivered through specialized chiplet architectures.

Geographically, North America leads the chiplet market with approximately 40% market share, driven by the presence of major semiconductor companies and hyperscale data center operators. Asia-Pacific follows closely and is expected to demonstrate the highest growth rate, fueled by substantial investments in semiconductor manufacturing infrastructure in countries like Taiwan, South Korea, and China.

The market dynamics are further shaped by the increasing focus on AI and machine learning applications, which demand specialized accelerators that can be efficiently implemented using chiplet-based designs. The ability to mix and match different types of computing elements (CPU, GPU, TPU, memory) through high-speed UCIe interconnects is creating new opportunities for customized computing solutions tailored to specific workloads.

Supply chain considerations are becoming increasingly important in the chiplet market, with geopolitical tensions and semiconductor shortages highlighting the strategic importance of this technology. Companies are investing in regional manufacturing capabilities to ensure resilience and security of supply for these critical components.

Data centers and cloud service providers represent the largest market segment, accounting for nearly 45% of the total chiplet market. These entities require increasingly powerful and energy-efficient computing solutions to handle the exponential growth in data processing demands. The adoption of UCIe (Universal Chiplet Interconnect Express) standards is accelerating this market segment's growth by enabling interoperability between chiplets from different vendors.

Consumer electronics constitutes the second-largest market segment, with high-end smartphones, tablets, and gaming consoles increasingly incorporating chiplet-based designs to deliver enhanced performance while managing thermal constraints. This segment is expected to grow significantly as manufacturers seek to differentiate their products through superior computing capabilities.

The automotive sector represents an emerging but rapidly growing market for chiplet-based solutions, particularly for advanced driver-assistance systems (ADAS) and autonomous driving platforms. These applications require high-performance, low-latency computing capabilities that can be efficiently delivered through specialized chiplet architectures.

Geographically, North America leads the chiplet market with approximately 40% market share, driven by the presence of major semiconductor companies and hyperscale data center operators. Asia-Pacific follows closely and is expected to demonstrate the highest growth rate, fueled by substantial investments in semiconductor manufacturing infrastructure in countries like Taiwan, South Korea, and China.

The market dynamics are further shaped by the increasing focus on AI and machine learning applications, which demand specialized accelerators that can be efficiently implemented using chiplet-based designs. The ability to mix and match different types of computing elements (CPU, GPU, TPU, memory) through high-speed UCIe interconnects is creating new opportunities for customized computing solutions tailored to specific workloads.

Supply chain considerations are becoming increasingly important in the chiplet market, with geopolitical tensions and semiconductor shortages highlighting the strategic importance of this technology. Companies are investing in regional manufacturing capabilities to ensure resilience and security of supply for these critical components.

Retimer and Equalization Technical Challenges

The implementation of UCIe (Universal Chiplet Interconnect Express) faces significant technical challenges in signal integrity as data rates increase beyond 16 GT/s. Signal degradation occurs due to channel loss, reflections, and crosstalk, requiring sophisticated retimer and equalization techniques to maintain reliable communication between chiplets.

Channel loss presents a primary obstacle, with high-frequency signal components experiencing severe attenuation through package traces, interposers, and PCB materials. At UCIe's target frequencies of 16-32 GT/s, the loss can exceed 20-30 dB, resulting in closed eye diagrams and increased bit error rates. This necessitates advanced equalization techniques to compensate for frequency-dependent losses.

Reflections caused by impedance discontinuities at die boundaries, C4 bumps, and package transitions further degrade signal quality. These discontinuities create signal reflections that interfere with the primary signal, causing inter-symbol interference (ISI) that compounds with increasing data rates. The compact nature of chiplet designs exacerbates this issue due to limited space for gradual transitions.

Crosstalk between adjacent channels represents another critical challenge. As UCIe implementations push for higher density interconnects, the proximity between channels increases electromagnetic coupling, introducing noise that reduces signal integrity. This is particularly problematic in advanced packaging technologies where signal lines may be separated by only a few microns.

Power delivery network (PDN) noise also impacts signal integrity. Voltage fluctuations in the power supply can couple into signal paths, creating jitter and reducing timing margins. The high-speed switching in UCIe interfaces demands clean power delivery, which becomes increasingly difficult as power density rises in chiplet designs.

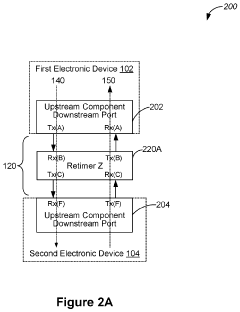

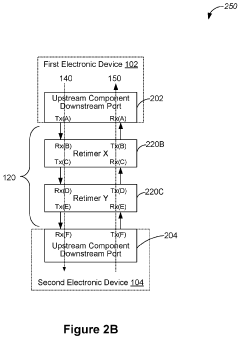

Retimer implementation faces its own set of challenges. Inserting retimers adds latency and power consumption, requiring careful optimization to maintain UCIe's performance advantages. The placement of retimers within the signal path is critical, as suboptimal positioning can introduce additional reflections and impedance mismatches.

Equalization techniques such as Feed-Forward Equalization (FFE), Decision Feedback Equalization (DFE), and Continuous Time Linear Equalization (CTLE) each present implementation tradeoffs. FFE can amplify noise while compensating for channel loss, DFE requires precise timing and increases circuit complexity, and CTLE struggles with varying channel characteristics across different chiplet configurations.

Temperature variations across chiplets further complicate equalization efforts, as channel characteristics change with temperature, potentially requiring adaptive equalization techniques that can respond to environmental changes during operation.

Channel loss presents a primary obstacle, with high-frequency signal components experiencing severe attenuation through package traces, interposers, and PCB materials. At UCIe's target frequencies of 16-32 GT/s, the loss can exceed 20-30 dB, resulting in closed eye diagrams and increased bit error rates. This necessitates advanced equalization techniques to compensate for frequency-dependent losses.

Reflections caused by impedance discontinuities at die boundaries, C4 bumps, and package transitions further degrade signal quality. These discontinuities create signal reflections that interfere with the primary signal, causing inter-symbol interference (ISI) that compounds with increasing data rates. The compact nature of chiplet designs exacerbates this issue due to limited space for gradual transitions.

Crosstalk between adjacent channels represents another critical challenge. As UCIe implementations push for higher density interconnects, the proximity between channels increases electromagnetic coupling, introducing noise that reduces signal integrity. This is particularly problematic in advanced packaging technologies where signal lines may be separated by only a few microns.

Power delivery network (PDN) noise also impacts signal integrity. Voltage fluctuations in the power supply can couple into signal paths, creating jitter and reducing timing margins. The high-speed switching in UCIe interfaces demands clean power delivery, which becomes increasingly difficult as power density rises in chiplet designs.

Retimer implementation faces its own set of challenges. Inserting retimers adds latency and power consumption, requiring careful optimization to maintain UCIe's performance advantages. The placement of retimers within the signal path is critical, as suboptimal positioning can introduce additional reflections and impedance mismatches.

Equalization techniques such as Feed-Forward Equalization (FFE), Decision Feedback Equalization (DFE), and Continuous Time Linear Equalization (CTLE) each present implementation tradeoffs. FFE can amplify noise while compensating for channel loss, DFE requires precise timing and increases circuit complexity, and CTLE struggles with varying channel characteristics across different chiplet configurations.

Temperature variations across chiplets further complicate equalization efforts, as channel characteristics change with temperature, potentially requiring adaptive equalization techniques that can respond to environmental changes during operation.

Current Retimer and Equalization Implementation Approaches

01 Retimer technology for signal integrity enhancement

Retimers are used to improve signal integrity in high-speed data transmission systems by regenerating signals. They sample incoming data, recover the clock, and retransmit clean signals with reduced jitter and noise. This technology helps maintain signal quality over longer distances and through multiple connection points, effectively extending the reach of high-speed interfaces while preserving data integrity.- Retimer technology for signal integrity enhancement: Retimers are used to improve signal integrity in high-speed data transmission systems by regenerating signals. They sample incoming data, recover the clock, and retransmit clean signals, effectively removing jitter and noise. This technology helps maintain signal quality over longer distances and through multiple connection points, making it essential for high-speed interfaces like PCIe, USB, and Ethernet connections.

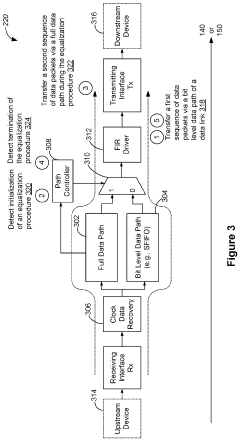

- Adaptive equalization techniques: Adaptive equalization techniques dynamically adjust to changing channel conditions to optimize signal integrity. These systems analyze incoming signals and automatically modify equalization parameters to compensate for channel impairments. They employ feedback mechanisms to continuously monitor signal quality and make real-time adjustments, ensuring optimal performance across varying operating conditions and data rates.

- Decision feedback equalization for high-speed interfaces: Decision feedback equalization (DFE) is a technique used in high-speed interfaces to mitigate inter-symbol interference. It works by using previously detected symbols to cancel out interference in the current symbol being detected. This approach is particularly effective for channels with severe frequency-dependent loss and reflections, making it valuable for maintaining signal integrity in high-speed serial links and backplane communications.

- System-level signal integrity solutions: System-level approaches to signal integrity involve comprehensive solutions that address multiple aspects of signal degradation. These include channel modeling, impedance matching, crosstalk reduction, and power integrity management. By considering the entire signal path from transmitter to receiver, these solutions optimize board layout, connector design, and system architecture to maintain signal quality across complex electronic systems.

- Advanced clock and data recovery mechanisms: Advanced clock and data recovery (CDR) mechanisms are essential components in retimers and equalizers that extract timing information from incoming data streams. These systems employ phase-locked loops, delay-locked loops, and other techniques to accurately recover clocks from jittery signals. Modern CDR implementations feature adaptive bandwidth control and jitter filtering capabilities to maintain timing accuracy under challenging signal conditions.

02 Adaptive equalization techniques for high-speed interfaces

Adaptive equalization techniques dynamically adjust to compensate for signal degradation in high-speed interfaces. These methods analyze incoming signals and automatically optimize equalization parameters to counter channel impairments such as attenuation, reflection, and crosstalk. By continuously adapting to changing channel conditions, these techniques maintain optimal signal integrity across various operating environments and data rates.Expand Specific Solutions03 Decision feedback equalization for signal recovery

Decision feedback equalization (DFE) is a powerful technique for mitigating intersymbol interference in high-speed data transmission. This method uses previously detected symbols to cancel out interference in the current symbol, effectively removing post-cursor ISI. DFE implementations can include multiple feedback taps to address various channel impairments, providing significant improvements in signal integrity for complex communication channels.Expand Specific Solutions04 PCIe and high-speed bus signal integrity solutions

Signal integrity solutions specifically designed for PCIe and other high-speed bus architectures address the unique challenges of maintaining data integrity at increasing speeds. These solutions incorporate specialized retiming, equalization, and jitter reduction techniques to ensure reliable data transmission across computer system interconnects. Advanced implementations may include lane-specific optimization, power management features, and compatibility with multiple PCIe generations.Expand Specific Solutions05 Testing and verification methods for signal integrity

Comprehensive testing and verification methods are essential for ensuring signal integrity in high-speed systems. These approaches include eye diagram analysis, bit error rate testing, and jitter measurement techniques to quantify signal quality. Advanced test methodologies may incorporate channel modeling, simulation tools, and automated calibration procedures to validate equalization and retiming implementations across various operating conditions and manufacturing variations.Expand Specific Solutions

Leading Companies in UCIe Ecosystem

The UCIe chiplet interconnect technology landscape is currently in its early growth phase, with a rapidly expanding market driven by increasing demand for high-performance computing solutions. The market is projected to grow significantly as chiplet-based designs become more prevalent in data centers, AI applications, and high-performance computing. Key players Intel, Qualcomm, and Samsung are leading technical innovation in retimer and equalization techniques, with Intel particularly establishing early standards leadership. Companies like Kandou Labs are developing specialized signal integrity solutions, while Huawei and Chinese firms such as Inspur and Xindong Microelectronics are making strategic investments to reduce technological gaps. The technology is approaching maturity in standardization but continues to evolve in implementation, with ongoing research at institutions like the National University of Defense Technology and The Ohio State University advancing next-generation solutions.

Intel Corp.

Technical Solution: Intel作为UCIe联盟的创始成员和主要推动者,开发了先进的Retimer技术用于芯粒互连。其技术方案采用自适应均衡器(AEQ)和决策反馈均衡器(DFE)相结合的架构,能够在UCIe标准下实现高达16GT/s的数据传输速率。Intel的Retimer设计包含多级均衡电路,可以有效补偿PCB走线和封装引起的信号损耗。特别是,Intel开发的低功耗CMOS Retimer技术能够在每通道功耗低于20mW的情况下提供完整的信号重定时和均衡功能,支持UCIe标准要求的低延迟和高带宽特性。Intel还实现了自适应阈值调整技术,可以根据信道特性动态优化信号检测阈值,提高信号完整性和系统可靠性。

优势:作为UCIe标准的主要推动者,Intel拥有完整的芯粒互连技术栈和生态系统支持;其Retimer技术在功耗效率和信号完整性方面表现出色;具有强大的制造能力和系统集成经验。劣势:其专有技术可能导致与其他厂商解决方案的互操作性挑战;技术实现复杂度较高,可能增加成本。

QUALCOMM, Inc.

Technical Solution: Qualcomm在UCIe芯粒互连领域开发了专门针对移动和边缘计算场景的Retimer和均衡技术。其技术方案基于自研的低功耗信号处理架构,采用混合均衡技术,结合前馈均衡(FFE)和连续时间线性均衡(CTLE),能够在功耗敏感的应用中提供出色的信号完整性。Qualcomm的Retimer设计特别注重降低延迟,采用创新的时钟恢复电路,将信号重定时延迟控制在10ps以内,同时支持UCIe标准的多种速率模式。其均衡技术采用自适应算法,可根据信道特性和环境变化动态调整均衡参数,确保在不同工作条件下维持最佳性能。Qualcomm还开发了专用的测试和验证方法,用于评估UCIe链路在各种工作条件下的性能和可靠性,包括温度变化、电源噪声和制造工艺偏差等因素的影响。

优势:在低功耗高效能设计方面具有丰富经验,特别适合移动和边缘计算设备;自适应均衡技术能够适应多种工作环境;拥有强大的系统级集成能力。劣势:相比服务器和数据中心领域的专业厂商,在超高速信号处理方面的经验相对较少;技术方案可能更侧重于特定应用场景。

Key Patents and Research in UCIe Signal Integrity

Technologies for optimizing transmitter equalization with high-speed retimer

PatentInactiveUS20190044760A1

Innovation

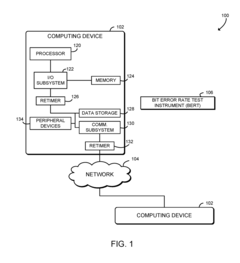

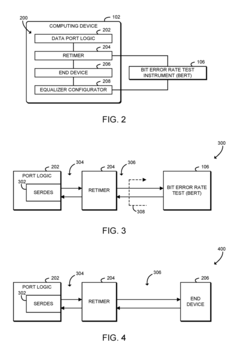

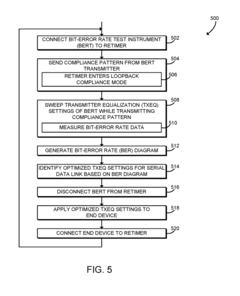

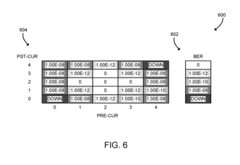

- A system that includes a computing device with retimers connected to high-speed serial data links, utilizing a bit-error rate test instrument (BERT) to sweep through multiple transmitter equalization settings, measure bit-error rate data, and apply optimized settings to the end device, thereby improving signal integrity and margin across the entire serial link.

Seamless bit-level low-latency retimer for data links

PatentActiveUS11159353B1

Innovation

- A retimer system integrating both a full data path and a bit-level data path, where the bit-level path is used for low-latency data transfer and seamlessly switches to the full data path during equalization procedures to reduce latency and maintain signal quality.

Thermal Management Considerations for UCIe Implementation

Thermal management represents a critical challenge in the implementation of UCIe (Universal Chiplet Interconnect Express) technology, particularly when considering retimer and equalization techniques. As chiplet designs become more prevalent in high-performance computing systems, the thermal implications of these interconnect technologies demand careful consideration.

The integration of retimers and equalization circuits in UCIe implementations introduces additional heat sources within already densely packed chiplet architectures. These components, while essential for maintaining signal integrity across high-speed links, generate significant thermal loads during operation. Typical retimer circuits can dissipate between 0.5W to 2W per channel, depending on data rates and equalization complexity.

Thermal coupling between adjacent chiplets presents another significant challenge. When multiple chiplets are placed in close proximity on an interposer or package substrate, heat generated by retimer circuits can affect neighboring components, potentially degrading their performance or reliability. This thermal interdependence necessitates holistic thermal management approaches that consider the entire package rather than individual components.

Advanced cooling solutions specifically designed for UCIe implementations include embedded microfluidic channels, phase-change materials, and thermally conductive adhesives. These technologies aim to efficiently extract heat from retimer and equalization circuits while maintaining the compact form factor that makes chiplet architectures attractive.

Thermal simulation and modeling have become essential tools in the design phase of UCIe implementations. Computational fluid dynamics (CFD) and finite element analysis (FEA) enable designers to predict hotspots and optimize component placement to minimize thermal issues. These simulations must account for the unique thermal characteristics of retimer circuits, including their dynamic power profiles during different operating conditions.

Power management techniques also play a crucial role in thermal control. Adaptive equalization algorithms that minimize power consumption while maintaining signal integrity can significantly reduce thermal loads. Similarly, dynamic power scaling of retimer circuits based on workload requirements helps manage thermal challenges without compromising performance.

The industry is moving toward standardized thermal metrics and testing methodologies specific to chiplet interconnects. These standards will enable better comparison between different UCIe implementations and provide guidelines for thermal design power (TDP) budgeting across complex multi-chiplet systems. Organizations like JEDEC and UCIe Consortium are actively working to establish these thermal characterization frameworks.

The integration of retimers and equalization circuits in UCIe implementations introduces additional heat sources within already densely packed chiplet architectures. These components, while essential for maintaining signal integrity across high-speed links, generate significant thermal loads during operation. Typical retimer circuits can dissipate between 0.5W to 2W per channel, depending on data rates and equalization complexity.

Thermal coupling between adjacent chiplets presents another significant challenge. When multiple chiplets are placed in close proximity on an interposer or package substrate, heat generated by retimer circuits can affect neighboring components, potentially degrading their performance or reliability. This thermal interdependence necessitates holistic thermal management approaches that consider the entire package rather than individual components.

Advanced cooling solutions specifically designed for UCIe implementations include embedded microfluidic channels, phase-change materials, and thermally conductive adhesives. These technologies aim to efficiently extract heat from retimer and equalization circuits while maintaining the compact form factor that makes chiplet architectures attractive.

Thermal simulation and modeling have become essential tools in the design phase of UCIe implementations. Computational fluid dynamics (CFD) and finite element analysis (FEA) enable designers to predict hotspots and optimize component placement to minimize thermal issues. These simulations must account for the unique thermal characteristics of retimer circuits, including their dynamic power profiles during different operating conditions.

Power management techniques also play a crucial role in thermal control. Adaptive equalization algorithms that minimize power consumption while maintaining signal integrity can significantly reduce thermal loads. Similarly, dynamic power scaling of retimer circuits based on workload requirements helps manage thermal challenges without compromising performance.

The industry is moving toward standardized thermal metrics and testing methodologies specific to chiplet interconnects. These standards will enable better comparison between different UCIe implementations and provide guidelines for thermal design power (TDP) budgeting across complex multi-chiplet systems. Organizations like JEDEC and UCIe Consortium are actively working to establish these thermal characterization frameworks.

Standardization and Interoperability Framework

The Universal Chiplet Interconnect Express (UCIe) represents a pivotal advancement in chiplet-based system design, necessitating robust standardization and interoperability frameworks to ensure seamless integration across diverse semiconductor technologies. The UCIe consortium, established in 2022, has developed comprehensive specifications that address signal integrity challenges through standardized retiming and equalization techniques.

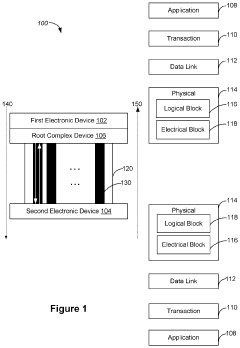

The UCIe 1.0 specification defines a multi-layered approach to standardization, encompassing physical layer, protocol layer, and software stack requirements. This hierarchical framework ensures that retiming and equalization implementations maintain consistency across different vendor solutions while accommodating technological variations. The physical layer specifications explicitly define parameters for transmitter equalization, receiver adaptation, and retimer functionality, establishing clear benchmarks for signal integrity performance.

Interoperability testing methodologies constitute a critical component of the UCIe framework, with defined procedures for validating equalization performance across heterogeneous chiplet interfaces. These methodologies include standardized test patterns, compliance criteria, and certification processes that verify proper implementation of equalization techniques across different silicon processes and packaging technologies.

The UCIe specification incorporates adaptive equalization protocols that enable dynamic optimization of signal integrity parameters based on channel characteristics. This adaptability is crucial for maintaining reliable communication across varying die-to-die distances and different substrate materials, with standardized training sequences facilitating automatic calibration of equalization settings during system initialization.

Cross-vendor compatibility represents a cornerstone of the UCIe framework, with standardized equalization coefficients and retimer specifications ensuring that chiplets from different manufacturers can effectively communicate. The specification defines mandatory equalization profiles that all UCIe-compliant devices must support, alongside optional enhanced profiles for specialized applications requiring higher performance.

The UCIe consortium has established a certification program for validating compliance with equalization and retiming standards, providing manufacturers with clear guidelines for implementation and testing. This program includes reference designs, compliance test suites, and interoperability workshops that facilitate industry-wide adoption of standardized signal integrity techniques.

Future roadmap considerations within the UCIe standardization framework address evolving requirements for higher data rates, reduced power consumption, and enhanced signal integrity. The consortium's working groups are actively developing specifications for advanced equalization techniques, including machine learning-based adaptation algorithms and enhanced decision feedback equalization methods, ensuring the standard remains relevant as chiplet technology continues to evolve.

The UCIe 1.0 specification defines a multi-layered approach to standardization, encompassing physical layer, protocol layer, and software stack requirements. This hierarchical framework ensures that retiming and equalization implementations maintain consistency across different vendor solutions while accommodating technological variations. The physical layer specifications explicitly define parameters for transmitter equalization, receiver adaptation, and retimer functionality, establishing clear benchmarks for signal integrity performance.

Interoperability testing methodologies constitute a critical component of the UCIe framework, with defined procedures for validating equalization performance across heterogeneous chiplet interfaces. These methodologies include standardized test patterns, compliance criteria, and certification processes that verify proper implementation of equalization techniques across different silicon processes and packaging technologies.

The UCIe specification incorporates adaptive equalization protocols that enable dynamic optimization of signal integrity parameters based on channel characteristics. This adaptability is crucial for maintaining reliable communication across varying die-to-die distances and different substrate materials, with standardized training sequences facilitating automatic calibration of equalization settings during system initialization.

Cross-vendor compatibility represents a cornerstone of the UCIe framework, with standardized equalization coefficients and retimer specifications ensuring that chiplets from different manufacturers can effectively communicate. The specification defines mandatory equalization profiles that all UCIe-compliant devices must support, alongside optional enhanced profiles for specialized applications requiring higher performance.

The UCIe consortium has established a certification program for validating compliance with equalization and retiming standards, providing manufacturers with clear guidelines for implementation and testing. This program includes reference designs, compliance test suites, and interoperability workshops that facilitate industry-wide adoption of standardized signal integrity techniques.

Future roadmap considerations within the UCIe standardization framework address evolving requirements for higher data rates, reduced power consumption, and enhanced signal integrity. The consortium's working groups are actively developing specifications for advanced equalization techniques, including machine learning-based adaptation algorithms and enhanced decision feedback equalization methods, ensuring the standard remains relevant as chiplet technology continues to evolve.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!