IP Licensing And Ecosystem For UCIe Chiplet Interconnect

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Background and Objectives

The Universal Chiplet Interconnect Express (UCIe) represents a paradigm shift in semiconductor design and manufacturing, emerging as a response to the slowing of Moore's Law and the increasing complexity of chip design. Historically, semiconductor advancement has been driven by transistor scaling, but physical limitations and economic constraints have necessitated alternative approaches to continue performance improvements. UCIe addresses this challenge by enabling a disaggregated chip design methodology, where complex systems can be built from smaller, specialized chiplets rather than monolithic dies.

The evolution of chiplet technology began with proprietary solutions from companies like AMD and Intel, but the industry recognized the need for standardization to foster broader adoption and ecosystem development. In March 2022, the UCIe consortium was formed by industry leaders including Intel, AMD, Arm, TSMC, Samsung, and others, marking a significant milestone in collaborative semiconductor innovation. The consortium's primary goal was to establish an open standard for die-to-die interconnects that would enable interoperability between chiplets from different vendors.

UCIe aims to create a "plug-and-play" ecosystem for chiplets, similar to how USB revolutionized peripheral connectivity in computing. The standard encompasses both physical layer specifications and protocol layers, providing a comprehensive framework for chiplet integration. This standardization is crucial for reducing design complexity, accelerating time-to-market, and enabling more cost-effective semiconductor solutions.

The technical objectives of UCIe include achieving high-bandwidth, low-latency communication between chiplets with minimal power consumption. The standard supports data rates starting at 16 GT/s in its first iteration, with a roadmap for future enhancements. Additionally, UCIe addresses thermal management, signal integrity, and testing methodologies critical for reliable multi-chiplet systems.

From a strategic perspective, UCIe aims to democratize advanced semiconductor design by allowing smaller companies to focus on specialized chiplets rather than complete SoCs. This could potentially reshape the semiconductor value chain, enabling more diverse participation in cutting-edge technology development. The standard also seeks to address supply chain resilience by facilitating a more modular approach to chip design and manufacturing.

The long-term vision for UCIe extends beyond technical specifications to encompass a comprehensive ecosystem including design tools, testing methodologies, and manufacturing processes. This holistic approach is essential for realizing the full potential of chiplet-based design and establishing UCIe as the dominant standard for heterogeneous integration in the semiconductor industry.

The evolution of chiplet technology began with proprietary solutions from companies like AMD and Intel, but the industry recognized the need for standardization to foster broader adoption and ecosystem development. In March 2022, the UCIe consortium was formed by industry leaders including Intel, AMD, Arm, TSMC, Samsung, and others, marking a significant milestone in collaborative semiconductor innovation. The consortium's primary goal was to establish an open standard for die-to-die interconnects that would enable interoperability between chiplets from different vendors.

UCIe aims to create a "plug-and-play" ecosystem for chiplets, similar to how USB revolutionized peripheral connectivity in computing. The standard encompasses both physical layer specifications and protocol layers, providing a comprehensive framework for chiplet integration. This standardization is crucial for reducing design complexity, accelerating time-to-market, and enabling more cost-effective semiconductor solutions.

The technical objectives of UCIe include achieving high-bandwidth, low-latency communication between chiplets with minimal power consumption. The standard supports data rates starting at 16 GT/s in its first iteration, with a roadmap for future enhancements. Additionally, UCIe addresses thermal management, signal integrity, and testing methodologies critical for reliable multi-chiplet systems.

From a strategic perspective, UCIe aims to democratize advanced semiconductor design by allowing smaller companies to focus on specialized chiplets rather than complete SoCs. This could potentially reshape the semiconductor value chain, enabling more diverse participation in cutting-edge technology development. The standard also seeks to address supply chain resilience by facilitating a more modular approach to chip design and manufacturing.

The long-term vision for UCIe extends beyond technical specifications to encompass a comprehensive ecosystem including design tools, testing methodologies, and manufacturing processes. This holistic approach is essential for realizing the full potential of chiplet-based design and establishing UCIe as the dominant standard for heterogeneous integration in the semiconductor industry.

Market Analysis for Chiplet-Based Computing Solutions

The chiplet-based computing solutions market is experiencing unprecedented growth, driven by the increasing demand for high-performance computing in data centers, AI applications, and edge computing. As traditional monolithic chip designs reach physical and economic limits, chiplet architecture has emerged as a revolutionary approach that allows for more efficient integration of heterogeneous components. The global market for chiplet-based solutions is projected to grow at a compound annual growth rate of 38% through 2028, reaching a market value of 57 billion dollars by the end of the forecast period.

The demand for chiplet technology is particularly strong in the high-performance computing (HPC) segment, where the need for specialized accelerators and custom silicon solutions continues to expand. Cloud service providers and hyperscalers represent the largest customer segment, accounting for approximately 45% of the current market demand, as they seek to optimize performance per watt and reduce total cost of ownership in their massive data centers.

UCIe (Universal Chiplet Interconnect Express) has emerged as a critical standard in this landscape, with market adoption accelerating since its introduction. Companies implementing UCIe-compliant designs are reporting 30% improvements in system performance and 25% reductions in power consumption compared to traditional monolithic approaches. This performance advantage is driving rapid market penetration, with UCIe-based solutions expected to capture 65% of the chiplet interconnect market by 2026.

From a regional perspective, North America currently leads the chiplet market with 42% share, followed by Asia-Pacific at 38% and Europe at 17%. However, the fastest growth is occurring in the Asia-Pacific region, particularly in Taiwan, South Korea, and China, where major semiconductor manufacturers are heavily investing in chiplet manufacturing capabilities and ecosystem development.

The market is segmented by application into data centers (48%), consumer electronics (22%), automotive (15%), telecommunications (10%), and others (5%). The data center segment dominates due to the immediate benefits chiplets offer in terms of customization, performance scaling, and thermal management for server applications.

Key market drivers include the rising costs of monolithic chip development at advanced nodes, increasing demand for specialized accelerators for AI/ML workloads, and the need for more efficient power consumption in data centers. Additionally, supply chain resilience has become a significant factor, with chiplet-based designs offering greater flexibility in sourcing components from different manufacturers and process nodes.

The demand for chiplet technology is particularly strong in the high-performance computing (HPC) segment, where the need for specialized accelerators and custom silicon solutions continues to expand. Cloud service providers and hyperscalers represent the largest customer segment, accounting for approximately 45% of the current market demand, as they seek to optimize performance per watt and reduce total cost of ownership in their massive data centers.

UCIe (Universal Chiplet Interconnect Express) has emerged as a critical standard in this landscape, with market adoption accelerating since its introduction. Companies implementing UCIe-compliant designs are reporting 30% improvements in system performance and 25% reductions in power consumption compared to traditional monolithic approaches. This performance advantage is driving rapid market penetration, with UCIe-based solutions expected to capture 65% of the chiplet interconnect market by 2026.

From a regional perspective, North America currently leads the chiplet market with 42% share, followed by Asia-Pacific at 38% and Europe at 17%. However, the fastest growth is occurring in the Asia-Pacific region, particularly in Taiwan, South Korea, and China, where major semiconductor manufacturers are heavily investing in chiplet manufacturing capabilities and ecosystem development.

The market is segmented by application into data centers (48%), consumer electronics (22%), automotive (15%), telecommunications (10%), and others (5%). The data center segment dominates due to the immediate benefits chiplets offer in terms of customization, performance scaling, and thermal management for server applications.

Key market drivers include the rising costs of monolithic chip development at advanced nodes, increasing demand for specialized accelerators for AI/ML workloads, and the need for more efficient power consumption in data centers. Additionally, supply chain resilience has become a significant factor, with chiplet-based designs offering greater flexibility in sourcing components from different manufacturers and process nodes.

UCIe Technology Status and Implementation Challenges

Universal Chiplet Interconnect Express (UCIe) represents a significant advancement in chiplet technology, yet its current implementation faces several notable challenges. The technology, while promising, is still in its early stages of development with the 1.0 specification released only in 2022. This nascent status means that comprehensive industry-wide adoption remains limited, with only a handful of companies actively implementing UCIe solutions in production environments.

One of the primary technical challenges involves the physical implementation of die-to-die connections. The ultra-fine pitch interconnects required for UCIe demand extremely precise manufacturing processes, with tolerances measured in micrometers. This level of precision presents significant yield challenges in high-volume manufacturing scenarios, particularly for companies without access to advanced packaging facilities.

Signal integrity issues also pose substantial obstacles. As data rates increase to meet bandwidth demands, maintaining signal quality across the die-to-die interfaces becomes increasingly difficult. Cross-talk, electromagnetic interference, and power integrity concerns all compound at higher frequencies, requiring sophisticated design techniques and potentially costly materials to mitigate.

Thermal management represents another critical challenge. The dense integration of multiple chiplets creates concentrated heat zones that can be difficult to dissipate effectively. This thermal density can lead to performance throttling, reliability concerns, and ultimately reduced product lifespans if not properly addressed through advanced cooling solutions.

Testing methodologies for UCIe implementations remain underdeveloped. Traditional testing approaches are often insufficient for validating die-to-die interfaces at scale, necessitating new test strategies and equipment investments. The lack of standardized testing protocols further complicates quality assurance processes across the supply chain.

From a geographical perspective, UCIe technology development is currently concentrated primarily in North America and East Asia, with companies like Intel, AMD, TSMC, and Samsung leading research efforts. European involvement has been more limited, though recent initiatives suggest growing interest in the region.

The ecosystem supporting UCIe remains fragmented, with interoperability between different vendors' implementations still presenting challenges. While the UCIe consortium has established baseline specifications, the practical implementation details often vary between companies, creating potential compatibility issues that must be resolved for the technology to reach its full potential.

One of the primary technical challenges involves the physical implementation of die-to-die connections. The ultra-fine pitch interconnects required for UCIe demand extremely precise manufacturing processes, with tolerances measured in micrometers. This level of precision presents significant yield challenges in high-volume manufacturing scenarios, particularly for companies without access to advanced packaging facilities.

Signal integrity issues also pose substantial obstacles. As data rates increase to meet bandwidth demands, maintaining signal quality across the die-to-die interfaces becomes increasingly difficult. Cross-talk, electromagnetic interference, and power integrity concerns all compound at higher frequencies, requiring sophisticated design techniques and potentially costly materials to mitigate.

Thermal management represents another critical challenge. The dense integration of multiple chiplets creates concentrated heat zones that can be difficult to dissipate effectively. This thermal density can lead to performance throttling, reliability concerns, and ultimately reduced product lifespans if not properly addressed through advanced cooling solutions.

Testing methodologies for UCIe implementations remain underdeveloped. Traditional testing approaches are often insufficient for validating die-to-die interfaces at scale, necessitating new test strategies and equipment investments. The lack of standardized testing protocols further complicates quality assurance processes across the supply chain.

From a geographical perspective, UCIe technology development is currently concentrated primarily in North America and East Asia, with companies like Intel, AMD, TSMC, and Samsung leading research efforts. European involvement has been more limited, though recent initiatives suggest growing interest in the region.

The ecosystem supporting UCIe remains fragmented, with interoperability between different vendors' implementations still presenting challenges. While the UCIe consortium has established baseline specifications, the practical implementation details often vary between companies, creating potential compatibility issues that must be resolved for the technology to reach its full potential.

Current IP Licensing Models for Chiplet Interconnect

01 UCIe chiplet interconnect architecture and standards

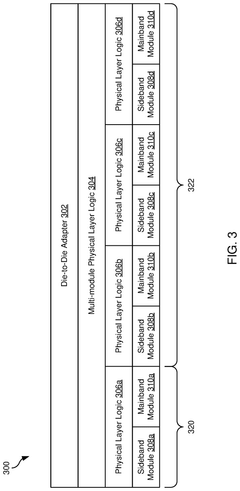

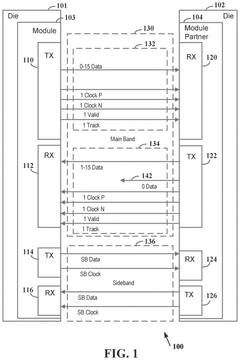

The Universal Chiplet Interconnect Express (UCIe) architecture provides standardized interfaces for connecting multiple chiplets within a package. This technology enables high-bandwidth, low-latency communication between different chiplets, supporting heterogeneous integration of various semiconductor components. The UCIe standard defines protocols, physical layer specifications, and electrical characteristics to ensure interoperability between chiplets from different vendors.- UCIe Chiplet Interconnect Architecture and Standards: Universal Chiplet Interconnect Express (UCIe) provides a standardized architecture for connecting multiple chiplets within a package. This technology defines physical layer specifications, protocols, and electrical interfaces that enable high-bandwidth, low-latency communication between different chiplets. The standardization allows for interoperability between chiplets from different manufacturers, creating a more flexible ecosystem for heterogeneous integration in advanced semiconductor packaging.

- IP Licensing Models for UCIe Technology: Various licensing models have been developed for UCIe chiplet interconnect intellectual property. These include patent pools, direct licensing agreements, and consortium-based licensing frameworks. The licensing structures typically address royalty rates, cross-licensing provisions, and compliance certification requirements. These models aim to balance fair compensation for IP holders while promoting widespread adoption of the UCIe standard across the semiconductor industry.

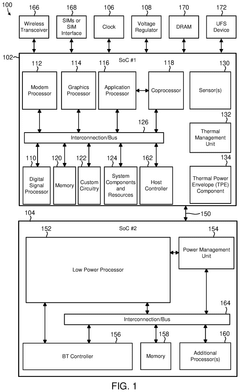

- Implementation of UCIe in Multi-Die Systems: UCIe technology enables the implementation of complex multi-die systems by providing standardized interfaces between chiplets. This approach allows system designers to combine different functional blocks (such as processors, memory, and specialized accelerators) from various vendors into a single package. The implementation includes die-to-die bridges, physical layer interfaces, and protocol translation mechanisms that maintain signal integrity across the interconnect while supporting high data transfer rates and power efficiency.

- Testing and Validation Methods for UCIe Compliance: Specialized testing and validation methodologies have been developed to ensure compliance with UCIe specifications. These include electrical characterization of die-to-die interfaces, protocol verification, and interoperability testing between chiplets from different vendors. The validation processes typically involve test chips, specialized equipment for high-speed signal analysis, and compliance test suites that verify adherence to the UCIe standard across various operating conditions and manufacturing processes.

- Security and Authentication in UCIe Implementations: Security mechanisms for UCIe chiplet interconnects address concerns related to intellectual property protection, data integrity, and authentication between chiplets. These include secure boot protocols, encrypted communication channels between dies, and hardware-based security features integrated into the interconnect fabric. The security architecture enables trusted execution environments across heterogeneous chiplets while preventing unauthorized access to sensitive data or intellectual property within the multi-die package.

02 IP licensing models for UCIe technology

Various licensing models exist for UCIe chiplet interconnect intellectual property, including patent pools, direct licensing, and open-source approaches. These models facilitate the adoption and implementation of UCIe technology across the semiconductor industry. Licensing agreements typically cover the use of patented technologies related to chiplet interfaces, communication protocols, and integration methodologies, enabling companies to incorporate UCIe-compliant interconnects into their designs.Expand Specific Solutions03 Testing and validation of UCIe-compliant chiplet interfaces

Testing and validation methodologies for UCIe-compliant chiplet interfaces ensure proper functionality and interoperability between different chiplets. These methods include electrical testing, protocol compliance verification, and system-level validation. Advanced testing techniques help identify and resolve issues related to signal integrity, power consumption, and thermal management in multi-chiplet packages, ensuring reliable operation of UCIe interconnects under various conditions.Expand Specific Solutions04 Integration of UCIe with advanced packaging technologies

UCIe chiplet interconnect technology can be integrated with various advanced packaging solutions, including 2.5D and 3D integration approaches. This integration enables the creation of complex systems-in-package with optimized performance, power efficiency, and form factor. The combination of UCIe with advanced packaging technologies facilitates the development of heterogeneous computing platforms that leverage chiplets manufactured using different process nodes and technologies.Expand Specific Solutions05 Security and authentication mechanisms for UCIe chiplet ecosystems

Security and authentication mechanisms are essential for protecting intellectual property and ensuring trusted operation in UCIe chiplet ecosystems. These mechanisms include secure boot processes, cryptographic authentication of chiplets, and protection against side-channel attacks. Implementing robust security features in UCIe interfaces helps prevent unauthorized access to sensitive data and functionality, while enabling secure communication between chiplets from different vendors.Expand Specific Solutions

Key Industry Players in UCIe Ecosystem

The UCIe chiplet interconnect technology is currently in an early growth phase, with significant industry momentum building. The market is projected to expand rapidly as chiplet-based designs become more prevalent in high-performance computing, AI, and data center applications. While the technology is still maturing, major semiconductor players are actively establishing the ecosystem. Intel leads as a founding member of the UCIe consortium, with Qualcomm, AMD (formerly Xilinx), Samsung, and IBM providing strong support. Chinese companies like Huawei and ZTE are also entering this space, indicating global interest. The ecosystem is evolving through collaborative IP licensing models, with companies like ARM contributing to standardization efforts. This diverse participation suggests UCIe is gaining traction as the preferred open standard for chiplet interconnection across the industry.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed a comprehensive UCIe implementation strategy focused on mobile and edge computing applications. Their approach leverages their expertise in system-on-chip design to create a flexible chiplet ecosystem optimized for power efficiency. Qualcomm's UCIe implementation features a die-to-die PHY layer achieving up to 16 GT/s data rates while maintaining power efficiency below 0.5 pJ/bit, critical for mobile applications. Their IP licensing model for UCIe technology includes both standard-essential patents and implementation-specific IP blocks, with licensing terms structured to encourage adoption across the mobile ecosystem. Qualcomm has developed specialized protocol adapters that bridge between UCIe and their proprietary interconnects, allowing gradual migration of existing designs. Their ecosystem approach emphasizes interoperability with third-party chiplets while providing optimized performance when using multiple Qualcomm-designed components together, creating a "better together" value proposition for licensees.

Strengths: Qualcomm's extensive experience in mobile SoC design gives them unique insights into power-constrained chiplet implementations. Their established licensing programs provide a ready framework for UCIe IP distribution. Weaknesses: Their focus on mobile applications may limit applicability in high-performance computing contexts. Some aspects of their implementation may favor their own processor architectures.

Intel Corp.

Technical Solution: Intel is a founding member and key driver of the UCIe (Universal Chiplet Interconnect Express) standard. Their technology approach centers on their Advanced Interface Bus (AIB) which formed the foundation for UCIe 1.0 specifications. Intel's implementation focuses on die-to-die interconnects that enable high-bandwidth, low-latency communication between chiplets at energy efficiencies of 0.5-1 pJ/bit. Their Embedded Multi-die Interconnect Bridge (EMIB) technology serves as a high-density interconnect pathway between chiplets, allowing for thousands of connections with minimal latency. Intel has developed a comprehensive IP licensing model that provides both hard and soft IP cores to ecosystem partners, with tiered licensing options based on production volume and application requirements. Their strategy emphasizes an open ecosystem approach, allowing partners to integrate Intel-designed chiplets with third-party components while maintaining standardized interfaces.

Strengths: As a founding member of UCIe, Intel has significant influence over standard development and extensive IP portfolio. Their established manufacturing capabilities enable rapid commercialization of UCIe-based designs. Weaknesses: Intel's licensing terms may favor larger partners, potentially creating barriers for smaller innovators. Their implementation may prioritize compatibility with Intel's own processor architectures.

Critical Patents and Technical Specifications for UCIe

Mechanism To Improve The Reliability Of Sideband In Chiplets

PatentPendingUS20250086136A1

Innovation

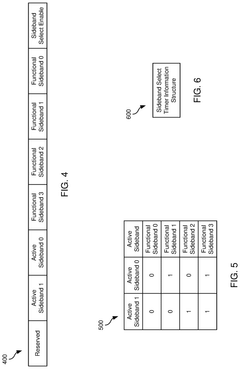

- The method involves transitioning the UCIe link from an active state to a reset state and then initializing a different functional sideband, allowing for runtime configuration of sidebands and aggregation of multiple sidebands to enhance communication reliability and throughput.

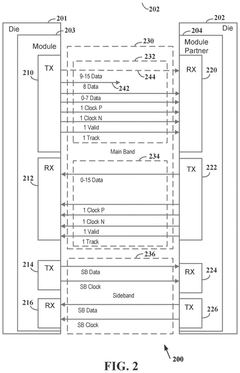

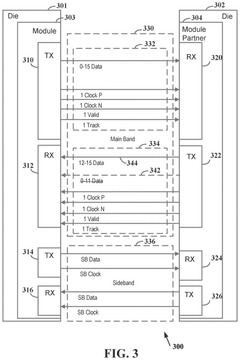

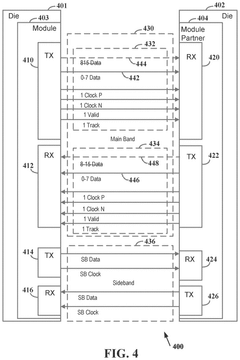

Variable link width in two directions for main band chip module connection

PatentPendingUS20240354279A1

Innovation

- Implementing a method to establish a die-to-die connection with a variable link width, allowing for independent configuration of transmit and receive data lanes through a sideband communication, enabling operation with different numbers of active data lanes in each direction to optimize power usage and data rates, and supporting fault tolerance by excluding faulty lines.

Interoperability and Standardization Efforts

The UCIe (Universal Chiplet Interconnect Express) standard represents a pivotal advancement in chiplet technology, with interoperability and standardization efforts forming the cornerstone of its ecosystem development. The consortium behind UCIe, which includes industry giants like Intel, AMD, Arm, TSMC, and Samsung, has established a comprehensive framework for ensuring seamless integration across different vendors' chiplets.

The standardization process for UCIe has been methodically structured into multiple layers, addressing physical, protocol, and software aspects of chiplet interconnection. At the physical layer, the standard defines precise electrical specifications, including signal integrity parameters, power delivery requirements, and thermal considerations. The protocol layer standardizes communication protocols, data formats, and error handling mechanisms, while the software layer focuses on driver interfaces and management frameworks.

Interoperability testing and certification programs have been implemented to validate compliance with UCIe specifications. These programs include rigorous testing methodologies for verifying electrical characteristics, protocol conformance, and system-level integration. The UCIe consortium has established dedicated testing facilities and third-party certification bodies to ensure objective evaluation of chiplet components against the standard.

Cross-vendor validation initiatives have emerged as a critical component of the UCIe ecosystem. These collaborative efforts involve multiple semiconductor manufacturers working together to verify interoperability between their respective chiplet implementations. Such initiatives have accelerated the maturation of the UCIe standard by identifying and addressing integration challenges early in the development cycle.

The UCIe standard incorporates provisions for backward compatibility and future extensibility, ensuring longevity and adaptability of the ecosystem. Version control mechanisms and clear migration paths have been defined to facilitate the evolution of the standard while maintaining compatibility with existing implementations. This approach protects investments in UCIe technology while enabling continuous innovation.

International standards organizations, including IEEE and JEDEC, have engaged with the UCIe consortium to align the standard with broader industry frameworks. This collaboration has enhanced the credibility and adoption potential of UCIe across global markets. Additionally, regional standardization bodies in North America, Europe, and Asia have begun incorporating UCIe specifications into their respective semiconductor industry guidelines.

Open-source reference implementations and development tools have been released to lower barriers to entry for new participants in the UCIe ecosystem. These resources include simulation models, verification suites, and design examples that facilitate the adoption of UCIe technology by smaller companies and academic institutions, thereby expanding the diversity and innovation potential of the ecosystem.

The standardization process for UCIe has been methodically structured into multiple layers, addressing physical, protocol, and software aspects of chiplet interconnection. At the physical layer, the standard defines precise electrical specifications, including signal integrity parameters, power delivery requirements, and thermal considerations. The protocol layer standardizes communication protocols, data formats, and error handling mechanisms, while the software layer focuses on driver interfaces and management frameworks.

Interoperability testing and certification programs have been implemented to validate compliance with UCIe specifications. These programs include rigorous testing methodologies for verifying electrical characteristics, protocol conformance, and system-level integration. The UCIe consortium has established dedicated testing facilities and third-party certification bodies to ensure objective evaluation of chiplet components against the standard.

Cross-vendor validation initiatives have emerged as a critical component of the UCIe ecosystem. These collaborative efforts involve multiple semiconductor manufacturers working together to verify interoperability between their respective chiplet implementations. Such initiatives have accelerated the maturation of the UCIe standard by identifying and addressing integration challenges early in the development cycle.

The UCIe standard incorporates provisions for backward compatibility and future extensibility, ensuring longevity and adaptability of the ecosystem. Version control mechanisms and clear migration paths have been defined to facilitate the evolution of the standard while maintaining compatibility with existing implementations. This approach protects investments in UCIe technology while enabling continuous innovation.

International standards organizations, including IEEE and JEDEC, have engaged with the UCIe consortium to align the standard with broader industry frameworks. This collaboration has enhanced the credibility and adoption potential of UCIe across global markets. Additionally, regional standardization bodies in North America, Europe, and Asia have begun incorporating UCIe specifications into their respective semiconductor industry guidelines.

Open-source reference implementations and development tools have been released to lower barriers to entry for new participants in the UCIe ecosystem. These resources include simulation models, verification suites, and design examples that facilitate the adoption of UCIe technology by smaller companies and academic institutions, thereby expanding the diversity and innovation potential of the ecosystem.

Legal and Competitive Implications of UCIe Licensing

The UCIe (Universal Chiplet Interconnect Express) licensing framework represents a critical component in the evolving chiplet ecosystem, with significant legal and competitive implications for industry participants. The consortium's approach to intellectual property licensing establishes a foundation that balances open industry adoption with protection of proprietary innovations.

The UCIe licensing model employs a RAND (Reasonable and Non-Discriminatory) framework, which requires members to license essential patents on fair terms. This structure aims to prevent patent holdups while ensuring innovators receive appropriate compensation for their technological contributions. However, this arrangement creates complex legal considerations regarding what constitutes "reasonable" terms, potentially leading to disputes among consortium members.

From a competitive standpoint, the UCIe licensing framework creates distinct market dynamics. Founding members including Intel, AMD, Arm, and TSMC gain significant advantages through their early influence on specifications and accumulated patent portfolios. This creates potential barriers to entry for smaller players who may face challenges navigating the licensing landscape without comparable patent assets for cross-licensing negotiations.

The licensing structure also impacts global competition, particularly considering geopolitical tensions affecting semiconductor supply chains. Companies from different regions may face varying challenges in accessing UCIe technologies based on export controls and national security considerations. This creates legal complexities regarding technology transfer and licensing compliance across international boundaries.

Antitrust considerations represent another significant legal dimension. As UCIe adoption grows, the consortium's licensing practices may face regulatory scrutiny regarding potential anti-competitive effects. The concentration of essential patents among a small group of major players could raise concerns about market power and exclusionary practices if licensing terms disproportionately favor established entities.

The UCIe ecosystem also presents unique challenges regarding derivative works and implementation patents. While the core specification may be licensed under RAND terms, companies developing proprietary enhancements face complex decisions about how to protect their innovations while maintaining interoperability. This creates a delicate balance between open standards and proprietary differentiation.

Looking forward, the evolution of UCIe licensing will significantly influence industry consolidation patterns. Companies with strong UCIe patent positions may become attractive acquisition targets, while those lacking essential IP may face competitive disadvantages that impact their market viability. This dynamic will likely shape merger and acquisition strategies throughout the semiconductor ecosystem as chiplet technology becomes increasingly central to computing architectures.

The UCIe licensing model employs a RAND (Reasonable and Non-Discriminatory) framework, which requires members to license essential patents on fair terms. This structure aims to prevent patent holdups while ensuring innovators receive appropriate compensation for their technological contributions. However, this arrangement creates complex legal considerations regarding what constitutes "reasonable" terms, potentially leading to disputes among consortium members.

From a competitive standpoint, the UCIe licensing framework creates distinct market dynamics. Founding members including Intel, AMD, Arm, and TSMC gain significant advantages through their early influence on specifications and accumulated patent portfolios. This creates potential barriers to entry for smaller players who may face challenges navigating the licensing landscape without comparable patent assets for cross-licensing negotiations.

The licensing structure also impacts global competition, particularly considering geopolitical tensions affecting semiconductor supply chains. Companies from different regions may face varying challenges in accessing UCIe technologies based on export controls and national security considerations. This creates legal complexities regarding technology transfer and licensing compliance across international boundaries.

Antitrust considerations represent another significant legal dimension. As UCIe adoption grows, the consortium's licensing practices may face regulatory scrutiny regarding potential anti-competitive effects. The concentration of essential patents among a small group of major players could raise concerns about market power and exclusionary practices if licensing terms disproportionately favor established entities.

The UCIe ecosystem also presents unique challenges regarding derivative works and implementation patents. While the core specification may be licensed under RAND terms, companies developing proprietary enhancements face complex decisions about how to protect their innovations while maintaining interoperability. This creates a delicate balance between open standards and proprietary differentiation.

Looking forward, the evolution of UCIe licensing will significantly influence industry consolidation patterns. Companies with strong UCIe patent positions may become attractive acquisition targets, while those lacking essential IP may face competitive disadvantages that impact their market viability. This dynamic will likely shape merger and acquisition strategies throughout the semiconductor ecosystem as chiplet technology becomes increasingly central to computing architectures.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!