Thermal Design For 2.5D/3D UCIe Chiplet Interconnect

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Thermal Management Evolution in Chiplet Architecture

The evolution of thermal management in chiplet architecture represents a critical progression in semiconductor packaging technology. Initially, thermal solutions for traditional monolithic chips focused on simple heat sinks and fans. As integration density increased, more sophisticated cooling methods emerged, including liquid cooling and phase-change materials. The transition to chiplet-based designs, however, fundamentally altered the thermal management landscape.

Early chiplet implementations around 2015-2017 relied primarily on adapted monolithic cooling solutions, which proved inadequate for the unique thermal profiles of multi-die packages. The thermal interfaces between chiplets and substrates created hotspots and thermal bottlenecks that conventional approaches couldn't efficiently address. This limitation drove significant innovation in thermal interface materials (TIMs) specifically optimized for chiplet architectures.

By 2018-2020, the industry witnessed the development of specialized thermal solutions for 2.5D packages, including enhanced TIMs with higher thermal conductivity and improved mechanical properties to accommodate the differential expansion between silicon dies and organic substrates. Thermal modeling techniques also evolved to accurately simulate the complex heat paths in multi-die packages.

The introduction of UCIe (Universal Chiplet Interconnect Express) in 2021-2022 marked another pivotal moment in thermal management evolution. The standardized interconnect architecture necessitated new thermal design approaches to handle the increased power density at die-to-die interfaces. This period saw the emergence of integrated cooling solutions where thermal management was considered from the earliest design stages rather than as an afterthought.

Recent advancements (2022-2023) have focused on active cooling technologies embedded directly within the interposer or substrate. These include microchannel liquid cooling, on-package thermoelectric coolers, and vapor chambers specifically designed for the unique thermal profiles of UCIe-based chiplet packages. The industry has also witnessed growing adoption of computational fluid dynamics (CFD) simulations tailored for multi-die thermal analysis.

The most cutting-edge developments involve heterogeneous integration of cooling solutions, where different cooling technologies are applied to different chiplets within the same package based on their specific thermal requirements. This approach recognizes that memory dies, logic dies, and analog components each have unique thermal profiles and cooling needs.

Looking forward, the thermal management roadmap for chiplet architectures is increasingly focused on three-dimensional integration challenges, where stacked dies create unprecedented cooling difficulties due to limited access to internal layers. Research into through-silicon vias (TSVs) repurposed as thermal conduits and diamond-based heat spreaders represents the frontier of thermal management evolution for advanced chiplet packages.

Early chiplet implementations around 2015-2017 relied primarily on adapted monolithic cooling solutions, which proved inadequate for the unique thermal profiles of multi-die packages. The thermal interfaces between chiplets and substrates created hotspots and thermal bottlenecks that conventional approaches couldn't efficiently address. This limitation drove significant innovation in thermal interface materials (TIMs) specifically optimized for chiplet architectures.

By 2018-2020, the industry witnessed the development of specialized thermal solutions for 2.5D packages, including enhanced TIMs with higher thermal conductivity and improved mechanical properties to accommodate the differential expansion between silicon dies and organic substrates. Thermal modeling techniques also evolved to accurately simulate the complex heat paths in multi-die packages.

The introduction of UCIe (Universal Chiplet Interconnect Express) in 2021-2022 marked another pivotal moment in thermal management evolution. The standardized interconnect architecture necessitated new thermal design approaches to handle the increased power density at die-to-die interfaces. This period saw the emergence of integrated cooling solutions where thermal management was considered from the earliest design stages rather than as an afterthought.

Recent advancements (2022-2023) have focused on active cooling technologies embedded directly within the interposer or substrate. These include microchannel liquid cooling, on-package thermoelectric coolers, and vapor chambers specifically designed for the unique thermal profiles of UCIe-based chiplet packages. The industry has also witnessed growing adoption of computational fluid dynamics (CFD) simulations tailored for multi-die thermal analysis.

The most cutting-edge developments involve heterogeneous integration of cooling solutions, where different cooling technologies are applied to different chiplets within the same package based on their specific thermal requirements. This approach recognizes that memory dies, logic dies, and analog components each have unique thermal profiles and cooling needs.

Looking forward, the thermal management roadmap for chiplet architectures is increasingly focused on three-dimensional integration challenges, where stacked dies create unprecedented cooling difficulties due to limited access to internal layers. Research into through-silicon vias (TSVs) repurposed as thermal conduits and diamond-based heat spreaders represents the frontier of thermal management evolution for advanced chiplet packages.

Market Demand for Advanced Chiplet Thermal Solutions

The global market for advanced chiplet thermal solutions is experiencing robust growth, driven primarily by the increasing adoption of heterogeneous integration technologies in high-performance computing applications. As traditional monolithic chip designs reach their physical and economic limits, the industry is rapidly pivoting toward chiplet-based architectures, with the UCIe (Universal Chiplet Interconnect Express) standard emerging as a critical enabler for this transition.

Market research indicates that the thermal management solutions market specifically for chiplet technologies is projected to grow at a compound annual growth rate of 24% through 2028, significantly outpacing the broader semiconductor cooling solutions market. This accelerated growth reflects the urgent need for specialized thermal solutions that can address the unique challenges posed by 2.5D and 3D integration schemes.

Data center operators represent the largest demand segment, accounting for approximately 42% of the current market. These customers are increasingly deploying high-density compute solutions based on chiplet architectures to maximize performance per watt and per square foot of facility space. Their primary concern centers on managing hotspots at interconnect points, where thermal density can exceed 500W/cm² in advanced applications.

The telecommunications sector follows as the second-largest market segment, driven by the deployment of edge computing infrastructure and 5G/6G network equipment. These applications demand not only high performance but also reliability under variable environmental conditions, creating unique thermal management requirements.

Consumer electronics manufacturers are emerging as a rapidly growing segment, particularly as mobile device processors and AI accelerators adopt chiplet designs to balance performance and power consumption. This segment values integrated thermal solutions that maintain form factor constraints while enabling higher performance.

Geographically, North America leads the market with 38% share, followed by East Asia at 34%, with particularly strong growth in Taiwan, South Korea, and Japan where major semiconductor manufacturing is concentrated. Europe represents 18% of the market, with Germany and the Netherlands showing the strongest demand signals.

The market is increasingly demanding solutions that can address the "thermal boundary resistance" challenge unique to chiplet designs, where heat transfer across interconnect interfaces becomes a critical bottleneck. Industry surveys indicate that 78% of system integrators consider thermal management as one of the top three challenges in adopting chiplet-based architectures, highlighting the significant market opportunity for innovative thermal design solutions.

Market research indicates that the thermal management solutions market specifically for chiplet technologies is projected to grow at a compound annual growth rate of 24% through 2028, significantly outpacing the broader semiconductor cooling solutions market. This accelerated growth reflects the urgent need for specialized thermal solutions that can address the unique challenges posed by 2.5D and 3D integration schemes.

Data center operators represent the largest demand segment, accounting for approximately 42% of the current market. These customers are increasingly deploying high-density compute solutions based on chiplet architectures to maximize performance per watt and per square foot of facility space. Their primary concern centers on managing hotspots at interconnect points, where thermal density can exceed 500W/cm² in advanced applications.

The telecommunications sector follows as the second-largest market segment, driven by the deployment of edge computing infrastructure and 5G/6G network equipment. These applications demand not only high performance but also reliability under variable environmental conditions, creating unique thermal management requirements.

Consumer electronics manufacturers are emerging as a rapidly growing segment, particularly as mobile device processors and AI accelerators adopt chiplet designs to balance performance and power consumption. This segment values integrated thermal solutions that maintain form factor constraints while enabling higher performance.

Geographically, North America leads the market with 38% share, followed by East Asia at 34%, with particularly strong growth in Taiwan, South Korea, and Japan where major semiconductor manufacturing is concentrated. Europe represents 18% of the market, with Germany and the Netherlands showing the strongest demand signals.

The market is increasingly demanding solutions that can address the "thermal boundary resistance" challenge unique to chiplet designs, where heat transfer across interconnect interfaces becomes a critical bottleneck. Industry surveys indicate that 78% of system integrators consider thermal management as one of the top three challenges in adopting chiplet-based architectures, highlighting the significant market opportunity for innovative thermal design solutions.

Current Thermal Challenges in 2.5D/3D UCIe Implementation

The implementation of UCIe (Universal Chiplet Interconnect Express) in 2.5D and 3D chiplet architectures faces significant thermal management challenges that must be addressed to ensure reliable operation and optimal performance. As chiplets are integrated more densely, heat dissipation becomes increasingly problematic due to the reduced surface area available for cooling and the proximity of high-power components.

Power density represents one of the most critical challenges, with some advanced chiplet designs exceeding 500W/cm² in localized hotspots. This extreme concentration of heat can lead to thermal throttling, reducing system performance and potentially causing reliability issues through accelerated electromigration and other temperature-dependent failure mechanisms.

The heterogeneous nature of chiplet integration compounds these challenges, as different dies with varying thermal properties and power profiles are placed in close proximity. This creates complex thermal gradients across the package that are difficult to model and manage. Silicon, interposers, organic substrates, and various interface materials all exhibit different thermal conductivities, creating bottlenecks in heat dissipation pathways.

Thermal interface materials (TIMs) between chiplets and heat spreaders present another significant challenge. Current TIMs often fail to provide adequate thermal conductivity for the extreme heat fluxes generated in advanced UCIe implementations. The thin bond lines required for electrical performance further constrain TIM selection and application methods.

In 3D stacked configurations, the thermal challenges become even more pronounced. Heat generated by dies in the middle or bottom of a stack must traverse through multiple silicon layers and bonding interfaces before reaching the primary cooling solution. This creates severe thermal constraints on the power consumption allowable for dies that are not directly accessible to cooling solutions.

The miniaturization of interconnects in UCIe implementations, while beneficial for electrical performance, creates thermal constriction points that impede heat flow. Microbumps and through-silicon vias (TSVs) provide limited thermal conductivity pathways compared to monolithic designs.

Testing and validation of thermal solutions for UCIe implementations present additional challenges. Traditional thermal testing methods often prove inadequate for accurately measuring temperature distributions across complex chiplet architectures. Real-time thermal monitoring becomes difficult due to limited sensor placement options within the densely packed structure.

Cooling solution attachment and mechanical stability also present significant engineering challenges. The need to maintain uniform pressure across multiple chiplets of varying heights while accommodating coefficient of thermal expansion (CTE) mismatches requires sophisticated mechanical designs that do not compromise electrical performance or reliability.

Power density represents one of the most critical challenges, with some advanced chiplet designs exceeding 500W/cm² in localized hotspots. This extreme concentration of heat can lead to thermal throttling, reducing system performance and potentially causing reliability issues through accelerated electromigration and other temperature-dependent failure mechanisms.

The heterogeneous nature of chiplet integration compounds these challenges, as different dies with varying thermal properties and power profiles are placed in close proximity. This creates complex thermal gradients across the package that are difficult to model and manage. Silicon, interposers, organic substrates, and various interface materials all exhibit different thermal conductivities, creating bottlenecks in heat dissipation pathways.

Thermal interface materials (TIMs) between chiplets and heat spreaders present another significant challenge. Current TIMs often fail to provide adequate thermal conductivity for the extreme heat fluxes generated in advanced UCIe implementations. The thin bond lines required for electrical performance further constrain TIM selection and application methods.

In 3D stacked configurations, the thermal challenges become even more pronounced. Heat generated by dies in the middle or bottom of a stack must traverse through multiple silicon layers and bonding interfaces before reaching the primary cooling solution. This creates severe thermal constraints on the power consumption allowable for dies that are not directly accessible to cooling solutions.

The miniaturization of interconnects in UCIe implementations, while beneficial for electrical performance, creates thermal constriction points that impede heat flow. Microbumps and through-silicon vias (TSVs) provide limited thermal conductivity pathways compared to monolithic designs.

Testing and validation of thermal solutions for UCIe implementations present additional challenges. Traditional thermal testing methods often prove inadequate for accurately measuring temperature distributions across complex chiplet architectures. Real-time thermal monitoring becomes difficult due to limited sensor placement options within the densely packed structure.

Cooling solution attachment and mechanical stability also present significant engineering challenges. The need to maintain uniform pressure across multiple chiplets of varying heights while accommodating coefficient of thermal expansion (CTE) mismatches requires sophisticated mechanical designs that do not compromise electrical performance or reliability.

Existing Thermal Design Solutions for Chiplet Integration

01 Thermal management solutions for chiplet interconnects

Various thermal management solutions are employed in UCIe chiplet interconnect designs to address heat dissipation challenges. These include integrated heat spreaders, thermal interface materials, and advanced cooling structures that efficiently transfer heat away from the interconnect regions. These solutions help maintain optimal operating temperatures for chiplets connected via UCIe interfaces, preventing thermal-induced performance degradation and ensuring reliable operation of multi-die packages.- Thermal management solutions for UCIe chiplet interconnects: Various thermal management solutions are employed in UCIe chiplet interconnect designs to address heat dissipation challenges. These include the use of thermal interface materials (TIMs), heat spreaders, and advanced cooling structures that efficiently transfer heat away from the interconnect regions. The thermal design must account for the high-density interconnects while maintaining signal integrity across the chiplet boundaries.

- Integration of cooling structures in multi-chiplet packages: Multi-chiplet packages with UCIe interconnects require specialized cooling structures integrated directly into the package design. These cooling solutions include embedded microfluidic channels, vapor chambers, and integrated heat sinks that are specifically designed to address hotspots at chiplet interfaces. The cooling structures are optimized to maintain uniform temperature distribution across multiple chiplets connected via UCIe interfaces.

- Thermal-aware UCIe interconnect routing and design: Thermal-aware design methodologies for UCIe interconnects focus on optimizing the routing patterns and physical layout to minimize thermal resistance and hotspots. These approaches include strategic placement of high-power components, thermal-aware signal routing, and the implementation of thermal vias and conduction paths. The design considers both electrical performance and thermal characteristics to ensure reliable operation of the chiplet interconnects.

- Advanced materials for thermal conductivity in UCIe implementations: Novel materials with enhanced thermal conductivity properties are being developed specifically for UCIe chiplet interconnect applications. These materials include advanced composites, diamond-like carbon coatings, graphene-based thermal interface materials, and specialized metal alloys. The materials are designed to efficiently conduct heat away from the interconnect regions while maintaining electrical isolation where needed.

- Thermal monitoring and dynamic management for UCIe interconnects: Integrated thermal monitoring and dynamic management systems are implemented in UCIe chiplet designs to optimize performance while preventing thermal issues. These systems include embedded temperature sensors, real-time thermal monitoring circuits, and adaptive power management algorithms that can adjust operating parameters based on thermal conditions. The dynamic management approach ensures reliable operation of UCIe interconnects under varying workloads and environmental conditions.

02 Thermal-aware chiplet placement and routing

Thermal considerations significantly influence the placement and routing strategies for chiplets using UCIe interconnects. By strategically positioning chiplets and designing interconnect pathways with thermal gradients in mind, designers can minimize hotspots and optimize heat distribution across the package. This approach includes analyzing thermal profiles during the design phase and implementing thermal-aware algorithms for chiplet arrangement to enhance overall thermal performance of multi-chiplet systems.Expand Specific Solutions03 Advanced cooling techniques for UCIe implementations

Innovative cooling techniques are being developed specifically for UCIe chiplet architectures. These include microfluidic cooling channels integrated near interconnect regions, phase-change cooling materials, and specialized heat sink designs that target the unique thermal challenges of chiplet interfaces. These advanced cooling solutions are crucial for high-performance computing applications where UCIe interconnects must maintain high data rates while managing significant thermal loads.Expand Specific Solutions04 Thermal simulation and modeling for UCIe designs

Comprehensive thermal simulation and modeling techniques are essential for optimizing UCIe chiplet interconnect designs. These approaches include multi-physics simulations that account for electrical, mechanical, and thermal interactions at the interconnect level. Advanced computational fluid dynamics models help predict hotspots and thermal bottlenecks, allowing designers to validate thermal solutions before physical implementation and ensure that UCIe interconnects meet thermal specifications under various operating conditions.Expand Specific Solutions05 Power-thermal co-optimization for UCIe interconnects

Power and thermal co-optimization strategies are increasingly important for UCIe chiplet designs. These approaches balance power consumption with thermal constraints by implementing dynamic power management techniques, thermal-aware clock gating, and adaptive voltage scaling at the interconnect level. By simultaneously addressing power and thermal concerns, these solutions extend the operational envelope of UCIe interconnects, enabling higher performance while maintaining thermal stability in densely packed chiplet architectures.Expand Specific Solutions

Key Industry Players in UCIe Thermal Management

The thermal design landscape for 2.5D/3D UCIe Chiplet Interconnect is evolving rapidly as the industry transitions from early adoption to growth phase. The market is projected to expand significantly as chiplet technology addresses performance and integration challenges in advanced computing. Leading semiconductor manufacturers including TSMC, Intel, GlobalFoundries, and Samsung are driving technical innovation, with each developing proprietary thermal management solutions for chiplet architectures. Companies like Qualcomm, IBM, and Huawei are advancing application-specific implementations, while specialized firms such as Jariet Technologies focus on niche thermal solutions. The technology is approaching maturity for high-performance computing applications, though consumer-grade implementations remain in development as thermal challenges in dense interconnect environments continue to be addressed through industry collaboration.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC's thermal design approach for 2.5D/3D UCIe chiplet interconnect focuses on their advanced Integrated Fan-Out (InFO) and System-on-Integrated-Chips (SoIC) packaging technologies. Their solution incorporates a multi-tiered thermal management system that combines microchannel liquid cooling with thermal interface materials (TIMs) specifically engineered for high thermal conductivity at ultra-thin bond lines. TSMC has developed proprietary thermal simulation models that account for the unique thermal pathways in chiplet architectures, allowing for accurate prediction of hotspots and thermal gradients across the interconnect interfaces. Their approach includes embedded silicon thermal bridges between chiplets to facilitate heat spreading and specialized thermal vias that create dedicated heat evacuation pathways from high-power chiplets to the package exterior[1]. TSMC has also implemented advanced thermal monitoring systems with distributed sensors that enable dynamic thermal management across the chiplet ecosystem.

Strengths: Industry-leading process node capabilities allow for optimized power efficiency in chiplet designs; extensive experience with high-volume heterogeneous integration; proprietary thermal simulation tools specifically calibrated for their manufacturing processes. Weaknesses: Their thermal solutions may be optimized primarily for their own manufacturing processes, potentially limiting flexibility for customers using multiple foundry partners.

Intel Corp.

Technical Solution: Intel's thermal design for UCIe chiplet interconnect leverages their Embedded Multi-die Interconnect Bridge (EMIB) and Foveros 3D packaging technologies. Their approach incorporates a comprehensive thermal solution that addresses the unique challenges of high-density interconnects in heterogeneous integration. Intel has developed an advanced thermal architecture that utilizes a combination of direct die-attached heat spreaders, phase-change thermal interface materials, and integrated vapor chambers to manage heat dissipation across chiplet boundaries[2]. Their solution includes specialized thermal pathways designed to evacuate heat from high-power compute tiles while maintaining the thermal integrity of sensitive I/O and memory chiplets. Intel's thermal design also incorporates active thermal management through embedded microcontrollers that dynamically adjust power distribution based on thermal feedback from distributed sensors across the package. Additionally, Intel has pioneered power delivery network designs that minimize resistive losses and associated thermal generation at the chiplet interfaces, reducing overall thermal load[3].

Strengths: Extensive experience with heterogeneous integration; strong vertical integration allowing for co-optimization of silicon and packaging; leadership role in UCIe consortium providing deep technical insights. Weaknesses: Their thermal solutions may be optimized primarily for x86 architecture workloads and may require adaptation for other computing paradigms; higher thermal design power requirements compared to some competitors.

Critical Patents in UCIe Thermal Dissipation Technologies

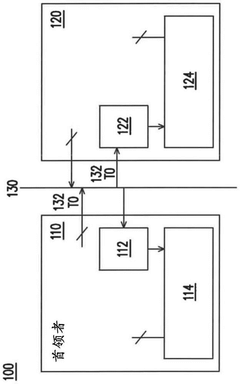

Semiconductor package and method of operating same

PatentPendingCN118039576A

Innovation

- Generating and synchronizing global clock signals by introducing redistribution structures and phase alignment elements into semiconductor packages enables clock signals between multiple semiconductor chips to be synchronized in a single global clock domain, resulting in more cost-effective data transmission .

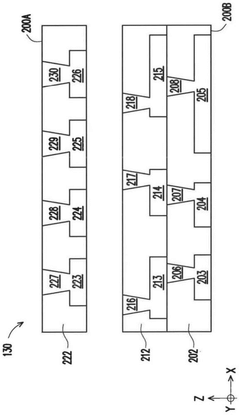

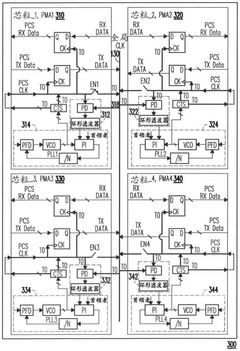

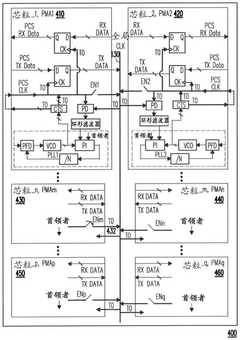

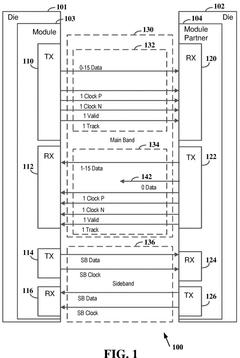

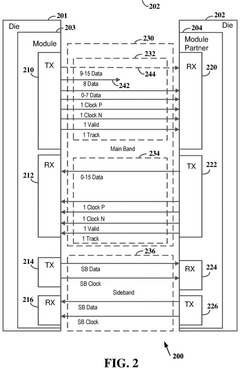

Variable link width in two directions for main band chip module connection

PatentWO2024226177A1

Innovation

- Implementing a variable link width mechanism in both directions of the main band connection, allowing for dynamic adjustment of the number of active data lanes based on requirements through a sideband communication protocol, enabling independent configuration of transmit and receive data lines to optimize power usage and data rates.

Material Science Advancements for Thermal Interface Materials

The evolution of Thermal Interface Materials (TIMs) represents a critical frontier in addressing thermal challenges for 2.5D/3D UCIe chiplet interconnect technologies. Recent advancements in material science have yielded significant improvements in thermal conductivity, reliability, and application methods for these essential components of thermal management systems.

Metal-based TIMs have seen remarkable development, with liquid metal solutions achieving thermal conductivity values exceeding 70 W/mK, substantially outperforming traditional greases. These materials offer excellent wetting properties and can fill microscopic surface irregularities, creating superior thermal interfaces between chiplets and heat dissipation structures.

Nano-enhanced polymer composites represent another breakthrough, incorporating carbon nanotubes, graphene, and boron nitride to achieve thermal conductivity improvements of 200-300% compared to conventional polymer-based TIMs. These materials maintain flexibility while delivering enhanced thermal performance, making them particularly suitable for the complex geometries found in 3D chiplet stacks.

Phase change materials (PCMs) have evolved to address the thermal cycling challenges inherent in chiplet designs. Advanced PCMs now feature precisely engineered melting points between 45-65°C, optimized for chiplet operating temperatures, while maintaining stability through thousands of thermal cycles without performance degradation.

Sintered silver and copper TIMs have emerged as high-performance solutions for critical thermal interfaces in chiplet packages. These materials can achieve thermal conductivity values of 200-400 W/mK after sintering processes, creating nearly void-free interfaces that significantly reduce thermal resistance at chiplet boundaries.

Conformal coating technologies have advanced to enable ultra-thin (1-5μm) TIM layers with minimal bond line thickness, critical for maintaining thermal performance while accommodating the extremely tight z-height constraints of stacked chiplet designs. These coatings can be precisely applied using advanced deposition techniques, ensuring uniform coverage across complex topographies.

Self-healing TIM formulations represent the cutting edge of reliability enhancement, incorporating microcapsules with healing agents that release upon crack formation, restoring thermal conductivity pathways. This technology addresses the long-term reliability concerns associated with thermal cycling in chiplet packages, potentially extending operational lifetimes by 30-50%.

Metal-based TIMs have seen remarkable development, with liquid metal solutions achieving thermal conductivity values exceeding 70 W/mK, substantially outperforming traditional greases. These materials offer excellent wetting properties and can fill microscopic surface irregularities, creating superior thermal interfaces between chiplets and heat dissipation structures.

Nano-enhanced polymer composites represent another breakthrough, incorporating carbon nanotubes, graphene, and boron nitride to achieve thermal conductivity improvements of 200-300% compared to conventional polymer-based TIMs. These materials maintain flexibility while delivering enhanced thermal performance, making them particularly suitable for the complex geometries found in 3D chiplet stacks.

Phase change materials (PCMs) have evolved to address the thermal cycling challenges inherent in chiplet designs. Advanced PCMs now feature precisely engineered melting points between 45-65°C, optimized for chiplet operating temperatures, while maintaining stability through thousands of thermal cycles without performance degradation.

Sintered silver and copper TIMs have emerged as high-performance solutions for critical thermal interfaces in chiplet packages. These materials can achieve thermal conductivity values of 200-400 W/mK after sintering processes, creating nearly void-free interfaces that significantly reduce thermal resistance at chiplet boundaries.

Conformal coating technologies have advanced to enable ultra-thin (1-5μm) TIM layers with minimal bond line thickness, critical for maintaining thermal performance while accommodating the extremely tight z-height constraints of stacked chiplet designs. These coatings can be precisely applied using advanced deposition techniques, ensuring uniform coverage across complex topographies.

Self-healing TIM formulations represent the cutting edge of reliability enhancement, incorporating microcapsules with healing agents that release upon crack formation, restoring thermal conductivity pathways. This technology addresses the long-term reliability concerns associated with thermal cycling in chiplet packages, potentially extending operational lifetimes by 30-50%.

Power-Thermal Co-optimization Strategies for UCIe Systems

Power-thermal co-optimization represents a critical approach for addressing the thermal challenges in UCIe (Universal Chiplet Interconnect Express) systems. As chiplet architectures become more prevalent in high-performance computing, the integration density increases significantly, creating concentrated thermal hotspots that can compromise system reliability and performance.

The fundamental principle of power-thermal co-optimization involves simultaneous management of power consumption and thermal dissipation across the entire chiplet ecosystem. This approach recognizes the intrinsic relationship between power usage and heat generation, treating them as interconnected variables rather than separate concerns.

In UCIe systems, several co-optimization strategies have emerged as particularly effective. Dynamic Voltage and Frequency Scaling (DVFS) techniques have been adapted specifically for chiplet architectures, allowing for fine-grained control over individual chiplets based on their thermal profiles and computational loads. This granular approach enables the system to maintain optimal performance while preventing thermal emergencies.

Workload distribution algorithms represent another crucial strategy, intelligently allocating computational tasks across available chiplets to balance thermal loads. These algorithms incorporate thermal awareness, prioritizing cooler regions of the package for computation-intensive tasks while allowing hotter areas to cool down through reduced activity.

Advanced thermal-aware floorplanning has proven essential during the design phase. By strategically positioning high-power chiplets adjacent to lower-power components and optimizing the placement relative to available cooling solutions, designers can significantly improve thermal distribution across the package.

Liquid cooling solutions specifically tailored for UCIe implementations have demonstrated superior performance compared to traditional air cooling. These solutions target the unique thermal characteristics of chiplet interfaces, where heat concentration is often most problematic.

Predictive thermal modeling has evolved to accommodate the complex thermal interactions in UCIe systems. These models incorporate the unique thermal properties of chiplet interfaces and can simulate heat flow across different materials and connection types, enabling designers to identify potential issues before physical implementation.

Runtime thermal management systems have been developed that continuously monitor thermal conditions across the chiplet ecosystem and dynamically adjust power states, workload distribution, and cooling parameters to maintain optimal operating conditions without unnecessary performance penalties.

The fundamental principle of power-thermal co-optimization involves simultaneous management of power consumption and thermal dissipation across the entire chiplet ecosystem. This approach recognizes the intrinsic relationship between power usage and heat generation, treating them as interconnected variables rather than separate concerns.

In UCIe systems, several co-optimization strategies have emerged as particularly effective. Dynamic Voltage and Frequency Scaling (DVFS) techniques have been adapted specifically for chiplet architectures, allowing for fine-grained control over individual chiplets based on their thermal profiles and computational loads. This granular approach enables the system to maintain optimal performance while preventing thermal emergencies.

Workload distribution algorithms represent another crucial strategy, intelligently allocating computational tasks across available chiplets to balance thermal loads. These algorithms incorporate thermal awareness, prioritizing cooler regions of the package for computation-intensive tasks while allowing hotter areas to cool down through reduced activity.

Advanced thermal-aware floorplanning has proven essential during the design phase. By strategically positioning high-power chiplets adjacent to lower-power components and optimizing the placement relative to available cooling solutions, designers can significantly improve thermal distribution across the package.

Liquid cooling solutions specifically tailored for UCIe implementations have demonstrated superior performance compared to traditional air cooling. These solutions target the unique thermal characteristics of chiplet interfaces, where heat concentration is often most problematic.

Predictive thermal modeling has evolved to accommodate the complex thermal interactions in UCIe systems. These models incorporate the unique thermal properties of chiplet interfaces and can simulate heat flow across different materials and connection types, enabling designers to identify potential issues before physical implementation.

Runtime thermal management systems have been developed that continuously monitor thermal conditions across the chiplet ecosystem and dynamically adjust power states, workload distribution, and cooling parameters to maintain optimal operating conditions without unnecessary performance penalties.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!