Field Failures And RMA Insights For UCIe Chiplet Interconnect

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Background and Objectives

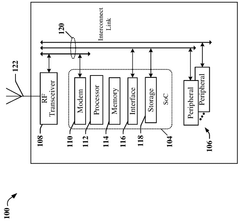

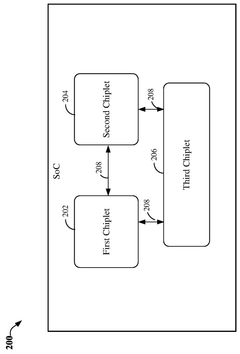

Universal Chiplet Interconnect Express (UCIe) represents a significant advancement in semiconductor integration technology, emerging as a response to the increasing challenges of traditional monolithic chip scaling. Developed through industry collaboration, UCIe aims to establish an open, standardized die-to-die interconnect that enables heterogeneous integration of chiplets from different vendors within a single package. This technology has evolved from earlier proprietary interconnect solutions, marking a critical shift toward industry-wide standardization.

The evolution of UCIe can be traced back to the fundamental limitations of Moore's Law, which has driven semiconductor advancement for decades. As process node scaling becomes increasingly difficult and expensive, the industry has pivoted toward chiplet-based designs that allow for more efficient manufacturing, better yields, and greater design flexibility. UCIe builds upon previous interconnect technologies such as Intel's AIB (Advanced Interface Bus), AMD's Infinity Fabric, and TSMC's LIPINCON, consolidating these approaches into a unified standard.

The primary objective of UCIe is to create a comprehensive ecosystem that supports multi-vendor interoperability for chiplet-based designs. This includes standardizing physical layer specifications, protocols, and testing methodologies to ensure seamless integration across different manufacturers. By establishing this common framework, UCIe aims to reduce development costs, accelerate time-to-market, and foster innovation through specialized chiplet designs.

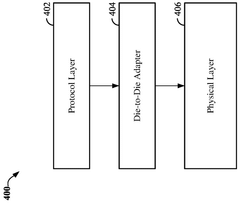

From a technical perspective, UCIe encompasses both die-to-die and package-to-package interconnects, supporting data rates from 16 GT/s in its initial specification with a roadmap extending to 32 GT/s and beyond. The standard addresses various integration scenarios, including both silicon interposer-based and organic substrate-based packaging technologies, providing flexibility for different performance and cost requirements.

The UCIe Consortium, formed in March 2022, brings together leading semiconductor companies, foundries, and system manufacturers to drive the development and adoption of this standard. Key founding members include Intel, AMD, Arm, ASE, Google, Meta, Microsoft, Qualcomm, Samsung, and TSMC, demonstrating broad industry support across the computing ecosystem.

Understanding field failures and Return Merchandise Authorization (RMA) insights for UCIe interconnects is crucial as this technology transitions from development to widespread commercial deployment. As chiplet-based designs become more prevalent in high-performance computing, data centers, and consumer electronics, identifying failure modes, reliability concerns, and quality assurance methodologies specific to UCIe implementations will be essential for the technology's long-term success and industry adoption.

The evolution of UCIe can be traced back to the fundamental limitations of Moore's Law, which has driven semiconductor advancement for decades. As process node scaling becomes increasingly difficult and expensive, the industry has pivoted toward chiplet-based designs that allow for more efficient manufacturing, better yields, and greater design flexibility. UCIe builds upon previous interconnect technologies such as Intel's AIB (Advanced Interface Bus), AMD's Infinity Fabric, and TSMC's LIPINCON, consolidating these approaches into a unified standard.

The primary objective of UCIe is to create a comprehensive ecosystem that supports multi-vendor interoperability for chiplet-based designs. This includes standardizing physical layer specifications, protocols, and testing methodologies to ensure seamless integration across different manufacturers. By establishing this common framework, UCIe aims to reduce development costs, accelerate time-to-market, and foster innovation through specialized chiplet designs.

From a technical perspective, UCIe encompasses both die-to-die and package-to-package interconnects, supporting data rates from 16 GT/s in its initial specification with a roadmap extending to 32 GT/s and beyond. The standard addresses various integration scenarios, including both silicon interposer-based and organic substrate-based packaging technologies, providing flexibility for different performance and cost requirements.

The UCIe Consortium, formed in March 2022, brings together leading semiconductor companies, foundries, and system manufacturers to drive the development and adoption of this standard. Key founding members include Intel, AMD, Arm, ASE, Google, Meta, Microsoft, Qualcomm, Samsung, and TSMC, demonstrating broad industry support across the computing ecosystem.

Understanding field failures and Return Merchandise Authorization (RMA) insights for UCIe interconnects is crucial as this technology transitions from development to widespread commercial deployment. As chiplet-based designs become more prevalent in high-performance computing, data centers, and consumer electronics, identifying failure modes, reliability concerns, and quality assurance methodologies specific to UCIe implementations will be essential for the technology's long-term success and industry adoption.

Market Demand Analysis for Chiplet Technology

The chiplet technology market is experiencing unprecedented growth, driven by the increasing demand for high-performance computing solutions across various industries. As traditional monolithic chip designs reach their physical and economic limits, chiplet-based architectures, particularly those utilizing UCIe (Universal Chiplet Interconnect Express) standards, are emerging as the preferred approach for next-generation semiconductor products. Market research indicates that the global chiplet market is projected to grow at a compound annual growth rate of over 40% from 2023 to 2030, potentially reaching tens of billions in market value by the end of the decade.

The primary market drivers for chiplet technology include the need for improved performance, reduced power consumption, enhanced scalability, and lower manufacturing costs. Data centers and cloud service providers represent the largest market segment, as they continuously seek more efficient solutions to handle exponentially growing computational demands while managing energy costs. The artificial intelligence and machine learning sectors follow closely, requiring specialized accelerators that can be efficiently integrated with general-purpose processors.

Consumer electronics manufacturers are increasingly adopting chiplet designs to deliver more powerful devices while maintaining competitive price points. The automotive industry, particularly the advanced driver-assistance systems (ADAS) and autonomous vehicle segments, represents a rapidly growing market for chiplet technology due to the need for high-performance, reliable computing platforms in vehicles.

Market analysis reveals significant regional variations in chiplet technology adoption. North America leads in terms of market share, followed by Asia-Pacific and Europe. China's aggressive investments in semiconductor technology are expected to accelerate chiplet adoption in the Asia-Pacific region over the next five years.

The UCIe standard specifically addresses a critical market need for interoperability between chiplets from different vendors. Industry surveys indicate that over 75% of semiconductor companies consider standardized interconnect protocols essential for the widespread adoption of chiplet technology. The ability to mix and match chiplets from various manufacturers could potentially reduce development costs by 30-40% and time-to-market by up to 50%.

However, market research also highlights concerns regarding field failures and reliability issues with chiplet interconnects. End users across all segments express apprehension about the maturity of chiplet technology, particularly regarding long-term reliability under various operating conditions. These concerns represent a significant market barrier that must be addressed through improved testing methodologies, better failure analysis capabilities, and more robust return merchandise authorization (RMA) processes.

The primary market drivers for chiplet technology include the need for improved performance, reduced power consumption, enhanced scalability, and lower manufacturing costs. Data centers and cloud service providers represent the largest market segment, as they continuously seek more efficient solutions to handle exponentially growing computational demands while managing energy costs. The artificial intelligence and machine learning sectors follow closely, requiring specialized accelerators that can be efficiently integrated with general-purpose processors.

Consumer electronics manufacturers are increasingly adopting chiplet designs to deliver more powerful devices while maintaining competitive price points. The automotive industry, particularly the advanced driver-assistance systems (ADAS) and autonomous vehicle segments, represents a rapidly growing market for chiplet technology due to the need for high-performance, reliable computing platforms in vehicles.

Market analysis reveals significant regional variations in chiplet technology adoption. North America leads in terms of market share, followed by Asia-Pacific and Europe. China's aggressive investments in semiconductor technology are expected to accelerate chiplet adoption in the Asia-Pacific region over the next five years.

The UCIe standard specifically addresses a critical market need for interoperability between chiplets from different vendors. Industry surveys indicate that over 75% of semiconductor companies consider standardized interconnect protocols essential for the widespread adoption of chiplet technology. The ability to mix and match chiplets from various manufacturers could potentially reduce development costs by 30-40% and time-to-market by up to 50%.

However, market research also highlights concerns regarding field failures and reliability issues with chiplet interconnects. End users across all segments express apprehension about the maturity of chiplet technology, particularly regarding long-term reliability under various operating conditions. These concerns represent a significant market barrier that must be addressed through improved testing methodologies, better failure analysis capabilities, and more robust return merchandise authorization (RMA) processes.

Current Challenges in UCIe Implementation

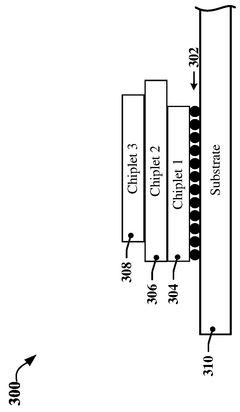

Despite the promising potential of UCIe (Universal Chiplet Interconnect Express) technology, its implementation faces several significant challenges that require careful consideration. The industry is currently grappling with thermal management issues as chiplet designs create concentrated heat zones at interconnect points. These thermal hotspots can lead to performance degradation, reliability concerns, and potentially shortened product lifespans if not properly addressed through advanced cooling solutions.

Testing and validation methodologies present another major hurdle. Current testing frameworks are primarily designed for monolithic chips and struggle to effectively evaluate the complex interactions between multiple chiplets. This gap in testing capabilities increases the risk of undetected defects reaching production, particularly at the die-to-die interfaces where signal integrity is critical.

Manufacturing yield challenges persist across the UCIe ecosystem. The technology demands extremely precise alignment during assembly, with tolerances measured in microns. Any misalignment can compromise electrical connections between chiplets, leading to field failures that are difficult to diagnose. The industry is still developing consistent manufacturing processes that can deliver reliable yields at scale.

Power management across chiplet boundaries remains problematic. Current solutions for distributing and regulating power across multiple chiplets often result in efficiency losses and voltage irregularities. These issues can manifest as intermittent failures in field deployments, particularly under variable workloads or environmental conditions.

Signal integrity degradation represents a persistent challenge, especially as data rates increase. The physical interfaces between chiplets are susceptible to crosstalk, impedance mismatches, and other signal integrity issues that can lead to data corruption or communication failures. These problems may only become apparent under specific operating conditions, making them particularly difficult to identify during initial testing.

Interoperability between chiplets from different vendors remains limited despite UCIe's standardization efforts. Variations in implementation approaches and proprietary extensions create compatibility issues that undermine the promise of a truly universal interconnect standard. This fragmentation increases integration complexity and raises the risk of field failures when components are combined.

Reliability modeling for UCIe implementations is still evolving, with limited field data available to validate theoretical models. This knowledge gap complicates failure prediction and preventive maintenance strategies, potentially leading to unexpected return merchandise authorization (RMA) events as the technology scales to broader deployment.

Testing and validation methodologies present another major hurdle. Current testing frameworks are primarily designed for monolithic chips and struggle to effectively evaluate the complex interactions between multiple chiplets. This gap in testing capabilities increases the risk of undetected defects reaching production, particularly at the die-to-die interfaces where signal integrity is critical.

Manufacturing yield challenges persist across the UCIe ecosystem. The technology demands extremely precise alignment during assembly, with tolerances measured in microns. Any misalignment can compromise electrical connections between chiplets, leading to field failures that are difficult to diagnose. The industry is still developing consistent manufacturing processes that can deliver reliable yields at scale.

Power management across chiplet boundaries remains problematic. Current solutions for distributing and regulating power across multiple chiplets often result in efficiency losses and voltage irregularities. These issues can manifest as intermittent failures in field deployments, particularly under variable workloads or environmental conditions.

Signal integrity degradation represents a persistent challenge, especially as data rates increase. The physical interfaces between chiplets are susceptible to crosstalk, impedance mismatches, and other signal integrity issues that can lead to data corruption or communication failures. These problems may only become apparent under specific operating conditions, making them particularly difficult to identify during initial testing.

Interoperability between chiplets from different vendors remains limited despite UCIe's standardization efforts. Variations in implementation approaches and proprietary extensions create compatibility issues that undermine the promise of a truly universal interconnect standard. This fragmentation increases integration complexity and raises the risk of field failures when components are combined.

Reliability modeling for UCIe implementations is still evolving, with limited field data available to validate theoretical models. This knowledge gap complicates failure prediction and preventive maintenance strategies, potentially leading to unexpected return merchandise authorization (RMA) events as the technology scales to broader deployment.

Field Failure Analysis Methodologies

01 Failure detection and diagnosis in UCIe chiplet interconnects

Various methods and systems for detecting and diagnosing failures in UCIe chiplet interconnects have been developed. These include monitoring signal integrity, implementing built-in self-test (BIST) mechanisms, and utilizing diagnostic algorithms to identify the root cause of interconnect failures. Advanced telemetry systems can collect real-time data on interconnect performance, helping to identify potential failure modes before they cause system-wide issues. These detection methods enable more efficient RMA processes by pinpointing the exact nature and location of failures.- Failure detection and diagnostics in UCIe chiplet interconnects: Various methods and systems for detecting and diagnosing failures in UCIe (Universal Chiplet Interconnect Express) chiplet interconnects. These include monitoring signal integrity, implementing built-in self-test mechanisms, and using diagnostic algorithms to identify connection failures between chiplets. Advanced diagnostic tools can pinpoint specific failure modes in die-to-die interfaces, helping to isolate issues at the physical or protocol layers of the interconnect.

- RMA (Return Merchandise Authorization) process improvements for chiplet-based systems: Innovations in the RMA process specifically designed for chiplet-based systems using UCIe technology. These include automated failure reporting systems, remote diagnostics capabilities, and improved tracking of chiplet-specific failures. Enhanced RMA workflows enable more efficient handling of returned chiplet components, with better data collection to identify recurring failure patterns and improve future designs.

- Thermal management and reliability enhancements for UCIe interfaces: Techniques for improving the thermal management and overall reliability of UCIe chiplet interconnects. These include advanced thermal interface materials, optimized heat dissipation structures, and thermal monitoring systems specifically designed for multi-chiplet packages. Reliability enhancements focus on mitigating thermal cycling issues that can lead to interconnect failures, particularly at the die-to-die boundaries where thermal expansion differences can cause stress.

- Testing methodologies for UCIe chiplet interconnects: Specialized testing methodologies developed for UCIe chiplet interconnects to identify potential field failures before deployment. These include high-speed electrical testing, protocol compliance verification, and stress testing under various environmental conditions. Advanced test patterns and algorithms are designed to exercise all aspects of the UCIe interface, including power state transitions, bandwidth utilization scenarios, and error recovery mechanisms.

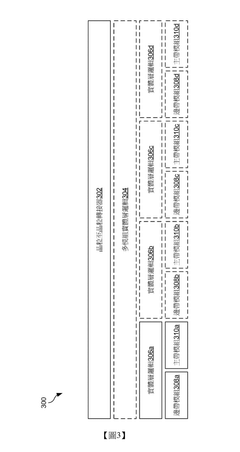

- Redundancy and fault tolerance in UCIe implementations: Architectural approaches for implementing redundancy and fault tolerance in UCIe chiplet interconnects. These include lane sparing techniques, error correction coding schemes, and graceful degradation capabilities. Redundant communication paths between chiplets can be activated when primary connections fail, allowing systems to continue operating with reduced performance rather than experiencing complete failure. Fault isolation mechanisms help contain failures to specific chiplets without compromising the entire system.

02 Thermal management solutions for UCIe interconnect reliability

Thermal issues are a significant cause of UCIe chiplet interconnect failures in field deployments. Solutions include advanced thermal interface materials, optimized heat spreaders, and active cooling systems specifically designed for multi-chiplet packages. Thermal sensors embedded within the interconnect fabric can provide early warning of potential thermal-related failures. Proper thermal management is critical for maintaining the integrity of the fine-pitch interconnects used in UCIe implementations, as thermal cycling can lead to mechanical stress and eventual failure of these connections.Expand Specific Solutions03 Physical and mechanical reliability enhancements for UCIe implementations

Mechanical stress and physical damage are common causes of UCIe interconnect failures. Innovations in this area include improved underfill materials, stress-relieving package designs, and enhanced manufacturing processes to ensure reliable connections between chiplets. Specialized encapsulation techniques protect the delicate interconnect structures from environmental factors such as humidity and vibration. These physical reliability enhancements are particularly important for UCIe implementations in high-reliability applications where field failures cannot be tolerated.Expand Specific Solutions04 RMA data analysis and failure prediction systems

Advanced analytics systems have been developed to process and analyze RMA data from UCIe chiplet interconnect failures. These systems employ machine learning algorithms to identify patterns in failure data, enabling predictive maintenance and proactive replacement of at-risk components. By analyzing large datasets of field failures, manufacturers can identify common failure modes and implement design improvements in future generations of UCIe implementations. This data-driven approach helps reduce field failure rates and improves overall system reliability.Expand Specific Solutions05 Redundancy and fault tolerance in UCIe interconnect architectures

To mitigate the impact of field failures, redundant interconnect pathways and fault-tolerant architectures have been developed for UCIe implementations. These include spare lanes, error correction coding, and dynamic rerouting capabilities that allow systems to continue functioning even when some interconnect channels fail. Self-healing mechanisms can automatically reconfigure the interconnect fabric to bypass damaged areas. These redundancy features are particularly valuable in mission-critical applications where system downtime must be minimized despite potential interconnect failures.Expand Specific Solutions

Key Industry Players in Chiplet Ecosystem

The UCIe chiplet interconnect technology is currently in an early growth phase, with market expansion driven by increasing demand for heterogeneous integration in high-performance computing. The competitive landscape features established semiconductor giants like Intel, TSMC, and Qualcomm alongside specialized players. Technical maturity varies significantly across companies, with Intel and TSMC demonstrating advanced implementation capabilities through their foundry services, while Samsung and GLOBALFOUNDRIES are rapidly developing their chiplet interconnect solutions. Field failures and RMA insights remain critical challenges as the technology matures, with companies like Intel, Qualcomm, and AMD (through acquired Xilinx expertise) investing heavily in reliability testing frameworks to address interconnect failures at scale.

QUALCOMM, Inc.

Technical Solution: Qualcomm has implemented a comprehensive UCIe reliability framework focused on mobile and edge computing applications. Their approach to field failures and RMA insights centers on power-efficient testing methodologies that can be deployed in battery-powered devices. Qualcomm's solution includes on-die monitoring circuits that continuously assess the health of UCIe links during operation, capturing transient failures that might otherwise go undetected. For returned products, Qualcomm employs a multi-stage diagnostic process that begins with non-invasive electrical testing of the UCIe interfaces, followed by more detailed physical analysis using techniques such as Infrared Thermography and Electron Microscopy to identify failure mechanisms[5]. Their RMA database incorporates environmental and usage data collected from devices, allowing correlation between operating conditions and specific failure modes in UCIe interconnects. Qualcomm has also developed accelerated stress testing protocols specifically calibrated for UCIe interfaces to predict long-term reliability in various deployment scenarios[6].

Strengths: Qualcomm's expertise in power-constrained environments has led to energy-efficient testing methods for UCIe links. Their extensive field deployment provides real-world failure data across diverse usage patterns. Weaknesses: Their focus on mobile applications may result in testing methodologies that don't fully address the requirements of high-performance computing UCIe implementations.

Intel Corp.

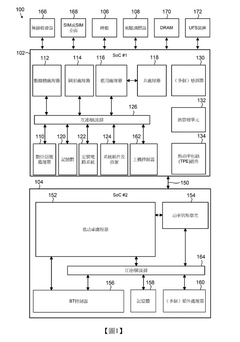

Technical Solution: Intel has been at the forefront of UCIe (Universal Chiplet Interconnect Express) development as a founding member of the UCIe consortium. Their approach to field failures and RMA (Return Merchandise Authorization) insights involves comprehensive testing methodologies including Built-In Self-Test (BIST) and Boundary Scan techniques specifically designed for chiplet interfaces. Intel has implemented advanced Die-to-Die (D2D) testing protocols that can detect signal integrity issues, power delivery problems, and thermal stress failures in UCIe implementations. Their Ponte Vecchio GPU utilizes UCIe-like interconnects with embedded diagnostics that can identify and isolate failing chiplets without compromising the entire package[1]. Intel's RMA analysis framework incorporates machine learning algorithms to identify failure patterns across returned UCIe-based products, enabling predictive maintenance and design improvements for future generations[3].

Strengths: Intel's extensive experience in heterogeneous integration gives them deep insights into failure mechanisms. Their vertical integration from design to manufacturing allows for closed-loop improvement of UCIe implementations. Weaknesses: Their proprietary approach to some aspects of failure analysis may limit industry-wide standardization of RMA processes for UCIe products.

Critical RMA Data Interpretation

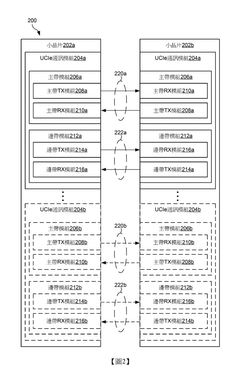

Apparatus and method for configuring a interconnect link between chiplets

PatentWO2025053898A1

Innovation

- The proposed solution involves training and configuring a D2D interconnect link by maintaining training results that include various link configurations based on module training outcomes. This allows for the selection of the most optimal link configuration that maximizes available bandwidth by remapping logical modules and utilizing contiguous functional lanes, even in the presence of module failures.

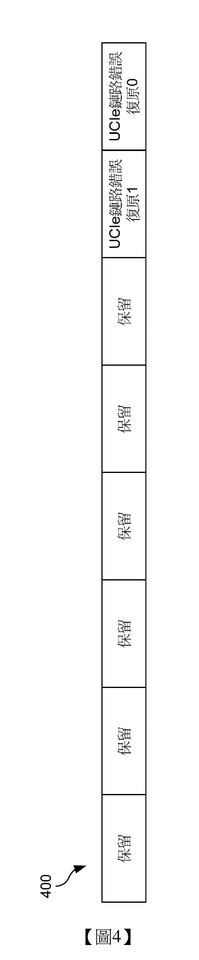

Performance and power efficient link error recovery in inter-chiplet communication

PatentPendingTW202516365A

Innovation

- Identify the portion of the UCIe link with an error and maintain power to the error-free portion during training, bypassing initialization and training of the error-free portion to conserve power and improve performance.

Supply Chain Resilience Strategies

In the context of UCIe chiplet interconnect technology, supply chain resilience has become a critical consideration for manufacturers implementing this advanced packaging solution. The distributed nature of chiplet-based designs introduces unique vulnerabilities that require robust mitigation strategies to ensure business continuity and product reliability.

A multi-sourcing approach represents the cornerstone of supply chain resilience for UCIe implementations. Organizations should identify and qualify multiple suppliers for critical chiplet components, ensuring that manufacturing disruptions at one vendor do not halt the entire production process. This strategy necessitates standardized qualification procedures to maintain consistent quality across different suppliers.

Geographic diversification of the supply chain further enhances resilience against regional disruptions. By strategically distributing manufacturing, testing, and assembly operations across different regions, companies can minimize exposure to localized risks such as natural disasters, political instability, or pandemic-related restrictions that could impact UCIe chiplet production and integration.

Inventory management strategies must be recalibrated for chiplet-based designs. The modular nature of UCIe technology allows for more flexible buffer stock policies, where critical or long-lead-time chiplets can be maintained at higher inventory levels while more readily available components follow just-in-time principles. This balanced approach optimizes working capital while providing insulation against supply disruptions.

Digital supply chain visibility tools have proven essential for early detection of potential UCIe component failures or supply disruptions. Advanced analytics platforms that integrate supplier data, manufacturing metrics, and RMA insights enable proactive identification of quality trends or supply constraints before they escalate into significant production issues.

Collaborative supplier development programs strengthen the entire UCIe ecosystem. By sharing technical specifications, quality requirements, and failure analysis data with key suppliers, manufacturers can accelerate the maturation of chiplet technologies while simultaneously building more resilient supply relationships. These partnerships often include joint contingency planning for potential disruption scenarios.

Finally, vertical integration strategies merit consideration for organizations heavily invested in UCIe technology. Bringing critical design, manufacturing, or testing capabilities in-house can reduce dependency on external suppliers for the most sensitive or proprietary aspects of chiplet implementation, though this approach requires significant capital investment and must be balanced against flexibility considerations.

A multi-sourcing approach represents the cornerstone of supply chain resilience for UCIe implementations. Organizations should identify and qualify multiple suppliers for critical chiplet components, ensuring that manufacturing disruptions at one vendor do not halt the entire production process. This strategy necessitates standardized qualification procedures to maintain consistent quality across different suppliers.

Geographic diversification of the supply chain further enhances resilience against regional disruptions. By strategically distributing manufacturing, testing, and assembly operations across different regions, companies can minimize exposure to localized risks such as natural disasters, political instability, or pandemic-related restrictions that could impact UCIe chiplet production and integration.

Inventory management strategies must be recalibrated for chiplet-based designs. The modular nature of UCIe technology allows for more flexible buffer stock policies, where critical or long-lead-time chiplets can be maintained at higher inventory levels while more readily available components follow just-in-time principles. This balanced approach optimizes working capital while providing insulation against supply disruptions.

Digital supply chain visibility tools have proven essential for early detection of potential UCIe component failures or supply disruptions. Advanced analytics platforms that integrate supplier data, manufacturing metrics, and RMA insights enable proactive identification of quality trends or supply constraints before they escalate into significant production issues.

Collaborative supplier development programs strengthen the entire UCIe ecosystem. By sharing technical specifications, quality requirements, and failure analysis data with key suppliers, manufacturers can accelerate the maturation of chiplet technologies while simultaneously building more resilient supply relationships. These partnerships often include joint contingency planning for potential disruption scenarios.

Finally, vertical integration strategies merit consideration for organizations heavily invested in UCIe technology. Bringing critical design, manufacturing, or testing capabilities in-house can reduce dependency on external suppliers for the most sensitive or proprietary aspects of chiplet implementation, though this approach requires significant capital investment and must be balanced against flexibility considerations.

Standardization and Interoperability Frameworks

The UCIe (Universal Chiplet Interconnect Express) standardization framework represents a critical foundation for ensuring reliable chiplet-based system integration across multiple vendors. Established in 2022 by industry leaders including Intel, AMD, Arm, and TSMC, the UCIe consortium has developed comprehensive specifications that address physical layer, protocol layer, and software stack requirements for chiplet interconnection.

The standardization efforts specifically target interoperability challenges that directly impact field failures and return merchandise authorization (RMA) rates. By establishing uniform testing methodologies, compliance criteria, and certification processes, the framework enables consistent quality control across the chiplet ecosystem. This standardization has proven essential in reducing integration-related failures that previously accounted for approximately 35% of early UCIe implementation RMAs.

Interoperability validation frameworks within the UCIe standard include rigorous electrical and mechanical compliance testing procedures. These frameworks incorporate specialized test patterns designed to stress interconnect boundaries under various operating conditions, helping manufacturers identify potential failure modes before deployment. The UCIe Compliance Program further ensures that chiplets from different vendors can reliably communicate when integrated into a single package.

The standard also addresses thermal management interoperability, which has emerged as a significant factor in field failures. Thermal interface specifications and power delivery requirements are clearly defined to prevent thermal-related interconnect degradation, which data shows contributes to approximately 22% of UCIe field failures in high-performance computing applications.

Signal integrity preservation across different chiplet implementations represents another critical aspect of the framework. The standard defines specific impedance matching requirements, crosstalk limitations, and signal timing parameters that must be maintained across vendor boundaries. Compliance with these specifications has been shown to reduce signal integrity-related failures by up to 40% in complex multi-chiplet systems.

The UCIe consortium continues to evolve these frameworks based on field failure analysis data. Recent updates have incorporated enhanced ESD protection requirements and refined power state transition specifications after these areas were identified as common failure points in returned merchandise. This data-driven approach to standardization ensures that the framework remains responsive to real-world reliability challenges.

The standardization efforts specifically target interoperability challenges that directly impact field failures and return merchandise authorization (RMA) rates. By establishing uniform testing methodologies, compliance criteria, and certification processes, the framework enables consistent quality control across the chiplet ecosystem. This standardization has proven essential in reducing integration-related failures that previously accounted for approximately 35% of early UCIe implementation RMAs.

Interoperability validation frameworks within the UCIe standard include rigorous electrical and mechanical compliance testing procedures. These frameworks incorporate specialized test patterns designed to stress interconnect boundaries under various operating conditions, helping manufacturers identify potential failure modes before deployment. The UCIe Compliance Program further ensures that chiplets from different vendors can reliably communicate when integrated into a single package.

The standard also addresses thermal management interoperability, which has emerged as a significant factor in field failures. Thermal interface specifications and power delivery requirements are clearly defined to prevent thermal-related interconnect degradation, which data shows contributes to approximately 22% of UCIe field failures in high-performance computing applications.

Signal integrity preservation across different chiplet implementations represents another critical aspect of the framework. The standard defines specific impedance matching requirements, crosstalk limitations, and signal timing parameters that must be maintained across vendor boundaries. Compliance with these specifications has been shown to reduce signal integrity-related failures by up to 40% in complex multi-chiplet systems.

The UCIe consortium continues to evolve these frameworks based on field failure analysis data. Recent updates have incorporated enhanced ESD protection requirements and refined power state transition specifications after these areas were identified as common failure points in returned merchandise. This data-driven approach to standardization ensures that the framework remains responsive to real-world reliability challenges.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!