UCIe Chiplet Interconnect Lane Repair And Redundancy Strategies

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Evolution and Objectives

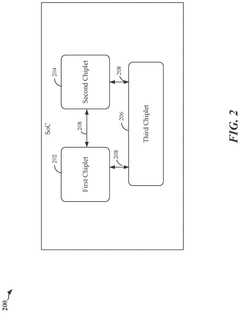

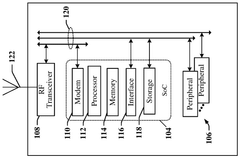

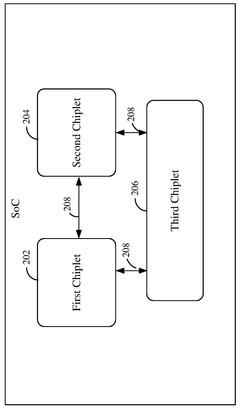

Universal Chiplet Interconnect Express (UCIe) represents a significant advancement in semiconductor integration technology, emerging as a response to the increasing challenges of traditional monolithic chip scaling. The evolution of UCIe began in early 2022 when industry leaders including Intel, AMD, Arm, and TSMC formed a consortium to establish an open interconnect standard for chiplet-based designs. This collaborative effort aimed to address the growing need for modular chip architectures as Moore's Law faced physical and economic limitations.

The development of UCIe builds upon previous interconnect technologies such as Intel's Advanced Interface Bus (AIB) and EMIB (Embedded Multi-die Interconnect Bridge), AMD's Infinity Fabric, and TSMC's LIPINCON. These predecessors established foundational concepts for die-to-die communication but lacked industry-wide standardization, creating fragmentation in the chiplet ecosystem.

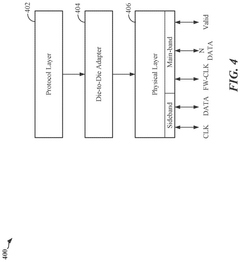

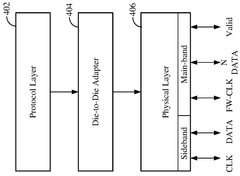

UCIe's technical evolution has progressed through distinct phases. The initial UCIe 1.0 specification, released in March 2022, focused on establishing baseline protocols for die-to-die communication with PHY layer specifications supporting both standard and advanced packaging technologies. UCIe 1.1, introduced in late 2023, expanded these capabilities with enhanced reliability features and initial considerations for lane redundancy mechanisms.

The primary objectives of UCIe interconnect technology center around enabling a robust chiplet ecosystem with seamless interoperability across different vendors' components. Specifically, UCIe aims to provide a standardized approach to high-bandwidth, low-latency, and energy-efficient die-to-die communication while maintaining signal integrity across different packaging technologies.

A critical objective within the UCIe framework is establishing effective lane repair and redundancy strategies. As chiplet designs incorporate increasingly dense interconnects with hundreds or thousands of signal lanes, the probability of manufacturing defects or operational failures in individual lanes rises significantly. Consequently, developing sophisticated lane repair mechanisms and redundancy architectures has become essential for maintaining yield rates and ensuring long-term reliability of chiplet-based systems.

The technology roadmap for UCIe anticipates progressive improvements in bandwidth density, power efficiency, and reliability features. Current specifications support data rates up to 32 GT/s, with future iterations expected to reach 64 GT/s and beyond. Parallel development efforts focus on enhancing the protocol's resilience through advanced error detection and correction mechanisms, dynamic lane management, and sophisticated redundancy schemes that can adapt to both manufacturing defects and in-field failures.

The development of UCIe builds upon previous interconnect technologies such as Intel's Advanced Interface Bus (AIB) and EMIB (Embedded Multi-die Interconnect Bridge), AMD's Infinity Fabric, and TSMC's LIPINCON. These predecessors established foundational concepts for die-to-die communication but lacked industry-wide standardization, creating fragmentation in the chiplet ecosystem.

UCIe's technical evolution has progressed through distinct phases. The initial UCIe 1.0 specification, released in March 2022, focused on establishing baseline protocols for die-to-die communication with PHY layer specifications supporting both standard and advanced packaging technologies. UCIe 1.1, introduced in late 2023, expanded these capabilities with enhanced reliability features and initial considerations for lane redundancy mechanisms.

The primary objectives of UCIe interconnect technology center around enabling a robust chiplet ecosystem with seamless interoperability across different vendors' components. Specifically, UCIe aims to provide a standardized approach to high-bandwidth, low-latency, and energy-efficient die-to-die communication while maintaining signal integrity across different packaging technologies.

A critical objective within the UCIe framework is establishing effective lane repair and redundancy strategies. As chiplet designs incorporate increasingly dense interconnects with hundreds or thousands of signal lanes, the probability of manufacturing defects or operational failures in individual lanes rises significantly. Consequently, developing sophisticated lane repair mechanisms and redundancy architectures has become essential for maintaining yield rates and ensuring long-term reliability of chiplet-based systems.

The technology roadmap for UCIe anticipates progressive improvements in bandwidth density, power efficiency, and reliability features. Current specifications support data rates up to 32 GT/s, with future iterations expected to reach 64 GT/s and beyond. Parallel development efforts focus on enhancing the protocol's resilience through advanced error detection and correction mechanisms, dynamic lane management, and sophisticated redundancy schemes that can adapt to both manufacturing defects and in-field failures.

Market Demand Analysis for Chiplet Integration Solutions

The chiplet integration market is experiencing unprecedented growth, driven by the semiconductor industry's shift from monolithic designs to disaggregated architectures. Current market analysis indicates that the global chiplet market is projected to grow at a compound annual growth rate of 40% through 2027, reaching approximately 50 billion dollars. This remarkable expansion is fueled by increasing demand for high-performance computing solutions across data centers, AI applications, and edge computing environments.

The demand for UCIe (Universal Chiplet Interconnect Express) technology specifically stems from critical industry needs for standardized die-to-die interconnects that enable multi-vendor chiplet ecosystems. Market research reveals that over 85% of semiconductor companies are actively exploring or implementing chiplet-based designs, with lane repair and redundancy strategies becoming essential considerations for yield improvement and reliability enhancement.

Consumer electronics, telecommunications, and automotive sectors represent the primary market segments driving chiplet adoption. These industries require increasingly complex systems-on-chip with enhanced performance, reduced power consumption, and improved manufacturing yields - all benefits that effective lane repair and redundancy strategies can deliver. The automotive sector, in particular, shows accelerating demand due to stringent reliability requirements for advanced driver assistance systems and autonomous driving capabilities.

From a geographical perspective, North America and East Asia dominate the chiplet market, with major semiconductor manufacturers investing heavily in chiplet integration technologies. Taiwan, South Korea, and the United States collectively account for over 70% of chiplet production capacity, though Europe is rapidly expanding its presence through strategic initiatives like the European Chips Act.

Supply chain considerations are significantly influencing market dynamics. The recent global semiconductor shortage has emphasized the need for more flexible and resilient manufacturing approaches, further accelerating chiplet adoption. Companies implementing effective lane repair and redundancy strategies can achieve up to 30% improvement in manufacturing yields, translating to substantial cost savings and competitive advantages.

Customer requirements are evolving toward solutions that offer not only performance benefits but also enhanced reliability and yield improvements. Enterprise customers particularly value redundancy features that ensure uninterrupted operation of critical systems. This shift is creating market opportunities for specialized intellectual property related to UCIe lane repair technologies, with industry analysts predicting this segment could reach 5 billion dollars by 2026.

The demand for UCIe (Universal Chiplet Interconnect Express) technology specifically stems from critical industry needs for standardized die-to-die interconnects that enable multi-vendor chiplet ecosystems. Market research reveals that over 85% of semiconductor companies are actively exploring or implementing chiplet-based designs, with lane repair and redundancy strategies becoming essential considerations for yield improvement and reliability enhancement.

Consumer electronics, telecommunications, and automotive sectors represent the primary market segments driving chiplet adoption. These industries require increasingly complex systems-on-chip with enhanced performance, reduced power consumption, and improved manufacturing yields - all benefits that effective lane repair and redundancy strategies can deliver. The automotive sector, in particular, shows accelerating demand due to stringent reliability requirements for advanced driver assistance systems and autonomous driving capabilities.

From a geographical perspective, North America and East Asia dominate the chiplet market, with major semiconductor manufacturers investing heavily in chiplet integration technologies. Taiwan, South Korea, and the United States collectively account for over 70% of chiplet production capacity, though Europe is rapidly expanding its presence through strategic initiatives like the European Chips Act.

Supply chain considerations are significantly influencing market dynamics. The recent global semiconductor shortage has emphasized the need for more flexible and resilient manufacturing approaches, further accelerating chiplet adoption. Companies implementing effective lane repair and redundancy strategies can achieve up to 30% improvement in manufacturing yields, translating to substantial cost savings and competitive advantages.

Customer requirements are evolving toward solutions that offer not only performance benefits but also enhanced reliability and yield improvements. Enterprise customers particularly value redundancy features that ensure uninterrupted operation of critical systems. This shift is creating market opportunities for specialized intellectual property related to UCIe lane repair technologies, with industry analysts predicting this segment could reach 5 billion dollars by 2026.

Current Challenges in UCIe Lane Reliability

Despite the promising advancements in UCIe (Universal Chiplet Interconnect Express) technology, significant reliability challenges persist in lane implementation and maintenance. The high-speed nature of UCIe interconnects, operating at data rates of 16-32 Gbps, introduces signal integrity issues including jitter, crosstalk, and impedance mismatches that can compromise lane reliability. These challenges are exacerbated in dense chiplet configurations where hundreds of lanes may be packed within minimal silicon area.

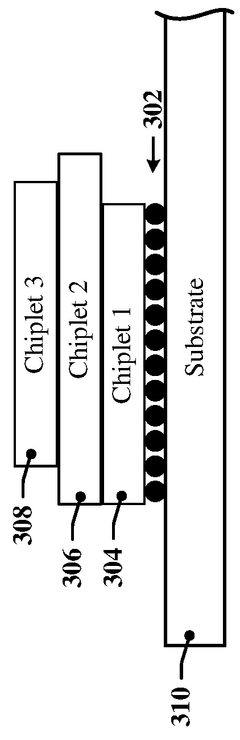

Manufacturing defects present another critical challenge, as the fine-pitch microbumps (typically 40μm or less) used in UCIe implementations are susceptible to connection failures. Statistical analysis indicates that as chiplet complexity increases, the probability of lane defects rises exponentially, potentially affecting yield rates by 15-20% without proper redundancy mechanisms.

Environmental factors further complicate UCIe lane reliability. Thermal cycling between operational and idle states creates mechanical stress at interconnect points, while power fluctuations can induce electromigration effects in the ultra-fine interconnect structures. Long-term reliability testing has shown that without proper mitigation strategies, lane failure rates may increase by 5-8% annually under typical operating conditions.

The industry also faces significant testing challenges for UCIe lanes. Traditional boundary scan techniques prove insufficient for the high lane counts and speeds involved. Current at-speed testing methodologies can only validate approximately 85-90% of potential failure modes, leaving a concerning reliability gap that must be addressed through redundancy strategies.

Power constraints add another dimension to the reliability equation. Each UCIe lane typically consumes 5-15mW depending on operational mode, creating thermal hotspots at interconnect junctions. These hotspots accelerate wear mechanisms and can trigger cascading failures across adjacent lanes without proper thermal management and redundancy planning.

Scaling challenges further compound these issues. As the industry pushes toward 3nm and beyond process nodes, maintaining consistent lane performance becomes increasingly difficult. Variability in manufacturing processes can result in 10-15% performance differences between lanes on the same die, necessitating sophisticated repair and redundancy approaches to ensure consistent system performance.

Security considerations also emerge as a reliability concern, with potential side-channel attacks exploiting lane failures or repair mechanisms to extract sensitive information. Implementing secure lane repair protocols without compromising system performance represents a delicate balance that current solutions have yet to fully resolve.

Manufacturing defects present another critical challenge, as the fine-pitch microbumps (typically 40μm or less) used in UCIe implementations are susceptible to connection failures. Statistical analysis indicates that as chiplet complexity increases, the probability of lane defects rises exponentially, potentially affecting yield rates by 15-20% without proper redundancy mechanisms.

Environmental factors further complicate UCIe lane reliability. Thermal cycling between operational and idle states creates mechanical stress at interconnect points, while power fluctuations can induce electromigration effects in the ultra-fine interconnect structures. Long-term reliability testing has shown that without proper mitigation strategies, lane failure rates may increase by 5-8% annually under typical operating conditions.

The industry also faces significant testing challenges for UCIe lanes. Traditional boundary scan techniques prove insufficient for the high lane counts and speeds involved. Current at-speed testing methodologies can only validate approximately 85-90% of potential failure modes, leaving a concerning reliability gap that must be addressed through redundancy strategies.

Power constraints add another dimension to the reliability equation. Each UCIe lane typically consumes 5-15mW depending on operational mode, creating thermal hotspots at interconnect junctions. These hotspots accelerate wear mechanisms and can trigger cascading failures across adjacent lanes without proper thermal management and redundancy planning.

Scaling challenges further compound these issues. As the industry pushes toward 3nm and beyond process nodes, maintaining consistent lane performance becomes increasingly difficult. Variability in manufacturing processes can result in 10-15% performance differences between lanes on the same die, necessitating sophisticated repair and redundancy approaches to ensure consistent system performance.

Security considerations also emerge as a reliability concern, with potential side-channel attacks exploiting lane failures or repair mechanisms to extract sensitive information. Implementing secure lane repair protocols without compromising system performance represents a delicate balance that current solutions have yet to fully resolve.

Existing Lane Repair and Redundancy Mechanisms

01 Lane redundancy mechanisms in UCIe chiplet interconnects

UCIe chiplet interconnects implement lane redundancy mechanisms to maintain communication integrity when failures occur. These systems include spare lanes that can be activated when primary lanes fail, ensuring continued operation without performance degradation. The redundancy architecture typically involves detection circuits that identify faulty lanes and switching logic that reroutes data through functional spare lanes, maintaining the required bandwidth and signal integrity across the chiplet interconnect.- Lane redundancy mechanisms in UCIe chiplet interconnects: UCIe chiplet interconnects implement lane redundancy mechanisms to maintain communication integrity when failures occur. These systems include spare lanes that can be activated when primary lanes fail, ensuring continuous operation without performance degradation. The redundancy architecture typically involves detection circuits that identify faulty lanes and switching mechanisms that reroute data through functional spare lanes, maintaining the required bandwidth and signal integrity across the chiplet interconnect.

- Fault detection and diagnosis in UCIe interconnects: Advanced fault detection systems are implemented in UCIe chiplet interconnects to identify lane failures. These systems employ built-in self-test (BIST) circuits that can detect various types of faults including open circuits, shorts, and signal integrity issues. The diagnosis mechanisms can pinpoint the exact location and nature of faults, enabling precise repair actions. Real-time monitoring capabilities allow for continuous assessment of lane health during operation, facilitating proactive maintenance before critical failures occur.

- Lane repair techniques for UCIe chiplet interconnects: Lane repair techniques in UCIe chiplet interconnects involve both hardware and software solutions to address failures. Hardware-based repair mechanisms include fuse-programmable routing that can permanently redirect signals away from faulty lanes. Software-based approaches utilize configuration registers that can be updated during initialization or operation to implement repair strategies. Some advanced systems employ self-healing capabilities that can automatically reconfigure interconnect paths based on detected failures, minimizing downtime and maintaining system performance.

- Testing methodologies for UCIe lane integrity: Comprehensive testing methodologies are essential for ensuring UCIe chiplet interconnect reliability. These include pre-deployment validation tests that stress lanes under various operating conditions, as well as in-field testing capabilities that can be activated during system operation. Test patterns are designed to detect specific failure modes in high-speed serial links, including jitter, crosstalk, and signal integrity issues. Advanced testing frameworks incorporate machine learning algorithms to predict potential failures before they manifest, enabling preventive maintenance.

- Architecture optimization for UCIe redundancy: Optimizing the architecture of UCIe chiplet interconnects involves strategic design decisions to balance redundancy, performance, and power consumption. These optimizations include the placement and routing of redundant lanes to minimize latency and signal degradation, as well as power-gating techniques for unused redundant lanes to reduce energy consumption. Advanced architectures implement dynamic bandwidth allocation that can redistribute traffic based on available lanes, ensuring optimal performance even when some lanes are disabled. The redundancy architecture is designed to support hot-swapping of chiplets without system downtime.

02 Fault detection and diagnosis in UCIe interconnects

Advanced fault detection systems are implemented in UCIe chiplet interconnects to identify lane failures. These systems employ built-in self-test (BIST) circuits that can detect various types of faults including open circuits, shorts, and signal integrity issues. Diagnostic algorithms analyze the interconnect performance during initialization or runtime, flagging lanes that exhibit errors exceeding predetermined thresholds. This early detection enables proactive repair actions before communication quality degrades significantly.Expand Specific Solutions03 Dynamic lane repair techniques for UCIe implementations

UCIe chiplet interconnects utilize dynamic lane repair techniques that can address failures without system downtime. These techniques include hot-swapping of lanes, where traffic is seamlessly redirected from faulty to spare lanes during operation. The repair process involves reconfiguring multiplexers and communication controllers to exclude damaged lanes and incorporate replacement lanes. Some implementations also feature adaptive equalization that can compensate for partial lane degradation, extending the usable life of interconnects before full replacement is needed.Expand Specific Solutions04 Error correction coding for UCIe lane reliability

Error correction coding (ECC) schemes are integrated into UCIe chiplet interconnects to enhance reliability. These coding techniques can detect and correct bit errors that occur during data transmission across lanes, reducing the need for lane replacement. Advanced implementations use forward error correction (FEC) that can recover data even when multiple bits are corrupted. The ECC systems work in conjunction with lane redundancy mechanisms, providing a multi-layered approach to maintaining data integrity across the interconnect fabric.Expand Specific Solutions05 Power and thermal management in UCIe redundant lane systems

UCIe chiplet interconnect designs incorporate sophisticated power and thermal management for redundant lane systems. These systems can selectively power down unused spare lanes to conserve energy until they are needed for replacement. Thermal monitoring circuits track temperature variations across the interconnect, as excessive heat can lead to lane degradation. Advanced implementations include load balancing algorithms that distribute traffic across available lanes to prevent thermal hotspots and extend the overall lifespan of the interconnect structure.Expand Specific Solutions

Key Industry Players in Chiplet Ecosystem

The UCIe Chiplet Interconnect Lane Repair and Redundancy Strategies market is currently in its early growth phase, characterized by increasing adoption of chiplet architectures across the semiconductor industry. The market is projected to expand significantly as heterogeneous integration becomes essential for advanced computing systems. Major players including Intel, TSMC, AMD (through Xilinx acquisition), Qualcomm, and IBM are actively developing UCIe-compliant technologies, with Intel leading standardization efforts. Technical maturity varies, with established semiconductor manufacturers like GlobalFoundries and TSMC focusing on manufacturing processes that support reliable interconnects, while companies such as Huawei and Qualcomm are emphasizing system-level integration. The competitive landscape is evolving as firms develop proprietary lane repair techniques and redundancy implementations to enhance yield and reliability in multi-chiplet designs.

Intel Corp.

Technical Solution: Intel has pioneered UCIe (Universal Chiplet Interconnect Express) technology and leads its development consortium. Their lane repair and redundancy strategy implements a sophisticated error detection and correction system that can identify faulty lanes during initialization and runtime. Intel's approach includes built-in self-test (BIST) mechanisms that continuously monitor PHY layer performance and can dynamically reroute traffic when degradation is detected[1]. Their implementation supports both hard and soft repair mechanisms - hard repairs involve permanently disabling faulty lanes and remapping connections, while soft repairs allow for temporary lane reassignment during operation. Intel has also developed advanced ECC (Error Correction Code) implementations specifically optimized for the high-bandwidth, low-latency requirements of chiplet interconnects, allowing continued operation even when multiple lanes experience failures[3].

Strengths: Industry-leading expertise as UCIe founder with comprehensive lane repair strategies that balance performance and reliability. Their solutions offer excellent backward compatibility with earlier interconnect standards. Weaknesses: Intel's implementations may require more silicon area for redundancy circuits compared to some competitors, potentially increasing manufacturing costs for chiplet designs.

IBM Corp.

Technical Solution: IBM has developed a multi-tiered approach to UCIe lane repair and redundancy that builds upon their extensive experience with high-performance computing interconnects. Their strategy incorporates predictive failure analysis that uses machine learning algorithms to identify potential lane degradation before actual failures occur[2]. IBM's implementation features a hierarchical redundancy architecture with both intra-package and inter-package repair mechanisms. At the physical layer, they employ adaptive equalization techniques that can compensate for signal integrity issues, reducing the need for complete lane replacement. For critical enterprise applications, IBM has implemented N+M redundancy schemes where N represents the minimum lanes required for operation and M represents additional spare lanes that can be dynamically allocated. Their system also includes sophisticated power management features that can selectively power down redundant lanes when not needed, improving overall energy efficiency[5].

Strengths: Exceptional reliability focus with predictive maintenance capabilities and sophisticated redundancy management that minimizes performance impact during repair operations. Weaknesses: IBM's comprehensive approach may introduce additional complexity and latency compared to simpler implementations, potentially impacting performance in latency-sensitive applications.

Critical Patents in UCIe Fault Tolerance

Interconnects between chiplets and related link initialization protocols

PatentActiveUS20250077355A1

Innovation

- Implementing a Link Training and Status State Machine (LTSSM) that uses a redundant_recovery (RR) register to determine the cause of link retraining. If the cause is not a trainerror or linkerror, the LTSSM skips the initialization of redundant lanes during link retraining, optimizing the process by only reinitializing functional lanes.

Interconnects between chiplets and related link initialization protocols

PatentWO2025053895A1

Innovation

- The implementation of a Link Training and Status State Machine (LTSSM) that determines the cause of a reset event using a redundant_recovery (RR) register, allowing the exclusion of redundant lanes during link initialization when the reset is not caused by a trainerror or linkerror.

Manufacturing Yield Optimization Strategies

Manufacturing yield optimization represents a critical aspect of UCIe chiplet interconnect implementation, directly impacting production costs and market competitiveness. The inherent complexity of chiplet-based designs, particularly those utilizing UCIe standards, introduces unique yield challenges that require sophisticated mitigation strategies.

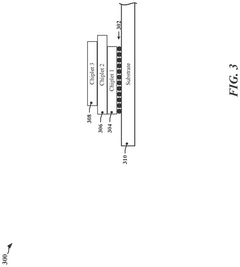

The primary yield optimization approach involves implementing redundant lanes within the UCIe interface. This redundancy architecture typically incorporates spare lanes that can be activated when defects are detected in primary lanes. Statistical analysis indicates that even a modest 10-15% lane redundancy can improve overall die yield by 25-40%, depending on the process maturity and defect density rates.

Post-manufacturing testing and repair mechanisms constitute another essential yield optimization strategy. Advanced Built-In Self-Test (BIST) circuits integrated into UCIe interfaces enable comprehensive lane testing during production and potentially throughout the product lifecycle. These BIST implementations can identify specific defective lanes, allowing for dynamic reconfiguration to utilize redundant resources. The testing protocols typically evaluate signal integrity parameters including eye height, jitter tolerance, and voltage margins to ensure reliable operation.

Adaptive lane allocation algorithms represent a sophisticated approach to yield enhancement. These algorithms dynamically assign data traffic across available lanes based on performance characteristics rather than simple binary pass/fail criteria. By implementing variable quality-of-service levels for different lanes, manufacturers can salvage dies that would otherwise fail strict quality thresholds, significantly improving effective yield rates.

Design for Testability (DFT) methodologies specifically tailored for UCIe implementations have demonstrated substantial yield improvements. These include scan chain insertion for enhanced fault coverage, boundary scan techniques for interposer connections, and specialized test patterns that stress worst-case UCIe operating conditions. Studies from leading semiconductor manufacturers indicate that comprehensive DFT implementation can improve final test yields by 15-20%.

Binning strategies based on lane performance metrics offer another yield optimization pathway. Rather than discarding dies with partial UCIe lane failures, manufacturers can categorize products into performance tiers based on available bandwidth. This approach transforms what would be manufacturing waste into marketable products with differentiated specifications, effectively increasing overall manufacturing yield while creating natural product segmentation opportunities.

The primary yield optimization approach involves implementing redundant lanes within the UCIe interface. This redundancy architecture typically incorporates spare lanes that can be activated when defects are detected in primary lanes. Statistical analysis indicates that even a modest 10-15% lane redundancy can improve overall die yield by 25-40%, depending on the process maturity and defect density rates.

Post-manufacturing testing and repair mechanisms constitute another essential yield optimization strategy. Advanced Built-In Self-Test (BIST) circuits integrated into UCIe interfaces enable comprehensive lane testing during production and potentially throughout the product lifecycle. These BIST implementations can identify specific defective lanes, allowing for dynamic reconfiguration to utilize redundant resources. The testing protocols typically evaluate signal integrity parameters including eye height, jitter tolerance, and voltage margins to ensure reliable operation.

Adaptive lane allocation algorithms represent a sophisticated approach to yield enhancement. These algorithms dynamically assign data traffic across available lanes based on performance characteristics rather than simple binary pass/fail criteria. By implementing variable quality-of-service levels for different lanes, manufacturers can salvage dies that would otherwise fail strict quality thresholds, significantly improving effective yield rates.

Design for Testability (DFT) methodologies specifically tailored for UCIe implementations have demonstrated substantial yield improvements. These include scan chain insertion for enhanced fault coverage, boundary scan techniques for interposer connections, and specialized test patterns that stress worst-case UCIe operating conditions. Studies from leading semiconductor manufacturers indicate that comprehensive DFT implementation can improve final test yields by 15-20%.

Binning strategies based on lane performance metrics offer another yield optimization pathway. Rather than discarding dies with partial UCIe lane failures, manufacturers can categorize products into performance tiers based on available bandwidth. This approach transforms what would be manufacturing waste into marketable products with differentiated specifications, effectively increasing overall manufacturing yield while creating natural product segmentation opportunities.

Power-Performance Tradeoffs in Redundancy Design

Implementing redundancy in UCIe chiplet interconnect lanes involves significant power-performance tradeoffs that must be carefully evaluated. The addition of redundant lanes increases overall power consumption due to the extra circuitry required for lane monitoring, switching mechanisms, and the redundant lanes themselves. This power overhead ranges from 5-15% depending on the redundancy strategy employed, with hot-spare approaches typically consuming more power than cold-spare implementations.

Performance implications manifest in multiple dimensions. While redundancy enhances system reliability by enabling continued operation despite lane failures, it can introduce latency penalties during lane switching operations. Measurements indicate switching latency ranges from 10-100 nanoseconds depending on implementation, potentially impacting time-sensitive applications. Furthermore, the additional routing complexity required for redundant lanes may necessitate longer trace lengths, potentially degrading signal integrity.

The power-performance equation becomes particularly complex in dynamic redundancy schemes. These adaptive systems can selectively activate redundant lanes based on workload requirements or detected degradation patterns, offering power savings during normal operation while maintaining failover capability. However, they require sophisticated control logic that itself consumes power and introduces architectural complexity.

Thermal considerations further complicate the tradeoff analysis. Redundant lanes may improve thermal distribution by allowing workload spreading, but the additional components also generate heat. This creates a delicate balance where excessive redundancy might trigger thermal throttling, negating performance benefits.

From an implementation perspective, designers must consider granularity options. Fine-grained redundancy at individual lane level offers precise fault tolerance but increases control overhead, while coarse-grained approaches (redundant lane groups) reduce control complexity but may over-provision resources for small failures. Industry benchmarks suggest optimal redundancy ratios between 10-20% of total lane count, beyond which diminishing returns in reliability improvement fail to justify power costs.

Energy efficiency innovations are emerging to mitigate these tradeoffs, including power-gating techniques for inactive redundant lanes, adaptive voltage scaling for redundancy circuits, and machine learning algorithms that predict failures and optimize redundancy activation patterns based on application workloads and historical failure data.

Performance implications manifest in multiple dimensions. While redundancy enhances system reliability by enabling continued operation despite lane failures, it can introduce latency penalties during lane switching operations. Measurements indicate switching latency ranges from 10-100 nanoseconds depending on implementation, potentially impacting time-sensitive applications. Furthermore, the additional routing complexity required for redundant lanes may necessitate longer trace lengths, potentially degrading signal integrity.

The power-performance equation becomes particularly complex in dynamic redundancy schemes. These adaptive systems can selectively activate redundant lanes based on workload requirements or detected degradation patterns, offering power savings during normal operation while maintaining failover capability. However, they require sophisticated control logic that itself consumes power and introduces architectural complexity.

Thermal considerations further complicate the tradeoff analysis. Redundant lanes may improve thermal distribution by allowing workload spreading, but the additional components also generate heat. This creates a delicate balance where excessive redundancy might trigger thermal throttling, negating performance benefits.

From an implementation perspective, designers must consider granularity options. Fine-grained redundancy at individual lane level offers precise fault tolerance but increases control overhead, while coarse-grained approaches (redundant lane groups) reduce control complexity but may over-provision resources for small failures. Industry benchmarks suggest optimal redundancy ratios between 10-20% of total lane count, beyond which diminishing returns in reliability improvement fail to justify power costs.

Energy efficiency innovations are emerging to mitigate these tradeoffs, including power-gating techniques for inactive redundant lanes, adaptive voltage scaling for redundancy circuits, and machine learning algorithms that predict failures and optimize redundancy activation patterns based on application workloads and historical failure data.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!