UCIe Chiplet Interconnect Multi-Vendor Interoperability Standards

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Technology Evolution and Objectives

The Universal Chiplet Interconnect Express (UCIe) represents a significant evolution in semiconductor integration technology, emerging from the limitations of traditional monolithic chip designs. As Moore's Law faces increasing physical and economic constraints, the industry has pivoted toward chiplet-based architectures that enable the disaggregation of system-on-chip (SoC) designs into smaller, specialized components. This paradigm shift addresses critical challenges in modern semiconductor manufacturing, including yield management, design complexity, and cost optimization.

The historical trajectory of chiplet technology began with proprietary interconnect solutions developed by major semiconductor companies like AMD, Intel, and TSMC. These early implementations demonstrated the viability of multi-die packaging but lacked standardization, creating significant barriers to ecosystem development and vendor interoperability. The formation of the UCIe consortium in March 2022 marked a pivotal moment, bringing together industry leaders to establish a unified standard for chiplet interconnection.

UCIe technology aims to create an open ecosystem where chiplets from different vendors can seamlessly integrate within a single package. This standardization effort focuses on defining both physical and protocol layers for die-to-die communication, with particular emphasis on maintaining high bandwidth, low latency, and power efficiency across the interconnect interface. The standard encompasses multiple packaging technologies, including silicon interposers and organic substrates, providing flexibility for various application requirements.

The primary technical objectives of UCIe include establishing a standardized physical interface for chiplet communication, defining protocol specifications that ensure interoperability, and creating a robust testing and validation framework. Additionally, the standard aims to support scalability across different performance tiers, from high-performance computing applications to power-constrained edge devices, while maintaining backward compatibility for future iterations.

From a market perspective, UCIe technology targets several strategic objectives. It seeks to accelerate innovation by enabling specialized silicon development, reduce time-to-market through modular design approaches, and create new business models centered around chiplet intellectual property. The standard also aims to democratize advanced packaging technologies, allowing smaller companies to participate in the high-performance computing market without the massive capital investments traditionally required.

Looking forward, the UCIe roadmap envisions progressive improvements in bandwidth density, energy efficiency, and signal integrity. The consortium has established working groups focused on expanding the specification to address emerging requirements in artificial intelligence, high-performance computing, and edge applications, with particular attention to thermal management challenges and advanced packaging techniques.

The historical trajectory of chiplet technology began with proprietary interconnect solutions developed by major semiconductor companies like AMD, Intel, and TSMC. These early implementations demonstrated the viability of multi-die packaging but lacked standardization, creating significant barriers to ecosystem development and vendor interoperability. The formation of the UCIe consortium in March 2022 marked a pivotal moment, bringing together industry leaders to establish a unified standard for chiplet interconnection.

UCIe technology aims to create an open ecosystem where chiplets from different vendors can seamlessly integrate within a single package. This standardization effort focuses on defining both physical and protocol layers for die-to-die communication, with particular emphasis on maintaining high bandwidth, low latency, and power efficiency across the interconnect interface. The standard encompasses multiple packaging technologies, including silicon interposers and organic substrates, providing flexibility for various application requirements.

The primary technical objectives of UCIe include establishing a standardized physical interface for chiplet communication, defining protocol specifications that ensure interoperability, and creating a robust testing and validation framework. Additionally, the standard aims to support scalability across different performance tiers, from high-performance computing applications to power-constrained edge devices, while maintaining backward compatibility for future iterations.

From a market perspective, UCIe technology targets several strategic objectives. It seeks to accelerate innovation by enabling specialized silicon development, reduce time-to-market through modular design approaches, and create new business models centered around chiplet intellectual property. The standard also aims to democratize advanced packaging technologies, allowing smaller companies to participate in the high-performance computing market without the massive capital investments traditionally required.

Looking forward, the UCIe roadmap envisions progressive improvements in bandwidth density, energy efficiency, and signal integrity. The consortium has established working groups focused on expanding the specification to address emerging requirements in artificial intelligence, high-performance computing, and edge applications, with particular attention to thermal management challenges and advanced packaging techniques.

Market Demand Analysis for Chiplet Interconnect Solutions

The chiplet interconnect market is experiencing unprecedented growth driven by the semiconductor industry's shift towards disaggregated chip designs. As traditional monolithic chip scaling faces physical and economic limitations under Moore's Law, chiplet-based architectures have emerged as a compelling alternative. Market research indicates the global chiplet market is projected to grow at a CAGR of 40% from 2023 to 2030, with the interconnect technologies representing a significant portion of this expansion.

The primary market demand for UCIe (Universal Chiplet Interconnect Express) standards stems from the need to address mounting challenges in semiconductor manufacturing. These include rising design costs, yield issues with large monolithic dies, and the increasing complexity of integrating diverse functionalities on a single chip. The standardization of chiplet interfaces enables semiconductor companies to mix and match components from different vendors, significantly reducing development cycles and costs.

Data center and cloud computing sectors represent the largest immediate market for UCIe technology, with hyperscalers actively seeking ways to customize silicon solutions while maintaining cost efficiency. These companies require high-bandwidth, low-latency connections between compute, memory, and accelerator chiplets to optimize performance for AI/ML workloads, which have grown by over 300% in processing demands over the past three years.

The automotive and industrial sectors are emerging as secondary markets with substantial growth potential. Advanced driver-assistance systems and autonomous vehicles require heterogeneous computing platforms that can be efficiently designed using chiplet-based architectures. Market analysis shows that approximately 70% of automotive semiconductor companies are exploring chiplet-based designs for their next-generation products.

Consumer electronics manufacturers are also showing increased interest in chiplet technology, particularly for high-performance mobile devices and gaming systems. The ability to integrate specialized processing units while maintaining power efficiency represents a significant value proposition in these markets.

From a supply chain perspective, UCIe standards address the critical need for resilience and flexibility. The semiconductor industry has experienced severe disruptions in recent years, highlighting the strategic importance of diversified sourcing options. UCIe's multi-vendor interoperability directly responds to this need by enabling companies to source chiplets from various suppliers without compatibility concerns.

The economic benefits of chiplet adoption are compelling, with industry reports suggesting potential cost reductions of 25-30% for complex system-on-chip designs when implemented using a chiplet approach. This cost advantage, combined with faster time-to-market and improved yield management, creates strong market pull for standardized interconnect solutions like UCIe.

The primary market demand for UCIe (Universal Chiplet Interconnect Express) standards stems from the need to address mounting challenges in semiconductor manufacturing. These include rising design costs, yield issues with large monolithic dies, and the increasing complexity of integrating diverse functionalities on a single chip. The standardization of chiplet interfaces enables semiconductor companies to mix and match components from different vendors, significantly reducing development cycles and costs.

Data center and cloud computing sectors represent the largest immediate market for UCIe technology, with hyperscalers actively seeking ways to customize silicon solutions while maintaining cost efficiency. These companies require high-bandwidth, low-latency connections between compute, memory, and accelerator chiplets to optimize performance for AI/ML workloads, which have grown by over 300% in processing demands over the past three years.

The automotive and industrial sectors are emerging as secondary markets with substantial growth potential. Advanced driver-assistance systems and autonomous vehicles require heterogeneous computing platforms that can be efficiently designed using chiplet-based architectures. Market analysis shows that approximately 70% of automotive semiconductor companies are exploring chiplet-based designs for their next-generation products.

Consumer electronics manufacturers are also showing increased interest in chiplet technology, particularly for high-performance mobile devices and gaming systems. The ability to integrate specialized processing units while maintaining power efficiency represents a significant value proposition in these markets.

From a supply chain perspective, UCIe standards address the critical need for resilience and flexibility. The semiconductor industry has experienced severe disruptions in recent years, highlighting the strategic importance of diversified sourcing options. UCIe's multi-vendor interoperability directly responds to this need by enabling companies to source chiplets from various suppliers without compatibility concerns.

The economic benefits of chiplet adoption are compelling, with industry reports suggesting potential cost reductions of 25-30% for complex system-on-chip designs when implemented using a chiplet approach. This cost advantage, combined with faster time-to-market and improved yield management, creates strong market pull for standardized interconnect solutions like UCIe.

Current UCIe Standards and Technical Challenges

The Universal Chiplet Interconnect Express (UCIe) standard, established in 2022, represents a significant advancement in chiplet integration technology. Currently, UCIe 1.0 specification defines both the die-to-die and package-to-package interconnect standards, focusing on two primary interface layers: the physical layer and the protocol layer. The physical layer encompasses electrical specifications, including signal integrity parameters, power delivery requirements, and mechanical considerations for chiplet integration. The protocol layer defines data transfer protocols, addressing schemes, and error handling mechanisms.

Despite its promising foundation, UCIe faces several critical technical challenges. Thermal management remains a primary concern as chiplet density increases, creating hotspots that can compromise system reliability. Current thermal solutions within the UCIe framework provide limited guidance for heterogeneous integration scenarios where different chiplets generate varying heat profiles.

Signal integrity issues present another significant challenge, particularly as data rates continue to escalate. The current UCIe standard supports data rates up to 16 GT/s, but maintaining signal quality across different vendor implementations has proven difficult. Cross-talk, impedance matching, and timing synchronization between chiplets from different manufacturers often require additional engineering efforts beyond the standard specifications.

Power delivery and management across multiple chiplets introduce complex challenges. The UCIe standard provides baseline power delivery network (PDN) specifications, but optimizing power distribution for chiplets with different voltage requirements and power profiles remains problematic. This is especially evident in mixed-process node implementations where advanced nodes (e.g., 5nm) are combined with mature nodes (e.g., 28nm).

Testing and validation methodologies represent another substantial hurdle. The current UCIe standard lacks comprehensive test protocols for multi-vendor interoperability scenarios. Known-good-die (KGD) testing approaches need enhancement to address the complexities of heterogeneous integration, particularly for fault isolation and performance verification across chiplet boundaries.

Security considerations within the UCIe framework remain underdeveloped. The standard provides limited mechanisms for secure boot, authentication between chiplets, and protection against side-channel attacks in multi-vendor environments. As chiplets potentially come from different security domains, establishing trust boundaries becomes increasingly complex.

Manufacturing yield and cost optimization continue to challenge widespread UCIe adoption. While the standard defines physical interfaces, it provides minimal guidance on design for manufacturability (DFM) practices that could improve yield in multi-vendor scenarios. The lack of standardized testing methodologies further complicates yield management across the supply chain.

Despite its promising foundation, UCIe faces several critical technical challenges. Thermal management remains a primary concern as chiplet density increases, creating hotspots that can compromise system reliability. Current thermal solutions within the UCIe framework provide limited guidance for heterogeneous integration scenarios where different chiplets generate varying heat profiles.

Signal integrity issues present another significant challenge, particularly as data rates continue to escalate. The current UCIe standard supports data rates up to 16 GT/s, but maintaining signal quality across different vendor implementations has proven difficult. Cross-talk, impedance matching, and timing synchronization between chiplets from different manufacturers often require additional engineering efforts beyond the standard specifications.

Power delivery and management across multiple chiplets introduce complex challenges. The UCIe standard provides baseline power delivery network (PDN) specifications, but optimizing power distribution for chiplets with different voltage requirements and power profiles remains problematic. This is especially evident in mixed-process node implementations where advanced nodes (e.g., 5nm) are combined with mature nodes (e.g., 28nm).

Testing and validation methodologies represent another substantial hurdle. The current UCIe standard lacks comprehensive test protocols for multi-vendor interoperability scenarios. Known-good-die (KGD) testing approaches need enhancement to address the complexities of heterogeneous integration, particularly for fault isolation and performance verification across chiplet boundaries.

Security considerations within the UCIe framework remain underdeveloped. The standard provides limited mechanisms for secure boot, authentication between chiplets, and protection against side-channel attacks in multi-vendor environments. As chiplets potentially come from different security domains, establishing trust boundaries becomes increasingly complex.

Manufacturing yield and cost optimization continue to challenge widespread UCIe adoption. While the standard defines physical interfaces, it provides minimal guidance on design for manufacturability (DFM) practices that could improve yield in multi-vendor scenarios. The lack of standardized testing methodologies further complicates yield management across the supply chain.

Current UCIe Implementation Approaches

01 UCIe architecture for chiplet interconnection

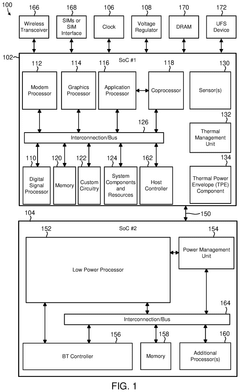

Universal Chiplet Interconnect Express (UCIe) provides a standardized architecture for connecting multiple chiplets within a package. This architecture enables high-speed, low-latency communication between different chiplets, supporting both die-to-die and package-to-package connections. The UCIe standard defines protocols, physical interfaces, and electrical specifications to ensure consistent performance across different implementations, facilitating the development of heterogeneous integrated systems.- UCIe architecture for chiplet interoperability: Universal Chiplet Interconnect Express (UCIe) architecture provides a standardized framework for connecting chiplets from different vendors. This architecture defines protocols, physical interfaces, and electrical specifications to ensure seamless integration of heterogeneous chiplets. The standardization enables multi-vendor chiplets to communicate effectively while maintaining performance, power efficiency, and reliability across different manufacturing processes and technologies.

- Testing and validation methods for UCIe compliance: Various testing and validation methodologies ensure chiplets from different vendors comply with UCIe specifications. These methods include interoperability testing frameworks, compliance verification tools, and certification processes that validate signal integrity, timing parameters, and protocol adherence. Automated test equipment and specialized test fixtures are used to verify that chiplets meet the electrical and functional requirements of the UCIe standard, ensuring reliable multi-vendor integration.

- Power management and thermal solutions for UCIe implementations: Power management techniques and thermal solutions are critical for UCIe chiplet implementations. These include dynamic voltage and frequency scaling, power state management across chiplet boundaries, and thermal monitoring systems that coordinate across multiple vendors' components. Advanced cooling solutions and thermal interface materials are designed to address the unique challenges of heterogeneous integration, ensuring reliable operation while maximizing energy efficiency in multi-vendor chiplet systems.

- Packaging technologies for UCIe chiplet integration: Advanced packaging technologies enable effective integration of UCIe-compliant chiplets from multiple vendors. These include 2.5D and 3D integration approaches, silicon interposers, and organic substrates with high-density interconnects. Specialized die-to-die bonding techniques, micro-bumping technologies, and through-silicon vias (TSVs) facilitate the physical integration of heterogeneous chiplets while maintaining the signal integrity required by the UCIe standard.

- Security and authentication mechanisms for UCIe chiplets: Security and authentication mechanisms ensure trusted operation in multi-vendor UCIe chiplet environments. These include secure boot processes, hardware root of trust implementations, and cryptographic protocols for chiplet-to-chiplet communications. Authentication systems verify the identity and integrity of chiplets from different vendors, while encryption and access control mechanisms protect sensitive data as it traverses between chiplets, preventing unauthorized access or tampering in heterogeneous systems.

02 Multi-vendor interoperability protocols and standards

Specific protocols and standards have been developed to ensure interoperability between chiplets from different vendors. These include standardized interfaces, communication protocols, and testing methodologies that allow chiplets from various manufacturers to work together seamlessly. The standardization efforts focus on defining common electrical and physical specifications, signal integrity requirements, and power management techniques to ensure reliable operation across different vendor implementations.Expand Specific Solutions03 Testing and validation methodologies for UCIe compliance

Comprehensive testing and validation methodologies have been developed to verify compliance with the UCIe standard and ensure interoperability between chiplets from different vendors. These methodologies include signal integrity testing, protocol compliance verification, and interoperability testing under various operating conditions. Automated test equipment and specialized test fixtures are used to validate the electrical and functional characteristics of UCIe implementations, ensuring reliable operation in multi-vendor environments.Expand Specific Solutions04 Power management and thermal considerations in UCIe implementations

Effective power management and thermal control are critical aspects of UCIe implementations, particularly in multi-vendor scenarios. Various techniques have been developed to optimize power consumption, manage heat dissipation, and ensure reliable operation across different thermal conditions. These include dynamic voltage and frequency scaling, power state management, and thermal monitoring systems that can adapt to changing workloads and environmental conditions, ensuring consistent performance and reliability in heterogeneous integrated systems.Expand Specific Solutions05 Security and authentication mechanisms for multi-vendor chiplets

Security and authentication mechanisms have been developed to protect data and ensure trusted communication between chiplets from different vendors. These mechanisms include secure boot processes, hardware-based authentication, encryption of data in transit, and access control systems. By implementing these security features, UCIe-based systems can maintain data integrity and confidentiality while preventing unauthorized access or tampering, which is particularly important in multi-vendor environments where trust boundaries may exist between different components.Expand Specific Solutions

Key Industry Players in Chiplet Ecosystem

The UCIe Chiplet Interconnect Multi-Vendor Interoperability Standards market is currently in its growth phase, with an expanding ecosystem of major players driving adoption. The market is projected to reach significant scale as chiplet technology becomes essential for advanced computing systems. Leading semiconductor companies including Intel, AMD (formerly ATI), Qualcomm, Samsung, and SK Hynix are actively developing UCIe-compatible solutions, with Intel being a primary pioneer. Chinese entities like ZTE and various research institutions are also making notable contributions. The technology has reached moderate maturity with established specifications, but full interoperability remains under development. Major technology companies such as Apple are exploring implementation, while automotive players like Mercedes-Benz represent emerging application sectors, indicating the standard's potential for cross-industry adoption.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed a comprehensive UCIe implementation strategy focused on mobile and edge computing applications. Their approach integrates UCIe with their existing Snapdragon platforms, enabling heterogeneous integration of specialized accelerators, modems, and processors. Qualcomm's UCIe implementation emphasizes power efficiency with adaptive power states that can scale interconnect performance based on workload demands. Their solution includes specialized PHY designs optimized for mobile form factors that maintain signal integrity while minimizing power consumption. Qualcomm has demonstrated UCIe links operating at up to 16 GT/s while consuming less than 1 pJ/bit, representing significant efficiency improvements over traditional interconnects. Their implementation includes built-in security features for die-to-die communication, including authentication mechanisms and encrypted channels to protect data moving between chiplets from different vendors.

Strengths: Exceptional power efficiency optimized for mobile applications; strong integration with existing Snapdragon ecosystem; advanced security features for chiplet authentication. Weaknesses: Less public information about implementation details compared to other UCIe members; potentially more focused on internal use than creating an open ecosystem.

Intel Corp.

Technical Solution: Intel is a founding member and key driver of the UCIe (Universal Chiplet Interconnect Express) standard. Their technology approach centers on an open die-to-die interconnect standard that enables mixing and matching of chiplets from different vendors. Intel's implementation leverages their EMIB (Embedded Multi-die Interconnect Bridge) and Foveros packaging technologies as complementary to UCIe. Their solution provides both standard and advanced physical layer options with two distinct protocols: a streaming protocol for memory access and a PCIe-based protocol for general-purpose communication. Intel has demonstrated UCIe implementations achieving up to 16 GT/s data rates in the standard version, with advanced implementations targeting 24-32 GT/s. Their approach emphasizes a "chiplet marketplace" ecosystem where silicon IP from different vendors can be integrated using standardized interfaces, allowing for more customized and cost-effective system designs.

Strengths: Strong industry leadership position as UCIe consortium founder; mature packaging technologies (EMIB, Foveros) that complement UCIe; extensive IP portfolio. Weaknesses: Potential competitive concerns from other semiconductor companies may limit adoption; implementation complexity for smaller players wanting to integrate with Intel's ecosystem.

Core Patents and Technical Specifications for UCIe

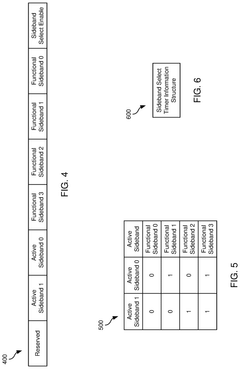

Mechanism To Improve The Reliability Of Sideband In Chiplets

PatentPendingUS20250086136A1

Innovation

- The method involves transitioning the UCIe link from an active state to a reset state and then initializing a different functional sideband, allowing for runtime configuration of sidebands and aggregation of multiple sidebands to enhance communication reliability and throughput.

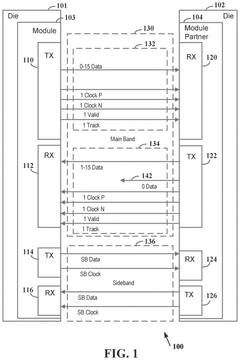

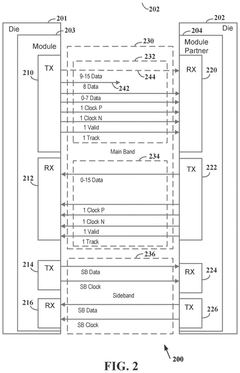

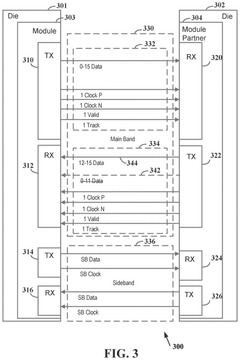

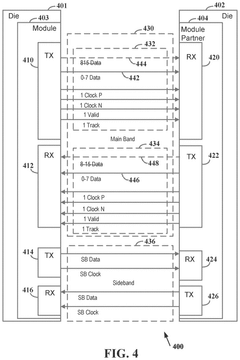

Variable link width in two directions for main band chip module connection

PatentPendingUS20240354279A1

Innovation

- Implementing a method to establish a die-to-die connection with a variable link width, allowing for independent configuration of transmit and receive data lanes through a sideband communication, enabling operation with different numbers of active data lanes in each direction to optimize power usage and data rates, and supporting fault tolerance by excluding faulty lines.

Interoperability Testing and Validation Methodologies

Interoperability testing for UCIe (Universal Chiplet Interconnect Express) requires comprehensive methodologies to ensure seamless integration between chiplets from different vendors. The validation process begins with protocol compliance testing, which verifies that each chiplet implementation adheres to the UCIe specification. This includes validating physical layer parameters, link training sequences, and protocol handshakes across various operating conditions.

Signal integrity testing forms a critical component of the validation methodology, involving measurements of eye diagrams, jitter, and crosstalk at the die-to-die interfaces. These tests must be performed across multiple process, voltage, and temperature (PVT) corners to ensure robust operation in real-world deployment scenarios. Advanced test equipment including high-speed oscilloscopes and bit error rate testers (BERTs) are essential for capturing the sub-nanosecond timing requirements of UCIe interfaces.

Interoperability validation matrices must be established to systematically test all possible combinations of chiplets from different vendors. These matrices track compatibility across various protocol layers, from physical interconnect to transaction layer protocols. The industry is moving toward standardized test chips and reference designs that serve as known-good implementations for validating third-party chiplets against the UCIe specification.

Power and thermal testing methodologies are equally important, as the dense integration of chiplets creates unique thermal challenges. Validation must include power state transitions, thermal throttling responses, and power management protocol compliance across vendor boundaries. This requires specialized test equipment capable of precise power measurement at the package level.

Automated test frameworks are emerging as essential tools for UCIe validation, enabling regression testing across firmware updates and silicon revisions. These frameworks typically incorporate both functional tests and stress tests designed to exercise corner cases in the specification. The UCIe consortium is working to standardize test vectors and compliance test suites similar to those established for PCIe and other mature interconnect standards.

System-level validation extends beyond chiplet-to-chiplet testing to include end-to-end application workloads. This methodology validates that the theoretical bandwidth and latency advantages of chiplet architectures translate to real-world performance improvements. Benchmarks specifically designed to stress multi-vendor chiplet interfaces are being developed by industry consortia to provide standardized performance metrics.

Signal integrity testing forms a critical component of the validation methodology, involving measurements of eye diagrams, jitter, and crosstalk at the die-to-die interfaces. These tests must be performed across multiple process, voltage, and temperature (PVT) corners to ensure robust operation in real-world deployment scenarios. Advanced test equipment including high-speed oscilloscopes and bit error rate testers (BERTs) are essential for capturing the sub-nanosecond timing requirements of UCIe interfaces.

Interoperability validation matrices must be established to systematically test all possible combinations of chiplets from different vendors. These matrices track compatibility across various protocol layers, from physical interconnect to transaction layer protocols. The industry is moving toward standardized test chips and reference designs that serve as known-good implementations for validating third-party chiplets against the UCIe specification.

Power and thermal testing methodologies are equally important, as the dense integration of chiplets creates unique thermal challenges. Validation must include power state transitions, thermal throttling responses, and power management protocol compliance across vendor boundaries. This requires specialized test equipment capable of precise power measurement at the package level.

Automated test frameworks are emerging as essential tools for UCIe validation, enabling regression testing across firmware updates and silicon revisions. These frameworks typically incorporate both functional tests and stress tests designed to exercise corner cases in the specification. The UCIe consortium is working to standardize test vectors and compliance test suites similar to those established for PCIe and other mature interconnect standards.

System-level validation extends beyond chiplet-to-chiplet testing to include end-to-end application workloads. This methodology validates that the theoretical bandwidth and latency advantages of chiplet architectures translate to real-world performance improvements. Benchmarks specifically designed to stress multi-vendor chiplet interfaces are being developed by industry consortia to provide standardized performance metrics.

Industry Consortium and Standardization Efforts

The UCIe (Universal Chiplet Interconnect Express) consortium represents one of the most significant industry collaborations in recent semiconductor history. Founded in March 2022, this alliance brings together semiconductor giants including Intel, AMD, Arm, TSMC, Samsung, and Qualcomm, with the explicit goal of establishing an open chiplet ecosystem. The consortium's primary mission is to develop and maintain interoperability standards that enable chiplets from different vendors to seamlessly communicate within the same package.

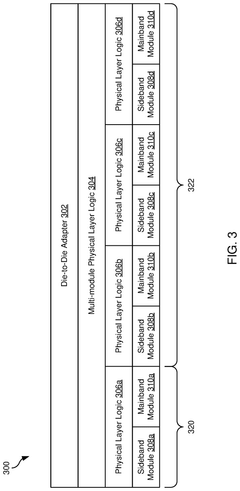

The standardization efforts of the UCIe consortium focus on three critical layers of the interconnect stack: the physical layer, the die-to-die adapter layer, and the protocol layer. This comprehensive approach ensures that chiplets can interact regardless of their manufacturing origin, creating unprecedented flexibility in system design. The consortium has successfully published the UCIe 1.0 specification, which defines the fundamental interconnect architecture supporting both standard and advanced packaging technologies.

Beyond the founding members, the UCIe consortium has expanded to include over 80 companies spanning the entire semiconductor value chain. This broad participation ensures that the standards reflect diverse industry needs and use cases. The consortium operates through technical working groups that address specific aspects of the specification, including electrical parameters, mechanical considerations, and protocol implementations.

The standardization process incorporates rigorous validation through interoperability testing events, where member companies verify that their chiplet implementations conform to the UCIe specifications. These testing frameworks are essential for building market confidence in multi-vendor chiplet solutions and accelerating industry adoption.

Complementary to UCIe, other industry groups are working on related standards that enhance the chiplet ecosystem. The Open Compute Project (OCP) has established initiatives focused on chiplet-based server architectures, while JEDEC has developed memory interface standards compatible with chiplet designs. The CHIPS Alliance, focusing on open-source hardware design, has also contributed tools and methodologies supporting chiplet integration.

The UCIe consortium maintains liaison relationships with these parallel standardization efforts to ensure alignment and prevent fragmentation of the chiplet ecosystem. This collaborative approach has been instrumental in establishing UCIe as the predominant standard for chiplet interconnects, with industry analysts projecting that UCIe-compliant chiplets will represent over 60% of the advanced packaging market by 2026.

The standardization efforts of the UCIe consortium focus on three critical layers of the interconnect stack: the physical layer, the die-to-die adapter layer, and the protocol layer. This comprehensive approach ensures that chiplets can interact regardless of their manufacturing origin, creating unprecedented flexibility in system design. The consortium has successfully published the UCIe 1.0 specification, which defines the fundamental interconnect architecture supporting both standard and advanced packaging technologies.

Beyond the founding members, the UCIe consortium has expanded to include over 80 companies spanning the entire semiconductor value chain. This broad participation ensures that the standards reflect diverse industry needs and use cases. The consortium operates through technical working groups that address specific aspects of the specification, including electrical parameters, mechanical considerations, and protocol implementations.

The standardization process incorporates rigorous validation through interoperability testing events, where member companies verify that their chiplet implementations conform to the UCIe specifications. These testing frameworks are essential for building market confidence in multi-vendor chiplet solutions and accelerating industry adoption.

Complementary to UCIe, other industry groups are working on related standards that enhance the chiplet ecosystem. The Open Compute Project (OCP) has established initiatives focused on chiplet-based server architectures, while JEDEC has developed memory interface standards compatible with chiplet designs. The CHIPS Alliance, focusing on open-source hardware design, has also contributed tools and methodologies supporting chiplet integration.

The UCIe consortium maintains liaison relationships with these parallel standardization efforts to ensure alignment and prevent fragmentation of the chiplet ecosystem. This collaborative approach has been instrumental in establishing UCIe as the predominant standard for chiplet interconnects, with industry analysts projecting that UCIe-compliant chiplets will represent over 60% of the advanced packaging market by 2026.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!