UCIe Chiplet Interconnect PHY Compliance And Testing Standards

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Evolution and Objectives

The Universal Chiplet Interconnect Express (UCIe) represents a significant evolution in semiconductor integration technology, emerging as a response to the increasing challenges of traditional monolithic chip scaling. The development of UCIe can be traced back to the fundamental limitations of Moore's Law, which has historically guided semiconductor advancement but has faced physical and economic constraints in recent years. As transistor density scaling became more difficult, the industry began exploring alternative approaches to continue performance improvements.

The chiplet paradigm emerged as a promising solution, allowing complex systems to be built from smaller, specialized silicon dies. Early chiplet implementations relied on proprietary interconnect technologies, creating fragmentation in the ecosystem and limiting interoperability. This fragmentation highlighted the need for standardization, setting the stage for UCIe's development.

In March 2022, the UCIe consortium was formally established with founding members including Intel, AMD, Arm, ASE, Google Cloud, Meta, Microsoft, Qualcomm, Samsung, and TSMC. This consortium represented an unprecedented collaboration among competitors, underscoring the industry-wide recognition of chiplet technology's importance. The initial UCIe 1.0 specification was released simultaneously, focusing on die-to-die interconnect standardization.

The primary objective of UCIe is to establish an open, industry-standard interconnect architecture that enables heterogeneous integration of chiplets within a package, regardless of vendor or process technology. This standardization aims to foster a more diverse and innovative chiplet ecosystem by ensuring interoperability between chiplets from different manufacturers.

Technical objectives of UCIe include defining standardized physical layer specifications, protocols, and testing methodologies to ensure reliable high-speed communication between chiplets. The standard addresses both electrical and optical interconnect technologies, with particular emphasis on power efficiency, signal integrity, and bandwidth density to meet the demands of next-generation computing applications.

UCIe also aims to support scalability across different market segments, from high-performance computing to mobile and edge devices. This requires flexibility in the specification to accommodate varying performance, power, and cost requirements while maintaining compatibility.

Looking forward, UCIe's evolution roadmap includes expanding beyond the initial focus on package-level integration to enable chiplet integration across multiple packages and potentially even across systems. The consortium is also working toward incorporating advanced features such as security mechanisms, power management capabilities, and support for emerging memory architectures to address the holistic needs of future computing systems.

The chiplet paradigm emerged as a promising solution, allowing complex systems to be built from smaller, specialized silicon dies. Early chiplet implementations relied on proprietary interconnect technologies, creating fragmentation in the ecosystem and limiting interoperability. This fragmentation highlighted the need for standardization, setting the stage for UCIe's development.

In March 2022, the UCIe consortium was formally established with founding members including Intel, AMD, Arm, ASE, Google Cloud, Meta, Microsoft, Qualcomm, Samsung, and TSMC. This consortium represented an unprecedented collaboration among competitors, underscoring the industry-wide recognition of chiplet technology's importance. The initial UCIe 1.0 specification was released simultaneously, focusing on die-to-die interconnect standardization.

The primary objective of UCIe is to establish an open, industry-standard interconnect architecture that enables heterogeneous integration of chiplets within a package, regardless of vendor or process technology. This standardization aims to foster a more diverse and innovative chiplet ecosystem by ensuring interoperability between chiplets from different manufacturers.

Technical objectives of UCIe include defining standardized physical layer specifications, protocols, and testing methodologies to ensure reliable high-speed communication between chiplets. The standard addresses both electrical and optical interconnect technologies, with particular emphasis on power efficiency, signal integrity, and bandwidth density to meet the demands of next-generation computing applications.

UCIe also aims to support scalability across different market segments, from high-performance computing to mobile and edge devices. This requires flexibility in the specification to accommodate varying performance, power, and cost requirements while maintaining compatibility.

Looking forward, UCIe's evolution roadmap includes expanding beyond the initial focus on package-level integration to enable chiplet integration across multiple packages and potentially even across systems. The consortium is also working toward incorporating advanced features such as security mechanisms, power management capabilities, and support for emerging memory architectures to address the holistic needs of future computing systems.

Market Demand Analysis for Chiplet-Based Architectures

The chiplet-based architecture market is experiencing unprecedented growth, driven by the semiconductor industry's shift away from traditional monolithic designs. This transition is primarily fueled by the physical limitations of Moore's Law and the escalating costs associated with advanced process nodes. Market research indicates that the global chiplet market is projected to grow at a compound annual growth rate of over 40% from 2023 to 2030, with the market value expected to reach tens of billions by mid-decade.

The demand for UCIe (Universal Chiplet Interconnect Express) compliance and testing standards stems from several critical market factors. First, heterogeneous integration has become essential as different components benefit from different process technologies. This approach allows memory, logic, analog, and RF components to be manufactured using their optimal process nodes, then integrated into a single package, significantly improving performance while reducing costs.

Data center operators and cloud service providers represent the largest market segment driving chiplet adoption. These entities face increasing pressure to improve computational density and energy efficiency while managing thermal constraints. Chiplet-based designs offer up to 30% better power efficiency compared to monolithic approaches at advanced nodes, making them particularly attractive for hyperscale deployments.

The automotive and edge computing sectors are emerging as secondary but rapidly growing markets for chiplet technology. As vehicles incorporate more advanced driver assistance systems and autonomous capabilities, the need for high-performance, reliable computing platforms that can be certified for automotive safety standards increases. UCIe standards provide the framework necessary for these mission-critical applications.

Consumer electronics manufacturers are also showing significant interest in chiplet architectures, particularly for high-performance mobile devices and next-generation gaming consoles. The ability to mix and match chiplets from different vendors while maintaining interoperability is viewed as a key advantage, potentially reducing time-to-market and enabling more customized solutions.

From a supply chain perspective, the standardization offered by UCIe addresses a critical market need for ecosystem development. Major semiconductor manufacturers, including Intel, AMD, TSMC, Samsung, and Arm, have joined the UCIe consortium, indicating strong industry alignment. This standardization is expected to create a more diverse and resilient supply chain, allowing smaller specialized firms to participate in the chiplet ecosystem by focusing on specific components rather than entire systems.

The testing and compliance market itself represents a significant opportunity, with specialized equipment manufacturers developing new tools specifically designed for chiplet interconnect validation. Industry analysts predict this segment could grow to hundreds of millions annually as chiplet adoption accelerates across multiple industries.

The demand for UCIe (Universal Chiplet Interconnect Express) compliance and testing standards stems from several critical market factors. First, heterogeneous integration has become essential as different components benefit from different process technologies. This approach allows memory, logic, analog, and RF components to be manufactured using their optimal process nodes, then integrated into a single package, significantly improving performance while reducing costs.

Data center operators and cloud service providers represent the largest market segment driving chiplet adoption. These entities face increasing pressure to improve computational density and energy efficiency while managing thermal constraints. Chiplet-based designs offer up to 30% better power efficiency compared to monolithic approaches at advanced nodes, making them particularly attractive for hyperscale deployments.

The automotive and edge computing sectors are emerging as secondary but rapidly growing markets for chiplet technology. As vehicles incorporate more advanced driver assistance systems and autonomous capabilities, the need for high-performance, reliable computing platforms that can be certified for automotive safety standards increases. UCIe standards provide the framework necessary for these mission-critical applications.

Consumer electronics manufacturers are also showing significant interest in chiplet architectures, particularly for high-performance mobile devices and next-generation gaming consoles. The ability to mix and match chiplets from different vendors while maintaining interoperability is viewed as a key advantage, potentially reducing time-to-market and enabling more customized solutions.

From a supply chain perspective, the standardization offered by UCIe addresses a critical market need for ecosystem development. Major semiconductor manufacturers, including Intel, AMD, TSMC, Samsung, and Arm, have joined the UCIe consortium, indicating strong industry alignment. This standardization is expected to create a more diverse and resilient supply chain, allowing smaller specialized firms to participate in the chiplet ecosystem by focusing on specific components rather than entire systems.

The testing and compliance market itself represents a significant opportunity, with specialized equipment manufacturers developing new tools specifically designed for chiplet interconnect validation. Industry analysts predict this segment could grow to hundreds of millions annually as chiplet adoption accelerates across multiple industries.

UCIe PHY Compliance Testing Landscape and Challenges

The UCIe PHY compliance testing landscape is characterized by a complex ecosystem of standards, methodologies, and challenges that must be navigated to ensure interoperability between chiplets from different vendors. Currently, the industry faces significant hurdles in establishing comprehensive testing frameworks that can adequately validate the high-speed die-to-die interconnects that UCIe enables.

Testing methodologies for UCIe PHY compliance must address multiple protocol layers and operating modes, including the Standard Die-to-Die (SD2D) interface that supports both advanced and standard packages. The testing landscape is further complicated by the need to validate both the Die-to-Die (D2D) and the Package-to-Package (P2P) implementations, each with distinct electrical characteristics and performance requirements.

A major challenge in UCIe PHY compliance testing is the ultra-high-speed signal integrity verification, with data rates reaching up to 16 GT/s in the current specification and roadmaps pointing to even higher speeds. Traditional test equipment and methodologies struggle to accurately measure and characterize signals at these frequencies, particularly when dealing with the extremely short channel lengths typical in chiplet implementations.

The industry also faces challenges related to test access. Unlike traditional chip testing where probe points are readily available, chiplet interconnects are often buried within packages, making direct probing difficult or impossible. This necessitates the development of specialized test structures, on-die measurement capabilities, and novel approaches to inferring compliance from limited observable parameters.

Power and thermal considerations present another significant challenge. The dense integration of chiplets can create hotspots and power distribution issues that affect signal integrity. Compliance testing must therefore account for these thermal effects and validate performance across a range of operating conditions.

Interoperability testing between chiplets from different vendors represents perhaps the most critical challenge. The UCIe standard aims to enable a mix-and-match ecosystem, but ensuring that chiplets from vendor A work seamlessly with those from vendor B requires robust compliance testing methodologies that can verify adherence to the standard across all implementation variations.

The testing landscape is further complicated by the rapid evolution of the UCIe standard itself. As the specification matures and adds new features, testing methodologies must evolve in parallel, creating a moving target for test equipment manufacturers and validation engineers.

Testing methodologies for UCIe PHY compliance must address multiple protocol layers and operating modes, including the Standard Die-to-Die (SD2D) interface that supports both advanced and standard packages. The testing landscape is further complicated by the need to validate both the Die-to-Die (D2D) and the Package-to-Package (P2P) implementations, each with distinct electrical characteristics and performance requirements.

A major challenge in UCIe PHY compliance testing is the ultra-high-speed signal integrity verification, with data rates reaching up to 16 GT/s in the current specification and roadmaps pointing to even higher speeds. Traditional test equipment and methodologies struggle to accurately measure and characterize signals at these frequencies, particularly when dealing with the extremely short channel lengths typical in chiplet implementations.

The industry also faces challenges related to test access. Unlike traditional chip testing where probe points are readily available, chiplet interconnects are often buried within packages, making direct probing difficult or impossible. This necessitates the development of specialized test structures, on-die measurement capabilities, and novel approaches to inferring compliance from limited observable parameters.

Power and thermal considerations present another significant challenge. The dense integration of chiplets can create hotspots and power distribution issues that affect signal integrity. Compliance testing must therefore account for these thermal effects and validate performance across a range of operating conditions.

Interoperability testing between chiplets from different vendors represents perhaps the most critical challenge. The UCIe standard aims to enable a mix-and-match ecosystem, but ensuring that chiplets from vendor A work seamlessly with those from vendor B requires robust compliance testing methodologies that can verify adherence to the standard across all implementation variations.

The testing landscape is further complicated by the rapid evolution of the UCIe standard itself. As the specification matures and adds new features, testing methodologies must evolve in parallel, creating a moving target for test equipment manufacturers and validation engineers.

Current UCIe PHY Compliance Testing Methodologies

01 UCIe PHY Layer Testing and Compliance Methodologies

The Universal Chiplet Interconnect Express (UCIe) standard requires specific testing methodologies for the physical (PHY) layer to ensure compliance. These methodologies include signal integrity testing, electrical parameter verification, and interoperability testing between different chiplet components. Testing procedures typically involve specialized equipment to measure parameters such as jitter, eye diagrams, and signal quality at the physical interconnect level to ensure reliable high-speed data transmission between chiplets.- UCIe PHY Layer Testing and Compliance Methodologies: Testing methodologies for Universal Chiplet Interconnect Express (UCIe) PHY layer compliance involve specific procedures to verify signal integrity, timing parameters, and electrical characteristics. These methodologies include test fixtures, automated testing sequences, and measurement techniques designed to validate that chiplet interconnects meet the UCIe specification requirements. Compliance testing ensures interoperability between different chiplets from various manufacturers within a package.

- Die-to-Die Interface Validation Systems: Systems for validating die-to-die interfaces in chiplet designs include specialized hardware and software tools that verify the proper functioning of UCIe interconnects. These validation systems can simulate various operating conditions, detect signal integrity issues, and measure performance metrics such as bandwidth, latency, and power consumption. They provide comprehensive testing capabilities for ensuring reliable communication between chiplets in multi-die packages.

- Automated Compliance Testing Frameworks: Automated frameworks for UCIe compliance testing streamline the verification process through predefined test sequences, automated measurements, and result analysis. These frameworks include software tools that control test equipment, apply test patterns, collect measurement data, and generate compliance reports. By automating the testing process, these frameworks reduce testing time, minimize human error, and ensure consistent application of the UCIe specification requirements.

- Chiplet Interconnect Performance Verification: Performance verification for chiplet interconnects involves measuring and analyzing key performance indicators such as data transfer rates, signal quality, power efficiency, and error rates. Testing methods include stress testing under various operating conditions, margin testing to determine operational limits, and long-term reliability testing. These verification procedures ensure that UCIe implementations meet performance requirements while maintaining compatibility with the standard.

- UCIe Compliance Certification Processes: Certification processes for UCIe compliance involve formal procedures for validating that chiplet interconnect implementations conform to the UCIe specification. These processes include submission of test results, review by certification authorities, and issuance of compliance certificates. Certification ensures that products from different vendors can interoperate seamlessly when integrated into multi-chiplet systems, fostering a robust ecosystem of compatible chiplet products.

02 Chiplet Interconnect Performance Validation Systems

Systems and methods for validating the performance of chiplet interconnects involve comprehensive testing frameworks that evaluate both functional and electrical characteristics. These validation systems typically include automated test equipment capable of measuring high-speed signal integrity, power delivery, thermal performance, and protocol compliance. The validation process ensures that chiplets from different vendors can seamlessly communicate when integrated into a multi-die package, which is essential for the modular chiplet ecosystem to function properly.Expand Specific Solutions03 UCIe Standard Compliance Certification Processes

The certification processes for UCIe standard compliance involve formal verification procedures that chiplet manufacturers must follow to ensure their products meet the established specifications. These processes typically include submission of test results to certification authorities, verification of design documentation, and potentially third-party validation testing. The certification ensures that chiplets adhering to the UCIe standard will function correctly when integrated with other compliant components, fostering an open ecosystem for chiplet-based designs.Expand Specific Solutions04 Advanced Testing Equipment for Chiplet Interconnects

Specialized testing equipment designed specifically for chiplet interconnect validation includes high-precision signal analyzers, protocol analyzers, and automated test platforms. These tools are capable of measuring the ultra-high-speed signals used in modern chiplet interfaces, detecting subtle signal integrity issues, and verifying compliance with the UCIe specification. The equipment often incorporates machine learning algorithms to identify potential issues and optimize test coverage while minimizing test time.Expand Specific Solutions05 Die-to-Die Interface Testing Methodologies

Testing methodologies specific to die-to-die interfaces in chiplet designs focus on verifying the reliability of connections between different silicon dies within a package. These methodologies include boundary scan testing, loopback testing, and built-in self-test (BIST) mechanisms that can verify interconnect functionality at various operating conditions. The testing approaches must account for the unique challenges of multi-die packages, including thermal gradients, mechanical stress, and power distribution variations that can affect signal integrity across the die-to-die interfaces.Expand Specific Solutions

Key Industry Players in UCIe Ecosystem

The UCIe Chiplet Interconnect PHY Compliance and Testing Standards market is currently in an early growth phase, characterized by increasing adoption as the industry transitions toward chiplet-based architectures. The market size is expanding rapidly, projected to reach significant value as major semiconductor players integrate chiplet technologies into their product roadmaps. From a technical maturity perspective, the ecosystem is still evolving, with key players like Intel, AMD (formerly ATI), Qualcomm, and Samsung leading standardization efforts. Companies including SK Hynix, MediaTek, and Cadence Design Systems are actively developing compliant solutions, while testing specialists such as Keysight Technologies are creating validation frameworks. Chinese entities including Inspur, Alibaba, and various research institutions are increasingly participating in this emerging standard, indicating its growing global importance for next-generation semiconductor design.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed a specialized UCIe PHY compliance and testing framework focused on mobile and edge computing applications. Their approach emphasizes power efficiency while maintaining high bandwidth for chiplet interconnects. Qualcomm's testing methodology includes comprehensive signal integrity analysis using advanced time and frequency domain measurements to validate UCIe PHY performance across different power states and operating conditions. Their compliance tools feature automated test sequences that verify both electrical and timing parameters according to the UCIe specification. Qualcomm has implemented specific test modes in their chiplet designs that facilitate in-system testing and validation, including built-in self-test (BIST) capabilities for production environments[2]. Their testing infrastructure supports data rates up to 32 GT/s with particular attention to power consumption metrics during various transfer modes. Qualcomm also employs specialized thermal testing to ensure reliable operation under the thermal constraints typical in mobile devices, with validation across multiple process nodes to ensure broad compatibility.

Strengths: Industry-leading expertise in low-power design and testing methodologies; comprehensive mobile-optimized validation approach; strong focus on power efficiency metrics during compliance testing. Weaknesses: Testing infrastructure may be more specialized toward mobile applications; less public documentation about their UCIe implementation compared to some competitors; potentially higher integration costs for partners outside their ecosystem.

Intel Corp.

Technical Solution: Intel is a founding member and leading contributor to the UCIe (Universal Chiplet Interconnect Express) standard. Their approach to UCIe PHY compliance and testing involves comprehensive validation methodologies across multiple layers. Intel has developed specialized test equipment and procedures for validating die-to-die (D2D) interconnects at both the physical and protocol layers. Their testing framework includes automated compliance tools that verify signal integrity, timing parameters, and power characteristics across different operating conditions. Intel's PHY implementation supports both standard and advanced modes with data rates up to 32 GT/s, and their compliance testing covers both package-level and die-level verification[1][3]. Intel has also created reference designs and validation platforms specifically for chiplet integration testing, allowing partners to verify interoperability before production. Their testing methodology includes stress testing under various environmental conditions to ensure reliability in real-world deployments.

Strengths: Industry-leading expertise in chiplet technology with extensive validation infrastructure and tools; comprehensive testing methodology covering all aspects of the UCIe standard; strong ecosystem partnerships enabling broad interoperability testing. Weaknesses: Proprietary elements in their testing approach may limit full transparency; higher implementation costs compared to some competitors; testing requirements may be overly stringent for some applications.

Critical Patents and Innovations in UCIe PHY Testing

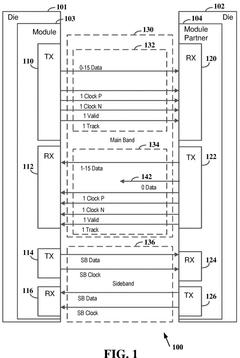

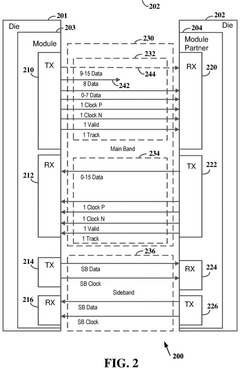

Variable link width in two directions for main band chip module connection

PatentPendingUS20240354279A1

Innovation

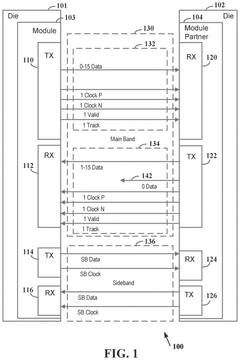

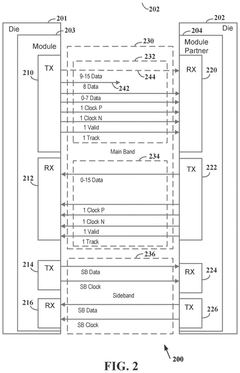

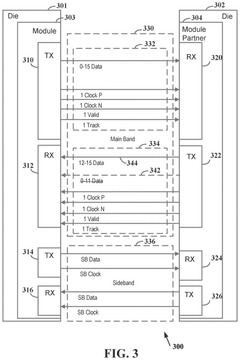

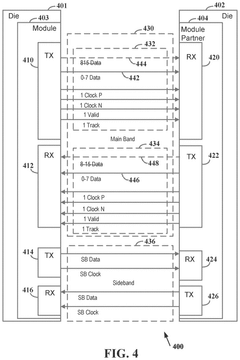

- Implementing a method to establish a die-to-die connection with a variable link width, allowing for independent configuration of transmit and receive data lanes through a sideband communication, enabling operation with different numbers of active data lanes in each direction to optimize power usage and data rates, and supporting fault tolerance by excluding faulty lines.

Variable link width in two directions for main band chip module connection

PatentWO2024226177A1

Innovation

- Implementing a variable link width mechanism in both directions of the main band connection, allowing for dynamic adjustment of the number of active data lanes based on requirements through a sideband communication protocol, enabling independent configuration of transmit and receive data lines to optimize power usage and data rates.

Interoperability Considerations for Multi-Vendor Chiplets

Interoperability across chiplets from different vendors represents one of the most critical challenges in the UCIe ecosystem. The Universal Chiplet Interconnect Express (UCIe) standard aims to establish a unified framework for chiplet-to-chiplet communication, but achieving true multi-vendor interoperability requires addressing several complex technical considerations beyond basic compliance.

Physical layer compatibility remains the foundation of successful chiplet integration. When combining chiplets from different manufacturers, variations in silicon processes, manufacturing tolerances, and design implementations can create signal integrity challenges at the PHY layer. These variations may manifest as impedance mismatches, timing skews, or power delivery inconsistencies that compromise the reliability of high-speed data transfers across the interconnect.

Protocol-level interoperability presents another dimension of complexity. While UCIe defines standard protocols, vendor-specific extensions or optimizations may introduce compatibility issues. Different interpretations of the specification or implementation choices can lead to subtle behavioral differences that only emerge during system integration. This necessitates comprehensive validation methodologies that verify protocol compatibility across the entire communication stack.

Power management coordination between multi-vendor chiplets introduces additional challenges. Different chiplets may implement varying power states, transition latencies, and thermal characteristics. Without proper coordination mechanisms, power state transitions could lead to communication failures or performance degradation. The UCIe standard must therefore include robust power management protocols that ensure synchronized operation across heterogeneous chiplet configurations.

Testing methodologies for multi-vendor scenarios require special consideration. Traditional single-vendor testing approaches may not adequately capture the complexities of cross-vendor integration. Comprehensive interoperability testing must include corner cases that verify behavior under various operating conditions, including power fluctuations, temperature variations, and recovery from error states.

Security and trust boundaries become particularly important in multi-vendor environments. Different chiplets may implement varying levels of security features, and establishing trusted communication channels between chiplets from different vendors requires standardized authentication and encryption mechanisms. The industry must develop clear guidelines for security interoperability to prevent potential vulnerabilities at chiplet interfaces.

Configuration and initialization sequences represent another critical aspect of multi-vendor interoperability. Standardized discovery mechanisms and capability negotiation protocols are essential to ensure that chiplets can properly identify and adapt to the capabilities of their communication partners, enabling optimal performance while maintaining compatibility.

Physical layer compatibility remains the foundation of successful chiplet integration. When combining chiplets from different manufacturers, variations in silicon processes, manufacturing tolerances, and design implementations can create signal integrity challenges at the PHY layer. These variations may manifest as impedance mismatches, timing skews, or power delivery inconsistencies that compromise the reliability of high-speed data transfers across the interconnect.

Protocol-level interoperability presents another dimension of complexity. While UCIe defines standard protocols, vendor-specific extensions or optimizations may introduce compatibility issues. Different interpretations of the specification or implementation choices can lead to subtle behavioral differences that only emerge during system integration. This necessitates comprehensive validation methodologies that verify protocol compatibility across the entire communication stack.

Power management coordination between multi-vendor chiplets introduces additional challenges. Different chiplets may implement varying power states, transition latencies, and thermal characteristics. Without proper coordination mechanisms, power state transitions could lead to communication failures or performance degradation. The UCIe standard must therefore include robust power management protocols that ensure synchronized operation across heterogeneous chiplet configurations.

Testing methodologies for multi-vendor scenarios require special consideration. Traditional single-vendor testing approaches may not adequately capture the complexities of cross-vendor integration. Comprehensive interoperability testing must include corner cases that verify behavior under various operating conditions, including power fluctuations, temperature variations, and recovery from error states.

Security and trust boundaries become particularly important in multi-vendor environments. Different chiplets may implement varying levels of security features, and establishing trusted communication channels between chiplets from different vendors requires standardized authentication and encryption mechanisms. The industry must develop clear guidelines for security interoperability to prevent potential vulnerabilities at chiplet interfaces.

Configuration and initialization sequences represent another critical aspect of multi-vendor interoperability. Standardized discovery mechanisms and capability negotiation protocols are essential to ensure that chiplets can properly identify and adapt to the capabilities of their communication partners, enabling optimal performance while maintaining compatibility.

Standardization Bodies and Governance Framework

The Universal Chiplet Interconnect Express (UCIe) standardization is governed by a consortium of industry leaders who collectively shape the development, implementation, and evolution of this critical chiplet interconnect technology. The UCIe Consortium, established in 2022, serves as the primary standardization body responsible for developing and maintaining the UCIe specifications, including the PHY compliance and testing standards.

The consortium operates through a structured governance framework with multiple tiers of membership. Promoter Members, including founding organizations like Intel, AMD, Arm, TSMC, and Samsung, hold board positions and possess significant voting rights on technical decisions and specification approvals. Contributor Members participate in technical working groups but have limited voting privileges, while Adopter Members gain access to specifications for implementation without direct involvement in the standard development process.

Technical Working Groups (TWGs) form the backbone of the UCIe standardization process. The PHY TWG specifically focuses on physical layer specifications, compliance criteria, and testing methodologies. This group comprises industry experts who collaborate to define electrical characteristics, signal integrity requirements, and interoperability parameters essential for reliable chiplet-to-chiplet communication.

The Compliance and Interoperability Working Group plays a crucial role in developing comprehensive test specifications, validation procedures, and certification processes. This group ensures that UCIe implementations across different vendors maintain consistent performance and compatibility, which is vital for the chiplet ecosystem's success.

The UCIe Consortium maintains liaison relationships with other relevant standards bodies, including IEEE, JEDEC, and OCP, to ensure alignment and prevent fragmentation in the broader interconnect standards landscape. These collaborative relationships facilitate the integration of UCIe with complementary technologies and standards.

The governance process for updating PHY compliance standards follows a structured path: technical proposals are submitted to relevant working groups, undergo technical review and refinement, proceed through draft specification development, face public review periods for broader industry feedback, and ultimately require formal approval by the Board of Directors before publication as official standards.

The consortium also oversees the certification program for UCIe PHY compliance, authorizing testing laboratories and defining the certification mark usage. This certification ecosystem ensures that products claiming UCIe compatibility have undergone rigorous testing against the established standards, providing confidence to system integrators and end users.

The consortium operates through a structured governance framework with multiple tiers of membership. Promoter Members, including founding organizations like Intel, AMD, Arm, TSMC, and Samsung, hold board positions and possess significant voting rights on technical decisions and specification approvals. Contributor Members participate in technical working groups but have limited voting privileges, while Adopter Members gain access to specifications for implementation without direct involvement in the standard development process.

Technical Working Groups (TWGs) form the backbone of the UCIe standardization process. The PHY TWG specifically focuses on physical layer specifications, compliance criteria, and testing methodologies. This group comprises industry experts who collaborate to define electrical characteristics, signal integrity requirements, and interoperability parameters essential for reliable chiplet-to-chiplet communication.

The Compliance and Interoperability Working Group plays a crucial role in developing comprehensive test specifications, validation procedures, and certification processes. This group ensures that UCIe implementations across different vendors maintain consistent performance and compatibility, which is vital for the chiplet ecosystem's success.

The UCIe Consortium maintains liaison relationships with other relevant standards bodies, including IEEE, JEDEC, and OCP, to ensure alignment and prevent fragmentation in the broader interconnect standards landscape. These collaborative relationships facilitate the integration of UCIe with complementary technologies and standards.

The governance process for updating PHY compliance standards follows a structured path: technical proposals are submitted to relevant working groups, undergo technical review and refinement, proceed through draft specification development, face public review periods for broader industry feedback, and ultimately require formal approval by the Board of Directors before publication as official standards.

The consortium also oversees the certification program for UCIe PHY compliance, authorizing testing laboratories and defining the certification mark usage. This certification ecosystem ensures that products claiming UCIe compatibility have undergone rigorous testing against the established standards, providing confidence to system integrators and end users.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!