UCIe Chiplet Interconnect Interposer Material Selection Criteria

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect Background and Objectives

The Universal Chiplet Interconnect Express (UCIe) represents a significant advancement in semiconductor integration technology, emerging as a response to the slowing of Moore's Law and the increasing challenges in traditional monolithic chip scaling. Developed through industry collaboration, UCIe aims to establish an open standard for die-to-die interconnection, enabling heterogeneous integration of chiplets from different vendors on a common substrate or interposer.

The evolution of chiplet technology can be traced back to the early 2010s when semiconductor manufacturers began exploring multi-chip module approaches to overcome the physical limitations of silicon scaling. The industry recognized that breaking down complex systems into smaller, specialized dies could offer advantages in yield, performance, and cost. This trend accelerated with AMD's introduction of their Infinity Fabric in 2017, followed by Intel's EMIB and TSMC's CoWoS technologies, all representing proprietary approaches to chiplet integration.

UCIe represents the next logical step in this evolution, moving from proprietary solutions to an open standard that promotes interoperability across the semiconductor ecosystem. Formally announced in March 2022 by a consortium including Intel, AMD, Arm, TSMC, Samsung, and other industry leaders, UCIe 1.0 specification established the foundation for a unified approach to chiplet interconnection.

The primary technical objectives of UCIe include establishing standardized physical and protocol layers for die-to-die communication, enabling high-bandwidth, low-latency connections between chiplets while maintaining energy efficiency. The standard aims to support both package-level integration (standard and advanced packaging) and silicon interposer-based integration, with data rates ranging from 16 GT/s to 32 GT/s in its initial specification.

A critical aspect of UCIe implementation is the selection of appropriate interposer materials, which directly impacts electrical performance, thermal management, reliability, and manufacturing costs. Traditional silicon interposers offer excellent dimensional stability and thermal matching with chiplets but present challenges in terms of cost and size limitations. Alternative materials such as glass, organic substrates, and ceramic composites are being explored to optimize the performance-cost balance.

The long-term vision for UCIe extends beyond merely establishing technical specifications. It aims to foster a new semiconductor ecosystem where chiplets become standardized building blocks that can be mixed and matched across vendors, potentially revolutionizing how integrated circuits are designed, manufactured, and brought to market. This "chiplet marketplace" concept could democratize access to advanced semiconductor technology, allowing smaller players to innovate without the massive capital investments traditionally required for cutting-edge chip development.

The evolution of chiplet technology can be traced back to the early 2010s when semiconductor manufacturers began exploring multi-chip module approaches to overcome the physical limitations of silicon scaling. The industry recognized that breaking down complex systems into smaller, specialized dies could offer advantages in yield, performance, and cost. This trend accelerated with AMD's introduction of their Infinity Fabric in 2017, followed by Intel's EMIB and TSMC's CoWoS technologies, all representing proprietary approaches to chiplet integration.

UCIe represents the next logical step in this evolution, moving from proprietary solutions to an open standard that promotes interoperability across the semiconductor ecosystem. Formally announced in March 2022 by a consortium including Intel, AMD, Arm, TSMC, Samsung, and other industry leaders, UCIe 1.0 specification established the foundation for a unified approach to chiplet interconnection.

The primary technical objectives of UCIe include establishing standardized physical and protocol layers for die-to-die communication, enabling high-bandwidth, low-latency connections between chiplets while maintaining energy efficiency. The standard aims to support both package-level integration (standard and advanced packaging) and silicon interposer-based integration, with data rates ranging from 16 GT/s to 32 GT/s in its initial specification.

A critical aspect of UCIe implementation is the selection of appropriate interposer materials, which directly impacts electrical performance, thermal management, reliability, and manufacturing costs. Traditional silicon interposers offer excellent dimensional stability and thermal matching with chiplets but present challenges in terms of cost and size limitations. Alternative materials such as glass, organic substrates, and ceramic composites are being explored to optimize the performance-cost balance.

The long-term vision for UCIe extends beyond merely establishing technical specifications. It aims to foster a new semiconductor ecosystem where chiplets become standardized building blocks that can be mixed and matched across vendors, potentially revolutionizing how integrated circuits are designed, manufactured, and brought to market. This "chiplet marketplace" concept could democratize access to advanced semiconductor technology, allowing smaller players to innovate without the massive capital investments traditionally required for cutting-edge chip development.

Market Demand Analysis for Advanced Chiplet Interconnect Solutions

The global chiplet market is experiencing unprecedented growth, driven by the increasing demand for high-performance computing solutions across various industries. As traditional monolithic chip designs reach their physical and economic limits, chiplet-based architectures have emerged as a compelling alternative, with the market projected to reach $57 billion by 2035, growing at a CAGR of 38% from 2023.

Data centers and cloud service providers represent the largest market segment for advanced chiplet interconnect solutions, accounting for approximately 45% of the current demand. These entities require ever-increasing computational power while facing constraints in power consumption and thermal management. UCIe (Universal Chiplet Interconnect Express) technology addresses these challenges by enabling modular chip designs with high-bandwidth, low-latency connections between chiplets.

The artificial intelligence and machine learning sector follows closely, constituting about 30% of market demand. As AI models grow exponentially in size and complexity, the need for specialized, heterogeneous computing architectures becomes critical. Chiplet-based designs allow for the integration of diverse processing elements (CPUs, GPUs, TPUs, memory) optimized for specific AI workloads, driving significant performance improvements while managing power constraints.

Telecommunications equipment manufacturers, particularly those involved in 5G and future 6G infrastructure development, represent approximately 15% of the market. These applications demand high-speed data processing capabilities with strict power efficiency requirements, making chiplet-based designs increasingly attractive.

Consumer electronics, automotive, and industrial automation collectively account for the remaining 10% of market demand, though these segments are expected to grow substantially as chiplet technology matures and becomes more cost-effective for mass-market applications.

Geographically, North America leads the market with 42% share, followed by Asia-Pacific at 38%, Europe at 15%, and other regions at 5%. China's aggressive investments in semiconductor self-sufficiency are expected to significantly alter this distribution within the next five years.

Market research indicates that customers prioritize several key factors when evaluating chiplet interconnect solutions: bandwidth density (cited by 87% of surveyed companies), power efficiency (82%), thermal performance (78%), manufacturing scalability (75%), and standardization/interoperability (73%). The material selection for interposers directly impacts all these factors, making it a critical decision point in chiplet design.

Industry analysts forecast that the demand for advanced materials supporting chiplet interconnect technologies will grow at 45% CAGR through 2030, outpacing the overall chiplet market growth and highlighting the strategic importance of interposer material selection in meeting evolving market requirements.

Data centers and cloud service providers represent the largest market segment for advanced chiplet interconnect solutions, accounting for approximately 45% of the current demand. These entities require ever-increasing computational power while facing constraints in power consumption and thermal management. UCIe (Universal Chiplet Interconnect Express) technology addresses these challenges by enabling modular chip designs with high-bandwidth, low-latency connections between chiplets.

The artificial intelligence and machine learning sector follows closely, constituting about 30% of market demand. As AI models grow exponentially in size and complexity, the need for specialized, heterogeneous computing architectures becomes critical. Chiplet-based designs allow for the integration of diverse processing elements (CPUs, GPUs, TPUs, memory) optimized for specific AI workloads, driving significant performance improvements while managing power constraints.

Telecommunications equipment manufacturers, particularly those involved in 5G and future 6G infrastructure development, represent approximately 15% of the market. These applications demand high-speed data processing capabilities with strict power efficiency requirements, making chiplet-based designs increasingly attractive.

Consumer electronics, automotive, and industrial automation collectively account for the remaining 10% of market demand, though these segments are expected to grow substantially as chiplet technology matures and becomes more cost-effective for mass-market applications.

Geographically, North America leads the market with 42% share, followed by Asia-Pacific at 38%, Europe at 15%, and other regions at 5%. China's aggressive investments in semiconductor self-sufficiency are expected to significantly alter this distribution within the next five years.

Market research indicates that customers prioritize several key factors when evaluating chiplet interconnect solutions: bandwidth density (cited by 87% of surveyed companies), power efficiency (82%), thermal performance (78%), manufacturing scalability (75%), and standardization/interoperability (73%). The material selection for interposers directly impacts all these factors, making it a critical decision point in chiplet design.

Industry analysts forecast that the demand for advanced materials supporting chiplet interconnect technologies will grow at 45% CAGR through 2030, outpacing the overall chiplet market growth and highlighting the strategic importance of interposer material selection in meeting evolving market requirements.

Current State and Challenges in Interposer Material Technology

The interposer material landscape for UCIe (Universal Chiplet Interconnect Express) implementations is currently dominated by silicon, which offers excellent thermal conductivity, dimensional stability, and compatibility with established semiconductor manufacturing processes. Silicon interposers enable high-density interconnects with fine pitch (sub-10μm) and support high bandwidth connections between chiplets. However, silicon interposers face significant cost challenges due to their complex manufacturing processes, particularly for large-area applications exceeding 50mm x 50mm dimensions.

Organic interposer materials have emerged as a cost-effective alternative, offering reduced manufacturing complexity and better scalability for larger form factors. These materials demonstrate good electrical performance for mid-range bandwidth requirements but struggle to match silicon's interconnect density and thermal management capabilities. Current organic interposers typically achieve minimum line/space dimensions of approximately 2-5μm, which limits their application in the highest-performance UCIe implementations.

Glass interposers represent a promising middle ground, offering better dimensional stability than organics while being more cost-effective than silicon. Recent advancements have enabled through-glass via (TGV) technologies with improved reliability, though challenges remain in achieving the ultra-fine pitch required for advanced UCIe applications. Glass interposers currently achieve line/space dimensions of approximately 1-2μm, positioning them between silicon and organic options.

A significant technical challenge across all interposer materials is managing coefficient of thermal expansion (CTE) mismatches between the interposer and attached chiplets. This mismatch creates mechanical stress during thermal cycling, potentially leading to connection failures at the interface points. Silicon offers the best CTE match with semiconductor chiplets but at higher cost, while organic and glass materials must incorporate specialized design features to mitigate these thermal expansion differences.

Signal integrity represents another critical challenge, particularly as UCIe implementations push toward higher data rates exceeding 32GT/s. Current interposer materials struggle with signal loss, crosstalk, and impedance control at these speeds, necessitating advanced design techniques including equalization, shielding structures, and precise impedance matching. The industry is actively researching advanced dielectric materials with improved loss tangent properties to address these high-frequency challenges.

Manufacturing scalability remains a persistent challenge, with current silicon interposer production limited by wafer size constraints and complex through-silicon via (TSV) processes. While organic and glass alternatives offer better scalability, they face yield challenges when implementing the fine-pitch interconnects required by UCIe specifications. The industry is exploring panel-level processing techniques to improve manufacturing economics for larger interposer formats.

Organic interposer materials have emerged as a cost-effective alternative, offering reduced manufacturing complexity and better scalability for larger form factors. These materials demonstrate good electrical performance for mid-range bandwidth requirements but struggle to match silicon's interconnect density and thermal management capabilities. Current organic interposers typically achieve minimum line/space dimensions of approximately 2-5μm, which limits their application in the highest-performance UCIe implementations.

Glass interposers represent a promising middle ground, offering better dimensional stability than organics while being more cost-effective than silicon. Recent advancements have enabled through-glass via (TGV) technologies with improved reliability, though challenges remain in achieving the ultra-fine pitch required for advanced UCIe applications. Glass interposers currently achieve line/space dimensions of approximately 1-2μm, positioning them between silicon and organic options.

A significant technical challenge across all interposer materials is managing coefficient of thermal expansion (CTE) mismatches between the interposer and attached chiplets. This mismatch creates mechanical stress during thermal cycling, potentially leading to connection failures at the interface points. Silicon offers the best CTE match with semiconductor chiplets but at higher cost, while organic and glass materials must incorporate specialized design features to mitigate these thermal expansion differences.

Signal integrity represents another critical challenge, particularly as UCIe implementations push toward higher data rates exceeding 32GT/s. Current interposer materials struggle with signal loss, crosstalk, and impedance control at these speeds, necessitating advanced design techniques including equalization, shielding structures, and precise impedance matching. The industry is actively researching advanced dielectric materials with improved loss tangent properties to address these high-frequency challenges.

Manufacturing scalability remains a persistent challenge, with current silicon interposer production limited by wafer size constraints and complex through-silicon via (TSV) processes. While organic and glass alternatives offer better scalability, they face yield challenges when implementing the fine-pitch interconnects required by UCIe specifications. The industry is exploring panel-level processing techniques to improve manufacturing economics for larger interposer formats.

Current Interposer Material Selection Methodologies

01 Thermal management materials for UCIe interposers

Thermal management is a critical factor in selecting materials for UCIe chiplet interconnect interposers. Materials with high thermal conductivity help dissipate heat efficiently from densely packed chiplets, preventing performance degradation and ensuring reliability. Advanced thermal interface materials and heat-dissipating substrates are incorporated into interposer designs to manage the thermal challenges of high-performance chiplet architectures. These materials often include metal-based composites or ceramics with optimized thermal properties.- Thermal management materials for UCIe interposers: Thermal management is critical for UCIe chiplet interconnects, requiring interposer materials with excellent thermal conductivity. Materials such as silicon carbide, aluminum nitride, and diamond-based composites are selected for their ability to efficiently dissipate heat generated by high-density chiplet configurations. These materials help maintain optimal operating temperatures across the interconnected chiplets, preventing thermal-induced performance degradation and ensuring reliability in high-performance computing applications.

- Electrical performance criteria for interposer materials: Electrical performance is a key selection criterion for UCIe interposer materials. Materials must exhibit low signal loss, minimal crosstalk, and controlled impedance to support high-speed data transmission between chiplets. Advanced ceramic substrates, organic laminates with embedded capacitance, and glass-based interposers are evaluated based on their dielectric constant, loss tangent, and frequency response characteristics. These properties directly impact signal integrity and bandwidth capabilities of the UCIe interconnect system.

- Mechanical stability and reliability considerations: Mechanical stability is essential for UCIe interposer materials to ensure reliable chiplet connections. Materials must have compatible coefficients of thermal expansion (CTE) with both silicon dies and package substrates to minimize stress during thermal cycling. Interposer materials are selected based on their mechanical strength, fracture toughness, and dimensional stability. Advanced composite materials, reinforced polymers, and silicon-based interposers with stress-relief features are employed to maintain structural integrity throughout the product lifecycle.

- Manufacturing process compatibility and scalability: UCIe interposer material selection is heavily influenced by manufacturing process compatibility and scalability considerations. Materials must be compatible with established semiconductor fabrication techniques, including lithography, etching, and metallization processes. Glass, silicon, and organic substrates with different process requirements are evaluated based on their ability to support fine-pitch interconnects, through-silicon vias (TSVs), and redistribution layers (RDLs). Cost-effective materials that enable high-yield manufacturing while meeting the dimensional precision requirements of UCIe specifications are preferred.

- Advanced material innovations for next-generation UCIe: Emerging materials are being developed to address the evolving requirements of next-generation UCIe implementations. These include heterogeneous integration of 2D materials like graphene, engineered substrates with embedded optical waveguides, and hybrid organic-inorganic composites. Novel materials with tunable properties are being explored to enable higher bandwidth density, improved power efficiency, and enhanced system integration. Research focuses on materials that can support sub-micron interconnect pitches while maintaining manufacturability and reliability for future chiplet architectures.

02 Electrical performance characteristics of interposer materials

The electrical properties of interposer materials significantly impact UCIe chiplet interconnect performance. Materials are selected based on their dielectric constant, signal integrity characteristics, and ability to support high-frequency data transmission with minimal loss. Low-loss dielectric materials that can maintain signal integrity at high frequencies are preferred. Additionally, materials that provide controlled impedance and minimize crosstalk between adjacent interconnects are essential for achieving the high bandwidth and low latency requirements of UCIe specifications.Expand Specific Solutions03 Mechanical stability and reliability considerations

Mechanical properties are crucial when selecting materials for UCIe chiplet interconnect interposers. Materials must provide dimensional stability, withstand thermal cycling, and maintain structural integrity during manufacturing and operation. Coefficient of thermal expansion (CTE) matching between the interposer, chiplets, and package substrate is essential to prevent stress-induced failures. Materials that offer high stiffness while accommodating the different expansion rates of silicon and organic substrates are particularly valuable for ensuring long-term reliability of chiplet-based systems.Expand Specific Solutions04 Advanced manufacturing compatibility of interposer materials

Materials for UCIe chiplet interconnect interposers must be compatible with advanced manufacturing processes. This includes considerations for fine-pitch wiring, through-silicon vias (TSVs), and microbump technologies. Materials that can be processed with high precision and yield are preferred. Additionally, materials must withstand the thermal budgets of various assembly steps, including die attach, underfill application, and solder reflow. The ability to create ultra-fine interconnect features while maintaining manufacturability at scale is a key selection criterion.Expand Specific Solutions05 Novel composite and hybrid interposer materials

Innovative composite and hybrid materials are being developed specifically for UCIe chiplet interconnect interposers. These materials combine the benefits of different material classes to achieve optimal performance across multiple criteria. Examples include glass-core organic substrates, silicon-organic hybrids, and advanced ceramic composites. These materials aim to balance electrical performance, thermal management, mechanical reliability, and cost-effectiveness. The development of these specialized materials is driven by the unique requirements of chiplet-based architectures and the need to support increasingly complex integration schemes.Expand Specific Solutions

Key Industry Players in UCIe Chiplet Ecosystem

The UCIe Chiplet Interconnect Interposer Material market is currently in an early growth phase, characterized by rapid technological development and expanding applications in advanced computing systems. The market is projected to grow significantly as chiplet architecture becomes more prevalent in high-performance computing, with estimates suggesting a multi-billion dollar opportunity by 2028. Leading semiconductor giants Intel, TSMC, and Samsung are at the forefront of UCIe material development, with Intel particularly driving standardization efforts. Other key players including Qualcomm, GlobalFoundries, and Shinko Electric are advancing specialized interposer materials with varying thermal, electrical, and mechanical properties. The technology maturity varies across different material solutions, with silicon interposers being most established while glass, organic, and advanced composite interposers represent emerging alternatives offering improved performance characteristics for next-generation chiplet integration.

Intel Corp.

Technical Solution: Intel's UCIe chiplet interconnect interposer material selection focuses on advanced silicon and organic substrates. Their silicon interposer technology utilizes Through-Silicon Vias (TSVs) to enable high-density interconnections between chiplets, supporting bandwidths exceeding 2 TB/s with latencies under 2ns. Intel has developed specialized silicon interposers with embedded capacitors and resistors to optimize signal integrity. For cost-sensitive applications, Intel employs organic substrate interposers with advanced build-up layers and microvias, achieving up to 25-100 Gbps per pin while maintaining thermal performance through copper-filled vias and specialized thermal interface materials. Their material selection criteria prioritize electrical performance (impedance matching, signal loss <0.5dB/mm), thermal conductivity (>100 W/mK for silicon), mechanical stability (CTE matching within 3-5 ppm/°C), and manufacturing scalability.

Strengths: Industry-leading silicon interposer technology with superior electrical performance and integration density; extensive manufacturing infrastructure; comprehensive material qualification process. Weaknesses: Higher cost structure for silicon interposers compared to organic alternatives; thermal management challenges in high-density implementations; longer development cycles for new material integration.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung's approach to UCIe chiplet interconnect interposer material selection centers on their advanced silicon interposer technology and glass substrate development. Their silicon interposers feature ultra-fine pitch redistribution layers (RDL) with line/space dimensions below 1μm and copper-filled TSVs with diameters as small as 5μm, enabling die-to-die connections with bandwidths up to 3.2 GT/s. Samsung has pioneered the use of low-loss glass substrates with tailored dielectric constants (Dk~5.0) and dissipation factors (Df<0.005) for high-frequency signal transmission. Their material selection criteria emphasize electrical performance (insertion loss <0.2dB/mm at 10GHz), thermal management (thermal conductivity >80 W/mK for silicon interposers), reliability (withstanding >1000 thermal cycles), and cost-effectiveness through panel-level processing for glass substrates. Samsung's interposer materials undergo rigorous qualification including high-temperature operating life tests and thermal cycling between -40°C and 125°C.

Strengths: Vertical integration capabilities from materials to packaging; advanced glass substrate technology offering superior electrical performance; established high-volume manufacturing infrastructure. Weaknesses: Higher initial costs for glass substrate implementation; thermal management challenges compared to silicon; complex supply chain for specialized materials.

Critical Material Properties Analysis for UCIe Implementation

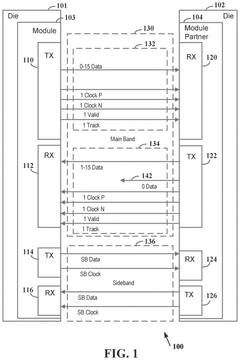

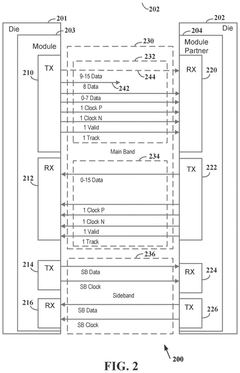

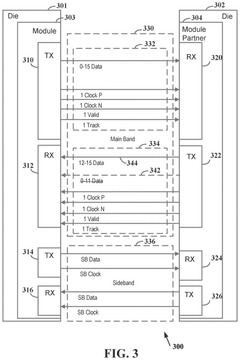

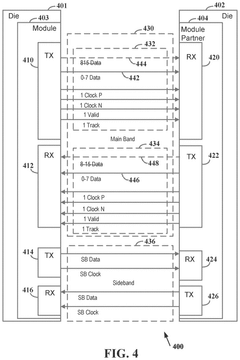

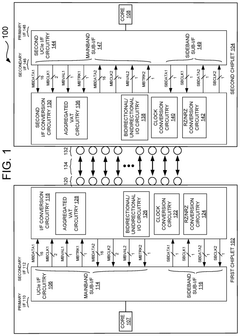

Variable link width in two directions for main band chip module connection

PatentPendingUS20240354279A1

Innovation

- Implementing a method to establish a die-to-die connection with a variable link width, allowing for independent configuration of transmit and receive data lanes through a sideband communication, enabling operation with different numbers of active data lanes in each direction to optimize power usage and data rates, and supporting fault tolerance by excluding faulty lines.

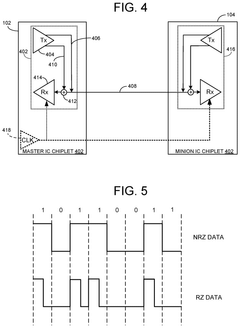

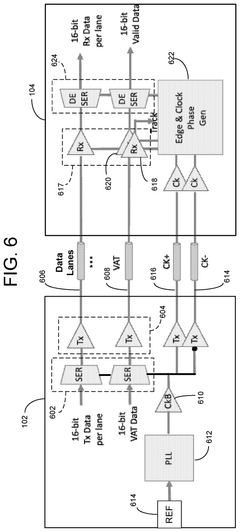

Interface conversion circuitry for universal chiplet interconnect express (UCIe)

PatentActiveUS12248419B1

Innovation

- The implementation of a converter circuit between the UCIe interface circuit and the bump interface, which includes local clock circuitry, oversampling circuitry, and majority detection circuitry, reduces the number of sideband links and corresponding bumps, thereby enhancing bandwidth density and reducing costs.

Thermal Management Considerations for Interposer Materials

Thermal management has emerged as a critical factor in the selection of interposer materials for UCIe chiplet interconnect implementations. As chiplet architectures continue to increase in density and performance requirements, the thermal characteristics of interposer materials directly impact system reliability, performance, and longevity. Silicon interposers, while offering excellent electrical properties, present thermal conductivity limitations (approximately 150 W/m·K) that can create hotspots in high-power applications.

Alternative materials such as aluminum nitride (AlN) and silicon carbide (SiC) demonstrate superior thermal conductivity values of 320 W/m·K and 490 W/m·K respectively, potentially offering significant advantages for thermally-intensive applications. However, these materials introduce manufacturing complexities and cost implications that must be carefully balanced against their thermal benefits.

The coefficient of thermal expansion (CTE) matching between interposer materials and attached chiplets represents another crucial consideration. Mismatches in CTE can lead to mechanical stress during thermal cycling, potentially causing connection failures at the die-to-interposer interface. Silicon interposers offer excellent CTE matching with silicon-based chiplets (approximately 2.6 ppm/°C), while organic interposers typically exhibit higher CTE values (15-17 ppm/°C) that require careful management through underfill materials and design accommodations.

Thermal interface materials (TIMs) between the interposer and attached components significantly influence overall thermal performance. Advanced TIMs incorporating metal particles, liquid metals, or phase-change materials can reduce thermal resistance at these critical junctions. The selection of appropriate TIMs must be integrated into the overall interposer material decision process.

Emerging cooling solutions, including integrated microfluidic channels within interposers, represent promising approaches for managing thermal challenges. Silicon and glass interposers can be effectively manufactured with embedded cooling channels, while organic interposers present greater fabrication challenges for such features. The compatibility of interposer materials with these advanced cooling techniques must be evaluated during material selection.

Computational fluid dynamics (CFD) modeling has become essential for predicting thermal behavior in complex chiplet architectures. These simulations enable engineers to identify potential hotspots and optimize thermal management strategies before physical implementation. The accuracy of these models depends on precise characterization of interposer material thermal properties across operating temperature ranges.

Alternative materials such as aluminum nitride (AlN) and silicon carbide (SiC) demonstrate superior thermal conductivity values of 320 W/m·K and 490 W/m·K respectively, potentially offering significant advantages for thermally-intensive applications. However, these materials introduce manufacturing complexities and cost implications that must be carefully balanced against their thermal benefits.

The coefficient of thermal expansion (CTE) matching between interposer materials and attached chiplets represents another crucial consideration. Mismatches in CTE can lead to mechanical stress during thermal cycling, potentially causing connection failures at the die-to-interposer interface. Silicon interposers offer excellent CTE matching with silicon-based chiplets (approximately 2.6 ppm/°C), while organic interposers typically exhibit higher CTE values (15-17 ppm/°C) that require careful management through underfill materials and design accommodations.

Thermal interface materials (TIMs) between the interposer and attached components significantly influence overall thermal performance. Advanced TIMs incorporating metal particles, liquid metals, or phase-change materials can reduce thermal resistance at these critical junctions. The selection of appropriate TIMs must be integrated into the overall interposer material decision process.

Emerging cooling solutions, including integrated microfluidic channels within interposers, represent promising approaches for managing thermal challenges. Silicon and glass interposers can be effectively manufactured with embedded cooling channels, while organic interposers present greater fabrication challenges for such features. The compatibility of interposer materials with these advanced cooling techniques must be evaluated during material selection.

Computational fluid dynamics (CFD) modeling has become essential for predicting thermal behavior in complex chiplet architectures. These simulations enable engineers to identify potential hotspots and optimize thermal management strategies before physical implementation. The accuracy of these models depends on precise characterization of interposer material thermal properties across operating temperature ranges.

Manufacturing Scalability and Cost Analysis

The manufacturing scalability and cost analysis of UCIe chiplet interconnect interposer materials presents significant considerations for industry adoption. Silicon interposers, while offering excellent electrical performance and thermal characteristics, face scalability challenges due to their complex manufacturing processes. The production requires specialized equipment and clean room facilities, resulting in higher capital expenditure. Current silicon interposer manufacturing capacity is limited, creating potential bottlenecks as chiplet adoption increases across the semiconductor industry.

Alternative materials such as organic substrates offer better scalability advantages with established high-volume manufacturing infrastructure. These materials leverage existing PCB manufacturing techniques, allowing for faster production ramp-up and lower initial investment. However, the trade-off appears in performance limitations compared to silicon, particularly in fine-pitch interconnect density and signal integrity at higher frequencies.

Glass interposers represent a middle-ground solution with promising scalability characteristics. The panel-based manufacturing approach for glass interposers enables larger production formats than silicon wafers, potentially reducing per-unit costs at scale. Current estimates suggest that at high volumes, glass interposer manufacturing could achieve 30-40% cost reduction compared to silicon alternatives while maintaining comparable electrical performance.

Cost modeling across different production volumes reveals interesting inflection points. For low to medium production volumes (under 100,000 units annually), silicon interposers remain prohibitively expensive due to high fixed costs. Organic substrates demonstrate the lowest entry cost but struggle to meet advanced performance requirements. Glass interposers become increasingly cost-competitive at annual production volumes exceeding 500,000 units, where economies of scale offset initial tooling investments.

Manufacturing yield considerations significantly impact overall cost structures. Silicon interposers typically achieve 85-90% yields in mature processes but require expensive known-good-die testing. Organic substrates generally achieve higher yields (92-95%) with simpler testing requirements. Glass interposer technology, still evolving, currently demonstrates yields in the 80-85% range but shows potential for improvement as manufacturing processes mature.

Supply chain resilience must also factor into scalability assessments. Silicon interposer production remains concentrated among a few advanced foundries, creating potential supply constraints. Organic substrate manufacturing is more geographically distributed, offering better supply chain diversity. Glass interposer production capacity is currently limited but expanding as more manufacturers recognize its potential as a strategic alternative material.

Alternative materials such as organic substrates offer better scalability advantages with established high-volume manufacturing infrastructure. These materials leverage existing PCB manufacturing techniques, allowing for faster production ramp-up and lower initial investment. However, the trade-off appears in performance limitations compared to silicon, particularly in fine-pitch interconnect density and signal integrity at higher frequencies.

Glass interposers represent a middle-ground solution with promising scalability characteristics. The panel-based manufacturing approach for glass interposers enables larger production formats than silicon wafers, potentially reducing per-unit costs at scale. Current estimates suggest that at high volumes, glass interposer manufacturing could achieve 30-40% cost reduction compared to silicon alternatives while maintaining comparable electrical performance.

Cost modeling across different production volumes reveals interesting inflection points. For low to medium production volumes (under 100,000 units annually), silicon interposers remain prohibitively expensive due to high fixed costs. Organic substrates demonstrate the lowest entry cost but struggle to meet advanced performance requirements. Glass interposers become increasingly cost-competitive at annual production volumes exceeding 500,000 units, where economies of scale offset initial tooling investments.

Manufacturing yield considerations significantly impact overall cost structures. Silicon interposers typically achieve 85-90% yields in mature processes but require expensive known-good-die testing. Organic substrates generally achieve higher yields (92-95%) with simpler testing requirements. Glass interposer technology, still evolving, currently demonstrates yields in the 80-85% range but shows potential for improvement as manufacturing processes mature.

Supply chain resilience must also factor into scalability assessments. Silicon interposer production remains concentrated among a few advanced foundries, creating potential supply constraints. Organic substrate manufacturing is more geographically distributed, offering better supply chain diversity. Glass interposer production capacity is currently limited but expanding as more manufacturers recognize its potential as a strategic alternative material.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!