Supply Chain Risk Assessment For UCIe Chiplet Interconnect

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Technology Background and Objectives

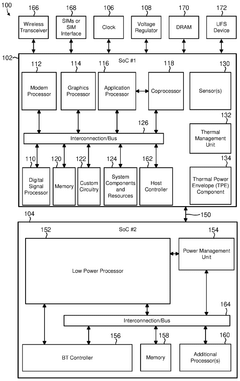

Universal Chiplet Interconnect Express (UCIe) represents a significant evolution in semiconductor integration technology, emerging from the limitations of traditional monolithic chip designs. As Moore's Law faces increasing physical and economic constraints, the industry has pivoted toward chiplet-based architectures that enable the disaggregation of system-on-chip (SoC) designs into smaller, specialized components. UCIe was formally introduced in March 2022 as an open industry standard, backed by major semiconductor companies including Intel, AMD, Arm, TSMC, and Samsung.

The historical trajectory of chiplet technology began with early multi-chip modules in the 1990s, progressing through 2.5D integration with silicon interposers in the 2010s, to today's advanced package-level integration. UCIe represents the culmination of these developments, offering standardized die-to-die interconnect protocols that promise to revolutionize semiconductor design and manufacturing.

The primary objective of UCIe technology is to establish an open, unified interconnect standard that enables heterogeneous integration of chiplets from different vendors, fabricated using different process nodes, into a single package. This standardization aims to foster a more diverse and innovative chiplet ecosystem while reducing development costs and time-to-market for complex semiconductor products.

UCIe addresses several critical technical goals: achieving high bandwidth density (up to 16 GT/s in UCIe 1.0), minimizing power consumption through efficient signaling, ensuring low latency communication between dies, and maintaining signal integrity across the interconnect. The standard encompasses both physical layer specifications and protocol stack definitions to ensure interoperability.

From a supply chain perspective, UCIe aims to transform the semiconductor industry's structure by enabling a more modular approach to chip design and manufacturing. This modularization potentially allows for greater specialization among suppliers, more flexible sourcing strategies, and reduced dependency on single vendors or manufacturing processes.

The long-term technical vision for UCIe includes scaling to higher data rates, reducing power consumption further, expanding protocol support, and enhancing security features. Future iterations of the standard are expected to address emerging requirements for artificial intelligence, high-performance computing, and edge computing applications, where the benefits of chiplet-based designs are particularly compelling.

As semiconductor manufacturing becomes increasingly concentrated in specific geographic regions, UCIe technology offers a potential pathway to more resilient supply chains through its inherent support for multi-vendor integration and manufacturing flexibility, though this also introduces new supply chain risks that must be carefully assessed.

The historical trajectory of chiplet technology began with early multi-chip modules in the 1990s, progressing through 2.5D integration with silicon interposers in the 2010s, to today's advanced package-level integration. UCIe represents the culmination of these developments, offering standardized die-to-die interconnect protocols that promise to revolutionize semiconductor design and manufacturing.

The primary objective of UCIe technology is to establish an open, unified interconnect standard that enables heterogeneous integration of chiplets from different vendors, fabricated using different process nodes, into a single package. This standardization aims to foster a more diverse and innovative chiplet ecosystem while reducing development costs and time-to-market for complex semiconductor products.

UCIe addresses several critical technical goals: achieving high bandwidth density (up to 16 GT/s in UCIe 1.0), minimizing power consumption through efficient signaling, ensuring low latency communication between dies, and maintaining signal integrity across the interconnect. The standard encompasses both physical layer specifications and protocol stack definitions to ensure interoperability.

From a supply chain perspective, UCIe aims to transform the semiconductor industry's structure by enabling a more modular approach to chip design and manufacturing. This modularization potentially allows for greater specialization among suppliers, more flexible sourcing strategies, and reduced dependency on single vendors or manufacturing processes.

The long-term technical vision for UCIe includes scaling to higher data rates, reducing power consumption further, expanding protocol support, and enhancing security features. Future iterations of the standard are expected to address emerging requirements for artificial intelligence, high-performance computing, and edge computing applications, where the benefits of chiplet-based designs are particularly compelling.

As semiconductor manufacturing becomes increasingly concentrated in specific geographic regions, UCIe technology offers a potential pathway to more resilient supply chains through its inherent support for multi-vendor integration and manufacturing flexibility, though this also introduces new supply chain risks that must be carefully assessed.

Market Demand Analysis for Chiplet-Based Solutions

The chiplet-based semiconductor market is experiencing unprecedented growth, driven by the increasing demand for high-performance computing solutions across various industries. Current market analysis indicates that the global chiplet market is projected to grow at a compound annual growth rate of 40% from 2023 to 2030, reaching significant market valuation by the end of the decade. This rapid expansion is primarily fueled by the inherent advantages of chiplet technology over traditional monolithic designs, including improved yield, enhanced performance, and greater design flexibility.

The demand for UCIe (Universal Chiplet Interconnect Express) based solutions is particularly strong in data centers and cloud computing environments, where the need for high-bandwidth, low-latency communication between processing elements is critical. Enterprise customers are increasingly seeking modular computing architectures that can be customized to specific workloads while maintaining energy efficiency, a key value proposition of chiplet-based designs.

Market research indicates that approximately 65% of high-performance computing systems are expected to incorporate chiplet technology by 2027, with UCIe emerging as the dominant interconnect standard. This transition is being accelerated by the growing complexity of semiconductor manufacturing at advanced nodes, where the economics of monolithic designs become increasingly challenging.

The automotive and telecommunications sectors represent emerging markets for chiplet-based solutions, particularly with the rollout of 5G infrastructure and the increasing computational requirements of autonomous vehicles. These applications demand specialized processing capabilities that can be efficiently delivered through heterogeneous integration of chiplets.

Supply chain considerations are becoming increasingly important in market adoption decisions. End customers are expressing growing concerns about supply chain resilience, with recent surveys indicating that 78% of semiconductor purchasers now consider supply chain risk as a critical factor in technology selection. This trend is particularly pronounced in strategic sectors such as defense, aerospace, and critical infrastructure.

Regional market analysis reveals varying adoption rates, with North America and East Asia leading in chiplet implementation. However, Europe is rapidly accelerating its investments in this technology, particularly through initiatives aimed at strengthening semiconductor sovereignty and reducing dependency on external suppliers.

The market is also witnessing increased demand for standardized testing and validation methodologies specific to chiplet-based designs, as customers seek assurance regarding the reliability and interoperability of multi-vendor chiplet solutions. This represents an emerging opportunity for specialized service providers in the semiconductor ecosystem.

The demand for UCIe (Universal Chiplet Interconnect Express) based solutions is particularly strong in data centers and cloud computing environments, where the need for high-bandwidth, low-latency communication between processing elements is critical. Enterprise customers are increasingly seeking modular computing architectures that can be customized to specific workloads while maintaining energy efficiency, a key value proposition of chiplet-based designs.

Market research indicates that approximately 65% of high-performance computing systems are expected to incorporate chiplet technology by 2027, with UCIe emerging as the dominant interconnect standard. This transition is being accelerated by the growing complexity of semiconductor manufacturing at advanced nodes, where the economics of monolithic designs become increasingly challenging.

The automotive and telecommunications sectors represent emerging markets for chiplet-based solutions, particularly with the rollout of 5G infrastructure and the increasing computational requirements of autonomous vehicles. These applications demand specialized processing capabilities that can be efficiently delivered through heterogeneous integration of chiplets.

Supply chain considerations are becoming increasingly important in market adoption decisions. End customers are expressing growing concerns about supply chain resilience, with recent surveys indicating that 78% of semiconductor purchasers now consider supply chain risk as a critical factor in technology selection. This trend is particularly pronounced in strategic sectors such as defense, aerospace, and critical infrastructure.

Regional market analysis reveals varying adoption rates, with North America and East Asia leading in chiplet implementation. However, Europe is rapidly accelerating its investments in this technology, particularly through initiatives aimed at strengthening semiconductor sovereignty and reducing dependency on external suppliers.

The market is also witnessing increased demand for standardized testing and validation methodologies specific to chiplet-based designs, as customers seek assurance regarding the reliability and interoperability of multi-vendor chiplet solutions. This represents an emerging opportunity for specialized service providers in the semiconductor ecosystem.

UCIe Interconnect Technology Status and Challenges

Universal Chiplet Interconnect Express (UCIe) represents a significant advancement in semiconductor integration technology, enabling heterogeneous chiplet integration across different process nodes and manufacturers. Currently, UCIe is at a critical juncture in its development cycle, with version 1.0 specifications released in 2022 and version 1.1 under development. The technology has gained substantial industry support with over 80 member companies in the UCIe Consortium, including major players like Intel, AMD, TSMC, and Samsung.

Despite its promising trajectory, UCIe faces several significant technical challenges. The primary challenge lies in ensuring interoperability across different manufacturers' chiplets, as variations in implementation can lead to compatibility issues. The standardization process is still evolving, with ongoing debates about protocol extensions and optimization for different use cases, creating uncertainty for early adopters.

Signal integrity presents another major hurdle, particularly as data rates increase to meet performance demands. At the targeted 16-32 GT/s speeds, maintaining signal quality across die-to-die interfaces becomes increasingly difficult, requiring advanced equalization techniques and careful power management. This challenge is compounded by thermal considerations, as densely packed chiplets generate significant heat that must be efficiently dissipated to prevent performance degradation.

Testing and validation methodologies for UCIe implementations remain underdeveloped, with limited industry consensus on best practices. This creates difficulties in ensuring quality and reliability across the supply chain, particularly when integrating chiplets from multiple vendors. The lack of mature testing frameworks increases development time and potentially introduces reliability risks.

From a supply chain perspective, UCIe faces geopolitical and concentration risks. The technology's advanced packaging requirements depend heavily on facilities concentrated in East Asia, particularly Taiwan and South Korea. This geographic concentration creates vulnerability to regional disruptions, whether from natural disasters, political tensions, or pandemic-related restrictions.

The ecosystem for UCIe is still developing, with limited availability of design tools, IP blocks, and verification methodologies specifically optimized for chiplet-based designs. This ecosystem immaturity creates barriers to adoption, particularly for smaller companies without extensive in-house expertise in advanced packaging technologies.

Material science challenges also persist, particularly regarding the development of advanced substrate materials that can support the high-density interconnects required by UCIe while maintaining reliability under thermal and mechanical stress. Current substrate technologies represent a potential bottleneck in the broader adoption of chiplet-based designs.

Despite its promising trajectory, UCIe faces several significant technical challenges. The primary challenge lies in ensuring interoperability across different manufacturers' chiplets, as variations in implementation can lead to compatibility issues. The standardization process is still evolving, with ongoing debates about protocol extensions and optimization for different use cases, creating uncertainty for early adopters.

Signal integrity presents another major hurdle, particularly as data rates increase to meet performance demands. At the targeted 16-32 GT/s speeds, maintaining signal quality across die-to-die interfaces becomes increasingly difficult, requiring advanced equalization techniques and careful power management. This challenge is compounded by thermal considerations, as densely packed chiplets generate significant heat that must be efficiently dissipated to prevent performance degradation.

Testing and validation methodologies for UCIe implementations remain underdeveloped, with limited industry consensus on best practices. This creates difficulties in ensuring quality and reliability across the supply chain, particularly when integrating chiplets from multiple vendors. The lack of mature testing frameworks increases development time and potentially introduces reliability risks.

From a supply chain perspective, UCIe faces geopolitical and concentration risks. The technology's advanced packaging requirements depend heavily on facilities concentrated in East Asia, particularly Taiwan and South Korea. This geographic concentration creates vulnerability to regional disruptions, whether from natural disasters, political tensions, or pandemic-related restrictions.

The ecosystem for UCIe is still developing, with limited availability of design tools, IP blocks, and verification methodologies specifically optimized for chiplet-based designs. This ecosystem immaturity creates barriers to adoption, particularly for smaller companies without extensive in-house expertise in advanced packaging technologies.

Material science challenges also persist, particularly regarding the development of advanced substrate materials that can support the high-density interconnects required by UCIe while maintaining reliability under thermal and mechanical stress. Current substrate technologies represent a potential bottleneck in the broader adoption of chiplet-based designs.

Current Supply Chain Risk Mitigation Strategies

01 Supply chain risk assessment for UCIe chiplet interconnects

Methods and systems for assessing supply chain risks specific to Universal Chiplet Interconnect Express (UCIe) technology. These approaches involve identifying vulnerabilities in the chiplet supply chain, evaluating potential disruptions, and implementing risk mitigation strategies. The assessment includes analyzing dependencies between chiplet manufacturers, interconnect technology providers, and system integrators to ensure resilience in the semiconductor ecosystem.- Supply chain security and risk management for chiplet interconnects: UCIe chiplet interconnect technology faces supply chain risks that require comprehensive security measures. These include implementing secure authentication protocols, encryption mechanisms, and monitoring systems to detect tampering or unauthorized access. Risk management frameworks specifically designed for chiplet-based systems help identify vulnerabilities in the supply chain and establish mitigation strategies to ensure the integrity of interconnected components.

- Blockchain-based verification for chiplet supply chain: Blockchain technology provides a secure and transparent method for tracking and verifying chiplet components throughout the supply chain. By creating immutable records of each component's origin, manufacturing process, and handling, blockchain systems can help detect counterfeit parts and unauthorized modifications. This approach enhances trust among supply chain participants and ensures the authenticity of UCIe chiplet interconnect components.

- Multi-vendor interoperability challenges in UCIe implementation: The UCIe chiplet interconnect standard faces challenges related to multi-vendor interoperability, which can introduce supply chain risks. Different manufacturers may implement the standard with slight variations, leading to compatibility issues and potential security vulnerabilities. Standardized testing protocols and certification processes are needed to ensure consistent implementation across vendors and reduce integration risks in heterogeneous chiplet systems.

- Geopolitical factors affecting chiplet supply chain resilience: Geopolitical tensions and trade restrictions significantly impact the UCIe chiplet interconnect supply chain. Regional manufacturing dependencies and export controls can disrupt the availability of critical components. Strategies to enhance supply chain resilience include diversifying manufacturing locations, developing alternative sourcing options, and creating stockpiles of essential components to mitigate disruptions caused by geopolitical events.

- Advanced testing and validation methods for chiplet security: Ensuring the security and reliability of UCIe chiplet interconnects requires advanced testing and validation methodologies. These include side-channel attack analysis, fault injection testing, and comprehensive verification of die-to-die interfaces. Automated testing frameworks can identify vulnerabilities in chiplet designs before integration, while post-manufacturing validation techniques help detect compromised components that might introduce security risks into the final system.

02 Security measures for UCIe chiplet interconnect implementations

Security protocols and mechanisms designed specifically for UCIe chiplet interconnect architectures to protect against supply chain attacks. These include authentication systems for chiplet verification, secure boot processes, encryption of data transmitted between chiplets, and tamper detection technologies. Such security measures help maintain the integrity of multi-chiplet systems and prevent unauthorized access or modifications to the interconnect infrastructure.Expand Specific Solutions03 Blockchain-based tracking for UCIe chiplet supply chain

Implementation of blockchain technology to create transparent and immutable records of UCIe chiplet components throughout the supply chain. This approach enables verification of chiplet provenance, tracks the movement of components from manufacturing to integration, and provides auditable records of quality control processes. Blockchain solutions help address counterfeiting concerns and ensure the authenticity of chiplets used in advanced packaging solutions.Expand Specific Solutions04 Redundancy and resilience strategies for UCIe implementations

Design methodologies that incorporate redundancy and resilience into UCIe chiplet-based systems to mitigate supply chain disruptions. These strategies include multi-sourcing of critical components, development of compatible alternative interconnect technologies, and architectural approaches that allow for graceful degradation rather than complete system failure when certain chiplets become unavailable. Such approaches help maintain system functionality despite supply chain challenges.Expand Specific Solutions05 Regulatory compliance and standardization for UCIe supply chain

Frameworks for ensuring UCIe chiplet interconnect technologies comply with international regulations and standards related to supply chain security. These include certification processes, compliance verification methods, and standardization efforts to establish common security requirements across the industry. The approaches address export control considerations, national security concerns, and the development of trusted supplier networks for critical chiplet components.Expand Specific Solutions

Key Industry Players in UCIe Ecosystem

The UCIe chiplet interconnect technology is currently in an early growth phase, with market size expected to expand significantly as chiplet adoption accelerates across computing sectors. The technology maturity is advancing rapidly with major semiconductor players establishing competitive positions. Intel leads as a founding member of the UCIe consortium, while TSMC, Qualcomm, and AMD (which acquired Xilinx) are developing complementary technologies. Emerging players like Chipletz and Avicena are introducing innovative solutions for chiplet integration. IBM and university research centers (University of Florida, Zhejiang University) are contributing to standards development. The competitive landscape reflects both established semiconductor manufacturers and specialized startups addressing supply chain risks through diversified manufacturing approaches and standardized interfaces.

QUALCOMM, Inc.

Technical Solution: Qualcomm has developed a sophisticated supply chain risk assessment framework for UCIe chiplet interconnect technology focused on mobile and edge computing applications. Their approach centers on a "Security-First" chiplet design methodology that incorporates hardware-level security features directly into the die-to-die interfaces. Qualcomm's supply chain monitoring system employs AI-driven predictive analytics to continuously evaluate over 15,000 components and 500+ suppliers specific to their chiplet ecosystem. Their proprietary "ChipGuard" platform implements real-time monitoring of manufacturing processes across multiple foundries, with automated alerts for any deviations that could indicate quality issues or tampering. Qualcomm has also pioneered advanced physical unclonable function (PUF) technology that creates unique cryptographic identifiers for each chiplet, enabling authentication throughout the supply chain and preventing counterfeiting. Their risk mitigation strategy includes geographic diversification of chiplet manufacturing across multiple regions to reduce geopolitical and natural disaster risks.

Strengths: Industry-leading expertise in mobile/edge computing applications; advanced security features integrated at hardware level; strong geographic diversification strategy. Weaknesses: Complex ecosystem with numerous suppliers increases potential vulnerability points; higher implementation costs compared to monolithic designs.

Intel Corp.

Technical Solution: Intel has pioneered the Universal Chiplet Interconnect Express (UCIe) standard as a founding member and leads the UCIe consortium. Their supply chain risk assessment approach for UCIe involves comprehensive multi-tier supplier monitoring using AI-powered analytics to track over 19,000 suppliers in real-time. Intel implements a Resilient Supply Chain Risk Intelligence (RSCI) platform that integrates geopolitical risk data, supplier financial health metrics, and manufacturing capacity constraints to create risk scores for chiplet ecosystem partners. Their approach includes physical supply chain security with tamper-evident packaging and blockchain-based traceability for chiplet components. Intel's Advanced Interface Bus (AIB) serves as the foundation for their UCIe implementation, with built-in security features including authentication protocols and encryption for die-to-die communications to prevent counterfeiting and tampering of chiplets.

Strengths: Industry-leading position as UCIe founder with established ecosystem partnerships; comprehensive multi-tier supplier visibility; integrated security features in chiplet design. Weaknesses: Heavy reliance on global manufacturing partners creates exposure to geopolitical risks; complex supply chain with numerous dependencies increases vulnerability points.

Critical Patents and Technical Documentation Analysis

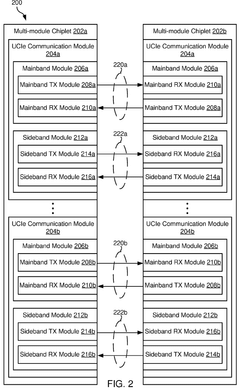

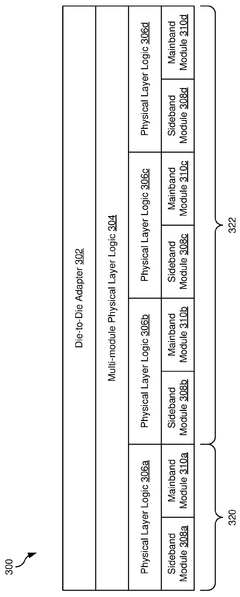

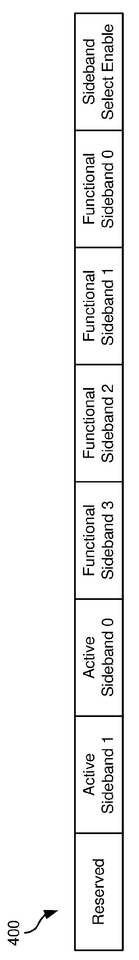

Mechanism to improve the reliability of sideband in chiplets

PatentWO2025058796A1

Innovation

- The method involves configuring UCIe links between multi-module chiplets to enable runtime selection and aggregation of sidebands, allowing for the use of different or additional sidebands beyond the initially active one, thereby reducing hardware stress and enhancing communication reliability.

Functional safety for system-on-chip arrangements

PatentPendingUS20240430125A1

Innovation

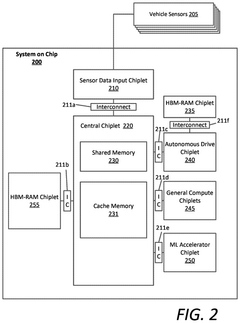

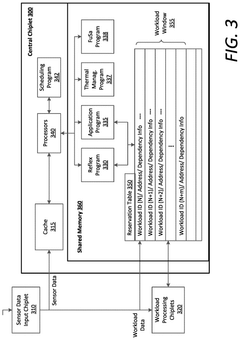

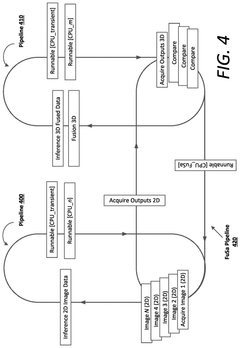

- A computing system with multiple System-on-Chip (SoC) arrangements, including a primary and backup SoC, executes a Functional Safety (FuSa) program to monitor shared memory, compare and verify independent pipeline outputs, and generate error correction codes, ensuring robust hardware components and reliable communication between chiplets, thereby enhancing ASIL ratings.

Geopolitical Factors Affecting UCIe Supply Chain

The geopolitical landscape significantly impacts the UCIe (Universal Chiplet Interconnect Express) supply chain, creating both opportunities and vulnerabilities for stakeholders. The concentration of semiconductor manufacturing capabilities in specific regions, particularly Taiwan, South Korea, and increasingly China, introduces substantial geopolitical risk factors. Taiwan's dominance in advanced semiconductor manufacturing through TSMC creates a critical dependency point that could be disrupted by regional tensions with China.

Trade restrictions and export controls between major economies, especially the ongoing technology competition between the United States and China, directly affect the availability of essential components and technologies for UCIe implementation. The U.S. CHIPS Act and similar initiatives in Europe and Japan represent attempts to reduce dependency on specific regions by reshoring semiconductor manufacturing capabilities, potentially altering the UCIe supply chain dynamics in the coming years.

National security concerns increasingly influence semiconductor policy decisions, with governments viewing chiplet technology as strategically important for both economic competitiveness and defense applications. This has led to increased scrutiny of foreign investments in semiconductor companies and restrictions on technology transfers that could impact UCIe adoption and standardization efforts.

Resource nationalism regarding critical minerals essential for semiconductor manufacturing presents another significant risk factor. Countries rich in materials like rare earth elements, cobalt, and high-purity silicon are increasingly leveraging these resources for geopolitical advantage, potentially affecting the cost and availability of UCIe components.

International standards and intellectual property protection regimes vary significantly across jurisdictions involved in the UCIe ecosystem. Divergent approaches to IP protection and enforcement can create complications for technology sharing and collaborative development essential to the UCIe standard's evolution and implementation.

The fragmentation of technology ecosystems along geopolitical lines threatens the universality implied in the UCIe standard. Regional technology spheres with incompatible standards could emerge if geopolitical tensions continue to escalate, undermining the interoperability benefits that make UCIe valuable to the industry.

Climate change policies and environmental regulations also introduce geopolitical dimensions to the UCIe supply chain, as different regions implement varying requirements for sustainable manufacturing practices and carbon footprint reduction, potentially creating competitive advantages or disadvantages based on regulatory environments.

Trade restrictions and export controls between major economies, especially the ongoing technology competition between the United States and China, directly affect the availability of essential components and technologies for UCIe implementation. The U.S. CHIPS Act and similar initiatives in Europe and Japan represent attempts to reduce dependency on specific regions by reshoring semiconductor manufacturing capabilities, potentially altering the UCIe supply chain dynamics in the coming years.

National security concerns increasingly influence semiconductor policy decisions, with governments viewing chiplet technology as strategically important for both economic competitiveness and defense applications. This has led to increased scrutiny of foreign investments in semiconductor companies and restrictions on technology transfers that could impact UCIe adoption and standardization efforts.

Resource nationalism regarding critical minerals essential for semiconductor manufacturing presents another significant risk factor. Countries rich in materials like rare earth elements, cobalt, and high-purity silicon are increasingly leveraging these resources for geopolitical advantage, potentially affecting the cost and availability of UCIe components.

International standards and intellectual property protection regimes vary significantly across jurisdictions involved in the UCIe ecosystem. Divergent approaches to IP protection and enforcement can create complications for technology sharing and collaborative development essential to the UCIe standard's evolution and implementation.

The fragmentation of technology ecosystems along geopolitical lines threatens the universality implied in the UCIe standard. Regional technology spheres with incompatible standards could emerge if geopolitical tensions continue to escalate, undermining the interoperability benefits that make UCIe valuable to the industry.

Climate change policies and environmental regulations also introduce geopolitical dimensions to the UCIe supply chain, as different regions implement varying requirements for sustainable manufacturing practices and carbon footprint reduction, potentially creating competitive advantages or disadvantages based on regulatory environments.

Standardization and Interoperability Considerations

The standardization of UCIe (Universal Chiplet Interconnect Express) represents a critical foundation for the chiplet ecosystem's growth and security. As an open industry standard, UCIe enables interoperability between chiplets from different vendors, creating both opportunities and challenges for supply chain risk management. The consortium backing UCIe includes major industry players like Intel, AMD, Arm, TSMC, and Samsung, providing broad industry support that enhances standardization efforts.

Interoperability within the UCIe framework requires robust standardization across physical, protocol, and software layers. The physical layer specifications must ensure consistent signal integrity across different manufacturing processes. Protocol layer standardization ensures reliable data exchange between heterogeneous chiplets. Software layer compatibility enables unified management of multi-vendor chiplet configurations. Any inconsistencies in these standardization efforts could introduce security vulnerabilities and reliability issues throughout the supply chain.

Certification and compliance testing mechanisms are essential for validating UCIe implementations against the established standards. Currently, the industry lacks comprehensive certification programs specifically for chiplet interconnects, creating potential interoperability gaps. Organizations must develop standardized testing methodologies to verify both functional compatibility and security compliance across the chiplet ecosystem. These certification processes should include supply chain verification components to ensure components meet both technical and security requirements.

Version control and backward compatibility present significant challenges for UCIe adoption. As the standard evolves, ensuring that newer chiplets can interface with existing ones becomes increasingly complex. Supply chain risk assessments must account for version fragmentation and potential incompatibilities between chiplet generations. Organizations implementing UCIe technology should establish clear policies for managing version transitions and maintaining compatibility across their chiplet portfolio.

International standards alignment represents another critical consideration for UCIe implementation. Different regions may develop varying interpretations or extensions of the UCIe standard, potentially creating geopolitical supply chain vulnerabilities. Harmonizing UCIe with other international standards bodies like ISO, IEC, and regional certification authorities will be essential for maintaining a cohesive global chiplet ecosystem. This alignment would facilitate smoother international trade of chiplet components while reducing regulatory compliance burdens.

Intellectual property considerations within the standardization process also impact supply chain security. The UCIe consortium must balance open standardization with appropriate IP protections to encourage innovation while preventing fragmentation. Clear licensing frameworks for essential patents will help prevent supply chain disruptions caused by IP disputes or licensing barriers that could otherwise restrict market access for certain vendors.

Interoperability within the UCIe framework requires robust standardization across physical, protocol, and software layers. The physical layer specifications must ensure consistent signal integrity across different manufacturing processes. Protocol layer standardization ensures reliable data exchange between heterogeneous chiplets. Software layer compatibility enables unified management of multi-vendor chiplet configurations. Any inconsistencies in these standardization efforts could introduce security vulnerabilities and reliability issues throughout the supply chain.

Certification and compliance testing mechanisms are essential for validating UCIe implementations against the established standards. Currently, the industry lacks comprehensive certification programs specifically for chiplet interconnects, creating potential interoperability gaps. Organizations must develop standardized testing methodologies to verify both functional compatibility and security compliance across the chiplet ecosystem. These certification processes should include supply chain verification components to ensure components meet both technical and security requirements.

Version control and backward compatibility present significant challenges for UCIe adoption. As the standard evolves, ensuring that newer chiplets can interface with existing ones becomes increasingly complex. Supply chain risk assessments must account for version fragmentation and potential incompatibilities between chiplet generations. Organizations implementing UCIe technology should establish clear policies for managing version transitions and maintaining compatibility across their chiplet portfolio.

International standards alignment represents another critical consideration for UCIe implementation. Different regions may develop varying interpretations or extensions of the UCIe standard, potentially creating geopolitical supply chain vulnerabilities. Harmonizing UCIe with other international standards bodies like ISO, IEC, and regional certification authorities will be essential for maintaining a cohesive global chiplet ecosystem. This alignment would facilitate smoother international trade of chiplet components while reducing regulatory compliance burdens.

Intellectual property considerations within the standardization process also impact supply chain security. The UCIe consortium must balance open standardization with appropriate IP protections to encourage innovation while preventing fragmentation. Clear licensing frameworks for essential patents will help prevent supply chain disruptions caused by IP disputes or licensing barriers that could otherwise restrict market access for certain vendors.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!