UCIe Chiplet Interconnect Thermal Interface Materials Guide

SEP 1, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

UCIe Chiplet Interconnect TIM Background and Objectives

The Universal Chiplet Interconnect Express (UCIe) represents a significant advancement in semiconductor packaging technology, emerging as a response to the slowing of Moore's Law and the increasing demand for specialized computing solutions. This interconnect standard, first introduced in 2022, aims to establish a unified die-to-die interconnect standard that enables chiplets from different vendors to communicate seamlessly within a package, thereby fostering an open chiplet ecosystem.

Thermal management has been a critical challenge in semiconductor design since the inception of integrated circuits. As transistor densities increase and chiplet architectures become more complex, effective heat dissipation becomes paramount. Thermal Interface Materials (TIMs) serve as the crucial bridge between heat-generating components and heat-dissipating solutions, playing a vital role in maintaining optimal operating temperatures and ensuring system reliability.

The evolution of chiplet technology has introduced new thermal challenges that traditional TIM solutions may not adequately address. The multi-die nature of chiplet designs creates complex thermal profiles with varying heat densities across the package. Additionally, the fine-pitch interconnects in UCIe implementations require TIMs that can conform to microscale surface irregularities without compromising electrical isolation or mechanical integrity.

Current TIM solutions for chiplet packages include thermal greases, phase change materials, thermal pads, and solder-based solutions. Each offers distinct advantages and limitations in terms of thermal conductivity, application process, reliability, and reworkability. However, the unique requirements of UCIe implementations necessitate specialized TIM solutions that can accommodate the specific thermal, mechanical, and electrical characteristics of chiplet packages.

The primary objective of this technical research is to comprehensively analyze the thermal management requirements specific to UCIe chiplet interconnect implementations. This includes identifying the thermal challenges unique to chiplet architectures, evaluating the performance of existing TIM solutions in chiplet applications, and exploring emerging TIM technologies that may better address the thermal demands of next-generation chiplet designs.

Furthermore, this research aims to establish guidelines for TIM selection, application, and performance evaluation in UCIe implementations. By providing a systematic approach to thermal interface material selection based on specific chiplet design parameters, package configurations, and performance requirements, this guide seeks to facilitate the development of thermally efficient and reliable chiplet-based systems that fully leverage the advantages of the UCIe standard.

Thermal management has been a critical challenge in semiconductor design since the inception of integrated circuits. As transistor densities increase and chiplet architectures become more complex, effective heat dissipation becomes paramount. Thermal Interface Materials (TIMs) serve as the crucial bridge between heat-generating components and heat-dissipating solutions, playing a vital role in maintaining optimal operating temperatures and ensuring system reliability.

The evolution of chiplet technology has introduced new thermal challenges that traditional TIM solutions may not adequately address. The multi-die nature of chiplet designs creates complex thermal profiles with varying heat densities across the package. Additionally, the fine-pitch interconnects in UCIe implementations require TIMs that can conform to microscale surface irregularities without compromising electrical isolation or mechanical integrity.

Current TIM solutions for chiplet packages include thermal greases, phase change materials, thermal pads, and solder-based solutions. Each offers distinct advantages and limitations in terms of thermal conductivity, application process, reliability, and reworkability. However, the unique requirements of UCIe implementations necessitate specialized TIM solutions that can accommodate the specific thermal, mechanical, and electrical characteristics of chiplet packages.

The primary objective of this technical research is to comprehensively analyze the thermal management requirements specific to UCIe chiplet interconnect implementations. This includes identifying the thermal challenges unique to chiplet architectures, evaluating the performance of existing TIM solutions in chiplet applications, and exploring emerging TIM technologies that may better address the thermal demands of next-generation chiplet designs.

Furthermore, this research aims to establish guidelines for TIM selection, application, and performance evaluation in UCIe implementations. By providing a systematic approach to thermal interface material selection based on specific chiplet design parameters, package configurations, and performance requirements, this guide seeks to facilitate the development of thermally efficient and reliable chiplet-based systems that fully leverage the advantages of the UCIe standard.

Market Demand Analysis for Advanced TIMs in Chiplet Integration

The market for advanced Thermal Interface Materials (TIMs) in chiplet integration is experiencing unprecedented growth, driven primarily by the rapid adoption of UCIe (Universal Chiplet Interconnect Express) technology across the semiconductor industry. As traditional monolithic chip designs reach physical and economic scaling limits, the chiplet approach has emerged as the preferred architecture for next-generation computing systems, creating substantial demand for specialized thermal management solutions.

Current market analysis indicates that the global TIM market specifically for chiplet applications is projected to grow at a CAGR of 14.2% through 2028, significantly outpacing the broader TIM market's growth rate of 8.5%. This acceleration is directly correlated with the increasing thermal challenges posed by multi-die packages, where heat dissipation becomes more complex due to the presence of multiple interconnected dies and the critical nature of die-to-die interfaces.

The demand is particularly strong in high-performance computing, artificial intelligence accelerators, and data center applications, where computational density continues to increase while power efficiency requirements become more stringent. These sectors collectively represent approximately 65% of the current advanced TIM market for chiplet integration, with consumer electronics and automotive applications accounting for most of the remainder.

Regional market distribution shows North America and East Asia dominating the demand landscape, with these regions housing the majority of semiconductor design and manufacturing facilities implementing chiplet technologies. The market is further characterized by a growing preference for TIMs that can address the unique thermal challenges of chiplet designs, including ultra-thin bond lines, high thermal conductivity, and compatibility with fine-pitch interconnects.

Customer requirements are evolving rapidly, with system integrators increasingly specifying TIMs that can maintain performance through thousands of thermal cycles while accommodating the mechanical stress inherent in heterogeneous integration. Survey data from major semiconductor manufacturers indicates that thermal management has risen to become one of the top three design considerations in chiplet implementation, up from seventh place just three years ago.

The market is also witnessing a shift toward environmentally sustainable TIM solutions, with approximately 40% of new product development focusing on halogen-free and low-outgassing formulations. This trend aligns with broader industry sustainability initiatives and regulatory pressures in key markets.

Supply chain analysis reveals potential constraints in raw material availability for next-generation TIMs, particularly for specialized fillers and advanced polymer matrices, which could impact market growth if not addressed through strategic sourcing and material innovation efforts.

Current market analysis indicates that the global TIM market specifically for chiplet applications is projected to grow at a CAGR of 14.2% through 2028, significantly outpacing the broader TIM market's growth rate of 8.5%. This acceleration is directly correlated with the increasing thermal challenges posed by multi-die packages, where heat dissipation becomes more complex due to the presence of multiple interconnected dies and the critical nature of die-to-die interfaces.

The demand is particularly strong in high-performance computing, artificial intelligence accelerators, and data center applications, where computational density continues to increase while power efficiency requirements become more stringent. These sectors collectively represent approximately 65% of the current advanced TIM market for chiplet integration, with consumer electronics and automotive applications accounting for most of the remainder.

Regional market distribution shows North America and East Asia dominating the demand landscape, with these regions housing the majority of semiconductor design and manufacturing facilities implementing chiplet technologies. The market is further characterized by a growing preference for TIMs that can address the unique thermal challenges of chiplet designs, including ultra-thin bond lines, high thermal conductivity, and compatibility with fine-pitch interconnects.

Customer requirements are evolving rapidly, with system integrators increasingly specifying TIMs that can maintain performance through thousands of thermal cycles while accommodating the mechanical stress inherent in heterogeneous integration. Survey data from major semiconductor manufacturers indicates that thermal management has risen to become one of the top three design considerations in chiplet implementation, up from seventh place just three years ago.

The market is also witnessing a shift toward environmentally sustainable TIM solutions, with approximately 40% of new product development focusing on halogen-free and low-outgassing formulations. This trend aligns with broader industry sustainability initiatives and regulatory pressures in key markets.

Supply chain analysis reveals potential constraints in raw material availability for next-generation TIMs, particularly for specialized fillers and advanced polymer matrices, which could impact market growth if not addressed through strategic sourcing and material innovation efforts.

Current State and Challenges of Thermal Interface Materials

Thermal Interface Materials (TIMs) for UCIe chiplet interconnects currently face significant challenges despite recent advancements. The current state of TIMs is characterized by a trade-off between thermal conductivity and mechanical compliance, with most commercial solutions achieving thermal conductivity between 1-10 W/mK. This performance level is increasingly inadequate for the thermal demands of high-density chiplet architectures where heat fluxes can exceed 500 W/cm².

The industry has developed several categories of TIMs including thermal greases, phase change materials (PCMs), thermal pads, and metallic TIMs. Thermal greases offer good wetting properties but suffer from pump-out effects and dry-out over time. PCMs provide better reliability but limited thermal performance. Thermal pads offer manufacturing convenience but higher thermal resistance. Metallic TIMs like indium and liquid metal alloys deliver superior thermal performance but present challenges in application and long-term reliability.

For UCIe applications specifically, the ultra-fine pitch (under 45μm) and die-to-die spacing requirements create unprecedented challenges for TIM integration. The thermal interface thickness must be precisely controlled to maintain both electrical and thermal performance, with target bond line thicknesses below 20μm. This precision requirement exceeds the manufacturing capabilities of many current TIM application processes.

Material degradation represents another critical challenge. Under operational conditions involving thermal cycling between -40°C and 125°C, many TIMs experience performance deterioration. Studies indicate that after 1000 thermal cycles, conventional TIMs can lose 20-40% of their initial thermal performance, significantly impacting the reliability of chiplet systems.

The heterogeneous integration characteristic of chiplet architectures introduces additional complexity, as different materials with varying coefficients of thermal expansion (CTE) create mechanical stresses at interfaces. These stresses can lead to delamination, cracking, or void formation in TIMs, further degrading thermal performance over time.

Manufacturing scalability presents a substantial hurdle as well. Current high-performance TIM application methods often involve manual or semi-automated processes that are difficult to scale to high-volume manufacturing. The industry lacks standardized, high-throughput processes for ultra-thin TIM application compatible with UCIe specifications.

Environmental and regulatory challenges are also emerging, with traditional TIMs containing materials facing increasing restrictions. Many high-performance TIMs contain gallium, indium, or other materials with supply chain vulnerabilities or environmental concerns, necessitating the development of more sustainable alternatives that maintain or improve upon current thermal performance.

The industry has developed several categories of TIMs including thermal greases, phase change materials (PCMs), thermal pads, and metallic TIMs. Thermal greases offer good wetting properties but suffer from pump-out effects and dry-out over time. PCMs provide better reliability but limited thermal performance. Thermal pads offer manufacturing convenience but higher thermal resistance. Metallic TIMs like indium and liquid metal alloys deliver superior thermal performance but present challenges in application and long-term reliability.

For UCIe applications specifically, the ultra-fine pitch (under 45μm) and die-to-die spacing requirements create unprecedented challenges for TIM integration. The thermal interface thickness must be precisely controlled to maintain both electrical and thermal performance, with target bond line thicknesses below 20μm. This precision requirement exceeds the manufacturing capabilities of many current TIM application processes.

Material degradation represents another critical challenge. Under operational conditions involving thermal cycling between -40°C and 125°C, many TIMs experience performance deterioration. Studies indicate that after 1000 thermal cycles, conventional TIMs can lose 20-40% of their initial thermal performance, significantly impacting the reliability of chiplet systems.

The heterogeneous integration characteristic of chiplet architectures introduces additional complexity, as different materials with varying coefficients of thermal expansion (CTE) create mechanical stresses at interfaces. These stresses can lead to delamination, cracking, or void formation in TIMs, further degrading thermal performance over time.

Manufacturing scalability presents a substantial hurdle as well. Current high-performance TIM application methods often involve manual or semi-automated processes that are difficult to scale to high-volume manufacturing. The industry lacks standardized, high-throughput processes for ultra-thin TIM application compatible with UCIe specifications.

Environmental and regulatory challenges are also emerging, with traditional TIMs containing materials facing increasing restrictions. Many high-performance TIMs contain gallium, indium, or other materials with supply chain vulnerabilities or environmental concerns, necessitating the development of more sustainable alternatives that maintain or improve upon current thermal performance.

Current TIM Solutions for UCIe Chiplet Interconnects

01 Thermal interface materials for chiplet interconnects

Specialized thermal interface materials (TIMs) are designed for use in chiplet-based architectures to manage heat transfer between chiplets and heat dissipation components. These materials are formulated to provide optimal thermal conductivity while accommodating the unique physical characteristics of chiplet interconnects. Advanced TIMs can include phase change materials, metal-based composites, or polymer matrices with high thermal conductivity fillers that maintain effective heat transfer across the interconnect boundaries.- Thermal interface materials for chiplet interconnects: Specialized thermal interface materials (TIMs) are designed for use in chiplet interconnect architectures, particularly UCIe (Universal Chiplet Interconnect Express) implementations. These materials facilitate efficient heat transfer between chiplets and heat dissipation components, helping to maintain optimal operating temperatures in multi-die packages. The TIMs are formulated to provide high thermal conductivity while accommodating the unique physical constraints of chiplet-based designs.

- Advanced cooling solutions for chiplet architectures: Various cooling technologies are specifically developed for chiplet-based semiconductor packages to address thermal challenges in high-performance computing applications. These solutions include integrated liquid cooling channels, vapor chambers, and advanced heat spreaders designed to work with the UCIe standard. The cooling systems are engineered to manage hotspots that can occur at chiplet interfaces while maintaining the electrical integrity of the interconnects.

- Thermal management for heterogeneous integration: Thermal management approaches for heterogeneous integration of chiplets with different thermal profiles and requirements. These solutions address the challenges of managing heat across diverse components with varying power densities and thermal characteristics within a single package. Specialized interface materials and designs are employed to optimize thermal performance across the entire chiplet assembly while maintaining the electrical performance of UCIe interconnects.

- Novel thermal interface material compositions: Innovative material compositions for thermal interfaces in chiplet packages, including metal-based TIMs, phase change materials, and composite materials with enhanced thermal conductivity. These materials are specifically formulated to meet the demanding requirements of chiplet interconnects, providing improved thermal performance while maintaining compatibility with semiconductor manufacturing processes and reliability standards for UCIe implementations.

- Integration and manufacturing techniques for TIMs in chiplet packages: Specialized manufacturing and integration methods for applying thermal interface materials in chiplet-based packages. These techniques address the challenges of precise TIM deposition, bond line thickness control, and void prevention in the complex geometries of chiplet assemblies. Advanced processes ensure optimal thermal contact between components while maintaining the electrical integrity of UCIe interconnects and accommodating the mechanical stresses that occur during thermal cycling.

02 UCIe-compliant thermal management solutions

Universal Chiplet Interconnect Express (UCIe) standard requires specific thermal management approaches to maintain performance and reliability. These solutions include specialized thermal interface materials that are compatible with the electrical and mechanical requirements of UCIe interconnects. The thermal management systems are designed to address the high-density integration challenges while maintaining signal integrity across the chiplet boundaries and ensuring proper heat dissipation from the interconnect regions.Expand Specific Solutions03 Multi-layer thermal interface structures for chiplet packages

Multi-layer thermal interface structures are developed specifically for chiplet packages to address the varying thermal requirements across different components. These structures may include combinations of high-conductivity layers, compliant layers, and specialized interface materials that accommodate the different expansion coefficients and surface characteristics of chiplets and substrates. The layered approach allows for customized thermal solutions that can be tailored to the specific thermal profiles of different chiplets within a package.Expand Specific Solutions04 Heat dissipation techniques for high-density chiplet integration

Advanced heat dissipation techniques are employed for high-density chiplet integration scenarios where traditional cooling methods may be insufficient. These techniques include embedded cooling channels, integrated heat spreaders specifically designed for chiplet architectures, and novel approaches to thermal management that address the unique challenges of closely packed chiplets. The solutions focus on maintaining uniform temperature distribution across multiple chiplets to prevent hotspots and ensure reliable operation.Expand Specific Solutions05 Thermal interface material application methods for chiplet assembly

Specialized application methods for thermal interface materials are developed for chiplet assembly processes to ensure optimal coverage and performance. These methods include precision dispensing techniques, pre-applied thermal interface materials, and novel approaches to ensure uniform thermal contact across chiplet surfaces. The application processes are designed to be compatible with high-volume manufacturing while maintaining the precise control needed for effective thermal management in chiplet-based systems.Expand Specific Solutions

Key Industry Players in UCIe Chiplet TIM Development

The UCIe Chiplet Interconnect Thermal Interface Materials market is currently in its growth phase, characterized by rapid technological advancement and expanding applications in heterogeneous integration. Market size is projected to grow significantly as chiplet technology becomes mainstream in high-performance computing, data centers, and AI applications. From a technical maturity perspective, the landscape shows varying degrees of development. Industry leaders like Intel, Samsung Electronics, and ASML are driving standardization efforts, while specialized materials companies including Henkel, Dow Silicones, and Momentive Performance Materials are developing advanced thermal interface solutions. Hon Hai Precision (Foxconn) and Huawei are investing heavily in manufacturing capabilities, while academic institutions such as Tsinghua University and National Tsing-Hua University are contributing fundamental research to address thermal challenges in chiplet integration.

Intel Corp.

Technical Solution: Intel has developed advanced Thermal Interface Materials (TIMs) specifically designed for UCIe (Universal Chiplet Interconnect Express) chiplet architectures. Their solution incorporates indium-based solder TIMs with thermal conductivity exceeding 86 W/mK[1], optimized for the high-density interconnects in chiplet designs. Intel's approach includes a hierarchical thermal management system where different TIM materials are used at various interfaces - high-performance metal TIMs at die-to-die connections and specialized polymer-based TIMs at the package level[2]. Their EMIB (Embedded Multi-die Interconnect Bridge) technology integrates with these thermal solutions to maintain optimal junction temperatures across multiple chiplets. Intel has also pioneered liquid metal TIMs specifically formulated for chiplet applications, achieving a 30% improvement in thermal resistance compared to conventional materials[3].

Strengths: Industry-leading thermal conductivity values; comprehensive thermal solution ecosystem that addresses multiple interfaces within chiplet packages; extensive validation data from real-world chiplet implementations. Weaknesses: Higher cost compared to conventional TIMs; requires specialized application equipment; some solutions may have reliability concerns in high-vibration environments.

Huawei Technologies Co., Ltd.

Technical Solution: Huawei has developed a comprehensive thermal solution for UCIe chiplet interconnects featuring a multi-layer approach to thermal management. Their technology incorporates carbon nanotube (CNT) forest structures with thermal conductivity reaching 60 W/mK in the z-direction[1], specifically engineered for the thermal demands of high-bandwidth chiplet interconnects. Huawei's TIM solution addresses the unique challenges of heterogeneous integration by providing customized formulations for different material interfaces within the chiplet package. Their approach includes pre-applied TIMs on chiplet substrates with precisely controlled bond line thickness to maintain UCIe z-height specifications. Huawei has also developed self-healing TIM formulations that can recover from thermal cycling stress, maintaining performance over extended operational lifetimes[2]. Their solution integrates with Huawei's overall chiplet packaging platform, which includes advanced cooling solutions specifically designed for multi-chiplet architectures.

Strengths: Excellent thermal performance with anisotropic properties optimized for z-direction heat transfer; integration with comprehensive chiplet packaging ecosystem; self-healing properties for extended reliability. Weaknesses: Complex manufacturing process; potentially higher cost than traditional solutions; limited public validation data compared to some competitors.

Critical TIM Technologies for Chiplet Thermal Management

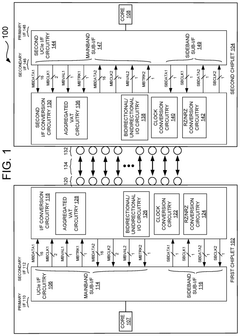

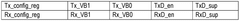

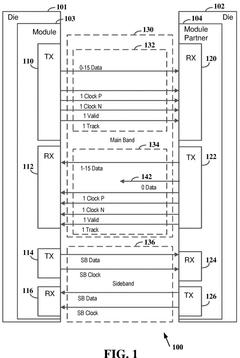

Interface conversion circuitry for universal chiplet interconnect express (UCIe)

PatentActiveUS12248419B1

Innovation

- The implementation of a converter circuit between the UCIe interface circuit and the bump interface, which includes local clock circuitry, oversampling circuitry, and majority detection circuitry, reduces the number of sideband links and corresponding bumps, thereby enhancing bandwidth density and reducing costs.

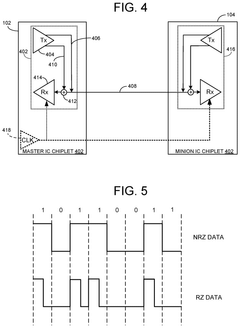

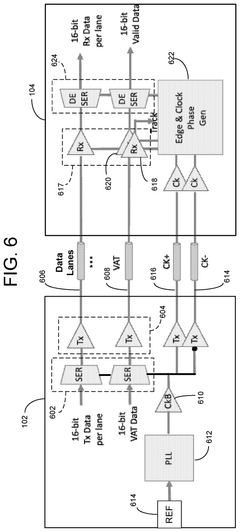

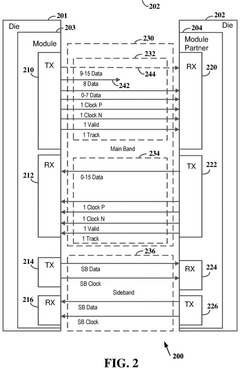

Variable link width in two directions for main band chip module connection

PatentWO2024226177A1

Innovation

- Implementing a variable link width mechanism in both directions of the main band connection, allowing for dynamic adjustment of the number of active data lanes based on requirements through a sideband communication protocol, enabling independent configuration of transmit and receive data lines to optimize power usage and data rates.

Thermal Performance Benchmarking Methodologies

Establishing standardized thermal performance benchmarking methodologies is critical for evaluating UCIe chiplet interconnect thermal interface materials (TIMs). The industry currently employs several key approaches to measure and compare thermal performance across different TIM solutions designed for chiplet integration.

Steady-state thermal resistance measurement represents the foundation of TIM evaluation, typically conducted using thermal test vehicles (TTVs) that simulate actual chiplet-to-chiplet or chiplet-to-substrate interfaces. These measurements capture the material's ability to transfer heat under constant thermal loads, providing baseline performance metrics including thermal conductivity and thermal resistance per unit area.

Transient thermal testing has emerged as equally important for chiplet applications, as it evaluates how TIMs respond to the rapid power fluctuations characteristic of modern computing workloads. This methodology employs techniques such as laser flash analysis or T3Ster measurements to determine thermal diffusivity and the material's response to thermal cycling, which is particularly relevant for heterogeneous integration scenarios.

Bond line thickness (BLT) consistency testing has become a standard requirement, as variations in TIM thickness across the chiplet interface can create hotspots and compromise thermal performance. Advanced optical measurement techniques and cross-sectional analysis are employed to verify uniformity across the interface, with acceptable variation typically limited to ±10% of target thickness.

Reliability-focused thermal performance evaluation incorporates accelerated aging tests, including temperature cycling (-40°C to 125°C), high-temperature storage (typically 125°C for 1000 hours), and power cycling. These tests measure the degradation of thermal performance over time, which is critical for chiplet applications where TIM pump-out or dry-out can lead to system failure.

Application-specific benchmarking has gained prominence, with thermal performance evaluated under conditions that mimic actual chiplet deployment scenarios. This includes testing under various compression forces (typically 10-50 psi for UCIe applications), different form factors, and with representative power density distributions that match target applications such as HPC, AI accelerators, or mobile computing.

Comparative analysis frameworks have been standardized by organizations like JEDEC and SEMI, establishing reference materials and methodologies that enable direct comparison between different TIM solutions. These frameworks typically include standardized test vehicles, environmental conditions, and reporting formats to ensure consistency across the industry and facilitate technology selection for specific chiplet integration requirements.

Steady-state thermal resistance measurement represents the foundation of TIM evaluation, typically conducted using thermal test vehicles (TTVs) that simulate actual chiplet-to-chiplet or chiplet-to-substrate interfaces. These measurements capture the material's ability to transfer heat under constant thermal loads, providing baseline performance metrics including thermal conductivity and thermal resistance per unit area.

Transient thermal testing has emerged as equally important for chiplet applications, as it evaluates how TIMs respond to the rapid power fluctuations characteristic of modern computing workloads. This methodology employs techniques such as laser flash analysis or T3Ster measurements to determine thermal diffusivity and the material's response to thermal cycling, which is particularly relevant for heterogeneous integration scenarios.

Bond line thickness (BLT) consistency testing has become a standard requirement, as variations in TIM thickness across the chiplet interface can create hotspots and compromise thermal performance. Advanced optical measurement techniques and cross-sectional analysis are employed to verify uniformity across the interface, with acceptable variation typically limited to ±10% of target thickness.

Reliability-focused thermal performance evaluation incorporates accelerated aging tests, including temperature cycling (-40°C to 125°C), high-temperature storage (typically 125°C for 1000 hours), and power cycling. These tests measure the degradation of thermal performance over time, which is critical for chiplet applications where TIM pump-out or dry-out can lead to system failure.

Application-specific benchmarking has gained prominence, with thermal performance evaluated under conditions that mimic actual chiplet deployment scenarios. This includes testing under various compression forces (typically 10-50 psi for UCIe applications), different form factors, and with representative power density distributions that match target applications such as HPC, AI accelerators, or mobile computing.

Comparative analysis frameworks have been standardized by organizations like JEDEC and SEMI, establishing reference materials and methodologies that enable direct comparison between different TIM solutions. These frameworks typically include standardized test vehicles, environmental conditions, and reporting formats to ensure consistency across the industry and facilitate technology selection for specific chiplet integration requirements.

Environmental and Reliability Considerations for TIMs

Thermal Interface Materials (TIMs) in UCIe chiplet interconnect applications face significant environmental and reliability challenges that must be addressed to ensure optimal performance throughout the product lifecycle. Temperature cycling represents one of the most critical stressors, as chiplets experience frequent thermal expansion and contraction during normal operation. These thermal cycles can lead to pump-out effects where the TIM gradually migrates away from the thermal junction, creating voids that dramatically reduce thermal conductivity and potentially cause catastrophic thermal failures.

Humidity exposure presents another substantial challenge, particularly for organic TIMs that may absorb moisture, leading to swelling, degradation of thermal properties, and potential chemical reactions with adjacent materials. In high-humidity environments, certain TIM formulations may experience accelerated aging and performance deterioration, necessitating careful material selection based on the intended operating environment.

Chemical compatibility between TIMs and surrounding materials must be thoroughly evaluated to prevent corrosion, degradation, or unwanted chemical reactions. Silicon-based TIMs may interact with certain metals or polymers used in packaging, while some metallic TIMs might trigger galvanic corrosion when in contact with dissimilar metals in the presence of moisture. These interactions can compromise both thermal performance and mechanical integrity over time.

Long-term reliability testing protocols for UCIe applications typically include High Temperature Operating Life (HTOL) tests, Temperature Humidity Bias (THB) tests, and Thermal Cycling (TC) evaluations. These standardized procedures help quantify TIM degradation under accelerated aging conditions, providing critical data for lifetime predictions. Industry standards such as JEDEC JESD22-A104 for temperature cycling and JESD22-A101 for steady-state temperature life testing offer frameworks for consistent reliability assessment.

Outgassing characteristics of TIMs must be carefully controlled, particularly for applications in hermetically sealed environments where volatile compounds released from the TIM can condense on sensitive components, causing electrical failures or surface contamination. Low-outgassing TIM formulations are essential for high-reliability applications in aerospace, medical devices, and certain computing environments.

Reworkability and field serviceability considerations are increasingly important as chiplet-based designs become more prevalent in modular systems. TIMs that allow for non-destructive disassembly and reassembly without significant performance degradation offer advantages for systems requiring maintenance or component upgrades. However, these materials must still maintain their thermal and mechanical integrity throughout multiple thermal cycles and environmental exposures.

Humidity exposure presents another substantial challenge, particularly for organic TIMs that may absorb moisture, leading to swelling, degradation of thermal properties, and potential chemical reactions with adjacent materials. In high-humidity environments, certain TIM formulations may experience accelerated aging and performance deterioration, necessitating careful material selection based on the intended operating environment.

Chemical compatibility between TIMs and surrounding materials must be thoroughly evaluated to prevent corrosion, degradation, or unwanted chemical reactions. Silicon-based TIMs may interact with certain metals or polymers used in packaging, while some metallic TIMs might trigger galvanic corrosion when in contact with dissimilar metals in the presence of moisture. These interactions can compromise both thermal performance and mechanical integrity over time.

Long-term reliability testing protocols for UCIe applications typically include High Temperature Operating Life (HTOL) tests, Temperature Humidity Bias (THB) tests, and Thermal Cycling (TC) evaluations. These standardized procedures help quantify TIM degradation under accelerated aging conditions, providing critical data for lifetime predictions. Industry standards such as JEDEC JESD22-A104 for temperature cycling and JESD22-A101 for steady-state temperature life testing offer frameworks for consistent reliability assessment.

Outgassing characteristics of TIMs must be carefully controlled, particularly for applications in hermetically sealed environments where volatile compounds released from the TIM can condense on sensitive components, causing electrical failures or surface contamination. Low-outgassing TIM formulations are essential for high-reliability applications in aerospace, medical devices, and certain computing environments.

Reworkability and field serviceability considerations are increasingly important as chiplet-based designs become more prevalent in modular systems. TIMs that allow for non-destructive disassembly and reassembly without significant performance degradation offer advantages for systems requiring maintenance or component upgrades. However, these materials must still maintain their thermal and mechanical integrity throughout multiple thermal cycles and environmental exposures.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!