Chiplet Uses for Revolutionary Digital Signal Processing Systems

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet DSP Evolution

The evolution of Chiplet-based Digital Signal Processing (DSP) systems represents a significant paradigm shift in the field of signal processing and semiconductor design. This technological progression can be traced through several key stages, each marked by notable advancements and innovations.

In the early 2000s, traditional monolithic DSP architectures dominated the landscape. These single-chip solutions offered integrated functionality but faced limitations in scalability and manufacturing yield. As signal processing demands increased, particularly in telecommunications and multimedia applications, the industry began exploring alternative approaches.

The mid-2000s saw the emergence of multi-core DSP architectures, which aimed to address performance bottlenecks by parallelizing signal processing tasks. While this approach improved processing capabilities, it still faced challenges in terms of power efficiency and die size limitations.

The concept of Chiplets gained traction in the early 2010s as a potential solution to these challenges. Initial Chiplet-based DSP designs focused on disaggregating certain functional blocks, such as memory or I/O interfaces, from the main processing core. This modular approach allowed for more flexible designs and improved manufacturing yields.

As Chiplet technology matured, the industry witnessed a shift towards more granular disaggregation of DSP functionalities. By the mid-2010s, companies began developing specialized Chiplets for specific signal processing tasks, such as FFT acceleration or adaptive filtering. This trend enabled the creation of highly customized DSP solutions tailored to specific application requirements.

The late 2010s marked a significant milestone with the introduction of advanced packaging technologies, such as 2.5D and 3D integration. These innovations allowed for more efficient interconnects between Chiplets, reducing latency and power consumption. This period also saw the development of standardized interfaces for Chiplet integration, facilitating interoperability and ecosystem growth.

Recent years have witnessed the convergence of Chiplet-based DSP systems with other emerging technologies. The integration of AI accelerators alongside DSP Chiplets has enabled more intelligent and adaptive signal processing capabilities. Additionally, the incorporation of photonic interconnects in Chiplet designs has opened new possibilities for high-bandwidth, low-latency signal processing applications.

Looking ahead, the evolution of Chiplet-based DSP systems is expected to continue along several trajectories. Advancements in heterogeneous integration techniques promise even greater flexibility in combining diverse processing elements. The development of more sophisticated power management strategies at the Chiplet level will further enhance energy efficiency. Moreover, the adoption of new materials and manufacturing processes may lead to breakthroughs in Chiplet performance and integration density.

In the early 2000s, traditional monolithic DSP architectures dominated the landscape. These single-chip solutions offered integrated functionality but faced limitations in scalability and manufacturing yield. As signal processing demands increased, particularly in telecommunications and multimedia applications, the industry began exploring alternative approaches.

The mid-2000s saw the emergence of multi-core DSP architectures, which aimed to address performance bottlenecks by parallelizing signal processing tasks. While this approach improved processing capabilities, it still faced challenges in terms of power efficiency and die size limitations.

The concept of Chiplets gained traction in the early 2010s as a potential solution to these challenges. Initial Chiplet-based DSP designs focused on disaggregating certain functional blocks, such as memory or I/O interfaces, from the main processing core. This modular approach allowed for more flexible designs and improved manufacturing yields.

As Chiplet technology matured, the industry witnessed a shift towards more granular disaggregation of DSP functionalities. By the mid-2010s, companies began developing specialized Chiplets for specific signal processing tasks, such as FFT acceleration or adaptive filtering. This trend enabled the creation of highly customized DSP solutions tailored to specific application requirements.

The late 2010s marked a significant milestone with the introduction of advanced packaging technologies, such as 2.5D and 3D integration. These innovations allowed for more efficient interconnects between Chiplets, reducing latency and power consumption. This period also saw the development of standardized interfaces for Chiplet integration, facilitating interoperability and ecosystem growth.

Recent years have witnessed the convergence of Chiplet-based DSP systems with other emerging technologies. The integration of AI accelerators alongside DSP Chiplets has enabled more intelligent and adaptive signal processing capabilities. Additionally, the incorporation of photonic interconnects in Chiplet designs has opened new possibilities for high-bandwidth, low-latency signal processing applications.

Looking ahead, the evolution of Chiplet-based DSP systems is expected to continue along several trajectories. Advancements in heterogeneous integration techniques promise even greater flexibility in combining diverse processing elements. The development of more sophisticated power management strategies at the Chiplet level will further enhance energy efficiency. Moreover, the adoption of new materials and manufacturing processes may lead to breakthroughs in Chiplet performance and integration density.

DSP Market Dynamics

The digital signal processing (DSP) market is experiencing significant growth and transformation, driven by the increasing demand for high-performance computing in various applications. The global DSP market size was valued at $12.48 billion in 2020 and is projected to reach $28.35 billion by 2028, growing at a CAGR of 9.2% during the forecast period. This robust growth is attributed to the rising adoption of DSP technologies in consumer electronics, telecommunications, automotive, and industrial sectors.

In the consumer electronics segment, the proliferation of smartphones, tablets, and smart home devices has been a major driver for DSP market expansion. These devices rely heavily on DSP chips for audio and video processing, image enhancement, and power management. The telecommunications industry continues to be a significant contributor to the DSP market, with the ongoing rollout of 5G networks requiring advanced signal processing capabilities for improved spectral efficiency and reduced latency.

The automotive sector is emerging as a key growth area for DSP applications, particularly in advanced driver assistance systems (ADAS) and autonomous vehicles. DSP chips play a crucial role in processing sensor data, enabling real-time decision-making, and enhancing overall vehicle safety and performance. The industrial sector is also witnessing increased adoption of DSP technologies for applications such as predictive maintenance, process control, and industrial automation.

Geographically, North America and Asia-Pacific are the dominant regions in the DSP market. North America leads in terms of technological advancements and research initiatives, while Asia-Pacific is experiencing rapid growth due to the presence of major semiconductor manufacturers and the increasing adoption of DSP technologies in countries like China, Japan, and South Korea.

The competitive landscape of the DSP market is characterized by the presence of several key players, including Texas Instruments, Analog Devices, NXP Semiconductors, and Xilinx (now part of AMD). These companies are continuously investing in research and development to enhance their DSP product portfolios and maintain their market positions. The market is also witnessing the entry of new players and startups focusing on specialized DSP applications, particularly in emerging fields such as artificial intelligence and machine learning.

As the demand for more powerful and energy-efficient DSP solutions continues to grow, the industry is shifting towards advanced architectures and manufacturing processes. The integration of DSP functionalities with other technologies, such as artificial intelligence and edge computing, is opening up new opportunities and applications. This trend is expected to drive further innovation and market expansion in the coming years, making the DSP market a dynamic and rapidly evolving sector within the broader semiconductor industry.

In the consumer electronics segment, the proliferation of smartphones, tablets, and smart home devices has been a major driver for DSP market expansion. These devices rely heavily on DSP chips for audio and video processing, image enhancement, and power management. The telecommunications industry continues to be a significant contributor to the DSP market, with the ongoing rollout of 5G networks requiring advanced signal processing capabilities for improved spectral efficiency and reduced latency.

The automotive sector is emerging as a key growth area for DSP applications, particularly in advanced driver assistance systems (ADAS) and autonomous vehicles. DSP chips play a crucial role in processing sensor data, enabling real-time decision-making, and enhancing overall vehicle safety and performance. The industrial sector is also witnessing increased adoption of DSP technologies for applications such as predictive maintenance, process control, and industrial automation.

Geographically, North America and Asia-Pacific are the dominant regions in the DSP market. North America leads in terms of technological advancements and research initiatives, while Asia-Pacific is experiencing rapid growth due to the presence of major semiconductor manufacturers and the increasing adoption of DSP technologies in countries like China, Japan, and South Korea.

The competitive landscape of the DSP market is characterized by the presence of several key players, including Texas Instruments, Analog Devices, NXP Semiconductors, and Xilinx (now part of AMD). These companies are continuously investing in research and development to enhance their DSP product portfolios and maintain their market positions. The market is also witnessing the entry of new players and startups focusing on specialized DSP applications, particularly in emerging fields such as artificial intelligence and machine learning.

As the demand for more powerful and energy-efficient DSP solutions continues to grow, the industry is shifting towards advanced architectures and manufacturing processes. The integration of DSP functionalities with other technologies, such as artificial intelligence and edge computing, is opening up new opportunities and applications. This trend is expected to drive further innovation and market expansion in the coming years, making the DSP market a dynamic and rapidly evolving sector within the broader semiconductor industry.

Chiplet Challenges

The adoption of chiplet technology in digital signal processing (DSP) systems presents several significant challenges that need to be addressed for successful implementation. One of the primary obstacles is the integration complexity associated with combining multiple chiplets into a cohesive system. This requires advanced packaging technologies and precise interconnect solutions to ensure seamless communication between different chiplets.

Thermal management poses another critical challenge in chiplet-based DSP systems. As multiple chiplets are packed closely together, heat dissipation becomes a major concern. Efficient cooling solutions and thermal design considerations are essential to maintain optimal performance and prevent thermal-induced failures.

Power distribution and management across multiple chiplets present unique challenges. Ensuring consistent power delivery to each chiplet while managing power consumption and efficiency requires sophisticated power distribution networks and intelligent power management techniques.

The design and optimization of inter-chiplet communication interfaces are crucial for achieving high-performance DSP systems. Bandwidth limitations, latency issues, and signal integrity concerns must be carefully addressed to maintain the overall system performance and reliability.

Testing and validation of chiplet-based DSP systems introduce new complexities. Traditional testing methodologies may not be sufficient, necessitating the development of new testing strategies and tools capable of verifying the functionality and performance of individual chiplets as well as the integrated system.

Standardization and interoperability remain significant challenges in the chiplet ecosystem. The lack of universal standards for chiplet interfaces and protocols can hinder the widespread adoption of chiplet technology in DSP systems. Efforts towards establishing industry-wide standards are crucial for fostering innovation and compatibility.

The yield and cost considerations associated with chiplet manufacturing and integration present economic challenges. While chiplets offer potential cost benefits through improved yield and mix-and-match flexibility, the initial investment in new manufacturing and packaging technologies can be substantial.

Ensuring security and trust in multi-chiplet systems is another critical challenge. As DSP systems often handle sensitive data, protecting against potential security vulnerabilities introduced by the chiplet architecture is paramount.

Lastly, the design and verification complexity of chiplet-based DSP systems pose significant challenges. Developing effective methodologies for system-level design, simulation, and verification of multi-chiplet architectures requires new tools and approaches, adding to the overall complexity of the development process.

Thermal management poses another critical challenge in chiplet-based DSP systems. As multiple chiplets are packed closely together, heat dissipation becomes a major concern. Efficient cooling solutions and thermal design considerations are essential to maintain optimal performance and prevent thermal-induced failures.

Power distribution and management across multiple chiplets present unique challenges. Ensuring consistent power delivery to each chiplet while managing power consumption and efficiency requires sophisticated power distribution networks and intelligent power management techniques.

The design and optimization of inter-chiplet communication interfaces are crucial for achieving high-performance DSP systems. Bandwidth limitations, latency issues, and signal integrity concerns must be carefully addressed to maintain the overall system performance and reliability.

Testing and validation of chiplet-based DSP systems introduce new complexities. Traditional testing methodologies may not be sufficient, necessitating the development of new testing strategies and tools capable of verifying the functionality and performance of individual chiplets as well as the integrated system.

Standardization and interoperability remain significant challenges in the chiplet ecosystem. The lack of universal standards for chiplet interfaces and protocols can hinder the widespread adoption of chiplet technology in DSP systems. Efforts towards establishing industry-wide standards are crucial for fostering innovation and compatibility.

The yield and cost considerations associated with chiplet manufacturing and integration present economic challenges. While chiplets offer potential cost benefits through improved yield and mix-and-match flexibility, the initial investment in new manufacturing and packaging technologies can be substantial.

Ensuring security and trust in multi-chiplet systems is another critical challenge. As DSP systems often handle sensitive data, protecting against potential security vulnerabilities introduced by the chiplet architecture is paramount.

Lastly, the design and verification complexity of chiplet-based DSP systems pose significant challenges. Developing effective methodologies for system-level design, simulation, and verification of multi-chiplet architectures requires new tools and approaches, adding to the overall complexity of the development process.

Current Chiplet DSP

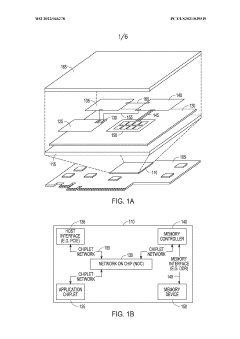

01 Chiplet-based digital signal processing architecture

This approach involves designing digital signal processing systems using multiple chiplets, which are smaller, specialized integrated circuits that can be combined to form a larger system. This modular architecture allows for greater flexibility, improved performance, and potentially lower costs in DSP applications.- Chiplet-based digital signal processing architecture: This approach involves designing digital signal processing systems using chiplet technology. Chiplets are small, modular integrated circuits that can be combined to form larger, more complex systems. In the context of digital signal processing, chiplets can be used to create flexible and scalable DSP architectures, allowing for improved performance and efficiency.

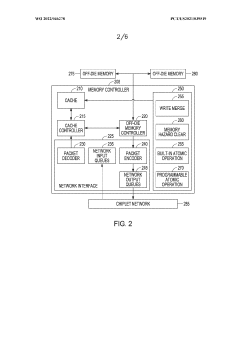

- Inter-chiplet communication for DSP applications: This focuses on developing efficient communication protocols and interfaces between chiplets in a digital signal processing system. These communication methods are crucial for ensuring high-speed data transfer and low-latency processing in multi-chiplet DSP architectures, enabling seamless integration of various DSP functions across multiple chiplets.

- Power management in chiplet-based DSP systems: This involves implementing advanced power management techniques in chiplet-based digital signal processing systems. By optimizing power distribution and consumption across multiple chiplets, these methods aim to improve energy efficiency and thermal management in complex DSP architectures.

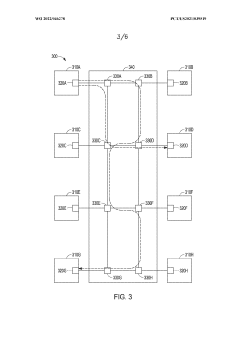

- Reconfigurable chiplet-based DSP architectures: This approach focuses on creating flexible and reconfigurable digital signal processing architectures using chiplets. By allowing dynamic reconfiguration of chiplet connections and functions, these systems can adapt to different DSP tasks and optimize performance based on specific application requirements.

- Integration of specialized DSP functions in chiplets: This involves designing chiplets with specialized digital signal processing functions, such as FFT processors, filters, or machine learning accelerators. By integrating these specialized functions into individual chiplets, complex DSP systems can be built more efficiently, allowing for modular and scalable designs.

02 Inter-chiplet communication for DSP

Efficient communication between chiplets is crucial for digital signal processing applications. This includes high-speed interfaces, low-latency protocols, and optimized data transfer mechanisms to ensure seamless integration of multiple chiplets in a DSP system.Expand Specific Solutions03 Power management in chiplet-based DSP systems

Implementing effective power management strategies in chiplet-based digital signal processing systems is essential for optimizing energy efficiency. This includes techniques for dynamic power gating, voltage scaling, and thermal management across multiple chiplets.Expand Specific Solutions04 Reconfigurable chiplet architectures for DSP

Developing reconfigurable chiplet architectures allows for adaptable digital signal processing systems that can be optimized for different applications or workloads. This flexibility enables more efficient use of resources and improved performance across various DSP tasks.Expand Specific Solutions05 AI-enhanced chiplet-based DSP

Integrating artificial intelligence capabilities into chiplet-based digital signal processing systems can enhance performance and enable more advanced signal processing techniques. This may include dedicated AI chiplets or AI-accelerated DSP algorithms distributed across multiple chiplets.Expand Specific Solutions

Chiplet DSP Players

The chiplet technology for revolutionary digital signal processing systems is in an early growth stage, with the market poised for significant expansion. The global chiplet market is projected to reach several billion dollars by 2025, driven by increasing demand for high-performance computing and AI applications. While the technology is still evolving, major players like Intel, AMD, and Huawei are making substantial investments in chiplet-based architectures. Companies such as Micron, Texas Instruments, and NXP Semiconductors are also exploring chiplet solutions for DSP applications, indicating a competitive landscape with diverse approaches to implementation and integration.

Intel Corp.

Technical Solution: Intel's approach to Chiplet-based Digital Signal Processing (DSP) systems leverages their advanced packaging technologies, particularly their Embedded Multi-die Interconnect Bridge (EMIB) and Foveros 3D packaging. For DSP applications, Intel integrates specialized DSP cores with high-bandwidth memory (HBM) and other functional blocks using these packaging technologies. This allows for heterogeneous integration, combining different process nodes and specialized IP blocks optimized for DSP workloads. Intel's Agilex FPGA family, which incorporates chiplet technology, can be configured for high-performance DSP applications, offering up to 40 TeraFLOPS of DSP performance[1]. The chiplet approach enables Intel to mix and match different IP blocks, potentially combining their x86 cores with dedicated DSP engines and AI accelerators, all within a single package, enhancing the overall system performance for complex signal processing tasks[2].

Strengths: Advanced packaging technologies allow for heterogeneous integration, optimizing performance and power efficiency. The flexibility to combine different IP blocks enables customized solutions for various DSP applications. Weaknesses: Complexity in design and manufacturing may lead to higher costs. Thermal management in densely packed chiplets can be challenging.

Texas Instruments Incorporated

Technical Solution: Texas Instruments (TI) approaches Chiplet-based DSP systems by leveraging their extensive experience in DSP technology and mixed-signal integration. While TI has not explicitly marketed chiplet-based products, their system-on-chip (SoC) designs for DSP applications incorporate principles that align with chiplet philosophy. TI's DSP cores, such as the C66x series, are often integrated with ARM cores and other specialized accelerators in a single package, resembling a chiplet-like approach. For revolutionary DSP systems, TI is likely exploring advanced packaging technologies to enable more modular and scalable designs. Their expertise in analog and mixed-signal processing allows them to potentially create chiplet-based systems that tightly integrate high-performance ADCs and DACs with digital processing elements. TI's mmWave sensors for automotive and industrial applications demonstrate their capability to integrate complex RF front-ends with powerful DSP backends, which could be further enhanced through chiplet-based designs[9]. Additionally, TI's focus on edge AI and IoT applications is driving the development of more flexible and power-efficient DSP solutions that could benefit from chiplet architecture[10].

Strengths: Deep expertise in DSP technology and mixed-signal integration. Strong presence in automotive and industrial markets provides valuable application insights. Weaknesses: Conservative approach to adopting new packaging technologies may result in slower adoption of full chiplet-based designs compared to some competitors.

Key Chiplet Patents

Technologies for a unified test and debug architecture

PatentWO2024205614A1

Innovation

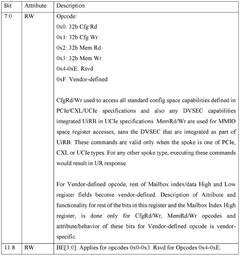

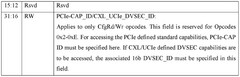

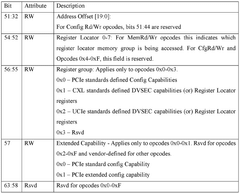

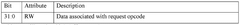

- A unified test and debug architecture is implemented using an external hardware debug interface that is interface-agnostic, employing Universal Chiplet Interconnect Express (UCIe) packets for debug messages, allowing for seamless communication and interoperability between chiplets, and enabling testing at various stages from sort stage to infield debugging.

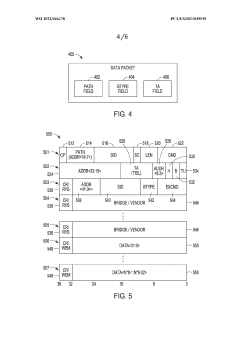

Ordered delivery of data packets based on type of path information in each packet

PatentWO2022046278A1

Innovation

- Incorporating a bridge-type field in data packets to indicate the type of path information, allowing for both address-based and transaction identifier-based ordering, enabling the network to support multiple use cases and bridge between different standards or protocols.

Chiplet Standards

Chiplet standards play a crucial role in enabling the widespread adoption and interoperability of chiplet-based designs for revolutionary digital signal processing (DSP) systems. These standards define the protocols, interfaces, and specifications that allow different chiplets to communicate and work together seamlessly within a single package.

One of the most prominent chiplet standards is the Universal Chiplet Interconnect Express (UCIe), which provides a standardized die-to-die interconnect protocol. UCIe enables high-bandwidth, low-latency communication between chiplets, making it particularly suitable for DSP applications that require intensive data processing and transfer. The standard supports both parallel and serial interfaces, offering flexibility for various DSP system architectures.

Another important standard is the Advanced Interface Bus (AIB), developed by Intel. AIB focuses on providing a high-speed, low-power interface for chiplet-to-chiplet communication. This standard is particularly beneficial for DSP systems that require energy-efficient operation while maintaining high performance.

The Open Compute Project (OCP) has also contributed to chiplet standardization efforts through its Open Domain-Specific Architecture (ODSA) subproject. ODSA aims to create an open chiplet ecosystem, defining standards for chiplet interfaces, packaging, and testing. These standards are crucial for ensuring interoperability between chiplets from different vendors, fostering innovation in DSP system design.

Chiplet standards also address the challenges of thermal management and power delivery in multi-chiplet systems. The Heterogeneous Integration Roadmap (HIR), supported by IEEE, SEMI, and other industry organizations, provides guidelines for thermal and power management in chiplet-based designs. These standards are essential for ensuring the reliability and performance of complex DSP systems that may incorporate multiple high-performance chiplets.

As DSP systems become more sophisticated, chiplet standards are evolving to support emerging technologies. For instance, standards for optical interconnects between chiplets are being developed to enable even higher bandwidth and lower latency communication. These advancements will be crucial for next-generation DSP applications in areas such as 5G/6G communications, artificial intelligence, and high-performance computing.

The adoption of chiplet standards in DSP systems offers numerous benefits, including reduced development costs, increased design flexibility, and improved time-to-market. By leveraging standardized interfaces and protocols, system designers can mix and match chiplets from different vendors to create customized DSP solutions that meet specific performance, power, and cost requirements.

One of the most prominent chiplet standards is the Universal Chiplet Interconnect Express (UCIe), which provides a standardized die-to-die interconnect protocol. UCIe enables high-bandwidth, low-latency communication between chiplets, making it particularly suitable for DSP applications that require intensive data processing and transfer. The standard supports both parallel and serial interfaces, offering flexibility for various DSP system architectures.

Another important standard is the Advanced Interface Bus (AIB), developed by Intel. AIB focuses on providing a high-speed, low-power interface for chiplet-to-chiplet communication. This standard is particularly beneficial for DSP systems that require energy-efficient operation while maintaining high performance.

The Open Compute Project (OCP) has also contributed to chiplet standardization efforts through its Open Domain-Specific Architecture (ODSA) subproject. ODSA aims to create an open chiplet ecosystem, defining standards for chiplet interfaces, packaging, and testing. These standards are crucial for ensuring interoperability between chiplets from different vendors, fostering innovation in DSP system design.

Chiplet standards also address the challenges of thermal management and power delivery in multi-chiplet systems. The Heterogeneous Integration Roadmap (HIR), supported by IEEE, SEMI, and other industry organizations, provides guidelines for thermal and power management in chiplet-based designs. These standards are essential for ensuring the reliability and performance of complex DSP systems that may incorporate multiple high-performance chiplets.

As DSP systems become more sophisticated, chiplet standards are evolving to support emerging technologies. For instance, standards for optical interconnects between chiplets are being developed to enable even higher bandwidth and lower latency communication. These advancements will be crucial for next-generation DSP applications in areas such as 5G/6G communications, artificial intelligence, and high-performance computing.

The adoption of chiplet standards in DSP systems offers numerous benefits, including reduced development costs, increased design flexibility, and improved time-to-market. By leveraging standardized interfaces and protocols, system designers can mix and match chiplets from different vendors to create customized DSP solutions that meet specific performance, power, and cost requirements.

Power Efficiency

Power efficiency is a critical aspect of Chiplet-based Digital Signal Processing (DSP) systems, offering significant advantages over traditional monolithic designs. The modular nature of Chiplets allows for optimized power distribution and management across different functional units. By segregating high-performance and low-power components, designers can implement targeted power-saving strategies for each Chiplet, resulting in overall system efficiency improvements.

One of the key benefits of Chiplet architecture in DSP systems is the ability to utilize different process nodes for various components. This heterogeneous integration enables the use of advanced, power-efficient nodes for critical DSP cores while employing mature, cost-effective nodes for less demanding functions. Such an approach not only optimizes power consumption but also balances performance and cost considerations.

Chiplet-based designs also facilitate more effective power gating techniques. Individual Chiplets can be selectively powered down when not in use, significantly reducing static power consumption. This granular control over power states is particularly beneficial in DSP systems with varying workloads, where certain processing elements may be idle during specific operational modes.

The interconnect technology used in Chiplet designs plays a crucial role in power efficiency. Advanced packaging technologies, such as 2.5D and 3D integration, enable shorter interconnects between Chiplets, reducing signal transmission distances and associated power losses. These packaging solutions also allow for more efficient thermal management, which is essential for maintaining optimal power efficiency under high-performance conditions.

Moreover, Chiplet architectures provide greater flexibility in implementing dynamic voltage and frequency scaling (DVFS) strategies. Each Chiplet can operate at its optimal voltage and frequency point, allowing for fine-tuned power management based on workload demands. This level of control is particularly advantageous in DSP systems that handle diverse signal processing tasks with varying computational intensities.

The modular nature of Chiplets also supports easier integration of specialized accelerators for specific DSP functions. These purpose-built accelerators can significantly improve energy efficiency for targeted operations compared to general-purpose processors. By incorporating such accelerators as separate Chiplets, designers can enhance overall system power efficiency without compromising flexibility or scalability.

One of the key benefits of Chiplet architecture in DSP systems is the ability to utilize different process nodes for various components. This heterogeneous integration enables the use of advanced, power-efficient nodes for critical DSP cores while employing mature, cost-effective nodes for less demanding functions. Such an approach not only optimizes power consumption but also balances performance and cost considerations.

Chiplet-based designs also facilitate more effective power gating techniques. Individual Chiplets can be selectively powered down when not in use, significantly reducing static power consumption. This granular control over power states is particularly beneficial in DSP systems with varying workloads, where certain processing elements may be idle during specific operational modes.

The interconnect technology used in Chiplet designs plays a crucial role in power efficiency. Advanced packaging technologies, such as 2.5D and 3D integration, enable shorter interconnects between Chiplets, reducing signal transmission distances and associated power losses. These packaging solutions also allow for more efficient thermal management, which is essential for maintaining optimal power efficiency under high-performance conditions.

Moreover, Chiplet architectures provide greater flexibility in implementing dynamic voltage and frequency scaling (DVFS) strategies. Each Chiplet can operate at its optimal voltage and frequency point, allowing for fine-tuned power management based on workload demands. This level of control is particularly advantageous in DSP systems that handle diverse signal processing tasks with varying computational intensities.

The modular nature of Chiplets also supports easier integration of specialized accelerators for specific DSP functions. These purpose-built accelerators can significantly improve energy efficiency for targeted operations compared to general-purpose processors. By incorporating such accelerators as separate Chiplets, designers can enhance overall system power efficiency without compromising flexibility or scalability.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!