How to Enhance Chiplet Reliability in Harsh Environments?

JUL 16, 202510 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Reliability Challenges and Objectives

Chiplet technology has emerged as a promising solution to address the challenges of traditional monolithic chip designs, offering improved performance, scalability, and cost-effectiveness. However, as chiplets find applications in increasingly demanding environments, ensuring their reliability becomes paramount. Harsh environments, characterized by extreme temperatures, radiation, vibration, and electromagnetic interference, pose significant challenges to chiplet performance and longevity.

The primary objective of enhancing chiplet reliability in harsh environments is to develop robust solutions that maintain optimal functionality and extend the operational lifespan of chiplet-based systems under adverse conditions. This goal encompasses several key aspects, including thermal management, radiation hardening, mechanical stability, and electromagnetic compatibility.

One of the critical challenges in harsh environments is thermal stress. Extreme temperature fluctuations can lead to thermal expansion and contraction, potentially causing mechanical failures at the interconnects between chiplets or between chiplets and the interposer. Additionally, prolonged exposure to high temperatures can accelerate various degradation mechanisms, such as electromigration and time-dependent dielectric breakdown, compromising the overall reliability of the system.

Radiation effects present another significant challenge, particularly in aerospace and nuclear applications. High-energy particles can cause single-event upsets, latchups, or even permanent damage to the chiplets. Developing effective radiation-hardening techniques without sacrificing performance or increasing costs is a key objective in enhancing chiplet reliability for these environments.

Mechanical stress from vibration and shock is also a critical concern, especially in automotive and industrial applications. The interconnects between chiplets and the substrate are particularly vulnerable to fatigue and failure under repeated mechanical stress. Ensuring robust mechanical connections while maintaining electrical performance is essential for long-term reliability.

Electromagnetic interference (EMI) poses challenges in maintaining signal integrity and preventing cross-talk between chiplets. In harsh environments with high levels of electromagnetic radiation, effective shielding and signal isolation techniques are crucial to ensure reliable operation and prevent data corruption or system malfunctions.

To address these challenges, the objectives of enhancing chiplet reliability in harsh environments include developing advanced packaging materials and techniques, implementing innovative thermal management solutions, designing radiation-hardened architectures, and creating robust testing and qualification methodologies. These efforts aim to push the boundaries of chiplet technology, enabling its deployment in critical applications where reliability is paramount, such as aerospace, defense, automotive, and industrial sectors.

The primary objective of enhancing chiplet reliability in harsh environments is to develop robust solutions that maintain optimal functionality and extend the operational lifespan of chiplet-based systems under adverse conditions. This goal encompasses several key aspects, including thermal management, radiation hardening, mechanical stability, and electromagnetic compatibility.

One of the critical challenges in harsh environments is thermal stress. Extreme temperature fluctuations can lead to thermal expansion and contraction, potentially causing mechanical failures at the interconnects between chiplets or between chiplets and the interposer. Additionally, prolonged exposure to high temperatures can accelerate various degradation mechanisms, such as electromigration and time-dependent dielectric breakdown, compromising the overall reliability of the system.

Radiation effects present another significant challenge, particularly in aerospace and nuclear applications. High-energy particles can cause single-event upsets, latchups, or even permanent damage to the chiplets. Developing effective radiation-hardening techniques without sacrificing performance or increasing costs is a key objective in enhancing chiplet reliability for these environments.

Mechanical stress from vibration and shock is also a critical concern, especially in automotive and industrial applications. The interconnects between chiplets and the substrate are particularly vulnerable to fatigue and failure under repeated mechanical stress. Ensuring robust mechanical connections while maintaining electrical performance is essential for long-term reliability.

Electromagnetic interference (EMI) poses challenges in maintaining signal integrity and preventing cross-talk between chiplets. In harsh environments with high levels of electromagnetic radiation, effective shielding and signal isolation techniques are crucial to ensure reliable operation and prevent data corruption or system malfunctions.

To address these challenges, the objectives of enhancing chiplet reliability in harsh environments include developing advanced packaging materials and techniques, implementing innovative thermal management solutions, designing radiation-hardened architectures, and creating robust testing and qualification methodologies. These efforts aim to push the boundaries of chiplet technology, enabling its deployment in critical applications where reliability is paramount, such as aerospace, defense, automotive, and industrial sectors.

Market Demand for Robust Chiplets

The market demand for robust chiplets in harsh environments has been steadily increasing across various industries. This growth is primarily driven by the expanding applications of electronic systems in challenging operational conditions, such as aerospace, automotive, industrial automation, and defense sectors. These industries require highly reliable and durable electronic components that can withstand extreme temperatures, vibrations, electromagnetic interference, and other environmental stressors.

In the aerospace industry, there is a growing need for chiplets that can operate reliably in high-altitude and space environments. These applications demand components that can function under extreme temperature fluctuations, radiation exposure, and vacuum conditions. The market for space-grade chiplets is expected to expand as commercial space exploration and satellite deployment activities continue to increase.

The automotive sector represents another significant market for robust chiplets. With the rise of electric vehicles and advanced driver assistance systems (ADAS), there is an increasing demand for chiplets that can operate reliably in harsh automotive environments. These components must withstand high temperatures, vibrations, and electromagnetic interference while maintaining long-term reliability throughout the vehicle's lifespan.

Industrial automation and the Internet of Things (IoT) are also driving the demand for robust chiplets. As manufacturing processes become more automated and interconnected, there is a growing need for reliable electronic components that can operate in challenging industrial environments. These chiplets must be able to withstand exposure to chemicals, dust, moisture, and extreme temperatures while maintaining consistent performance.

The defense sector continues to be a significant consumer of robust chiplets for use in military equipment and systems. These applications require components that can operate reliably in battlefield conditions, including extreme temperatures, shock, and vibration. The demand for ruggedized chiplets in defense applications is expected to remain strong as military technologies continue to advance.

The market for robust chiplets is also being influenced by the broader trend towards miniaturization and increased functionality in electronic devices. As chiplets become smaller and more complex, ensuring their reliability in harsh environments becomes increasingly challenging. This has led to a growing demand for advanced packaging and protection technologies that can enhance the durability of chiplets without compromising their performance or size advantages.

Furthermore, the increasing focus on sustainability and energy efficiency is driving demand for chiplets that can operate reliably in high-temperature environments, reducing the need for energy-intensive cooling systems. This trend is particularly relevant in data centers and high-performance computing applications, where thermal management is a critical concern.

In the aerospace industry, there is a growing need for chiplets that can operate reliably in high-altitude and space environments. These applications demand components that can function under extreme temperature fluctuations, radiation exposure, and vacuum conditions. The market for space-grade chiplets is expected to expand as commercial space exploration and satellite deployment activities continue to increase.

The automotive sector represents another significant market for robust chiplets. With the rise of electric vehicles and advanced driver assistance systems (ADAS), there is an increasing demand for chiplets that can operate reliably in harsh automotive environments. These components must withstand high temperatures, vibrations, and electromagnetic interference while maintaining long-term reliability throughout the vehicle's lifespan.

Industrial automation and the Internet of Things (IoT) are also driving the demand for robust chiplets. As manufacturing processes become more automated and interconnected, there is a growing need for reliable electronic components that can operate in challenging industrial environments. These chiplets must be able to withstand exposure to chemicals, dust, moisture, and extreme temperatures while maintaining consistent performance.

The defense sector continues to be a significant consumer of robust chiplets for use in military equipment and systems. These applications require components that can operate reliably in battlefield conditions, including extreme temperatures, shock, and vibration. The demand for ruggedized chiplets in defense applications is expected to remain strong as military technologies continue to advance.

The market for robust chiplets is also being influenced by the broader trend towards miniaturization and increased functionality in electronic devices. As chiplets become smaller and more complex, ensuring their reliability in harsh environments becomes increasingly challenging. This has led to a growing demand for advanced packaging and protection technologies that can enhance the durability of chiplets without compromising their performance or size advantages.

Furthermore, the increasing focus on sustainability and energy efficiency is driving demand for chiplets that can operate reliably in high-temperature environments, reducing the need for energy-intensive cooling systems. This trend is particularly relevant in data centers and high-performance computing applications, where thermal management is a critical concern.

Current State and Limitations of Chiplet Technology

Chiplet technology has emerged as a promising solution to address the challenges of traditional monolithic chip design, offering improved scalability, flexibility, and cost-effectiveness. However, the current state of chiplet technology still faces several limitations, particularly when it comes to ensuring reliability in harsh environments.

One of the primary challenges is the interconnect reliability between chiplets. While advanced packaging technologies like 2.5D and 3D integration have enabled high-bandwidth, low-latency communication between chiplets, these interconnects are susceptible to thermal and mechanical stresses. In harsh environments, such as those with extreme temperatures or high vibration levels, the reliability of these interconnects can be compromised, leading to signal integrity issues and potential system failures.

Thermal management remains a significant concern for chiplet-based systems. The heterogeneous nature of chiplets, often combining different process nodes and functionalities, can lead to uneven heat distribution across the package. This thermal imbalance can cause hotspots and thermal gradients, which are exacerbated in harsh environments. Current cooling solutions may struggle to maintain optimal operating temperatures for all chiplets simultaneously, potentially impacting performance and long-term reliability.

Power distribution and management across chiplets present another limitation. As chiplets become more complex and power-hungry, ensuring efficient and stable power delivery to each component becomes increasingly challenging. In harsh environments, power fluctuations or electromagnetic interference can further complicate this issue, potentially leading to voltage drops or noise that affect chiplet performance and reliability.

The integration of chiplets from different vendors or manufacturing processes introduces additional complexities in terms of testing and validation. While standards like UCIe (Universal Chiplet Interconnect Express) aim to improve interoperability, ensuring consistent performance and reliability across heterogeneous chiplets remains a challenge. This is particularly true when considering the diverse range of environmental conditions that may be encountered in harsh environments.

Material selection and packaging technologies for chiplet-based systems also face limitations in harsh environments. Current materials used for substrates, interposers, and encapsulation may not provide sufficient protection against extreme temperatures, corrosive atmospheres, or radiation exposure. Developing materials and packaging solutions that can withstand these conditions while maintaining the necessary electrical and thermal properties is an ongoing area of research.

Lastly, the current state of chiplet technology is limited by the lack of comprehensive modeling and simulation tools that can accurately predict system behavior in harsh environments. While existing tools can model individual chiplets or specific aspects of multi-chip systems, there is a need for integrated simulation platforms that can account for the complex interactions between chiplets, packaging, and environmental factors to ensure reliable operation under extreme conditions.

One of the primary challenges is the interconnect reliability between chiplets. While advanced packaging technologies like 2.5D and 3D integration have enabled high-bandwidth, low-latency communication between chiplets, these interconnects are susceptible to thermal and mechanical stresses. In harsh environments, such as those with extreme temperatures or high vibration levels, the reliability of these interconnects can be compromised, leading to signal integrity issues and potential system failures.

Thermal management remains a significant concern for chiplet-based systems. The heterogeneous nature of chiplets, often combining different process nodes and functionalities, can lead to uneven heat distribution across the package. This thermal imbalance can cause hotspots and thermal gradients, which are exacerbated in harsh environments. Current cooling solutions may struggle to maintain optimal operating temperatures for all chiplets simultaneously, potentially impacting performance and long-term reliability.

Power distribution and management across chiplets present another limitation. As chiplets become more complex and power-hungry, ensuring efficient and stable power delivery to each component becomes increasingly challenging. In harsh environments, power fluctuations or electromagnetic interference can further complicate this issue, potentially leading to voltage drops or noise that affect chiplet performance and reliability.

The integration of chiplets from different vendors or manufacturing processes introduces additional complexities in terms of testing and validation. While standards like UCIe (Universal Chiplet Interconnect Express) aim to improve interoperability, ensuring consistent performance and reliability across heterogeneous chiplets remains a challenge. This is particularly true when considering the diverse range of environmental conditions that may be encountered in harsh environments.

Material selection and packaging technologies for chiplet-based systems also face limitations in harsh environments. Current materials used for substrates, interposers, and encapsulation may not provide sufficient protection against extreme temperatures, corrosive atmospheres, or radiation exposure. Developing materials and packaging solutions that can withstand these conditions while maintaining the necessary electrical and thermal properties is an ongoing area of research.

Lastly, the current state of chiplet technology is limited by the lack of comprehensive modeling and simulation tools that can accurately predict system behavior in harsh environments. While existing tools can model individual chiplets or specific aspects of multi-chip systems, there is a need for integrated simulation platforms that can account for the complex interactions between chiplets, packaging, and environmental factors to ensure reliable operation under extreme conditions.

Existing Harsh Environment Protection Strategies

01 Thermal management for chiplet reliability

Effective thermal management is crucial for ensuring chiplet reliability. This involves implementing advanced cooling solutions, optimizing heat dissipation pathways, and using materials with superior thermal conductivity. Proper thermal management helps prevent overheating, reduces thermal stress, and extends the lifespan of chiplets in high-performance computing applications.- Thermal management for chiplet reliability: Effective thermal management is crucial for ensuring chiplet reliability. This involves implementing advanced cooling solutions, optimizing heat dissipation pathways, and using materials with superior thermal conductivity. Proper thermal management helps prevent overheating, reduces thermal stress, and extends the lifespan of chiplets in high-performance computing applications.

- Interconnect design for improved chiplet reliability: Robust interconnect design is essential for enhancing chiplet reliability. This includes developing advanced packaging technologies, optimizing signal integrity, and implementing redundant connections. Improved interconnect designs help reduce signal degradation, minimize electrical failures, and enhance overall system performance in multi-chiplet architectures.

- Fault tolerance and error correction in chiplet systems: Implementing fault tolerance mechanisms and error correction techniques is crucial for maintaining chiplet reliability. This involves developing advanced error detection and correction algorithms, implementing redundancy schemes, and designing self-healing capabilities. These approaches help mitigate the impact of manufacturing defects, transient faults, and aging-related issues in chiplet-based systems.

- Power management strategies for chiplet reliability: Effective power management is essential for ensuring chiplet reliability in complex systems. This includes implementing dynamic voltage and frequency scaling, power gating techniques, and intelligent power distribution. Advanced power management strategies help reduce power consumption, minimize heat generation, and improve the overall reliability and lifespan of chiplet-based architectures.

- Testing and validation methodologies for chiplet reliability: Comprehensive testing and validation methodologies are crucial for ensuring chiplet reliability throughout the product lifecycle. This involves developing advanced test patterns, implementing built-in self-test mechanisms, and utilizing machine learning-based predictive maintenance techniques. Robust testing and validation approaches help identify potential failure modes, improve yield rates, and enhance the overall reliability of chiplet-based systems.

02 Interconnect design for improved chiplet reliability

Robust interconnect design is essential for enhancing chiplet reliability. This includes developing advanced packaging technologies, optimizing signal integrity, and implementing redundant connections. Improved interconnect designs help reduce signal degradation, minimize electrical failures, and enhance overall system performance in multi-chiplet architectures.Expand Specific Solutions03 Testing and fault tolerance mechanisms for chiplets

Implementing comprehensive testing protocols and fault tolerance mechanisms is critical for ensuring chiplet reliability. This involves developing advanced built-in self-test (BIST) capabilities, error detection and correction techniques, and redundancy schemes. These approaches help identify and mitigate potential failures, improving the overall reliability and yield of chiplet-based systems.Expand Specific Solutions04 Power management strategies for chiplet reliability

Effective power management is crucial for maintaining chiplet reliability. This includes implementing dynamic voltage and frequency scaling, power gating techniques, and intelligent power distribution across chiplets. Advanced power management strategies help reduce power consumption, minimize heat generation, and improve the overall reliability and lifespan of chiplet-based systems.Expand Specific Solutions05 Materials and manufacturing processes for enhanced chiplet reliability

Developing advanced materials and refining manufacturing processes are key to improving chiplet reliability. This involves using novel substrate materials, implementing precise die-to-die bonding techniques, and optimizing chip-package interactions. These advancements help reduce manufacturing defects, improve thermal performance, and enhance the overall reliability of chiplet-based systems in various applications.Expand Specific Solutions

Key Players in Chiplet Manufacturing

The chiplet reliability enhancement market in harsh environments is in a growth phase, driven by increasing demand for robust semiconductor solutions across industries. The market size is expanding as more sectors adopt chiplet technology for high-performance applications. Technologically, the field is advancing rapidly, with companies like Samsung Electronics, Intel, and Micron Technology leading innovation. These firms are developing advanced packaging techniques, thermal management solutions, and radiation-hardened designs to improve chiplet reliability. Other players such as Infineon Technologies and NXP are also contributing significantly to the field, focusing on automotive and industrial applications where harsh environment performance is critical. The competitive landscape is characterized by a mix of established semiconductor giants and specialized firms, all striving to address the unique challenges of chiplet reliability in extreme conditions.

Samsung Electronics Co., Ltd.

Technical Solution: Samsung has developed advanced packaging technologies to enhance chiplet reliability in harsh environments. Their approach includes the use of through-silicon vias (TSVs) and interposers for improved thermal management and signal integrity[1]. They have also implemented advanced materials such as low-k dielectrics and copper pillars to enhance interconnect reliability[2]. Samsung's 3D packaging technology, X-Cube, utilizes a hybrid bonding process that enables ultra-fine pitch connections between chiplets, improving overall system performance and reliability[3]. Additionally, they have introduced a moisture-resistant packaging solution that incorporates a special coating to protect chiplets from humidity and corrosion in challenging environments[4].

Strengths: Advanced 3D packaging technology, expertise in materials science, and comprehensive approach to thermal management. Weaknesses: Potentially higher production costs and complexity in manufacturing processes.

Infineon Technologies AG

Technical Solution: Infineon has developed a range of solutions to enhance chiplet reliability in harsh environments, particularly for automotive and industrial applications. Their HybridPACK™ power module platform incorporates advanced thermal management and interconnect technologies to improve reliability under extreme conditions[1]. Infineon's chip-embedding technology, known as Embedded Wafer Level Ball Grid Array (eWLB), enables the integration of multiple chiplets in a compact, robust package suitable for harsh environments[2]. They have also implemented advanced materials and coatings to protect chiplets from moisture, corrosion, and mechanical stress[3]. Infineon's automotive-qualified chiplets undergo rigorous testing and qualification procedures to ensure reliability in extreme temperature and vibration conditions[4].

Strengths: Strong focus on automotive and industrial applications, advanced power module technologies, and extensive experience in harsh environment qualifications. Weaknesses: Potential limitations in addressing high-performance computing applications.

Core Innovations in Chiplet Reliability

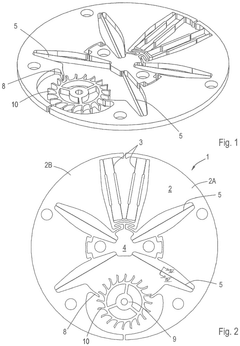

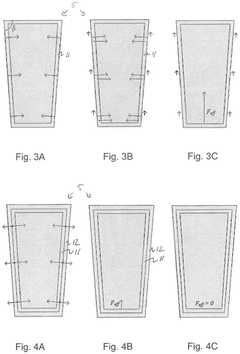

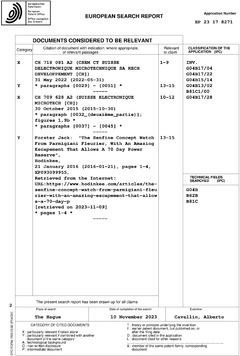

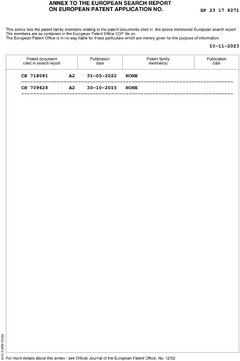

Component, such as an oscillator, for a movement for a watch

PatentPendingEP4474921A1

Innovation

- Applying a layer that exerts a stress, either compressive or tensile, on the brittle material to reduce stress concentration and temperature sensitivity, with the stress from the additional layer being opposite to the initial layer, thereby minimizing the overall stress and improving the reliability of horological parts.

Environmental Impact of Chiplet Manufacturing

The environmental impact of chiplet manufacturing is a critical consideration in the pursuit of enhancing chiplet reliability in harsh environments. As the demand for more powerful and efficient computing solutions grows, the chiplet approach has gained traction due to its potential for improved performance and cost-effectiveness. However, this manufacturing process also raises concerns about its ecological footprint.

Chiplet production involves the creation of smaller, specialized silicon dies that are later integrated into a larger package. This modular approach allows for greater flexibility and customization but may lead to increased resource consumption and waste generation. The manufacturing of chiplets requires sophisticated cleanroom environments, which demand significant energy inputs for maintaining precise temperature and humidity controls. Additionally, the use of specialized chemicals and materials in the fabrication process can contribute to air and water pollution if not properly managed.

Water usage is another significant environmental factor in chiplet manufacturing. The production of semiconductors, including chiplets, requires large volumes of ultra-pure water for cleaning and processing. This intensive water consumption can strain local water resources, particularly in regions already facing water scarcity issues. Furthermore, the wastewater generated from these processes often contains trace amounts of chemicals and metals, necessitating complex treatment systems to prevent environmental contamination.

The energy-intensive nature of chiplet manufacturing also contributes to its environmental impact. The operation of high-precision equipment, such as lithography machines and etching tools, consumes substantial amounts of electricity. This energy demand often translates to increased carbon emissions, depending on the energy sources used by the manufacturing facilities. As the industry strives for smaller and more complex chiplet designs, the energy requirements for production may continue to rise.

Electronic waste (e-waste) is another environmental concern associated with chiplet manufacturing. While chiplets themselves are small, the overall increase in electronic device production and shorter product lifecycles contribute to the growing e-waste problem. Proper recycling and disposal of chiplets and the devices they are integrated into are essential to mitigate this impact. However, the complex nature of chiplet packages can make recycling more challenging, potentially leading to increased landfill waste or improper disposal.

To address these environmental challenges, the semiconductor industry is exploring various sustainability initiatives. These include implementing more efficient manufacturing processes, adopting renewable energy sources, improving water recycling systems, and developing eco-friendly packaging materials. Additionally, research into biodegradable substrates and recyclable chiplet designs is ongoing, aiming to reduce the long-term environmental impact of these advanced computing components.

Chiplet production involves the creation of smaller, specialized silicon dies that are later integrated into a larger package. This modular approach allows for greater flexibility and customization but may lead to increased resource consumption and waste generation. The manufacturing of chiplets requires sophisticated cleanroom environments, which demand significant energy inputs for maintaining precise temperature and humidity controls. Additionally, the use of specialized chemicals and materials in the fabrication process can contribute to air and water pollution if not properly managed.

Water usage is another significant environmental factor in chiplet manufacturing. The production of semiconductors, including chiplets, requires large volumes of ultra-pure water for cleaning and processing. This intensive water consumption can strain local water resources, particularly in regions already facing water scarcity issues. Furthermore, the wastewater generated from these processes often contains trace amounts of chemicals and metals, necessitating complex treatment systems to prevent environmental contamination.

The energy-intensive nature of chiplet manufacturing also contributes to its environmental impact. The operation of high-precision equipment, such as lithography machines and etching tools, consumes substantial amounts of electricity. This energy demand often translates to increased carbon emissions, depending on the energy sources used by the manufacturing facilities. As the industry strives for smaller and more complex chiplet designs, the energy requirements for production may continue to rise.

Electronic waste (e-waste) is another environmental concern associated with chiplet manufacturing. While chiplets themselves are small, the overall increase in electronic device production and shorter product lifecycles contribute to the growing e-waste problem. Proper recycling and disposal of chiplets and the devices they are integrated into are essential to mitigate this impact. However, the complex nature of chiplet packages can make recycling more challenging, potentially leading to increased landfill waste or improper disposal.

To address these environmental challenges, the semiconductor industry is exploring various sustainability initiatives. These include implementing more efficient manufacturing processes, adopting renewable energy sources, improving water recycling systems, and developing eco-friendly packaging materials. Additionally, research into biodegradable substrates and recyclable chiplet designs is ongoing, aiming to reduce the long-term environmental impact of these advanced computing components.

Standardization Efforts in Chiplet Industry

Standardization efforts in the chiplet industry have become increasingly crucial as the technology gains traction in harsh environment applications. These efforts aim to establish common protocols, interfaces, and design methodologies to ensure interoperability and reliability across different chiplet implementations.

One of the primary standardization initiatives is the Universal Chiplet Interconnect Express (UCIe), which focuses on creating a unified interconnect standard for chiplets. UCIe addresses the need for high-speed, low-latency communication between chiplets, which is essential for maintaining reliability in harsh environments. The standard encompasses physical layer specifications, protocol layer definitions, and software stack recommendations, providing a comprehensive framework for chiplet integration.

Another significant standardization effort is the Advanced Interface Bus (AIB) consortium, which aims to develop an open-source interconnect standard for chiplets. AIB focuses on creating a flexible and scalable interface that can adapt to various chiplet configurations and performance requirements. This adaptability is particularly valuable for harsh environment applications, where chiplets may need to operate under diverse conditions.

The JEDEC Solid State Technology Association has also been actively involved in chiplet standardization, particularly in the development of the Chiplet Physical Interface (CPI) standard. CPI addresses the mechanical and electrical aspects of chiplet integration, including thermal management and power delivery, which are critical factors in enhancing reliability in harsh environments.

In addition to these industry-wide initiatives, several companies are working on their own chiplet standards and ecosystems. For instance, Intel's Embedded Multi-die Interconnect Bridge (EMIB) and AMD's Infinity Fabric technologies represent proprietary approaches to chiplet integration. While these solutions may offer optimized performance for specific applications, the industry is gradually moving towards more open and interoperable standards to foster innovation and reduce development costs.

Standardization efforts also extend to testing and qualification methodologies for chiplets in harsh environments. Organizations such as SEMI and IEEE are developing guidelines and standards for assessing chiplet reliability under extreme conditions, including temperature cycling, vibration, and electromagnetic interference. These standards aim to provide a consistent framework for evaluating chiplet performance and durability in challenging operational scenarios.

As the chiplet industry continues to evolve, collaboration between semiconductor manufacturers, system integrators, and standards bodies will be crucial in establishing robust and widely adopted standards. These efforts will not only enhance chiplet reliability in harsh environments but also accelerate the adoption of chiplet technology across various industries, from aerospace and defense to automotive and industrial applications.

One of the primary standardization initiatives is the Universal Chiplet Interconnect Express (UCIe), which focuses on creating a unified interconnect standard for chiplets. UCIe addresses the need for high-speed, low-latency communication between chiplets, which is essential for maintaining reliability in harsh environments. The standard encompasses physical layer specifications, protocol layer definitions, and software stack recommendations, providing a comprehensive framework for chiplet integration.

Another significant standardization effort is the Advanced Interface Bus (AIB) consortium, which aims to develop an open-source interconnect standard for chiplets. AIB focuses on creating a flexible and scalable interface that can adapt to various chiplet configurations and performance requirements. This adaptability is particularly valuable for harsh environment applications, where chiplets may need to operate under diverse conditions.

The JEDEC Solid State Technology Association has also been actively involved in chiplet standardization, particularly in the development of the Chiplet Physical Interface (CPI) standard. CPI addresses the mechanical and electrical aspects of chiplet integration, including thermal management and power delivery, which are critical factors in enhancing reliability in harsh environments.

In addition to these industry-wide initiatives, several companies are working on their own chiplet standards and ecosystems. For instance, Intel's Embedded Multi-die Interconnect Bridge (EMIB) and AMD's Infinity Fabric technologies represent proprietary approaches to chiplet integration. While these solutions may offer optimized performance for specific applications, the industry is gradually moving towards more open and interoperable standards to foster innovation and reduce development costs.

Standardization efforts also extend to testing and qualification methodologies for chiplets in harsh environments. Organizations such as SEMI and IEEE are developing guidelines and standards for assessing chiplet reliability under extreme conditions, including temperature cycling, vibration, and electromagnetic interference. These standards aim to provide a consistent framework for evaluating chiplet performance and durability in challenging operational scenarios.

As the chiplet industry continues to evolve, collaboration between semiconductor manufacturers, system integrators, and standards bodies will be crucial in establishing robust and widely adopted standards. These efforts will not only enhance chiplet reliability in harsh environments but also accelerate the adoption of chiplet technology across various industries, from aerospace and defense to automotive and industrial applications.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!