How to Ensure Chiplet-Based Systems Meet Industry Quality Standards?

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Technology Evolution and Objectives

Chiplet technology has emerged as a revolutionary approach in semiconductor design and manufacturing, offering a paradigm shift from traditional monolithic chip designs. The evolution of chiplet technology can be traced back to the early 2010s when the semiconductor industry began facing challenges in scaling monolithic chips due to physical limitations and increasing costs. The primary objective of chiplet technology is to overcome these limitations by disaggregating complex system-on-chip (SoC) designs into smaller, more manageable components called chiplets.

The development of chiplet technology has been driven by several key factors. First, the slowdown of Moore's Law has pushed the industry to explore alternative approaches to improve performance and efficiency. Chiplets allow for the integration of different process nodes and technologies within a single package, enabling optimal performance and cost-effectiveness. Second, the increasing demand for specialized computing solutions in areas such as artificial intelligence, high-performance computing, and edge computing has necessitated more flexible and modular chip designs.

Throughout its evolution, chiplet technology has seen significant advancements in interconnect technologies, packaging methods, and design methodologies. The introduction of advanced packaging technologies like 2.5D and 3D integration has been crucial in enabling efficient chiplet-based systems. These technologies allow for high-bandwidth, low-latency communication between chiplets, addressing one of the primary challenges in chiplet integration.

The objectives of chiplet technology extend beyond merely overcoming scaling limitations. They include improving yield rates, reducing time-to-market for new products, enhancing design flexibility, and enabling more cost-effective manufacturing processes. By allowing different components of a system to be manufactured separately and then integrated, chiplet technology offers the potential for significant cost savings and improved performance across a wide range of applications.

As the technology continues to mature, ensuring that chiplet-based systems meet industry quality standards has become a critical objective. This involves developing standardized interfaces, improving testing methodologies for multi-chiplet systems, and establishing robust quality assurance processes throughout the design, manufacturing, and integration stages. The industry is working towards creating open standards and ecosystems that will facilitate wider adoption and interoperability of chiplet-based solutions.

Looking ahead, the evolution of chiplet technology is expected to play a pivotal role in shaping the future of semiconductor design and manufacturing. As the technology progresses, objectives will likely expand to include further improvements in energy efficiency, thermal management, and system-level optimization. The ultimate goal is to establish chiplet technology as a mainstream approach that can deliver high-performance, cost-effective, and scalable solutions across diverse computing applications.

The development of chiplet technology has been driven by several key factors. First, the slowdown of Moore's Law has pushed the industry to explore alternative approaches to improve performance and efficiency. Chiplets allow for the integration of different process nodes and technologies within a single package, enabling optimal performance and cost-effectiveness. Second, the increasing demand for specialized computing solutions in areas such as artificial intelligence, high-performance computing, and edge computing has necessitated more flexible and modular chip designs.

Throughout its evolution, chiplet technology has seen significant advancements in interconnect technologies, packaging methods, and design methodologies. The introduction of advanced packaging technologies like 2.5D and 3D integration has been crucial in enabling efficient chiplet-based systems. These technologies allow for high-bandwidth, low-latency communication between chiplets, addressing one of the primary challenges in chiplet integration.

The objectives of chiplet technology extend beyond merely overcoming scaling limitations. They include improving yield rates, reducing time-to-market for new products, enhancing design flexibility, and enabling more cost-effective manufacturing processes. By allowing different components of a system to be manufactured separately and then integrated, chiplet technology offers the potential for significant cost savings and improved performance across a wide range of applications.

As the technology continues to mature, ensuring that chiplet-based systems meet industry quality standards has become a critical objective. This involves developing standardized interfaces, improving testing methodologies for multi-chiplet systems, and establishing robust quality assurance processes throughout the design, manufacturing, and integration stages. The industry is working towards creating open standards and ecosystems that will facilitate wider adoption and interoperability of chiplet-based solutions.

Looking ahead, the evolution of chiplet technology is expected to play a pivotal role in shaping the future of semiconductor design and manufacturing. As the technology progresses, objectives will likely expand to include further improvements in energy efficiency, thermal management, and system-level optimization. The ultimate goal is to establish chiplet technology as a mainstream approach that can deliver high-performance, cost-effective, and scalable solutions across diverse computing applications.

Market Demand for Chiplet-Based Systems

The market demand for chiplet-based systems has been steadily growing, driven by the increasing need for high-performance, energy-efficient, and cost-effective computing solutions across various industries. As traditional monolithic chip designs approach their physical limits, chiplet technology offers a promising alternative that allows for more flexible and scalable semiconductor solutions.

In the data center and cloud computing sector, there is a significant demand for chiplet-based systems due to their ability to deliver higher performance and improved power efficiency. Major cloud service providers and enterprise customers are seeking solutions that can handle the exponential growth in data processing requirements while minimizing energy consumption and operational costs.

The telecommunications industry, particularly with the ongoing rollout of 5G networks, is another key driver of chiplet demand. Network infrastructure providers are looking for chiplet-based systems that can offer the necessary processing power and flexibility to support the diverse requirements of 5G applications, from edge computing to core network functions.

In the automotive sector, the shift towards electric vehicles and advanced driver assistance systems (ADAS) is creating a strong market pull for chiplet-based solutions. These systems require high-performance, low-power computing capabilities that can be efficiently integrated into the limited space available in vehicles.

The consumer electronics market is also showing increased interest in chiplet technology. Smartphone manufacturers, in particular, are exploring chiplet-based designs to enhance device performance while managing power consumption and form factor constraints.

High-performance computing (HPC) and artificial intelligence (AI) applications represent another significant market segment for chiplet-based systems. Research institutions, government agencies, and private enterprises are seeking more powerful and efficient computing solutions to tackle complex scientific simulations, data analytics, and AI model training.

The industrial automation sector is gradually adopting chiplet technology to enhance the capabilities of smart manufacturing systems and Internet of Things (IoT) devices. These applications require a combination of high-performance computing, real-time processing, and energy efficiency, which chiplet-based systems can effectively deliver.

As the demand for chiplet-based systems grows across these diverse sectors, there is an increasing emphasis on ensuring that these systems meet industry quality standards. This focus on quality is crucial for maintaining reliability, performance, and interoperability in mission-critical applications and consumer products alike.

In the data center and cloud computing sector, there is a significant demand for chiplet-based systems due to their ability to deliver higher performance and improved power efficiency. Major cloud service providers and enterprise customers are seeking solutions that can handle the exponential growth in data processing requirements while minimizing energy consumption and operational costs.

The telecommunications industry, particularly with the ongoing rollout of 5G networks, is another key driver of chiplet demand. Network infrastructure providers are looking for chiplet-based systems that can offer the necessary processing power and flexibility to support the diverse requirements of 5G applications, from edge computing to core network functions.

In the automotive sector, the shift towards electric vehicles and advanced driver assistance systems (ADAS) is creating a strong market pull for chiplet-based solutions. These systems require high-performance, low-power computing capabilities that can be efficiently integrated into the limited space available in vehicles.

The consumer electronics market is also showing increased interest in chiplet technology. Smartphone manufacturers, in particular, are exploring chiplet-based designs to enhance device performance while managing power consumption and form factor constraints.

High-performance computing (HPC) and artificial intelligence (AI) applications represent another significant market segment for chiplet-based systems. Research institutions, government agencies, and private enterprises are seeking more powerful and efficient computing solutions to tackle complex scientific simulations, data analytics, and AI model training.

The industrial automation sector is gradually adopting chiplet technology to enhance the capabilities of smart manufacturing systems and Internet of Things (IoT) devices. These applications require a combination of high-performance computing, real-time processing, and energy efficiency, which chiplet-based systems can effectively deliver.

As the demand for chiplet-based systems grows across these diverse sectors, there is an increasing emphasis on ensuring that these systems meet industry quality standards. This focus on quality is crucial for maintaining reliability, performance, and interoperability in mission-critical applications and consumer products alike.

Chiplet Quality Challenges and Constraints

The development of chiplet-based systems presents significant challenges in ensuring industry-wide quality standards. One of the primary constraints is the complexity of integrating multiple chiplets from different manufacturers, each potentially using diverse process nodes and design methodologies. This heterogeneity introduces variability in performance, power consumption, and reliability, making it difficult to establish uniform quality metrics across the entire system.

Thermal management emerges as a critical challenge in chiplet-based designs. The dense packaging of multiple chiplets can lead to hotspots and thermal gradients, potentially impacting the overall system reliability and performance. Addressing this issue requires advanced cooling solutions and careful thermal design considerations, which may increase manufacturing costs and complexity.

Signal integrity and power delivery pose additional hurdles in maintaining quality standards. As chiplets communicate through high-speed interconnects, ensuring clean signal transmission becomes crucial. The design of power delivery networks must account for the varying power requirements of different chiplets while minimizing voltage drops and noise. These factors directly influence system stability and performance, necessitating sophisticated design and testing methodologies.

Testing and validation of chiplet-based systems present unique challenges. Traditional testing methods may not be sufficient to detect defects at the chiplet-to-chiplet interface or system-level issues arising from the integration of multiple chiplets. Developing comprehensive test strategies that can effectively identify faults in both individual chiplets and the integrated system is essential for maintaining quality standards.

The lack of standardization in chiplet interfaces and protocols further complicates quality assurance efforts. While initiatives like Universal Chiplet Interconnect Express (UCIe) aim to address this, the industry is still in the early stages of adopting universal standards. This fragmentation makes it challenging to ensure interoperability and consistent performance across chiplets from different vendors.

Yield management in chiplet-based systems introduces another layer of complexity. While chiplets allow for better yield management of individual components, the overall system yield can be impacted by the integration process. Ensuring high-quality connections between chiplets and managing the yield of the entire assembly process becomes critical for maintaining cost-effectiveness and meeting quality standards.

Lastly, the reliability and longevity of chiplet-based systems pose ongoing challenges. With multiple components integrated into a single package, predicting and ensuring the long-term reliability of the entire system becomes more complex. Factors such as thermal cycling, mechanical stress, and electromigration must be carefully considered to meet industry expectations for product lifespan and reliability.

Thermal management emerges as a critical challenge in chiplet-based designs. The dense packaging of multiple chiplets can lead to hotspots and thermal gradients, potentially impacting the overall system reliability and performance. Addressing this issue requires advanced cooling solutions and careful thermal design considerations, which may increase manufacturing costs and complexity.

Signal integrity and power delivery pose additional hurdles in maintaining quality standards. As chiplets communicate through high-speed interconnects, ensuring clean signal transmission becomes crucial. The design of power delivery networks must account for the varying power requirements of different chiplets while minimizing voltage drops and noise. These factors directly influence system stability and performance, necessitating sophisticated design and testing methodologies.

Testing and validation of chiplet-based systems present unique challenges. Traditional testing methods may not be sufficient to detect defects at the chiplet-to-chiplet interface or system-level issues arising from the integration of multiple chiplets. Developing comprehensive test strategies that can effectively identify faults in both individual chiplets and the integrated system is essential for maintaining quality standards.

The lack of standardization in chiplet interfaces and protocols further complicates quality assurance efforts. While initiatives like Universal Chiplet Interconnect Express (UCIe) aim to address this, the industry is still in the early stages of adopting universal standards. This fragmentation makes it challenging to ensure interoperability and consistent performance across chiplets from different vendors.

Yield management in chiplet-based systems introduces another layer of complexity. While chiplets allow for better yield management of individual components, the overall system yield can be impacted by the integration process. Ensuring high-quality connections between chiplets and managing the yield of the entire assembly process becomes critical for maintaining cost-effectiveness and meeting quality standards.

Lastly, the reliability and longevity of chiplet-based systems pose ongoing challenges. With multiple components integrated into a single package, predicting and ensuring the long-term reliability of the entire system becomes more complex. Factors such as thermal cycling, mechanical stress, and electromigration must be carefully considered to meet industry expectations for product lifespan and reliability.

Current Quality Assurance Methods

01 Standardization of chiplet interfaces

Establishing standardized interfaces for chiplets is crucial for ensuring compatibility and interoperability in chiplet-based systems. This includes defining protocols for communication between chiplets, power management, and thermal control. Standardization efforts focus on creating universal interconnect specifications that allow chiplets from different manufacturers to work seamlessly together, improving system flexibility and reducing development costs.- Standardization of chiplet interfaces: Establishing standardized interfaces for chiplets is crucial for ensuring compatibility and interoperability in chiplet-based systems. This includes defining protocols for communication between chiplets, power management, and thermal control. Standardized interfaces enable easier integration of chiplets from different manufacturers and improve overall system reliability.

- Testing and validation methodologies: Developing comprehensive testing and validation methodologies specific to chiplet-based systems is essential for maintaining quality standards. This involves creating test patterns for individual chiplets, as well as system-level testing to ensure proper integration and performance. Advanced testing techniques may include built-in self-test (BIST) capabilities and automated test equipment (ATE) for chiplets.

- Thermal management and power efficiency: Ensuring effective thermal management and power efficiency is critical for chiplet-based systems. This includes developing standards for heat dissipation, power distribution, and energy-efficient designs. Implementing advanced cooling solutions and power management techniques helps maintain system stability and longevity.

- Packaging and integration standards: Establishing standards for packaging and integration of chiplets is crucial for ensuring consistent quality in chiplet-based systems. This includes defining guidelines for die-to-die bonding, substrate materials, and interconnect technologies. Standardized packaging approaches help improve manufacturability, reliability, and yield of chiplet-based systems.

- Quality assurance and reliability metrics: Developing specific quality assurance and reliability metrics for chiplet-based systems is essential for maintaining high standards. This includes establishing benchmarks for system performance, longevity, and fault tolerance. Implementing rigorous quality control processes and reliability testing methodologies helps ensure consistent product quality across different chiplet combinations and manufacturers.

02 Quality assurance in chiplet manufacturing

Implementing rigorous quality control measures in the manufacturing process of chiplets is essential for maintaining high standards in chiplet-based systems. This involves developing advanced testing methodologies, including wafer-level and known-good-die testing, to ensure each chiplet meets performance and reliability requirements before integration. Quality assurance processes also encompass defect detection, yield improvement strategies, and traceability throughout the supply chain.Expand Specific Solutions03 Thermal management and power efficiency standards

Establishing standards for thermal management and power efficiency is critical in chiplet-based systems. This includes developing guidelines for heat dissipation techniques, power distribution across chiplets, and energy-efficient design practices. Standards in this area aim to optimize system performance while minimizing power consumption and ensuring reliable operation under various thermal conditions.Expand Specific Solutions04 Integration and packaging standards for chiplets

Developing standards for chiplet integration and packaging is essential for ensuring consistency and reliability in chiplet-based systems. This includes specifications for advanced packaging technologies, such as 2.5D and 3D integration, interposer design, and through-silicon via (TSV) implementation. These standards aim to improve system performance, reduce form factors, and enhance overall system reliability.Expand Specific Solutions05 Performance and reliability testing standards

Establishing comprehensive standards for performance and reliability testing of chiplet-based systems is crucial for ensuring product quality. This includes developing standardized benchmarking methodologies, stress testing protocols, and long-term reliability assessment techniques. These standards aim to provide consistent evaluation criteria across different chiplet configurations and manufacturers, enabling accurate comparison and validation of system performance and reliability.Expand Specific Solutions

Key Players in Chiplet Ecosystem

The chiplet-based systems market is in a growth phase, driven by increasing demand for high-performance computing and AI applications. The market size is expanding rapidly, with major players like Intel, AMD, and TSMC investing heavily in chiplet technology. Technical maturity varies, with some companies like Intel and AMD already offering commercial products, while others like Micron and IBM are in advanced development stages. The competitive landscape is intensifying as more companies enter the market, including specialized firms like Chipletz and established semiconductor manufacturers. Quality assurance remains a critical challenge, with industry leaders collaborating on standards and testing methodologies to ensure chiplet-based systems meet rigorous performance and reliability requirements.

Intel Corp.

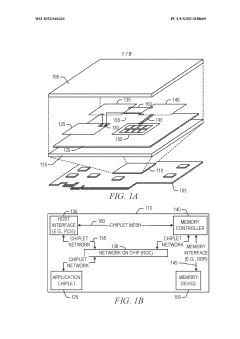

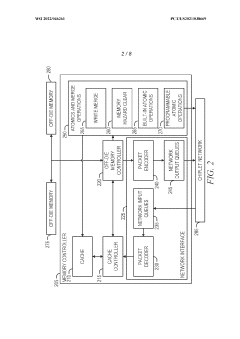

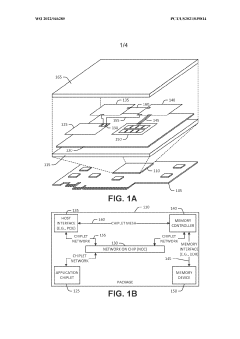

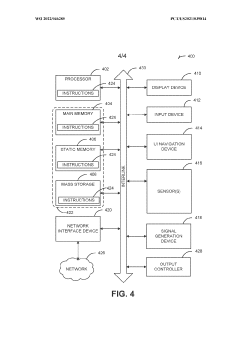

Technical Solution: Intel's approach to ensuring chiplet-based systems meet industry quality standards involves a comprehensive strategy called "Advanced Packaging". This includes their Embedded Multi-die Interconnect Bridge (EMIB) and Foveros 3D packaging technologies. EMIB allows for high-density interconnects between chiplets, while Foveros enables vertical stacking of chips[1]. Intel implements rigorous testing procedures, including Known Good Die (KGD) testing, which ensures each chiplet meets performance and quality standards before integration[2]. They also utilize advanced simulation and modeling tools to predict system-level performance and reliability. Intel's Co-EMIB technology combines EMIB and Foveros, allowing for even more complex chiplet arrangements while maintaining high quality standards[3].

Strengths: Advanced packaging technologies, comprehensive testing procedures, and simulation tools. Weaknesses: Potential for increased complexity in manufacturing and higher costs compared to traditional monolithic designs.

Taiwan Semiconductor Manufacturing Co., Ltd.

Technical Solution: TSMC ensures chiplet-based systems meet industry quality standards through their Integrated Fan-Out (InFO) and System on Integrated Chips (SoIC) technologies. InFO allows for high-density, low-profile packaging of multiple chips, while SoIC enables 3D chip stacking with extremely fine pitch bonding[4]. TSMC implements a stringent quality control process, including wafer-level testing and burn-in procedures to identify potential defects early in the manufacturing process. They also utilize advanced inspection techniques such as scanning acoustic microscopy and X-ray imaging to detect any internal defects in chiplet packages[5]. TSMC's 3DFabric platform integrates various advanced packaging technologies, ensuring a holistic approach to chiplet-based system quality[6].

Strengths: Advanced packaging technologies, comprehensive testing and inspection procedures. Weaknesses: Potential for increased production costs and longer time-to-market for highly complex designs.

Innovative Chiplet Testing Techniques

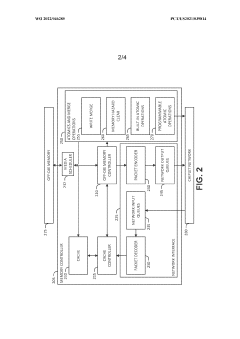

Multiple protocol header processing

PatentWO2022046261A1

Innovation

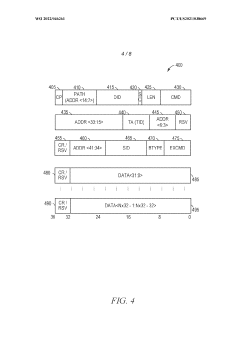

- The implementation of a header processing system that includes a bridge type (BTYPE) field to identify the protocol, allowing for the interpretation of command fields differently based on this field, enabling a single network to carry packets of various protocols without encapsulation, and utilizing a chiplet system with a chiplet protocol interface (CPI) for efficient inter-chiplet communication.

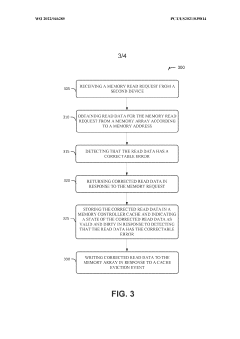

Method of demand scrubbing by placing corrected data in memory-side cache

PatentWO2022046285A1

Innovation

- Implementing a memory controller chiplet with cache management and error correction capabilities that allow for demand scrubbing by storing corrected data in the memory controller cache and writing it back to the storage array during cache eviction events, thereby minimizing the need for additional read-modify-write paths and simplifying data correction.

Industry Standards for Chiplet Systems

Industry standards play a crucial role in ensuring the quality, reliability, and interoperability of chiplet-based systems. These standards are developed and maintained by various organizations, including the IEEE, JEDEC, and OCP, to address the unique challenges posed by chiplet architectures.

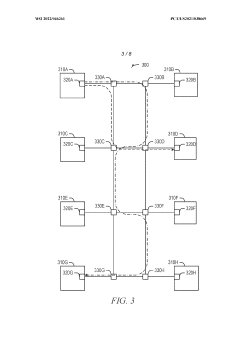

One of the key standards in this domain is the Advanced Interface Bus (AIB) specification, developed by Intel and now managed by the OCP. AIB defines a die-to-die interconnect protocol that enables high-bandwidth, low-latency communication between chiplets. This standard is essential for ensuring seamless integration of chiplets from different vendors within a single package.

JEDEC has also been actively developing standards for chiplet-based systems. The JC-63 Committee on Multichip Packages and Related Technologies is working on specifications for chiplet interfaces, thermal management, and testing methodologies. These standards aim to establish a common framework for chiplet design and integration, facilitating interoperability and reducing time-to-market for chiplet-based products.

The IEEE 2851-2020 standard focuses on the exchange of IP-XACT design data between different tools and design teams. This standard is particularly relevant for chiplet-based systems, as it enables efficient collaboration and data sharing in complex multi-die designs.

Another important standard is the Universal Chiplet Interconnect Express (UCIe), which defines a universal interconnect standard for chiplets. UCIe aims to create an open ecosystem for chiplet-based designs, allowing for mix-and-match of chiplets from different vendors while ensuring compatibility and performance.

In addition to these specific standards, general semiconductor industry standards such as those related to electrostatic discharge (ESD) protection, thermal management, and reliability testing are also applicable to chiplet-based systems. These standards ensure that chiplet designs meet the same rigorous quality and reliability requirements as traditional monolithic ICs.

As chiplet technology continues to evolve, industry standards are expected to adapt and expand to address new challenges. Future standards may focus on areas such as advanced packaging technologies, 3D integration, and system-level optimization for chiplet-based designs. The ongoing collaboration between industry leaders, research institutions, and standards organizations will be crucial in shaping these standards and driving the adoption of chiplet technology across various application domains.

One of the key standards in this domain is the Advanced Interface Bus (AIB) specification, developed by Intel and now managed by the OCP. AIB defines a die-to-die interconnect protocol that enables high-bandwidth, low-latency communication between chiplets. This standard is essential for ensuring seamless integration of chiplets from different vendors within a single package.

JEDEC has also been actively developing standards for chiplet-based systems. The JC-63 Committee on Multichip Packages and Related Technologies is working on specifications for chiplet interfaces, thermal management, and testing methodologies. These standards aim to establish a common framework for chiplet design and integration, facilitating interoperability and reducing time-to-market for chiplet-based products.

The IEEE 2851-2020 standard focuses on the exchange of IP-XACT design data between different tools and design teams. This standard is particularly relevant for chiplet-based systems, as it enables efficient collaboration and data sharing in complex multi-die designs.

Another important standard is the Universal Chiplet Interconnect Express (UCIe), which defines a universal interconnect standard for chiplets. UCIe aims to create an open ecosystem for chiplet-based designs, allowing for mix-and-match of chiplets from different vendors while ensuring compatibility and performance.

In addition to these specific standards, general semiconductor industry standards such as those related to electrostatic discharge (ESD) protection, thermal management, and reliability testing are also applicable to chiplet-based systems. These standards ensure that chiplet designs meet the same rigorous quality and reliability requirements as traditional monolithic ICs.

As chiplet technology continues to evolve, industry standards are expected to adapt and expand to address new challenges. Future standards may focus on areas such as advanced packaging technologies, 3D integration, and system-level optimization for chiplet-based designs. The ongoing collaboration between industry leaders, research institutions, and standards organizations will be crucial in shaping these standards and driving the adoption of chiplet technology across various application domains.

Supply Chain Considerations for Chiplets

The supply chain for chiplet-based systems presents unique challenges and considerations that are critical to ensuring industry quality standards are met. As chiplets involve the integration of multiple die from potentially different manufacturers, supply chain management becomes more complex and requires careful coordination.

One key consideration is the sourcing of chiplets from multiple vendors. This multi-vendor approach can introduce variability in quality, performance, and reliability. To mitigate these risks, robust supplier qualification processes must be implemented. These processes should include thorough evaluation of each supplier's manufacturing capabilities, quality control systems, and track record in producing high-quality semiconductor components.

Traceability throughout the supply chain is another crucial aspect. Each chiplet should be traceable back to its origin, including information on the manufacturing process, materials used, and any testing or qualification results. This level of traceability enables better quality control and facilitates root cause analysis in case of any issues that may arise during integration or in the field.

Standardization of interfaces and protocols between chiplets is essential for ensuring compatibility and reducing integration challenges. Industry-wide standards, such as those developed by the Open Compute Project (OCP) or JEDEC, can help streamline the supply chain by enabling interoperability between chiplets from different suppliers.

Inventory management and just-in-time delivery become more critical in chiplet-based systems. With multiple components from various sources, coordinating the availability of all necessary chiplets for system integration requires sophisticated logistics planning. This includes considering lead times, production capacities, and potential supply disruptions for each chiplet supplier.

Quality control measures must be implemented at multiple stages of the supply chain. This includes incoming quality inspection of individual chiplets, in-process testing during integration, and final system-level testing. Advanced testing methodologies, such as Known Good Die (KGD) testing, become particularly important to ensure that only fully functional chiplets are used in the final assembly.

The packaging and integration processes also play a crucial role in the supply chain. Advanced packaging technologies, such as 2.5D and 3D integration, require specialized equipment and expertise. Ensuring that packaging partners have the necessary capabilities and maintain consistent quality standards is essential for the overall reliability of chiplet-based systems.

Lastly, supply chain resilience and risk management strategies are vital. This includes diversifying suppliers where possible, maintaining buffer inventories of critical components, and developing contingency plans for potential supply disruptions. Regular supply chain audits and continuous improvement initiatives can help identify and address vulnerabilities before they impact product quality or availability.

One key consideration is the sourcing of chiplets from multiple vendors. This multi-vendor approach can introduce variability in quality, performance, and reliability. To mitigate these risks, robust supplier qualification processes must be implemented. These processes should include thorough evaluation of each supplier's manufacturing capabilities, quality control systems, and track record in producing high-quality semiconductor components.

Traceability throughout the supply chain is another crucial aspect. Each chiplet should be traceable back to its origin, including information on the manufacturing process, materials used, and any testing or qualification results. This level of traceability enables better quality control and facilitates root cause analysis in case of any issues that may arise during integration or in the field.

Standardization of interfaces and protocols between chiplets is essential for ensuring compatibility and reducing integration challenges. Industry-wide standards, such as those developed by the Open Compute Project (OCP) or JEDEC, can help streamline the supply chain by enabling interoperability between chiplets from different suppliers.

Inventory management and just-in-time delivery become more critical in chiplet-based systems. With multiple components from various sources, coordinating the availability of all necessary chiplets for system integration requires sophisticated logistics planning. This includes considering lead times, production capacities, and potential supply disruptions for each chiplet supplier.

Quality control measures must be implemented at multiple stages of the supply chain. This includes incoming quality inspection of individual chiplets, in-process testing during integration, and final system-level testing. Advanced testing methodologies, such as Known Good Die (KGD) testing, become particularly important to ensure that only fully functional chiplets are used in the final assembly.

The packaging and integration processes also play a crucial role in the supply chain. Advanced packaging technologies, such as 2.5D and 3D integration, require specialized equipment and expertise. Ensuring that packaging partners have the necessary capabilities and maintain consistent quality standards is essential for the overall reliability of chiplet-based systems.

Lastly, supply chain resilience and risk management strategies are vital. This includes diversifying suppliers where possible, maintaining buffer inventories of critical components, and developing contingency plans for potential supply disruptions. Regular supply chain audits and continuous improvement initiatives can help identify and address vulnerabilities before they impact product quality or availability.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!