How to Ensure Chiplet Interoperability Across Device Platforms?

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Interoperability Background and Objectives

Chiplets have emerged as a revolutionary approach in semiconductor design, offering a pathway to overcome the limitations of traditional monolithic chip architectures. This technology allows for the disaggregation of complex system-on-chip (SoC) designs into smaller, more manageable functional blocks. The concept of chiplets has gained significant traction in recent years, driven by the increasing demand for higher performance, lower power consumption, and reduced manufacturing costs in various electronic devices.

The evolution of chiplet technology can be traced back to the early 2010s when the semiconductor industry began exploring alternatives to address the challenges posed by Moore's Law. As transistor scaling became increasingly difficult and expensive, chiplets presented a viable solution to continue improving chip performance and functionality. The modular nature of chiplets allows for the integration of different process nodes and technologies within a single package, enabling manufacturers to optimize performance, power, and cost for specific components.

The primary objective of ensuring chiplet interoperability across device platforms is to establish a standardized ecosystem that facilitates seamless integration and communication between chiplets from different vendors. This goal is crucial for promoting innovation, reducing time-to-market, and fostering competition in the semiconductor industry. Achieving interoperability requires addressing several key challenges, including standardizing interfaces, developing common protocols, and ensuring compatibility across various packaging technologies.

One of the main drivers behind the push for chiplet interoperability is the need to create a more flexible and scalable approach to chip design. By enabling mix-and-match capabilities, manufacturers can leverage the best-in-class components from different suppliers, leading to more optimized and cost-effective solutions. This approach also allows for faster product iterations and customization, as chiplets can be swapped or upgraded without redesigning the entire system.

The semiconductor industry has recognized the importance of chiplet interoperability, leading to the formation of various consortia and standardization efforts. These initiatives aim to develop open standards and specifications that will enable seamless integration of chiplets from multiple vendors. The ultimate goal is to create a thriving ecosystem where chiplets can be easily integrated into diverse device platforms, ranging from high-performance computing systems to mobile devices and Internet of Things (IoT) applications.

The evolution of chiplet technology can be traced back to the early 2010s when the semiconductor industry began exploring alternatives to address the challenges posed by Moore's Law. As transistor scaling became increasingly difficult and expensive, chiplets presented a viable solution to continue improving chip performance and functionality. The modular nature of chiplets allows for the integration of different process nodes and technologies within a single package, enabling manufacturers to optimize performance, power, and cost for specific components.

The primary objective of ensuring chiplet interoperability across device platforms is to establish a standardized ecosystem that facilitates seamless integration and communication between chiplets from different vendors. This goal is crucial for promoting innovation, reducing time-to-market, and fostering competition in the semiconductor industry. Achieving interoperability requires addressing several key challenges, including standardizing interfaces, developing common protocols, and ensuring compatibility across various packaging technologies.

One of the main drivers behind the push for chiplet interoperability is the need to create a more flexible and scalable approach to chip design. By enabling mix-and-match capabilities, manufacturers can leverage the best-in-class components from different suppliers, leading to more optimized and cost-effective solutions. This approach also allows for faster product iterations and customization, as chiplets can be swapped or upgraded without redesigning the entire system.

The semiconductor industry has recognized the importance of chiplet interoperability, leading to the formation of various consortia and standardization efforts. These initiatives aim to develop open standards and specifications that will enable seamless integration of chiplets from multiple vendors. The ultimate goal is to create a thriving ecosystem where chiplets can be easily integrated into diverse device platforms, ranging from high-performance computing systems to mobile devices and Internet of Things (IoT) applications.

Market Demand for Cross-Platform Chiplet Solutions

The market demand for cross-platform chiplet solutions has been steadily growing in recent years, driven by the increasing complexity of semiconductor designs and the need for more flexible and cost-effective manufacturing processes. As traditional monolithic chip designs reach their physical and economic limits, chiplet-based architectures have emerged as a promising alternative, offering improved scalability, performance, and cost-efficiency.

The semiconductor industry is witnessing a shift towards heterogeneous integration, where different functional blocks or chiplets are combined on a single package. This approach allows for the integration of diverse technologies, such as logic, memory, and analog components, each optimized for specific functions. The demand for cross-platform chiplet solutions stems from the need to ensure interoperability between these diverse components, regardless of their origin or manufacturing process.

One of the key drivers for this demand is the growing adoption of artificial intelligence and machine learning applications across various industries. These applications require high-performance computing capabilities that can be efficiently achieved through chiplet-based designs. The ability to mix and match chiplets from different vendors or platforms enables system designers to create customized solutions tailored to specific AI workloads, leading to improved performance and energy efficiency.

The automotive industry is another significant contributor to the demand for cross-platform chiplet solutions. As vehicles become increasingly connected and autonomous, they require more sophisticated computing systems that can handle complex sensor data processing, real-time decision-making, and advanced driver assistance features. Chiplet-based architectures offer the flexibility to integrate various specialized components, such as high-performance processors, graphics units, and sensor interfaces, while ensuring interoperability across different vehicle platforms.

The telecommunications sector, particularly with the rollout of 5G networks, is also driving demand for cross-platform chiplet solutions. The need for high-bandwidth, low-latency communication systems requires advanced semiconductor designs that can efficiently handle massive data processing and transmission. Chiplet-based architectures allow for the integration of diverse radio frequency, baseband processing, and network interface components, enabling the development of flexible and scalable 5G infrastructure.

Furthermore, the demand for cross-platform chiplet solutions is fueled by the growing trend of edge computing. As more devices become connected to the Internet of Things (IoT), there is an increasing need for powerful, energy-efficient computing capabilities at the edge of networks. Chiplet-based designs offer the flexibility to create customized edge computing solutions that can adapt to various deployment scenarios while maintaining interoperability with different IoT platforms and protocols.

The market demand for cross-platform chiplet solutions is also influenced by the need for more sustainable and cost-effective semiconductor manufacturing processes. By enabling the reuse and integration of pre-validated chiplets, this approach can potentially reduce development time, lower manufacturing costs, and improve overall yield. This aspect is particularly attractive to smaller companies and startups that may not have the resources to develop full custom chip designs but can leverage chiplet-based solutions to create innovative products.

The semiconductor industry is witnessing a shift towards heterogeneous integration, where different functional blocks or chiplets are combined on a single package. This approach allows for the integration of diverse technologies, such as logic, memory, and analog components, each optimized for specific functions. The demand for cross-platform chiplet solutions stems from the need to ensure interoperability between these diverse components, regardless of their origin or manufacturing process.

One of the key drivers for this demand is the growing adoption of artificial intelligence and machine learning applications across various industries. These applications require high-performance computing capabilities that can be efficiently achieved through chiplet-based designs. The ability to mix and match chiplets from different vendors or platforms enables system designers to create customized solutions tailored to specific AI workloads, leading to improved performance and energy efficiency.

The automotive industry is another significant contributor to the demand for cross-platform chiplet solutions. As vehicles become increasingly connected and autonomous, they require more sophisticated computing systems that can handle complex sensor data processing, real-time decision-making, and advanced driver assistance features. Chiplet-based architectures offer the flexibility to integrate various specialized components, such as high-performance processors, graphics units, and sensor interfaces, while ensuring interoperability across different vehicle platforms.

The telecommunications sector, particularly with the rollout of 5G networks, is also driving demand for cross-platform chiplet solutions. The need for high-bandwidth, low-latency communication systems requires advanced semiconductor designs that can efficiently handle massive data processing and transmission. Chiplet-based architectures allow for the integration of diverse radio frequency, baseband processing, and network interface components, enabling the development of flexible and scalable 5G infrastructure.

Furthermore, the demand for cross-platform chiplet solutions is fueled by the growing trend of edge computing. As more devices become connected to the Internet of Things (IoT), there is an increasing need for powerful, energy-efficient computing capabilities at the edge of networks. Chiplet-based designs offer the flexibility to create customized edge computing solutions that can adapt to various deployment scenarios while maintaining interoperability with different IoT platforms and protocols.

The market demand for cross-platform chiplet solutions is also influenced by the need for more sustainable and cost-effective semiconductor manufacturing processes. By enabling the reuse and integration of pre-validated chiplets, this approach can potentially reduce development time, lower manufacturing costs, and improve overall yield. This aspect is particularly attractive to smaller companies and startups that may not have the resources to develop full custom chip designs but can leverage chiplet-based solutions to create innovative products.

Current Challenges in Chiplet Interoperability

Chiplet interoperability across device platforms faces several significant challenges that hinder widespread adoption and seamless integration. One of the primary obstacles is the lack of standardized interfaces and protocols for chiplet-to-chiplet communication. Different manufacturers often employ proprietary interconnect technologies, making it difficult to mix and match chiplets from various sources.

The diversity of packaging technologies and form factors also presents a major hurdle. Chiplets designed for one packaging solution may not be compatible with others, limiting flexibility in system design and integration. This incompatibility extends to thermal management and power delivery systems, which can vary significantly between platforms.

Another critical challenge is the absence of a unified design and verification methodology for multi-chiplet systems. Traditional EDA tools and workflows are often ill-equipped to handle the complexities of chiplet-based designs, leading to increased development time and potential reliability issues. The lack of standardized testing and validation procedures for chiplet interoperability further compounds this problem.

Data synchronization and latency management across chiplets pose significant technical challenges, especially in high-performance computing applications. Ensuring consistent timing and low-latency communication between chiplets from different vendors or technology nodes requires sophisticated design techniques and potentially specialized hardware.

The heterogeneity of chiplets, while offering advantages in terms of customization and optimization, also introduces complexities in system integration. Differences in process nodes, voltage domains, and clock frequencies between chiplets can lead to signal integrity issues and increased power consumption if not carefully managed.

Security and trust verification for multi-vendor chiplet solutions represent another layer of complexity. Ensuring that chiplets from different sources can securely interact without compromising system integrity or exposing sensitive data remains a significant challenge.

Lastly, the economic and supply chain implications of chiplet interoperability cannot be overlooked. The current ecosystem lacks the necessary infrastructure and business models to support a truly open chiplet marketplace, where designers can easily source and integrate chiplets from multiple vendors. Overcoming these challenges requires concerted efforts from industry stakeholders to develop standards, tools, and practices that enable seamless chiplet interoperability across diverse device platforms.

The diversity of packaging technologies and form factors also presents a major hurdle. Chiplets designed for one packaging solution may not be compatible with others, limiting flexibility in system design and integration. This incompatibility extends to thermal management and power delivery systems, which can vary significantly between platforms.

Another critical challenge is the absence of a unified design and verification methodology for multi-chiplet systems. Traditional EDA tools and workflows are often ill-equipped to handle the complexities of chiplet-based designs, leading to increased development time and potential reliability issues. The lack of standardized testing and validation procedures for chiplet interoperability further compounds this problem.

Data synchronization and latency management across chiplets pose significant technical challenges, especially in high-performance computing applications. Ensuring consistent timing and low-latency communication between chiplets from different vendors or technology nodes requires sophisticated design techniques and potentially specialized hardware.

The heterogeneity of chiplets, while offering advantages in terms of customization and optimization, also introduces complexities in system integration. Differences in process nodes, voltage domains, and clock frequencies between chiplets can lead to signal integrity issues and increased power consumption if not carefully managed.

Security and trust verification for multi-vendor chiplet solutions represent another layer of complexity. Ensuring that chiplets from different sources can securely interact without compromising system integrity or exposing sensitive data remains a significant challenge.

Lastly, the economic and supply chain implications of chiplet interoperability cannot be overlooked. The current ecosystem lacks the necessary infrastructure and business models to support a truly open chiplet marketplace, where designers can easily source and integrate chiplets from multiple vendors. Overcoming these challenges requires concerted efforts from industry stakeholders to develop standards, tools, and practices that enable seamless chiplet interoperability across diverse device platforms.

Existing Chiplet Interoperability Standards

01 Standardized interfaces for chiplet communication

Developing standardized interfaces and protocols for communication between different chiplets is crucial for interoperability. This includes creating common specifications for data transfer, power management, and signal integrity across various chiplet designs. Standardization enables seamless integration of chiplets from different manufacturers, promoting a more diverse and flexible ecosystem.- Standardized interfaces for chiplet communication: Developing standardized interfaces and protocols for communication between different chiplets is crucial for interoperability. This includes creating common specifications for data transfer, power management, and signal integrity across various chiplet designs and manufacturers.

- Advanced packaging technologies for chiplet integration: Utilizing advanced packaging technologies, such as 2.5D and 3D integration, to enable efficient interconnection and communication between heterogeneous chiplets. These technologies focus on improving signal integrity, reducing latency, and optimizing power consumption in multi-chiplet systems.

- Software-defined chiplet configuration and management: Implementing software-defined approaches for configuring and managing chiplet-based systems. This includes developing flexible software frameworks that can dynamically allocate resources, optimize performance, and ensure compatibility across different chiplet configurations.

- Interoperable power and thermal management: Designing power and thermal management systems that can effectively operate across diverse chiplet architectures. This involves creating adaptive power distribution networks and thermal solutions that can accommodate varying power requirements and heat dissipation characteristics of different chiplets.

- Security and authentication protocols for chiplet ecosystems: Developing robust security and authentication protocols to ensure secure communication and data exchange between chiplets from different vendors. This includes implementing encryption methods, secure boot processes, and hardware-level security features to protect against potential vulnerabilities in multi-chiplet systems.

02 Advanced packaging technologies for chiplet integration

Implementing advanced packaging technologies is essential for effective chiplet integration. This involves developing innovative methods for connecting and assembling multiple chiplets within a single package, such as 2.5D and 3D integration techniques. These technologies address challenges related to thermal management, power delivery, and signal integrity in multi-chiplet designs.Expand Specific Solutions03 Software-defined chiplet configuration and management

Creating software-defined approaches for chiplet configuration and management enhances interoperability. This includes developing APIs and middleware that allow for dynamic allocation of chiplet resources, runtime optimization, and seamless integration of chiplets with different functionalities. Such software solutions enable more flexible and adaptable chiplet-based systems.Expand Specific Solutions04 Interoperable power and thermal management systems

Designing interoperable power and thermal management systems is crucial for chiplet-based architectures. This involves creating standardized methods for power distribution, voltage regulation, and heat dissipation across multiple chiplets. Effective power and thermal management ensures optimal performance and reliability in heterogeneous chiplet configurations.Expand Specific Solutions05 Security and authentication protocols for chiplet ecosystems

Developing robust security and authentication protocols for chiplet ecosystems is essential for ensuring trust and integrity in multi-vendor chiplet designs. This includes creating standardized methods for secure boot, encryption, and access control across different chiplets. These protocols safeguard against potential vulnerabilities in heterogeneous chiplet configurations.Expand Specific Solutions

Key Players in Chiplet Ecosystem

The chiplet interoperability landscape is evolving rapidly, with the market in its early growth stage. Major players like Intel, Micron, and Xilinx are driving innovation in this emerging field. The technology is still maturing, with companies focusing on developing standardized interfaces and protocols to ensure seamless integration across different platforms. As the demand for more powerful and efficient computing solutions grows, the chiplet market is expected to expand significantly in the coming years. Companies are investing heavily in research and development to overcome technical challenges and establish their position in this competitive space.

Intel Corp.

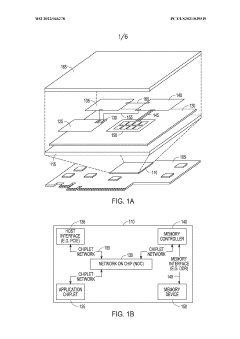

Technical Solution: Intel's approach to ensuring chiplet interoperability focuses on their Universal Chiplet Interconnect Express (UCIe) standard. UCIe aims to create an open ecosystem for chiplet-based designs, enabling mix-and-match of chiplets from different vendors. The standard defines both the physical and protocol layers for die-to-die interconnection, supporting data rates up to 16 GT/s[1]. Intel's implementation includes advanced packaging technologies like EMIB (Embedded Multi-die Interconnect Bridge) and Foveros 3D packaging, which allow for high-bandwidth, low-latency connections between chiplets[2]. They've also developed a modular SoC design approach, allowing for flexible integration of various IP blocks and chiplets[3].

Strengths: Open standard promoting industry-wide adoption, high-performance interconnect, advanced packaging technologies. Weaknesses: Potential challenges in achieving full compatibility with all third-party chiplets, reliance on industry-wide adoption for maximum effectiveness.

Xilinx, Inc.

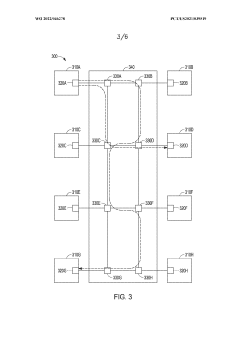

Technical Solution: Xilinx, now part of AMD, has been pioneering chiplet interoperability through their Adaptive Compute Acceleration Platform (ACAP) and advanced packaging technologies. Their Versal ACAP architecture utilizes a modular approach, integrating various types of processing engines (scalar engines, adaptable hardware engines, and intelligent engines) as chiplets[10]. Xilinx's Network-on-Chip (NoC) technology provides a high-bandwidth, low-latency interconnect between these chiplets, supporting data rates up to 2.5 Tbps[11]. They've also developed the Stacked Silicon Interconnect (SSI) technology, which allows for the integration of multiple FPGA dies into a single package, effectively creating a large-scale chiplet-based system[12]. Xilinx has been actively participating in industry standardization efforts, including the ODSA and UCIe initiatives, to promote interoperability across different vendors.

Strengths: Flexible and adaptable architecture, high-performance NoC, advanced packaging technologies. Weaknesses: Potential complexity in programming and optimization, may require specialized tools and expertise.

Core Innovations in Chiplet Interface Technologies

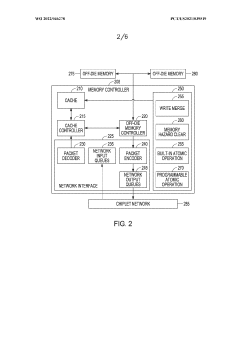

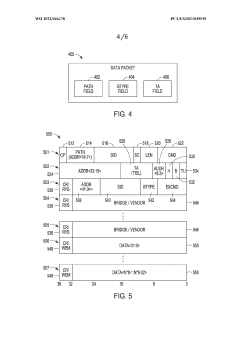

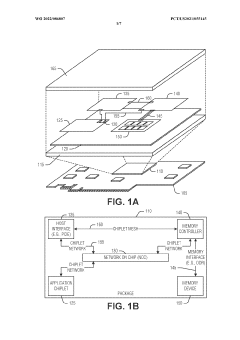

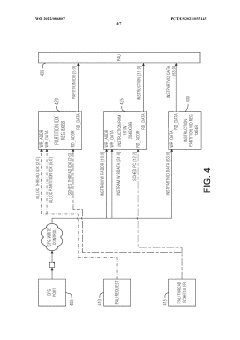

Ordered delivery of data packets based on type of path information in each packet

PatentWO2022046278A1

Innovation

- Incorporating a bridge-type field in data packets to indicate the type of path information, allowing for both address-based and transaction identifier-based ordering, enabling the network to support multiple use cases and bridge between different standards or protocols.

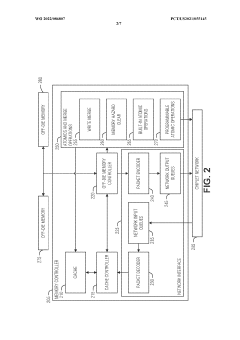

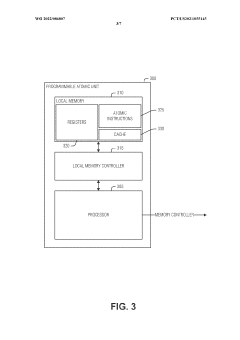

On-demand programmable atomic kernel loading

PatentWO2022086807A1

Innovation

- Implementing an on-demand mechanism for loading PAO kernels, where PAUs register for potential use and reserve space, loading the kernel only when requested, and signaling a trap to initiate kernel transfer when needed.

Standardization Efforts and Industry Consortiums

Ensuring chiplet interoperability across device platforms requires concerted efforts from various industry stakeholders. Standardization initiatives and industry consortiums play a crucial role in establishing common frameworks and protocols that enable seamless integration of chiplets from different manufacturers.

One of the most prominent organizations leading the charge in chiplet standardization is the Universal Chiplet Interconnect Express (UCIe) consortium. Formed in 2022, UCIe brings together major players in the semiconductor industry, including Intel, AMD, Arm, TSMC, and Samsung, among others. The consortium aims to develop and promote an open industry standard for die-to-die interconnects, which is essential for chiplet-based designs.

The UCIe specification defines a standardized die-to-die interconnect that covers multiple layers of the hardware stack, including the physical layer, protocol layer, and software layer. This comprehensive approach ensures that chiplets from different vendors can communicate effectively and efficiently when integrated into a single package.

Another significant industry initiative is the Open Compute Project (OCP), which has established the Open Domain-Specific Architecture (ODSA) workgroup. The ODSA focuses on creating open standards for chiplet-based designs, with a particular emphasis on developing a Bunch of Wires (BoW) interface for chiplet-to-chiplet communication.

The JEDEC Solid State Technology Association has also been actively involved in chiplet standardization efforts. Their JC-63 Committee for Multichip Modules is working on developing standards for chiplet-based designs, addressing aspects such as thermal management, power delivery, and signal integrity.

In addition to these consortiums, individual companies are also contributing to the standardization landscape. For instance, AMD has proposed its Infinity Fabric interconnect as a potential industry standard for chiplet communication. Similarly, Intel has been promoting its Advanced Interface Bus (AIB) as an open standard for chiplet integration.

The collaboration between these various standardization efforts and industry consortiums is crucial for ensuring widespread adoption of chiplet technology. By establishing common protocols and interfaces, these initiatives reduce the barriers to entry for smaller companies and promote innovation in the semiconductor industry.

However, challenges remain in aligning the interests of different stakeholders and ensuring that standards evolve to keep pace with rapid technological advancements. Continued cooperation and open dialogue among industry players will be essential to overcome these challenges and realize the full potential of chiplet-based designs across diverse device platforms.

One of the most prominent organizations leading the charge in chiplet standardization is the Universal Chiplet Interconnect Express (UCIe) consortium. Formed in 2022, UCIe brings together major players in the semiconductor industry, including Intel, AMD, Arm, TSMC, and Samsung, among others. The consortium aims to develop and promote an open industry standard for die-to-die interconnects, which is essential for chiplet-based designs.

The UCIe specification defines a standardized die-to-die interconnect that covers multiple layers of the hardware stack, including the physical layer, protocol layer, and software layer. This comprehensive approach ensures that chiplets from different vendors can communicate effectively and efficiently when integrated into a single package.

Another significant industry initiative is the Open Compute Project (OCP), which has established the Open Domain-Specific Architecture (ODSA) workgroup. The ODSA focuses on creating open standards for chiplet-based designs, with a particular emphasis on developing a Bunch of Wires (BoW) interface for chiplet-to-chiplet communication.

The JEDEC Solid State Technology Association has also been actively involved in chiplet standardization efforts. Their JC-63 Committee for Multichip Modules is working on developing standards for chiplet-based designs, addressing aspects such as thermal management, power delivery, and signal integrity.

In addition to these consortiums, individual companies are also contributing to the standardization landscape. For instance, AMD has proposed its Infinity Fabric interconnect as a potential industry standard for chiplet communication. Similarly, Intel has been promoting its Advanced Interface Bus (AIB) as an open standard for chiplet integration.

The collaboration between these various standardization efforts and industry consortiums is crucial for ensuring widespread adoption of chiplet technology. By establishing common protocols and interfaces, these initiatives reduce the barriers to entry for smaller companies and promote innovation in the semiconductor industry.

However, challenges remain in aligning the interests of different stakeholders and ensuring that standards evolve to keep pace with rapid technological advancements. Continued cooperation and open dialogue among industry players will be essential to overcome these challenges and realize the full potential of chiplet-based designs across diverse device platforms.

Performance and Power Efficiency Considerations

Performance and power efficiency are critical considerations in ensuring chiplet interoperability across device platforms. As chiplet technology continues to evolve, the need for optimized performance and reduced power consumption becomes increasingly important. One of the primary challenges in chiplet-based designs is managing the communication between different chiplets, which can significantly impact overall system performance and energy efficiency.

To address these challenges, designers must focus on developing high-bandwidth, low-latency interconnects between chiplets. Advanced packaging technologies, such as 2.5D and 3D integration, play a crucial role in enabling efficient chiplet-to-chiplet communication. These packaging solutions allow for shorter interconnect lengths, reducing signal propagation delays and power consumption associated with data transfer between chiplets.

Power management techniques are essential for optimizing energy efficiency in chiplet-based systems. Implementing fine-grained power gating and dynamic voltage and frequency scaling (DVFS) at the chiplet level can help reduce overall power consumption. Additionally, intelligent power distribution and thermal management strategies are necessary to ensure optimal performance across different chiplets, especially in heterogeneous systems combining chiplets with varying power requirements.

Standardization efforts, such as the Universal Chiplet Interconnect Express (UCIe) specification, are crucial for ensuring interoperability and performance consistency across different chiplet implementations. By defining common protocols and electrical interfaces, these standards enable seamless integration of chiplets from various vendors, promoting a more diverse and competitive ecosystem while maintaining high performance and power efficiency.

Memory bandwidth and cache coherency are other critical factors affecting chiplet interoperability and performance. Designers must carefully consider memory hierarchy and cache architectures to minimize data movement between chiplets and reduce latency. Implementing efficient cache coherency protocols and optimizing memory access patterns can significantly improve overall system performance and reduce power consumption associated with data transfers.

As chiplet designs become more complex, advanced simulation and modeling tools are essential for predicting and optimizing performance and power efficiency. These tools enable designers to evaluate different chiplet configurations, interconnect topologies, and power management strategies before committing to physical implementations, reducing development time and costs while ensuring optimal performance across diverse device platforms.

To address these challenges, designers must focus on developing high-bandwidth, low-latency interconnects between chiplets. Advanced packaging technologies, such as 2.5D and 3D integration, play a crucial role in enabling efficient chiplet-to-chiplet communication. These packaging solutions allow for shorter interconnect lengths, reducing signal propagation delays and power consumption associated with data transfer between chiplets.

Power management techniques are essential for optimizing energy efficiency in chiplet-based systems. Implementing fine-grained power gating and dynamic voltage and frequency scaling (DVFS) at the chiplet level can help reduce overall power consumption. Additionally, intelligent power distribution and thermal management strategies are necessary to ensure optimal performance across different chiplets, especially in heterogeneous systems combining chiplets with varying power requirements.

Standardization efforts, such as the Universal Chiplet Interconnect Express (UCIe) specification, are crucial for ensuring interoperability and performance consistency across different chiplet implementations. By defining common protocols and electrical interfaces, these standards enable seamless integration of chiplets from various vendors, promoting a more diverse and competitive ecosystem while maintaining high performance and power efficiency.

Memory bandwidth and cache coherency are other critical factors affecting chiplet interoperability and performance. Designers must carefully consider memory hierarchy and cache architectures to minimize data movement between chiplets and reduce latency. Implementing efficient cache coherency protocols and optimizing memory access patterns can significantly improve overall system performance and reduce power consumption associated with data transfers.

As chiplet designs become more complex, advanced simulation and modeling tools are essential for predicting and optimizing performance and power efficiency. These tools enable designers to evaluate different chiplet configurations, interconnect topologies, and power management strategies before committing to physical implementations, reducing development time and costs while ensuring optimal performance across diverse device platforms.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!