How to Optimize Chiplet Arrangements for High-Volume Data Management?

JUL 16, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

Patsnap Eureka helps you evaluate technical feasibility & market potential.

Chiplet Technology Evolution and Objectives

Chiplet technology has emerged as a revolutionary approach in the semiconductor industry, offering a paradigm shift in chip design and manufacturing. The evolution of chiplets can be traced back to the early 2010s when traditional monolithic chip designs began to face significant challenges in terms of scalability, performance, and cost-effectiveness. As Moore's Law reached its physical limits, chiplets presented a viable solution to continue advancing computing capabilities.

The primary objective of chiplet technology is to disaggregate complex System-on-Chip (SoC) designs into smaller, more manageable components. This modular approach allows for greater flexibility in chip design, improved yield rates, and the ability to mix and match different process nodes within a single package. In the context of high-volume data management, chiplets offer the potential to optimize performance, power efficiency, and cost-effectiveness of data processing systems.

The evolution of chiplet technology has been marked by several key milestones. Initially, the focus was on developing reliable interconnect technologies to enable high-bandwidth, low-latency communication between chiplets. This led to the development of advanced packaging technologies such as 2.5D and 3D integration. As the technology matured, industry standards like Universal Chiplet Interconnect Express (UCIe) emerged, promoting interoperability and accelerating adoption across the semiconductor ecosystem.

In recent years, the objectives of chiplet technology have expanded beyond mere disaggregation. There is a growing emphasis on heterogeneous integration, allowing for the combination of chiplets with different functionalities and process nodes. This approach is particularly relevant for data-intensive applications, as it enables the optimization of specific components for tasks such as data processing, memory management, and I/O operations.

For high-volume data management, the evolution of chiplet technology aims to address several critical challenges. These include improving data throughput, reducing latency, enhancing energy efficiency, and scaling compute and memory resources cost-effectively. The modular nature of chiplets allows for the creation of customized solutions tailored to specific data management requirements, potentially revolutionizing the design of data centers and high-performance computing systems.

Looking ahead, the objectives of chiplet technology in the realm of high-volume data management are likely to focus on further miniaturization, increased integration density, and the development of advanced cooling solutions to manage thermal challenges. Additionally, there is a growing interest in exploring novel materials and 3D stacking techniques to push the boundaries of chiplet performance and efficiency.

The primary objective of chiplet technology is to disaggregate complex System-on-Chip (SoC) designs into smaller, more manageable components. This modular approach allows for greater flexibility in chip design, improved yield rates, and the ability to mix and match different process nodes within a single package. In the context of high-volume data management, chiplets offer the potential to optimize performance, power efficiency, and cost-effectiveness of data processing systems.

The evolution of chiplet technology has been marked by several key milestones. Initially, the focus was on developing reliable interconnect technologies to enable high-bandwidth, low-latency communication between chiplets. This led to the development of advanced packaging technologies such as 2.5D and 3D integration. As the technology matured, industry standards like Universal Chiplet Interconnect Express (UCIe) emerged, promoting interoperability and accelerating adoption across the semiconductor ecosystem.

In recent years, the objectives of chiplet technology have expanded beyond mere disaggregation. There is a growing emphasis on heterogeneous integration, allowing for the combination of chiplets with different functionalities and process nodes. This approach is particularly relevant for data-intensive applications, as it enables the optimization of specific components for tasks such as data processing, memory management, and I/O operations.

For high-volume data management, the evolution of chiplet technology aims to address several critical challenges. These include improving data throughput, reducing latency, enhancing energy efficiency, and scaling compute and memory resources cost-effectively. The modular nature of chiplets allows for the creation of customized solutions tailored to specific data management requirements, potentially revolutionizing the design of data centers and high-performance computing systems.

Looking ahead, the objectives of chiplet technology in the realm of high-volume data management are likely to focus on further miniaturization, increased integration density, and the development of advanced cooling solutions to manage thermal challenges. Additionally, there is a growing interest in exploring novel materials and 3D stacking techniques to push the boundaries of chiplet performance and efficiency.

Data Management Market Demand Analysis

The data management market is experiencing unprecedented growth, driven by the exponential increase in data generation across various sectors. As organizations grapple with the challenges of storing, processing, and analyzing vast amounts of information, the demand for efficient data management solutions has skyrocketed. This surge in demand is particularly evident in industries such as finance, healthcare, e-commerce, and telecommunications, where data-driven decision-making has become a critical competitive advantage.

The global data management market size was valued at $73.5 billion in 2020 and is projected to reach $135.9 billion by 2025, growing at a CAGR of 13.1% during the forecast period. This robust growth is fueled by several factors, including the increasing adoption of cloud-based solutions, the rise of big data analytics, and the growing importance of data governance and compliance.

One of the key drivers of market demand is the need for high-volume data processing capabilities. As organizations collect and store ever-increasing amounts of data, there is a growing requirement for solutions that can handle massive data volumes efficiently. This has led to a surge in demand for advanced hardware architectures, such as chiplet-based designs, which offer improved performance and scalability for data-intensive applications.

The financial services sector, in particular, has emerged as a major consumer of high-volume data management solutions. Banks, insurance companies, and investment firms are leveraging big data analytics to enhance risk management, detect fraud, and personalize customer experiences. The healthcare industry is another significant market, with the increasing adoption of electronic health records and the growing importance of data-driven medical research driving demand for robust data management systems.

Cloud service providers are also experiencing a surge in demand for data management solutions, as more businesses migrate their operations to the cloud. This trend has created a need for scalable, high-performance data processing architectures that can handle the diverse workloads of multiple clients simultaneously.

The Internet of Things (IoT) and edge computing are emerging as significant drivers of market demand. As billions of connected devices generate vast amounts of data at the edge, there is a growing need for efficient data management solutions that can process and analyze this information in real-time. This trend is particularly relevant for industries such as manufacturing, smart cities, and autonomous vehicles.

In response to these market demands, chiplet-based architectures are gaining traction as a promising solution for high-volume data management. By optimizing chiplet arrangements, manufacturers can create highly scalable and efficient systems that meet the diverse needs of data-intensive applications. This approach allows for greater flexibility in system design, improved thermal management, and enhanced performance-per-watt ratios, all of which are critical factors in addressing the growing demands of the data management market.

The global data management market size was valued at $73.5 billion in 2020 and is projected to reach $135.9 billion by 2025, growing at a CAGR of 13.1% during the forecast period. This robust growth is fueled by several factors, including the increasing adoption of cloud-based solutions, the rise of big data analytics, and the growing importance of data governance and compliance.

One of the key drivers of market demand is the need for high-volume data processing capabilities. As organizations collect and store ever-increasing amounts of data, there is a growing requirement for solutions that can handle massive data volumes efficiently. This has led to a surge in demand for advanced hardware architectures, such as chiplet-based designs, which offer improved performance and scalability for data-intensive applications.

The financial services sector, in particular, has emerged as a major consumer of high-volume data management solutions. Banks, insurance companies, and investment firms are leveraging big data analytics to enhance risk management, detect fraud, and personalize customer experiences. The healthcare industry is another significant market, with the increasing adoption of electronic health records and the growing importance of data-driven medical research driving demand for robust data management systems.

Cloud service providers are also experiencing a surge in demand for data management solutions, as more businesses migrate their operations to the cloud. This trend has created a need for scalable, high-performance data processing architectures that can handle the diverse workloads of multiple clients simultaneously.

The Internet of Things (IoT) and edge computing are emerging as significant drivers of market demand. As billions of connected devices generate vast amounts of data at the edge, there is a growing need for efficient data management solutions that can process and analyze this information in real-time. This trend is particularly relevant for industries such as manufacturing, smart cities, and autonomous vehicles.

In response to these market demands, chiplet-based architectures are gaining traction as a promising solution for high-volume data management. By optimizing chiplet arrangements, manufacturers can create highly scalable and efficient systems that meet the diverse needs of data-intensive applications. This approach allows for greater flexibility in system design, improved thermal management, and enhanced performance-per-watt ratios, all of which are critical factors in addressing the growing demands of the data management market.

Chiplet Arrangement Challenges

The optimization of chiplet arrangements for high-volume data management presents several significant challenges. One of the primary obstacles is the complexity of interconnect design. As the number of chiplets increases, the interconnect architecture becomes more intricate, requiring careful planning to minimize signal latency and power consumption while maximizing bandwidth. This challenge is further compounded by the need to maintain signal integrity across multiple chiplets, which can be affected by factors such as crosstalk and electromagnetic interference.

Another major challenge lies in thermal management. High-performance chiplets generate substantial heat, and when multiple chiplets are arranged in close proximity, efficient heat dissipation becomes crucial. Designers must consider innovative cooling solutions and thermal-aware placement strategies to prevent hotspots and ensure optimal performance across the entire chiplet array. This challenge is particularly acute in data-intensive applications where continuous high-throughput processing is required.

Power distribution and management pose additional difficulties in chiplet arrangements. As the number of chiplets grows, delivering stable and sufficient power to each component becomes more complex. Voltage drops and power fluctuations can lead to performance inconsistencies or even system failures. Engineers must develop sophisticated power delivery networks and implement advanced power management techniques to ensure reliable operation across the entire chiplet ecosystem.

The challenge of yield and cost optimization is also significant. While chiplets offer the potential for improved yield compared to monolithic designs, the assembly process introduces new complexities. Ensuring consistent quality and performance across multiple chiplets from potentially different manufacturing processes or even different suppliers requires rigorous testing and quality control measures. Balancing the cost benefits of smaller die sizes with the additional expenses of integration and packaging is a delicate task that impacts the overall economic viability of chiplet-based solutions.

Standardization and interoperability present ongoing challenges in the chiplet ecosystem. The lack of universal standards for chiplet interfaces and protocols can limit the flexibility and reusability of chiplet designs across different platforms and applications. Efforts to establish industry-wide standards are underway, but achieving widespread adoption and compatibility remains a complex undertaking.

Lastly, the challenge of system-level optimization cannot be overlooked. Arranging chiplets for optimal data flow and processing efficiency requires a holistic approach that considers not only the physical layout but also the logical architecture of the system. Balancing compute, memory, and I/O resources across multiple chiplets to achieve maximum performance for high-volume data management workloads is a multidimensional optimization problem that demands sophisticated design tools and methodologies.

Another major challenge lies in thermal management. High-performance chiplets generate substantial heat, and when multiple chiplets are arranged in close proximity, efficient heat dissipation becomes crucial. Designers must consider innovative cooling solutions and thermal-aware placement strategies to prevent hotspots and ensure optimal performance across the entire chiplet array. This challenge is particularly acute in data-intensive applications where continuous high-throughput processing is required.

Power distribution and management pose additional difficulties in chiplet arrangements. As the number of chiplets grows, delivering stable and sufficient power to each component becomes more complex. Voltage drops and power fluctuations can lead to performance inconsistencies or even system failures. Engineers must develop sophisticated power delivery networks and implement advanced power management techniques to ensure reliable operation across the entire chiplet ecosystem.

The challenge of yield and cost optimization is also significant. While chiplets offer the potential for improved yield compared to monolithic designs, the assembly process introduces new complexities. Ensuring consistent quality and performance across multiple chiplets from potentially different manufacturing processes or even different suppliers requires rigorous testing and quality control measures. Balancing the cost benefits of smaller die sizes with the additional expenses of integration and packaging is a delicate task that impacts the overall economic viability of chiplet-based solutions.

Standardization and interoperability present ongoing challenges in the chiplet ecosystem. The lack of universal standards for chiplet interfaces and protocols can limit the flexibility and reusability of chiplet designs across different platforms and applications. Efforts to establish industry-wide standards are underway, but achieving widespread adoption and compatibility remains a complex undertaking.

Lastly, the challenge of system-level optimization cannot be overlooked. Arranging chiplets for optimal data flow and processing efficiency requires a holistic approach that considers not only the physical layout but also the logical architecture of the system. Balancing compute, memory, and I/O resources across multiple chiplets to achieve maximum performance for high-volume data management workloads is a multidimensional optimization problem that demands sophisticated design tools and methodologies.

Current Chiplet Optimization Techniques

01 Chiplet interconnection and communication

This approach focuses on optimizing the interconnection and communication between chiplets in a multi-chip system. It involves developing efficient data transfer protocols, implementing high-speed interfaces, and managing signal integrity to ensure seamless data flow between chiplets. These techniques aim to reduce latency and improve overall system performance in chiplet-based architectures.- Chiplet interconnection and communication: This approach focuses on optimizing the interconnection and communication between chiplets in a multi-chip system. It involves developing efficient data transfer protocols, implementing high-speed interfaces, and managing signal integrity to ensure seamless data flow between chiplets. These techniques aim to reduce latency and improve overall system performance in chiplet-based architectures.

- Power management in chiplet arrangements: Power management strategies for chiplet-based systems are crucial for optimizing energy efficiency. This includes implementing dynamic voltage and frequency scaling, power gating techniques, and intelligent power distribution across chiplets. Advanced power management solutions help balance performance and energy consumption in complex chiplet arrangements.

- Data coherency and synchronization in chiplet systems: Maintaining data coherency and synchronization across multiple chiplets is essential for system reliability. This involves developing protocols for cache coherence, implementing efficient memory management techniques, and ensuring consistent data states across distributed chiplet components. These methods help prevent data conflicts and maintain system integrity in multi-chiplet architectures.

- Thermal management for chiplet arrangements: Effective thermal management is critical in chiplet-based designs to prevent overheating and maintain optimal performance. This includes developing advanced cooling solutions, implementing thermal-aware task scheduling, and designing efficient heat dissipation mechanisms. These techniques help manage heat distribution across chiplets and ensure stable operation of the overall system.

- Chiplet configuration and resource allocation: Dynamic configuration and resource allocation in chiplet systems allow for flexible and efficient utilization of computing resources. This involves developing algorithms for task distribution, implementing adaptive chiplet interconnect topologies, and managing shared resources across chiplets. These approaches enable optimized performance and adaptability in varying workload scenarios for chiplet-based architectures.

02 Power management in chiplet arrangements

Power management strategies for chiplet-based systems are crucial for optimizing energy efficiency and thermal performance. This includes implementing dynamic voltage and frequency scaling, power gating techniques, and intelligent power distribution across chiplets. Advanced power management solutions help balance performance and energy consumption in complex chiplet arrangements.Expand Specific Solutions03 Data coherency and synchronization in chiplet systems

Maintaining data coherency and synchronization across multiple chiplets is essential for system reliability and consistency. This involves implementing cache coherency protocols, developing efficient memory management techniques, and ensuring proper data synchronization between chiplets. These methods help prevent data conflicts and maintain system integrity in distributed chiplet architectures.Expand Specific Solutions04 Chiplet configuration and reconfigurability

This approach focuses on designing flexible chiplet arrangements that can be dynamically configured or reconfigured based on workload requirements. It includes developing modular chiplet designs, implementing programmable interconnects, and creating software-defined chiplet management systems. These techniques enable adaptable and scalable chiplet-based architectures that can optimize performance for various applications.Expand Specific Solutions05 Thermal management and reliability in chiplet systems

Effective thermal management and reliability enhancement are critical for chiplet-based designs. This involves implementing advanced cooling solutions, developing thermal-aware task scheduling algorithms, and employing fault-tolerant techniques. These methods aim to maintain optimal operating temperatures, improve system reliability, and extend the lifespan of chiplet arrangements in high-performance computing environments.Expand Specific Solutions

Key Chiplet Industry Players

The optimization of chiplet arrangements for high-volume data management is currently in a rapidly evolving phase, with significant market growth potential. The market is driven by increasing demand for efficient data processing in various sectors. While the technology is still maturing, major players like IBM, Samsung Electronics, and Micron Technology are making substantial advancements. These companies are leveraging their expertise in semiconductor design and manufacturing to develop innovative chiplet solutions. The competitive landscape is characterized by a mix of established tech giants and specialized semiconductor firms, each contributing unique approaches to chiplet optimization. As the technology progresses, we can expect increased collaboration and competition among these players to drive further innovations in high-volume data management solutions.

Micron Technology, Inc.

Technical Solution: Micron's approach to optimizing chiplet arrangements for high-volume data management focuses on their Hybrid Memory Cube (HMC) technology. HMC utilizes 3D stacking of DRAM dies with a logic layer, interconnected by Through-Silicon Vias (TSVs). This architecture allows for higher bandwidth, lower power consumption, and improved thermal management compared to traditional DRAM configurations[1]. Micron has further enhanced this technology by implementing advanced packaging techniques, such as silicon interposers and micro-bumps, to create more efficient chiplet-based systems. Their latest iterations incorporate AI-driven placement algorithms to optimize the arrangement of chiplets based on data flow patterns and thermal considerations[3].

Strengths: High bandwidth, reduced power consumption, and improved thermal management. Weaknesses: Complexity in manufacturing and potentially higher initial costs.

International Business Machines Corp.

Technical Solution: IBM's approach to chiplet optimization for high-volume data management centers around their Power10 processor architecture. This design utilizes a modular chiplet-based approach, where multiple smaller dies are integrated onto a single package. IBM employs advanced packaging technologies such as their proprietary Silicon Carrier Packaging (SCP) to interconnect these chiplets[2]. The Power10 architecture incorporates dedicated AI accelerators and memory compression technologies to enhance data processing capabilities. IBM has also developed a novel interconnect fabric that allows for high-speed, low-latency communication between chiplets, enabling more efficient data movement and processing[4]. Their design philosophy focuses on scalability, allowing for easy integration of additional chiplets to meet varying data management needs.

Strengths: Scalability, integration of AI accelerators, and advanced interconnect technology. Weaknesses: Potential compatibility issues with non-IBM systems and ecosystem limitations.

Innovative Chiplet Arrangement Patents

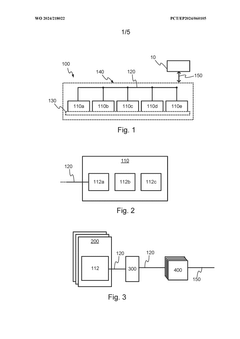

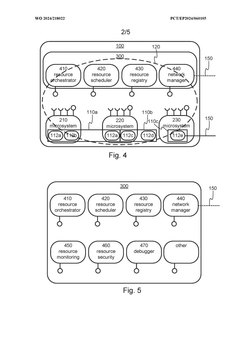

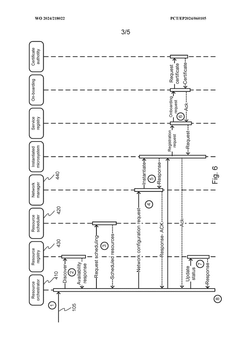

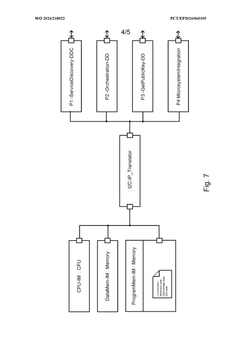

Chiplet arrangement

PatentWO2024218022A1

Innovation

- A chiplet arrangement with a control plane that orchestrates microsystems and microservices, utilizing a resource orchestrator, network manager, and resource scheduler to dynamically instantiate and manage hardware resources based on availability and utilization, enabling optimized resource utilization, scalability, and reduced power consumption.

Multiplying and adding small-exponent floating-point format data elements with integer addition

PatentPendingUS20250004721A1

Innovation

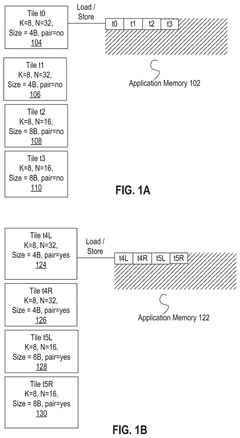

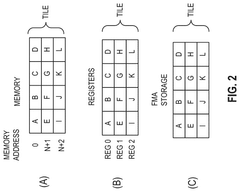

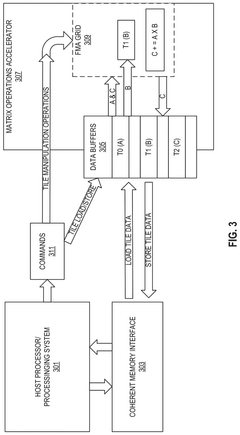

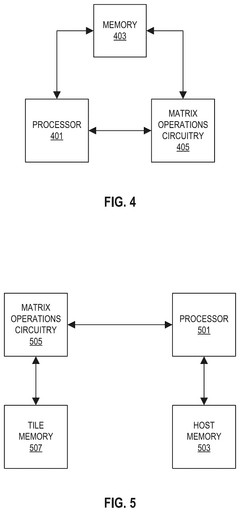

- The implementation of matrix operations using 2-dimensional data structures referred to as 'tiles' within central processing units (CPUs), graphic processing units (GPUs), and accelerators, which allow for optimized matrix multiplication, addition, and other operations by configuring tiles with specific dimensions and data types, enabling efficient memory access and operation.

Thermal Management Strategies

Thermal management is a critical aspect of optimizing chiplet arrangements for high-volume data management. As data processing demands increase, the heat generated by densely packed chiplets becomes a significant challenge. Effective thermal management strategies are essential to maintain optimal performance, reliability, and longevity of chiplet-based systems.

One key approach to thermal management in chiplet arrangements is the implementation of advanced cooling solutions. Liquid cooling systems, for instance, offer superior heat dissipation compared to traditional air cooling methods. By circulating a coolant through microchannels integrated into the chiplet package, these systems can efficiently remove heat from high-power density areas. This allows for more compact chiplet arrangements without compromising thermal performance.

Another strategy involves the strategic placement of chiplets based on their thermal characteristics. By positioning high-power chiplets adjacent to lower-power ones, heat can be more evenly distributed across the package. This approach, known as thermal-aware placement, helps prevent localized hotspots and improves overall thermal efficiency. Additionally, incorporating thermal interface materials (TIMs) with high thermal conductivity between chiplets and heat spreaders can further enhance heat transfer.

Advanced packaging technologies also play a crucial role in thermal management. Three-dimensional integrated circuits (3D-ICs) and through-silicon vias (TSVs) enable vertical stacking of chiplets, which can improve thermal performance by reducing the distance heat must travel to reach cooling solutions. These technologies also allow for the integration of dedicated thermal management layers within the chiplet stack.

Dynamic thermal management techniques are increasingly important for optimizing chiplet arrangements. These methods involve real-time monitoring of temperature across the chiplet package and adjusting performance parameters accordingly. Techniques such as dynamic voltage and frequency scaling (DVFS) can be applied selectively to individual chiplets, allowing for fine-grained control over power consumption and heat generation.

Emerging materials and manufacturing processes are also contributing to improved thermal management in chiplet arrangements. For example, the development of high thermal conductivity substrates and advanced heat spreading materials can significantly enhance heat dissipation from chiplets. Additionally, novel manufacturing techniques, such as heterogeneous integration, allow for the incorporation of specialized cooling structures directly into the chiplet package.

As chiplet technology continues to evolve, thermal management strategies must adapt to meet the increasing demands of high-volume data management. The integration of artificial intelligence and machine learning algorithms for predictive thermal management holds promise for further optimizing chiplet arrangements. These advanced techniques can anticipate thermal issues and proactively adjust system parameters to maintain optimal performance while minimizing heat-related challenges.

One key approach to thermal management in chiplet arrangements is the implementation of advanced cooling solutions. Liquid cooling systems, for instance, offer superior heat dissipation compared to traditional air cooling methods. By circulating a coolant through microchannels integrated into the chiplet package, these systems can efficiently remove heat from high-power density areas. This allows for more compact chiplet arrangements without compromising thermal performance.

Another strategy involves the strategic placement of chiplets based on their thermal characteristics. By positioning high-power chiplets adjacent to lower-power ones, heat can be more evenly distributed across the package. This approach, known as thermal-aware placement, helps prevent localized hotspots and improves overall thermal efficiency. Additionally, incorporating thermal interface materials (TIMs) with high thermal conductivity between chiplets and heat spreaders can further enhance heat transfer.

Advanced packaging technologies also play a crucial role in thermal management. Three-dimensional integrated circuits (3D-ICs) and through-silicon vias (TSVs) enable vertical stacking of chiplets, which can improve thermal performance by reducing the distance heat must travel to reach cooling solutions. These technologies also allow for the integration of dedicated thermal management layers within the chiplet stack.

Dynamic thermal management techniques are increasingly important for optimizing chiplet arrangements. These methods involve real-time monitoring of temperature across the chiplet package and adjusting performance parameters accordingly. Techniques such as dynamic voltage and frequency scaling (DVFS) can be applied selectively to individual chiplets, allowing for fine-grained control over power consumption and heat generation.

Emerging materials and manufacturing processes are also contributing to improved thermal management in chiplet arrangements. For example, the development of high thermal conductivity substrates and advanced heat spreading materials can significantly enhance heat dissipation from chiplets. Additionally, novel manufacturing techniques, such as heterogeneous integration, allow for the incorporation of specialized cooling structures directly into the chiplet package.

As chiplet technology continues to evolve, thermal management strategies must adapt to meet the increasing demands of high-volume data management. The integration of artificial intelligence and machine learning algorithms for predictive thermal management holds promise for further optimizing chiplet arrangements. These advanced techniques can anticipate thermal issues and proactively adjust system parameters to maintain optimal performance while minimizing heat-related challenges.

Interconnect Technologies for Chiplets

Interconnect technologies play a crucial role in optimizing chiplet arrangements for high-volume data management. As chiplets become increasingly prevalent in modern computing architectures, the need for efficient and high-performance interconnects has become paramount. These technologies enable seamless communication between different chiplets, allowing for improved data transfer rates and reduced latency.

One of the primary interconnect technologies for chiplets is the Advanced Interface Bus (AIB), developed by Intel. AIB provides a high-bandwidth, low-power interface that allows for flexible chiplet integration. It supports data rates up to 2 Gbps per pin, making it suitable for high-volume data management applications. The AIB standard has been adopted by several industry players, promoting interoperability and standardization in chiplet-based designs.

Another significant interconnect technology is TSMC's Chip-on-Wafer-on-Substrate (CoWoS) platform. CoWoS enables the integration of multiple chiplets on a single interposer, facilitating high-bandwidth connections between different components. This technology has been particularly effective in addressing the challenges of high-performance computing and artificial intelligence applications, where data movement is a critical factor.

AMD's Infinity Fabric is another notable interconnect technology designed for chiplet-based architectures. It provides a scalable and coherent interface that allows for efficient communication between different chiplets within a processor. The Infinity Fabric has been instrumental in AMD's success with multi-chip module (MCM) designs, enabling high-performance processors with optimized data management capabilities.

Emerging interconnect technologies are also pushing the boundaries of chiplet integration. Silicon photonics, for instance, offers the potential for ultra-high-bandwidth connections between chiplets using optical signals. This technology could revolutionize data transfer rates in chiplet-based systems, particularly for applications requiring massive data movement.

As chiplet arrangements become more complex, 3D integration techniques are gaining traction. Technologies like through-silicon vias (TSVs) and micro-bumps enable vertical stacking of chiplets, significantly increasing interconnect density and reducing signal path lengths. These advancements are crucial for optimizing data flow in high-volume data management scenarios.

The development of standardized interconnect protocols, such as the Universal Chiplet Interconnect Express (UCIe), is also shaping the future of chiplet integration. UCIe aims to create a common interface for chiplets from different vendors, promoting interoperability and reducing design complexity. This standardization effort is expected to accelerate the adoption of chiplet-based architectures across various industries.

One of the primary interconnect technologies for chiplets is the Advanced Interface Bus (AIB), developed by Intel. AIB provides a high-bandwidth, low-power interface that allows for flexible chiplet integration. It supports data rates up to 2 Gbps per pin, making it suitable for high-volume data management applications. The AIB standard has been adopted by several industry players, promoting interoperability and standardization in chiplet-based designs.

Another significant interconnect technology is TSMC's Chip-on-Wafer-on-Substrate (CoWoS) platform. CoWoS enables the integration of multiple chiplets on a single interposer, facilitating high-bandwidth connections between different components. This technology has been particularly effective in addressing the challenges of high-performance computing and artificial intelligence applications, where data movement is a critical factor.

AMD's Infinity Fabric is another notable interconnect technology designed for chiplet-based architectures. It provides a scalable and coherent interface that allows for efficient communication between different chiplets within a processor. The Infinity Fabric has been instrumental in AMD's success with multi-chip module (MCM) designs, enabling high-performance processors with optimized data management capabilities.

Emerging interconnect technologies are also pushing the boundaries of chiplet integration. Silicon photonics, for instance, offers the potential for ultra-high-bandwidth connections between chiplets using optical signals. This technology could revolutionize data transfer rates in chiplet-based systems, particularly for applications requiring massive data movement.

As chiplet arrangements become more complex, 3D integration techniques are gaining traction. Technologies like through-silicon vias (TSVs) and micro-bumps enable vertical stacking of chiplets, significantly increasing interconnect density and reducing signal path lengths. These advancements are crucial for optimizing data flow in high-volume data management scenarios.

The development of standardized interconnect protocols, such as the Universal Chiplet Interconnect Express (UCIe), is also shaping the future of chiplet integration. UCIe aims to create a common interface for chiplets from different vendors, promoting interoperability and reducing design complexity. This standardization effort is expected to accelerate the adoption of chiplet-based architectures across various industries.

Unlock deeper insights with Patsnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with Patsnap Eureka AI Agent Platform!