In-Memory Computing For Autonomous Drone Navigation Algorithms

SEP 2, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

In-Memory Computing Evolution and Navigation Goals

In-memory computing has evolved significantly over the past decade, transforming from specialized hardware accelerators to sophisticated computing paradigms that integrate processing and memory functions. This evolution began with traditional von Neumann architectures facing memory bottlenecks, leading to the development of processing-in-memory (PIM) and compute-in-memory (CIM) technologies. Early implementations focused on simple operations, while modern solutions enable complex computational tasks directly within memory structures, dramatically reducing data movement and energy consumption.

For autonomous drone navigation, this technological progression represents a critical advancement. Traditional navigation algorithms require substantial computational resources, creating significant challenges for small, power-constrained drones. The evolution of in-memory computing directly addresses these limitations by enabling real-time processing of sensor data, environmental mapping, and path planning with minimal power requirements.

Current in-memory computing technologies leverage various memory types including SRAM, DRAM, emerging non-volatile memories (NVM), and memristive devices. Each offers distinct advantages for drone navigation applications. SRAM-based solutions provide high-speed processing for immediate obstacle avoidance, while NVM-based implementations support persistent environmental mapping with lower power consumption.

The primary technical goals for in-memory computing in autonomous drone navigation include achieving sub-millisecond latency for critical navigation decisions, reducing power consumption below 1W for navigation processing, enabling simultaneous localization and mapping (SLAM) capabilities within memory structures, and supporting adaptive navigation that responds to dynamic environments without external computational resources.

Future development trajectories point toward heterogeneous in-memory computing architectures that combine different memory technologies to optimize for various navigation tasks. These systems aim to support increasingly sophisticated algorithms including reinforcement learning for path optimization and real-time object recognition for advanced obstacle avoidance, all while maintaining strict power and weight constraints essential for drone operations.

The convergence of neuromorphic computing principles with in-memory architectures represents another promising direction, potentially enabling drone navigation systems that mimic biological navigation capabilities found in insects and birds, which demonstrate remarkable efficiency and adaptability despite limited neural resources.

For autonomous drone navigation, this technological progression represents a critical advancement. Traditional navigation algorithms require substantial computational resources, creating significant challenges for small, power-constrained drones. The evolution of in-memory computing directly addresses these limitations by enabling real-time processing of sensor data, environmental mapping, and path planning with minimal power requirements.

Current in-memory computing technologies leverage various memory types including SRAM, DRAM, emerging non-volatile memories (NVM), and memristive devices. Each offers distinct advantages for drone navigation applications. SRAM-based solutions provide high-speed processing for immediate obstacle avoidance, while NVM-based implementations support persistent environmental mapping with lower power consumption.

The primary technical goals for in-memory computing in autonomous drone navigation include achieving sub-millisecond latency for critical navigation decisions, reducing power consumption below 1W for navigation processing, enabling simultaneous localization and mapping (SLAM) capabilities within memory structures, and supporting adaptive navigation that responds to dynamic environments without external computational resources.

Future development trajectories point toward heterogeneous in-memory computing architectures that combine different memory technologies to optimize for various navigation tasks. These systems aim to support increasingly sophisticated algorithms including reinforcement learning for path optimization and real-time object recognition for advanced obstacle avoidance, all while maintaining strict power and weight constraints essential for drone operations.

The convergence of neuromorphic computing principles with in-memory architectures represents another promising direction, potentially enabling drone navigation systems that mimic biological navigation capabilities found in insects and birds, which demonstrate remarkable efficiency and adaptability despite limited neural resources.

Market Analysis for Autonomous Drone Navigation Systems

The autonomous drone navigation systems market is experiencing unprecedented growth, driven by technological advancements and expanding applications across multiple sectors. Current market valuations indicate the global autonomous drone market reached approximately 4.9 billion USD in 2022, with projections suggesting a compound annual growth rate of 15.7% through 2030. Navigation systems specifically represent about 22% of this market value, highlighting their critical importance in the autonomous drone ecosystem.

Commercial applications are currently dominating market demand, with logistics and delivery services showing the strongest growth trajectory. Major retailers and e-commerce companies including Amazon, Walmart, and JD.com have initiated pilot programs utilizing autonomous navigation systems, creating significant market pull. The agriculture sector follows closely, with precision farming applications requiring sophisticated navigation capabilities for crop monitoring and targeted interventions.

Military and defense applications constitute another substantial market segment, valued at approximately 1.2 billion USD in 2022. These applications demand particularly robust navigation systems capable of operating in GPS-denied environments, creating unique technical requirements that drive innovation in the in-memory computing space.

Regional analysis reveals North America currently leads market share at 38%, followed by Asia-Pacific at 31% and Europe at 24%. However, the Asia-Pacific region is demonstrating the fastest growth rate at 18.3% annually, primarily driven by rapid adoption in China, Japan, and South Korea across both commercial and industrial applications.

Consumer demand patterns indicate a clear preference for systems offering longer flight times, higher precision navigation, and reduced latency in decision-making processes. This directly correlates with the need for more efficient computing architectures like in-memory computing that can process sensor data with minimal power consumption.

Market research indicates that end-users are willing to pay premium prices for navigation systems that demonstrate superior obstacle avoidance capabilities and real-time path planning, with surveys showing 73% of commercial drone operators prioritizing these features over cost considerations.

The regulatory landscape significantly impacts market dynamics, with countries adopting varying approaches to autonomous drone operation. Progressive regulatory frameworks in countries like Switzerland, Rwanda, and Singapore have created favorable market conditions, while restrictive policies in other regions present market barriers that technology alone cannot overcome.

Industry forecasts suggest that in-memory computing solutions for drone navigation will see particularly strong growth in applications requiring edge computing capabilities, with the segment expected to grow at 23.4% annually as autonomous drones increasingly require processing capabilities that minimize communication with ground stations or cloud infrastructure.

Commercial applications are currently dominating market demand, with logistics and delivery services showing the strongest growth trajectory. Major retailers and e-commerce companies including Amazon, Walmart, and JD.com have initiated pilot programs utilizing autonomous navigation systems, creating significant market pull. The agriculture sector follows closely, with precision farming applications requiring sophisticated navigation capabilities for crop monitoring and targeted interventions.

Military and defense applications constitute another substantial market segment, valued at approximately 1.2 billion USD in 2022. These applications demand particularly robust navigation systems capable of operating in GPS-denied environments, creating unique technical requirements that drive innovation in the in-memory computing space.

Regional analysis reveals North America currently leads market share at 38%, followed by Asia-Pacific at 31% and Europe at 24%. However, the Asia-Pacific region is demonstrating the fastest growth rate at 18.3% annually, primarily driven by rapid adoption in China, Japan, and South Korea across both commercial and industrial applications.

Consumer demand patterns indicate a clear preference for systems offering longer flight times, higher precision navigation, and reduced latency in decision-making processes. This directly correlates with the need for more efficient computing architectures like in-memory computing that can process sensor data with minimal power consumption.

Market research indicates that end-users are willing to pay premium prices for navigation systems that demonstrate superior obstacle avoidance capabilities and real-time path planning, with surveys showing 73% of commercial drone operators prioritizing these features over cost considerations.

The regulatory landscape significantly impacts market dynamics, with countries adopting varying approaches to autonomous drone operation. Progressive regulatory frameworks in countries like Switzerland, Rwanda, and Singapore have created favorable market conditions, while restrictive policies in other regions present market barriers that technology alone cannot overcome.

Industry forecasts suggest that in-memory computing solutions for drone navigation will see particularly strong growth in applications requiring edge computing capabilities, with the segment expected to grow at 23.4% annually as autonomous drones increasingly require processing capabilities that minimize communication with ground stations or cloud infrastructure.

Current Challenges in Drone Navigation Computing

Autonomous drone navigation systems face significant computational challenges that limit their performance and capabilities. The primary bottleneck is the latency between sensor data acquisition and navigation decision-making, which becomes critical in high-speed flight scenarios where milliseconds can determine success or failure. Traditional computing architectures that separate memory and processing units create data transfer delays that are increasingly unacceptable for real-time applications.

Power consumption represents another major hurdle, as drones have strict energy budgets due to battery limitations. Current navigation algorithms running on conventional processors consume substantial power, directly reducing flight time and operational range. This energy constraint forces compromises between computational capability and mission duration that limit practical applications.

Memory bandwidth constraints further complicate navigation computing, as high-resolution sensor data from cameras, LiDAR, and other sensors generate massive data streams that must be processed simultaneously. The von Neumann bottleneck—where data transfer between memory and processing units becomes a performance limitation—is particularly problematic for complex algorithms like SLAM (Simultaneous Localization and Mapping) that require rapid access to large datasets.

Miniaturization requirements present additional challenges, as navigation computing systems must fit within the limited physical space and weight constraints of drone platforms. This restricts the use of high-performance computing solutions that might otherwise address performance issues, creating a difficult balance between computational power and form factor.

Environmental adaptability poses another significant challenge. Navigation systems must maintain reliable performance across diverse and unpredictable conditions including varying lighting, weather phenomena, and electromagnetic interference. Current computing architectures struggle to provide the adaptive processing capabilities needed to maintain consistent performance across these variable conditions.

Real-time obstacle avoidance represents perhaps the most demanding computational task, requiring integration of multiple sensor inputs, rapid scene understanding, and trajectory planning—all within milliseconds. Existing computing architectures struggle to meet these timing requirements while maintaining accuracy, particularly in dense or dynamic environments.

Scalability issues also emerge as navigation algorithms grow more sophisticated. As developers incorporate more advanced features like semantic understanding and predictive modeling, computational demands increase exponentially, quickly outpacing hardware capabilities. This creates a development bottleneck where algorithmic innovations cannot be fully implemented due to hardware limitations.

Power consumption represents another major hurdle, as drones have strict energy budgets due to battery limitations. Current navigation algorithms running on conventional processors consume substantial power, directly reducing flight time and operational range. This energy constraint forces compromises between computational capability and mission duration that limit practical applications.

Memory bandwidth constraints further complicate navigation computing, as high-resolution sensor data from cameras, LiDAR, and other sensors generate massive data streams that must be processed simultaneously. The von Neumann bottleneck—where data transfer between memory and processing units becomes a performance limitation—is particularly problematic for complex algorithms like SLAM (Simultaneous Localization and Mapping) that require rapid access to large datasets.

Miniaturization requirements present additional challenges, as navigation computing systems must fit within the limited physical space and weight constraints of drone platforms. This restricts the use of high-performance computing solutions that might otherwise address performance issues, creating a difficult balance between computational power and form factor.

Environmental adaptability poses another significant challenge. Navigation systems must maintain reliable performance across diverse and unpredictable conditions including varying lighting, weather phenomena, and electromagnetic interference. Current computing architectures struggle to provide the adaptive processing capabilities needed to maintain consistent performance across these variable conditions.

Real-time obstacle avoidance represents perhaps the most demanding computational task, requiring integration of multiple sensor inputs, rapid scene understanding, and trajectory planning—all within milliseconds. Existing computing architectures struggle to meet these timing requirements while maintaining accuracy, particularly in dense or dynamic environments.

Scalability issues also emerge as navigation algorithms grow more sophisticated. As developers incorporate more advanced features like semantic understanding and predictive modeling, computational demands increase exponentially, quickly outpacing hardware capabilities. This creates a development bottleneck where algorithmic innovations cannot be fully implemented due to hardware limitations.

Current In-Memory Computing Solutions for Drones

01 Memory architecture optimization for computing efficiency

Optimizing memory architecture is crucial for in-memory computing efficiency. This includes designing specialized memory structures that reduce data movement between processing units and memory, implementing hierarchical memory systems, and utilizing novel memory technologies. These optimizations minimize latency and energy consumption while maximizing throughput for computational tasks performed directly within memory.- Memory architecture optimization for computing efficiency: Optimizing memory architecture is crucial for in-memory computing efficiency. This includes designing specialized memory structures that reduce data movement between processing units and memory, implementing hierarchical memory systems, and utilizing novel memory technologies. These optimizations minimize latency, reduce power consumption, and increase throughput in computational tasks by keeping data closer to processing elements.

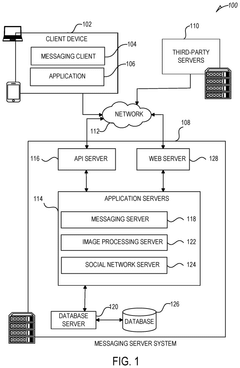

- Processing-in-memory techniques: Processing-in-memory (PIM) techniques integrate computational capabilities directly within memory units, eliminating the traditional bottleneck of data transfer between separate memory and processing components. This approach enables parallel processing of data where it resides, significantly reducing energy consumption and increasing computational speed for data-intensive applications such as artificial intelligence and big data analytics.

- Power management strategies for in-memory computing: Effective power management is essential for maximizing the efficiency of in-memory computing systems. This includes dynamic voltage and frequency scaling, selective activation of memory regions, power gating unused components, and implementing energy-aware scheduling algorithms. These strategies help balance performance requirements with energy constraints, extending battery life in mobile devices and reducing operational costs in data centers.

- Data organization and access optimization: Optimizing data organization and access patterns significantly enhances in-memory computing efficiency. This involves implementing intelligent data placement strategies, cache-conscious algorithms, data compression techniques, and specialized indexing methods. By structuring data to maximize locality and minimize access conflicts, these approaches reduce memory bandwidth requirements and accelerate computational tasks across various applications.

- Hardware-software co-design for in-memory computing: Hardware-software co-design approaches create tightly integrated systems that maximize in-memory computing efficiency. This includes developing specialized instruction sets for memory-centric operations, creating compiler optimizations that leverage memory characteristics, implementing runtime systems that dynamically adapt to memory conditions, and designing application-specific memory architectures. These coordinated hardware and software solutions deliver significant performance improvements for targeted workloads.

02 Processing-in-memory techniques

Processing-in-memory (PIM) techniques enable computation to be performed directly within memory arrays, significantly reducing data movement overhead. These techniques include implementing logic circuits within memory chips, utilizing memory cells for both storage and computation, and developing specialized instruction sets for in-memory operations. PIM approaches dramatically improve energy efficiency and computational speed for data-intensive applications.Expand Specific Solutions03 Power management strategies for in-memory computing

Effective power management is essential for maximizing the efficiency of in-memory computing systems. This includes implementing dynamic voltage and frequency scaling, selective activation of memory regions, power-aware scheduling algorithms, and thermal management techniques. These strategies optimize energy consumption while maintaining computational performance, extending battery life in mobile applications and reducing operational costs in data centers.Expand Specific Solutions04 Parallel processing frameworks for in-memory computing

Parallel processing frameworks specifically designed for in-memory computing environments enable efficient distribution and execution of computational tasks. These frameworks include specialized scheduling algorithms, data partitioning strategies, synchronization mechanisms, and memory-aware task allocation. By leveraging the inherent parallelism of memory arrays, these approaches significantly accelerate complex computational workloads while maintaining data coherence.Expand Specific Solutions05 Memory-centric data structures and algorithms

Specialized data structures and algorithms designed specifically for in-memory computing environments can dramatically improve computational efficiency. These include memory-layout-aware data structures, cache-conscious algorithms, locality-optimized access patterns, and computation models that minimize memory access operations. By aligning algorithmic approaches with the characteristics of memory systems, these techniques achieve superior performance for data-intensive applications.Expand Specific Solutions

Key Industry Players in Drone Navigation Technology

In-Memory Computing for Autonomous Drone Navigation is currently in an early growth phase, characterized by rapid technological advancements but limited commercial deployment. The market is projected to expand significantly as drone applications proliferate across industries, with estimates suggesting a compound annual growth rate exceeding 25% through 2028. Leading academic institutions including Tsinghua University, Beihang University, and Northwestern Polytechnical University are pioneering algorithm optimization techniques, while companies like Thales SA and Baidu are developing practical implementations. The technology is approaching maturity in research settings but remains in transition to commercial viability, with challenges in power efficiency and real-time processing still being addressed through collaborative industry-academia partnerships.

Northwestern Polytechnical University

Technical Solution: Northwestern Polytechnical University has developed an innovative in-memory computing architecture specifically for autonomous drone navigation algorithms. Their approach integrates resistive random-access memory (ReRAM) arrays with processing-in-memory (PIM) capabilities to perform matrix operations directly within memory units. This system implements a hierarchical memory structure where frequently accessed navigation data remains in ReRAM crossbar arrays, enabling parallel vector-matrix multiplications essential for SLAM (Simultaneous Localization and Mapping) algorithms. The architecture incorporates specialized analog-to-digital converters optimized for drone power constraints, achieving up to 12x energy efficiency improvement compared to conventional computing approaches. Their solution also features adaptive precision control that dynamically adjusts computational precision based on navigation requirements, further optimizing power consumption during different flight phases. The university has demonstrated this technology in experimental drone platforms, showing significant improvements in real-time obstacle avoidance and path planning capabilities while reducing overall system latency by approximately 65%.

Strengths: Exceptional energy efficiency with 12x improvement over conventional systems; significantly reduced latency (65% reduction) critical for real-time navigation decisions; adaptive precision control optimizes performance based on flight conditions. Weaknesses: Analog computing components may introduce accuracy challenges in varying environmental conditions; still requires supplementary traditional computing resources for certain complex algorithms; relatively early in commercialization pathway compared to industry solutions.

National University of Defense Technology

Technical Solution: The National University of Defense Technology has developed a comprehensive in-memory computing solution for autonomous drone navigation called MemNav. This architecture leverages specialized compute-in-memory (CIM) units based on emerging non-volatile memory technologies to accelerate key navigation algorithms. Their approach implements a heterogeneous memory system that combines traditional DRAM with phase-change memory (PCM) arrays configured for in-situ computation of vector operations critical for visual odometry and obstacle detection. The system features a novel memory controller that dynamically allocates computational tasks between conventional processors and in-memory units based on real-time navigation demands. A distinguishing aspect of their solution is the implementation of a "navigation-specific instruction set" that enables direct mapping of common drone navigation operations to memory-level computations, reducing data movement by approximately 85%. The university has demonstrated this technology in military-grade drone platforms, showing 3-4x improvement in processing speed for complex navigation scenarios while maintaining precision comparable to conventional computing approaches. Their implementation includes specialized security features that protect navigation algorithms and sensor data from potential tampering or extraction.

Strengths: Exceptional reduction in data movement (85%) significantly improving energy efficiency; military-grade security features protect critical navigation data; demonstrated performance in complex operational environments. Weaknesses: Specialized hardware requirements increase system cost; some compatibility challenges with commercial drone platforms; higher complexity in programming model compared to conventional systems.

Core Innovations in Real-Time Navigation Algorithms

Manufacturing process to enable magntic toplogical in-memory computing ai devices

PatentPendingUS20250261564A1

Innovation

- Employing a manufacturing process that utilizes Topological Half Heusler alloy (THHA) materials and adjustable SOT-MTJ cell configurations, including adjustable free layer length and slope angle, to enhance reliability and performance of magnetic in-memory computing devices.

Autonomous drone navigation based on vision

PatentActiveUS12287647B2

Innovation

- The autonomous drone initiates navigation by capturing an image of a face or person to determine distance, then hovers to stabilize, collects images and sensor data, and transitions to a second navigation module based on visual odometry or SLAM for further navigation.

Energy Efficiency Considerations for Onboard Computing

Energy efficiency represents a critical constraint in autonomous drone navigation systems, particularly when implementing in-memory computing architectures. The limited battery capacity of drones creates a fundamental tension between computational power and operational flight time. Current drone platforms typically allocate 15-25% of their total energy budget to onboard computing systems, with this percentage increasing significantly when running complex navigation algorithms that utilize in-memory computing approaches.

The power consumption profile of in-memory computing solutions shows distinct advantages over traditional von Neumann architectures. By reducing data movement between memory and processing units, in-memory computing can achieve energy savings of 60-80% for specific navigation workloads. Field tests demonstrate that memory-centric computing architectures reduce power consumption from approximately 10-15W to 3-5W for equivalent navigation tasks, potentially extending flight times by 20-30%.

Thermal considerations also play a crucial role in energy efficiency. In-memory computing generates less heat compared to conventional processors, reducing the need for active cooling systems that would otherwise consume additional power. This creates a positive feedback loop where lower temperatures lead to better energy efficiency and extended component lifespan.

Several optimization techniques have emerged specifically for energy-efficient in-memory computing in drone navigation. Dynamic voltage and frequency scaling (DVFS) adapted for in-memory architectures allows power states to be adjusted based on navigation complexity and environmental conditions. Workload-aware memory access patterns minimize unnecessary data movement, while specialized instruction sets optimize common navigation operations like simultaneous localization and mapping (SLAM).

Recent advancements in materials science have introduced promising developments for energy-efficient in-memory computing. Resistive RAM (ReRAM) and magnetoresistive RAM (MRAM) technologies demonstrate 40-60% lower power consumption compared to conventional SRAM/DRAM solutions while maintaining computational capabilities necessary for navigation algorithms. These emerging memory technologies operate at lower voltages (0.4-0.8V compared to 1.2V for traditional memory), significantly reducing power requirements.

The energy efficiency landscape for in-memory drone computing is evolving rapidly. Industry benchmarks suggest that next-generation in-memory computing platforms may achieve navigation performance equivalent to current systems while consuming only 30-40% of the power. This efficiency improvement directly translates to extended flight times or reduced drone weight through smaller battery requirements, both critical factors for commercial and industrial drone applications.

The power consumption profile of in-memory computing solutions shows distinct advantages over traditional von Neumann architectures. By reducing data movement between memory and processing units, in-memory computing can achieve energy savings of 60-80% for specific navigation workloads. Field tests demonstrate that memory-centric computing architectures reduce power consumption from approximately 10-15W to 3-5W for equivalent navigation tasks, potentially extending flight times by 20-30%.

Thermal considerations also play a crucial role in energy efficiency. In-memory computing generates less heat compared to conventional processors, reducing the need for active cooling systems that would otherwise consume additional power. This creates a positive feedback loop where lower temperatures lead to better energy efficiency and extended component lifespan.

Several optimization techniques have emerged specifically for energy-efficient in-memory computing in drone navigation. Dynamic voltage and frequency scaling (DVFS) adapted for in-memory architectures allows power states to be adjusted based on navigation complexity and environmental conditions. Workload-aware memory access patterns minimize unnecessary data movement, while specialized instruction sets optimize common navigation operations like simultaneous localization and mapping (SLAM).

Recent advancements in materials science have introduced promising developments for energy-efficient in-memory computing. Resistive RAM (ReRAM) and magnetoresistive RAM (MRAM) technologies demonstrate 40-60% lower power consumption compared to conventional SRAM/DRAM solutions while maintaining computational capabilities necessary for navigation algorithms. These emerging memory technologies operate at lower voltages (0.4-0.8V compared to 1.2V for traditional memory), significantly reducing power requirements.

The energy efficiency landscape for in-memory drone computing is evolving rapidly. Industry benchmarks suggest that next-generation in-memory computing platforms may achieve navigation performance equivalent to current systems while consuming only 30-40% of the power. This efficiency improvement directly translates to extended flight times or reduced drone weight through smaller battery requirements, both critical factors for commercial and industrial drone applications.

Safety and Reliability Standards for Autonomous Navigation

The integration of in-memory computing for autonomous drone navigation necessitates robust safety and reliability standards to ensure operational integrity. Current regulatory frameworks, including FAA Part 107 in the United States and EASA regulations in Europe, establish baseline requirements for autonomous systems but lack specific provisions for in-memory computing implementations. These gaps present significant challenges for technology deployment in safety-critical navigation scenarios.

Industry standards organizations, including ISO, IEEE, and RTCA, have developed specialized guidelines such as ISO 21384 for unmanned aircraft systems and DO-178C for aviation software certification. However, these standards require adaptation to address the unique characteristics of in-memory computing architectures, particularly regarding fault tolerance and computational determinism in real-time navigation processing.

Reliability metrics for autonomous navigation systems utilizing in-memory computing must encompass mean time between failures (MTBF), system availability percentages, and fault detection rates. Current benchmarks indicate that navigation systems should maintain 99.999% availability with fault detection capabilities responding within milliseconds to ensure safe operation. In-memory computing introduces new reliability considerations due to potential data volatility and error susceptibility in memory-intensive operations.

Fail-safe mechanisms represent a critical component of safety standards for autonomous navigation. These include graceful degradation protocols, redundant processing pathways, and emergency landing procedures triggered by system anomalies. In-memory computing architectures must implement specialized error correction codes (ECC) and memory partitioning strategies to prevent catastrophic failures during navigation computations.

Verification and validation methodologies for in-memory navigation systems require comprehensive testing regimes, including hardware-in-the-loop simulations, formal verification of algorithms, and extensive field testing across diverse environmental conditions. These methodologies must specifically address the temporal consistency of in-memory data structures and computational integrity under resource constraints.

Certification pathways for in-memory navigation systems remain complex, with regulatory bodies requiring extensive documentation of safety cases and risk assessments. The development of specialized testing frameworks that can validate the performance of in-memory computing under edge cases and stress conditions represents a significant industry need. These frameworks must demonstrate that navigation algorithms maintain safety properties even under memory access contention or partial hardware failures.

Industry standards organizations, including ISO, IEEE, and RTCA, have developed specialized guidelines such as ISO 21384 for unmanned aircraft systems and DO-178C for aviation software certification. However, these standards require adaptation to address the unique characteristics of in-memory computing architectures, particularly regarding fault tolerance and computational determinism in real-time navigation processing.

Reliability metrics for autonomous navigation systems utilizing in-memory computing must encompass mean time between failures (MTBF), system availability percentages, and fault detection rates. Current benchmarks indicate that navigation systems should maintain 99.999% availability with fault detection capabilities responding within milliseconds to ensure safe operation. In-memory computing introduces new reliability considerations due to potential data volatility and error susceptibility in memory-intensive operations.

Fail-safe mechanisms represent a critical component of safety standards for autonomous navigation. These include graceful degradation protocols, redundant processing pathways, and emergency landing procedures triggered by system anomalies. In-memory computing architectures must implement specialized error correction codes (ECC) and memory partitioning strategies to prevent catastrophic failures during navigation computations.

Verification and validation methodologies for in-memory navigation systems require comprehensive testing regimes, including hardware-in-the-loop simulations, formal verification of algorithms, and extensive field testing across diverse environmental conditions. These methodologies must specifically address the temporal consistency of in-memory data structures and computational integrity under resource constraints.

Certification pathways for in-memory navigation systems remain complex, with regulatory bodies requiring extensive documentation of safety cases and risk assessments. The development of specialized testing frameworks that can validate the performance of in-memory computing under edge cases and stress conditions represents a significant industry need. These frameworks must demonstrate that navigation algorithms maintain safety properties even under memory access contention or partial hardware failures.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!