Ethernet application layer protocol control system and method based on hardware acceleration

An application layer protocol and hardware acceleration technology, which is applied in the computer field, can solve problems such as system instability, failure to recover, and attacks, and achieve the effects of CPU acceleration, reducing the burden on the CPU, and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0021] A kind of Ethernet application layer protocol control system based on hardware acceleration, see figure 1 ,

[0022] Including an FPGA electrically connected to the CPU;

[0023] Described FPGA is provided with a plurality of processing engines, realizes the parallel processing of application layer network protocol packet; Described FPGA is used for receiving application layer network protocol packet, carries out protocol analysis to described application layer network protocol packet, and utilizes multiple parallel The protocol identification algorithm matches the analysis results, and performs corresponding control operations according to the matching results; the control operations include discarding or forwarding application-layer network protocol packets that do not require in-depth processing, and application-layer network protocol packets that will require in-depth processing transmitted to the CPU for processing;

[0024] The FPGA is also used to receive the p...

Embodiment 2

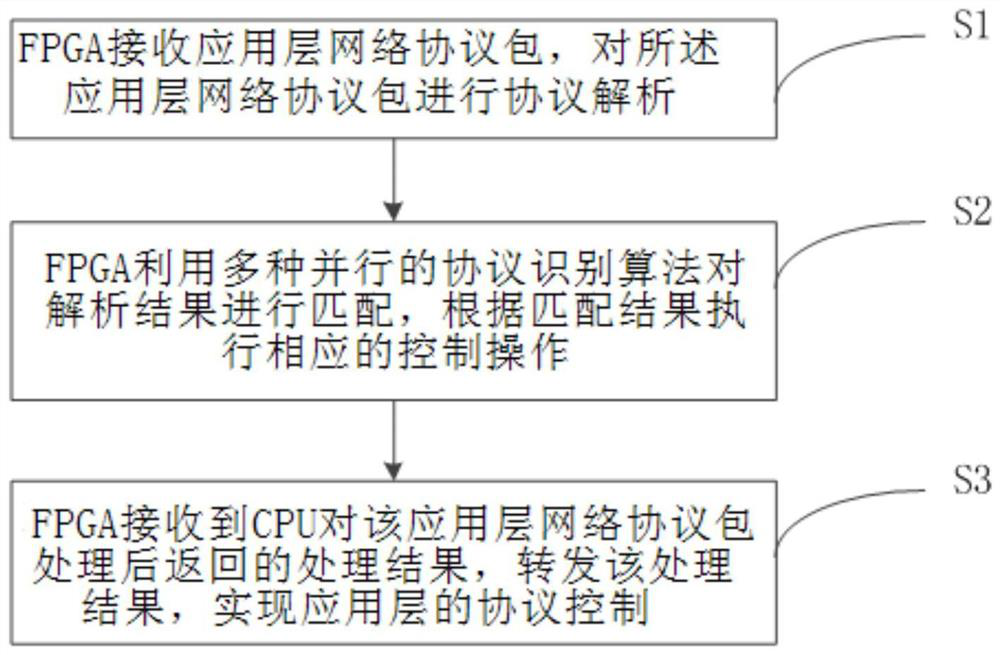

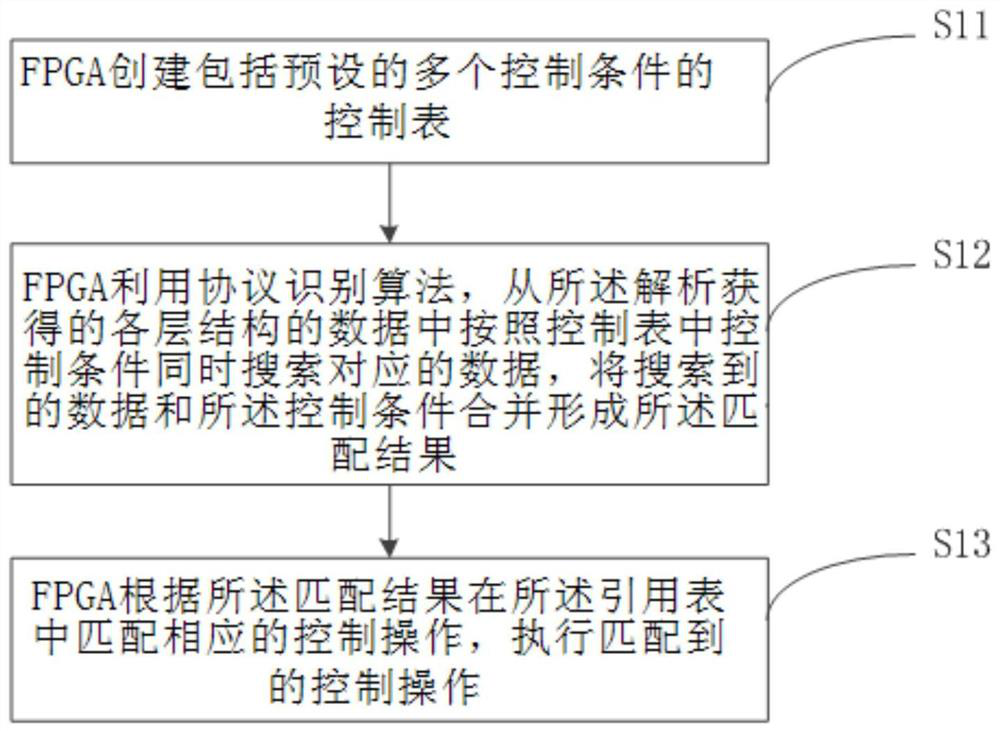

[0049] A kind of Ethernet application layer protocol control method based on hardware acceleration, see figure 2 , including the following steps:

[0050] S1: FPGA receives the application layer network protocol packet, and performs protocol analysis on the application layer network protocol packet;

[0051] S2: The FPGA uses a variety of parallel protocol recognition algorithms to match the analysis results, and performs corresponding control operations according to the matching results; the control operations include discarding or forwarding application layer network protocol packets that do not require in-depth processing, and performing The deeply processed application layer network protocol packet is transmitted to the CPU for processing;

[0052] S3: The FPGA receives the processing result returned by the CPU after processing the application layer network protocol packet, forwards the processing result, and realizes the protocol control of the application layer.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More