Patents

Literature

85results about How to "Accelerated implementation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and system for accelerating UDP protocol

InactiveCN105791315AAccelerated implementationTransmissionProtocol ApplicationProtocol for Carrying Authentication for Network Access

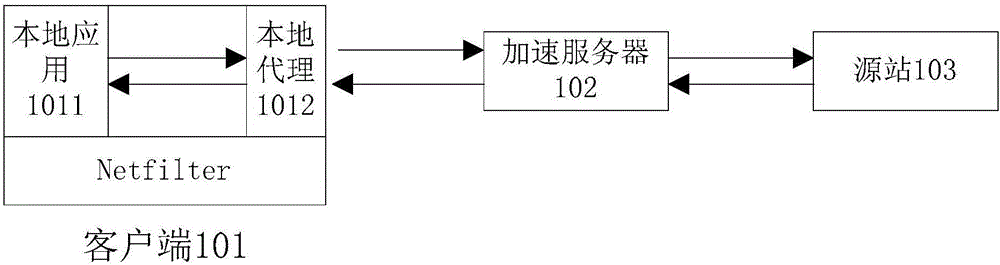

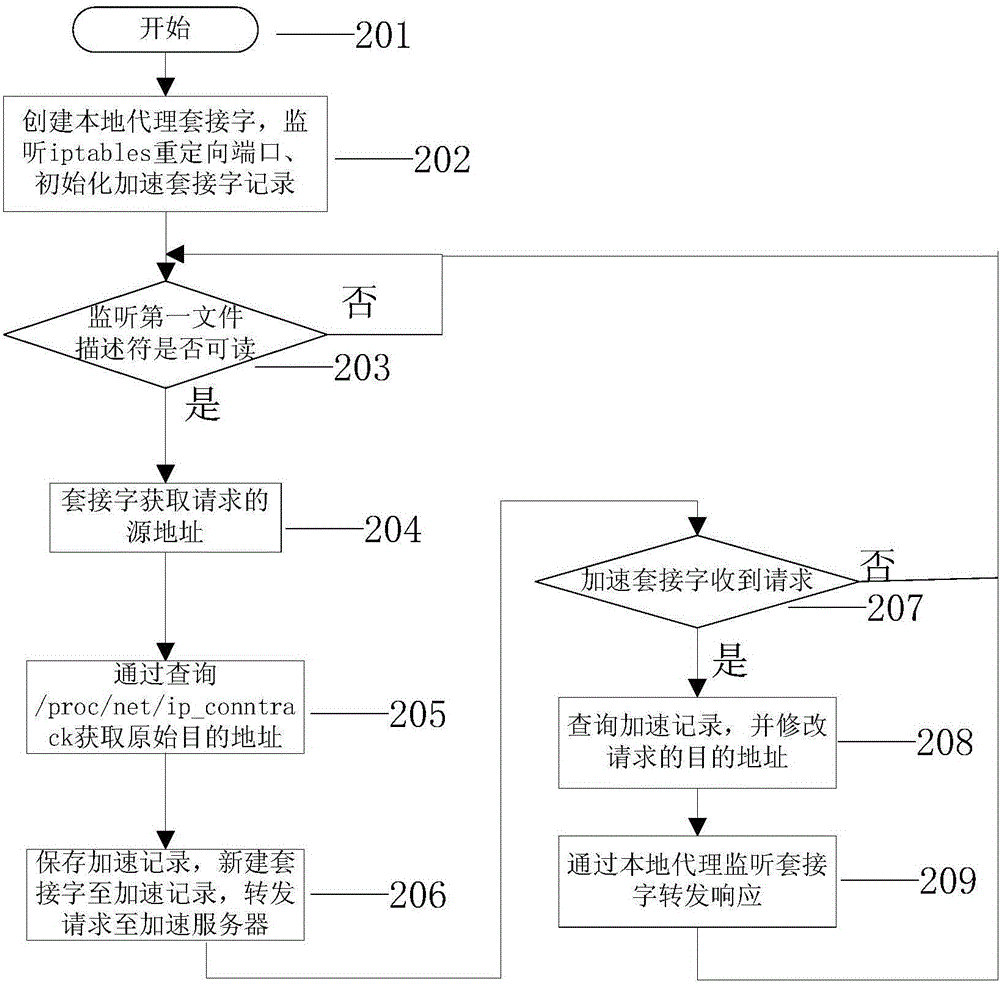

The invention discloses a method and a system for accelerating a UDP protocol. The system comprises a client, an accelerating server and a source station, wherein the client comprises a home agent located in an application layer, to-be-accelerated one or more home applications, and a network filter in an IP layer. After receiving a request, the home agent recognizes a redirecting request from a different application and queries the original destination address, and the destination address and the request are packaged and then transmitted to the accelerating server; the accelerating server analyzes the original destination address and agents the request, and a response is returned to the home agent; and after the home agent receives the response from the accelerating server, an accelerating record is queried, and the response is forwarded to the corresponding home application.

Owner:CHINANETCENT TECH

Decompression method, device and system for FPGA heterogeneous acceleration platform

InactiveCN107027036AIncrease parallelismAccelerateDigital video signal modificationSelective content distributionData informationHardware circuits

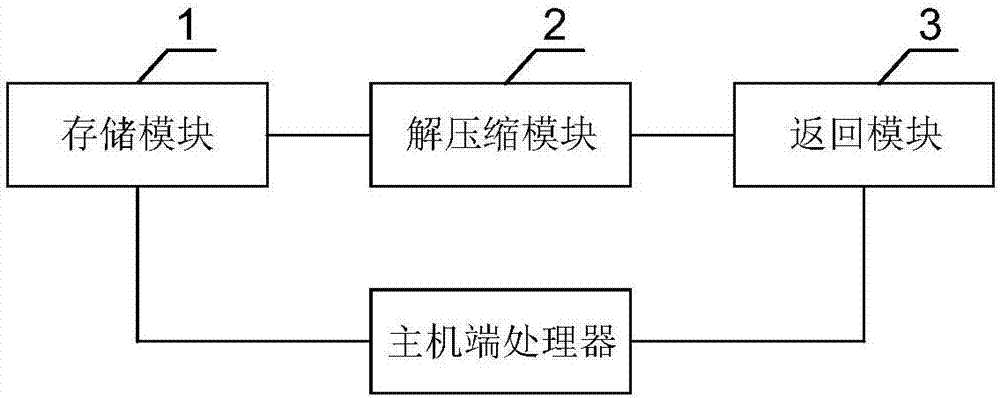

The embodiment of the invention discloses a decompression method, device and system for an FPGA heterogeneous acceleration platform. The method comprises the following steps: receiving first data to be decompressed sent by a host side processor and storing the first data to be decompressed; calling a decompression algorithm implemented by an FPGA hardware circuit according to a start-up instruction and parameter information sent by the host side processor, and decompressing the first data to be decompressed based on the decompression algorithm to obtain decompressed data, wherein the parameter information contains data information corresponding to the first data to be decompressed and a compression relation table; and storing the decompressed data, and returning a completion signal to the host side processor to ensure that the host side processor receives the completion signal and then reads the decompressed data. According to the decompression method, device and system disclosed by the invention, the decompression speed can be increased during use, and the power consumption required during decompression can be reduced.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

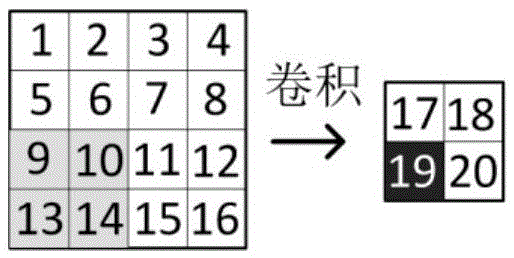

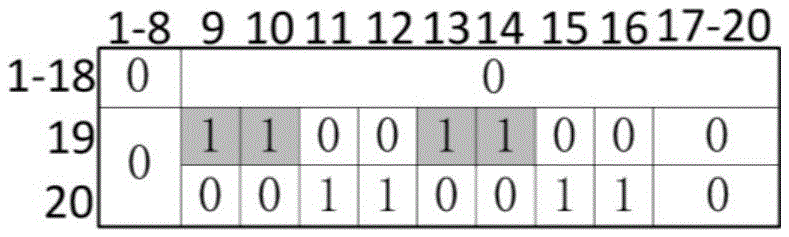

Convolution nerve network acceleration method based on pre-deciding and system

InactiveCN105631519AAccelerated implementationNeural learning methodsLinear classifierCharacteristic point

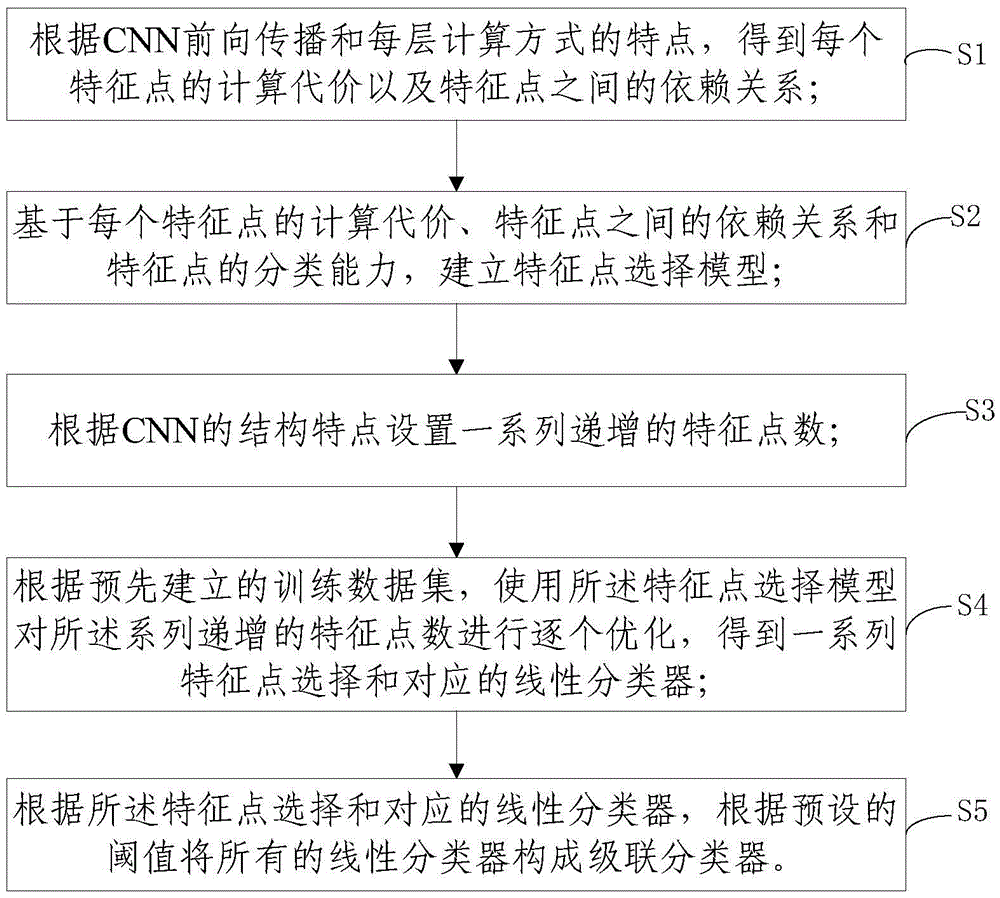

The invention discloses a convolution nerve network acceleration method based on pre-deciding, comprising steps of obtaining a calculation price of each characteristic point and dependency relation between the characteristic points according to the characteristics that CNN forward propagation and each layer calculation mode, establishing a characteristic point selection model on the basis of the calculation price of each characteristic point, the dependency relation between the characteristic points and the classification capability of the characteristic point, configuring a series of incremental characteristic point quantities according to the structure characteristic points, using the characteristic point selection model to perform one-by-one optimization on the series of incrementing characteristic point number according to a training data set which is established in advance to obtain linearity classifiers which are chosen by and corresponding to the series of characteristic points, and constituting all linearity classifiers into cascade classifiers according to the linearity classifiers which are chosen by and corresponding to the series of characteristic points and the preset threshold. The invention fully utilizes the CNN characteristic redundancy, the multilayer characteristic calculation cost variation and multistage characteristic discrimination capability to realize the acceleration of the CNN on the binary classification and the specific object detection.

Owner:BEIJING UNIV OF TECH

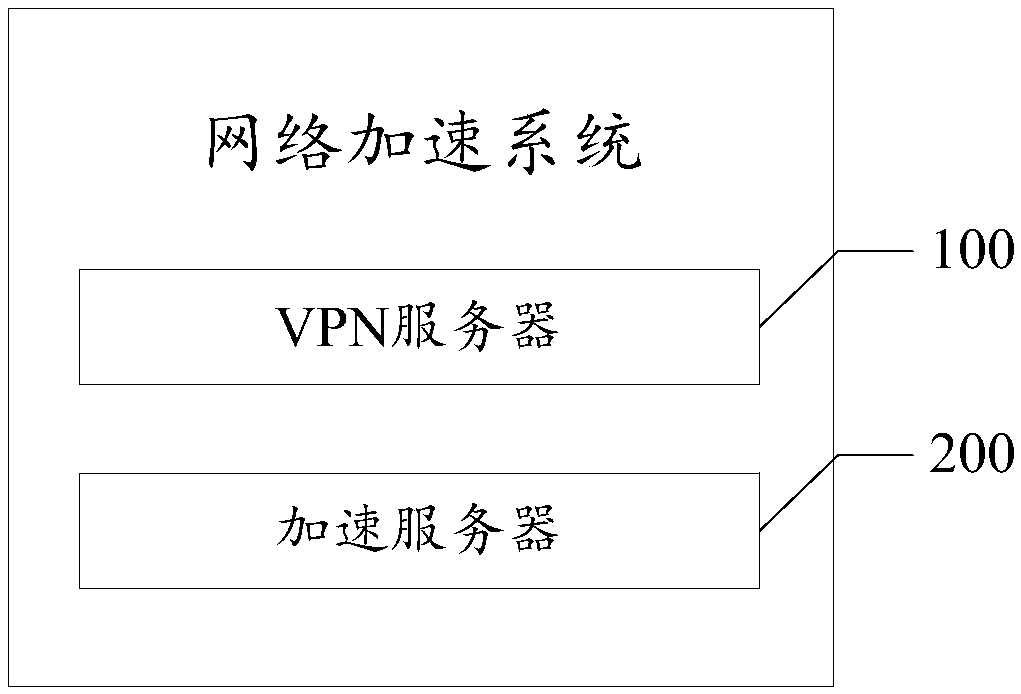

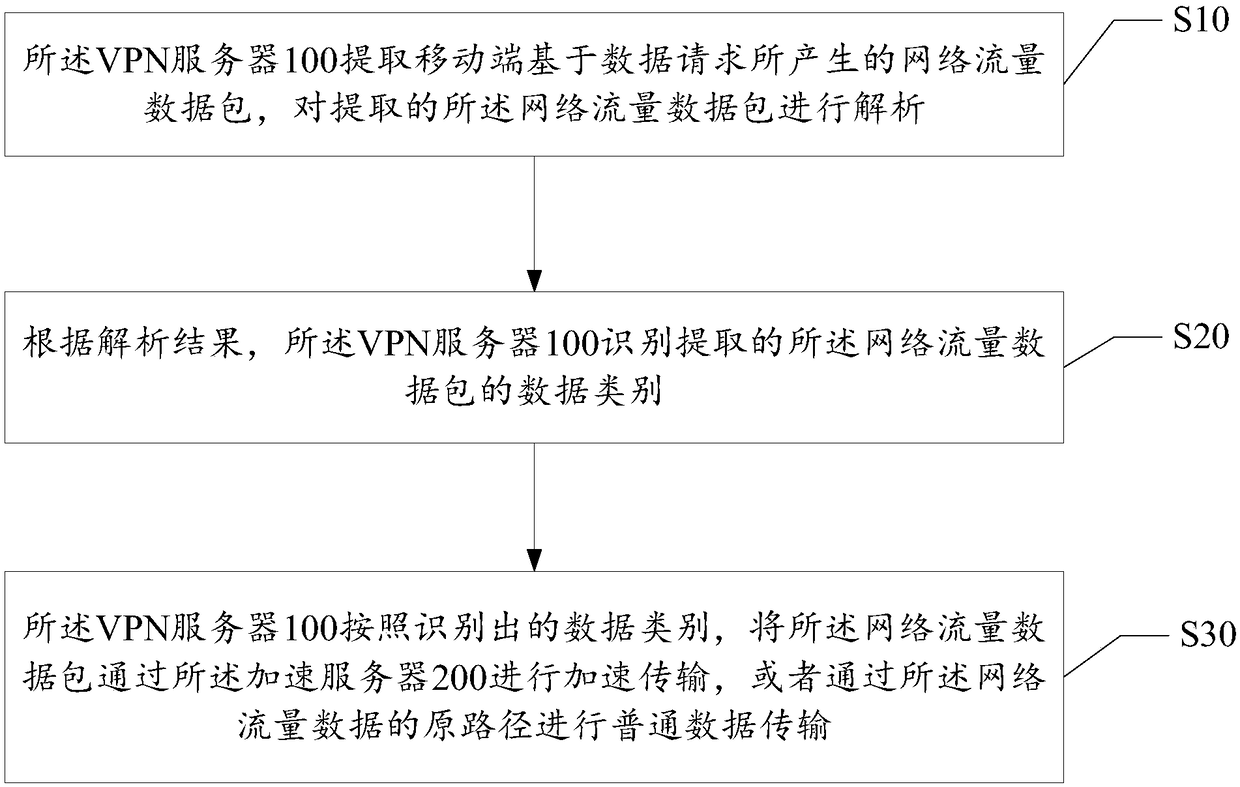

Network accelerating system

ActiveCN108429701AAccelerated implementationSave on acceleration bandwidth costsNetworks interconnectionTraffic capacityNetwork packet

The invention discloses a network accelerating system. The network accelerating system comprises a VPN server and an accelerating server, wherein the VPN server extracts a network traffic data packagegenerated by a mobile terminal based on a data request and analyzes the extracted network traffic data package; the VPN server identifies a data type of the extracted network traffic data package according to an analysis result; the VPN server accelerates transmission of the network traffic data package through the accelerating server according to the identified data type or transmits the networktraffic data package as common data through an original path of the network traffic data. Corresponding network requests are identified and split according to the data type of the network traffic data package, the network bandwidth is accelerated, bandwidth acceleration cost is saved, and unnecessary resource loss is prevented.

Owner:SICHUAN SUBAO NETWORK TECH CO LTD

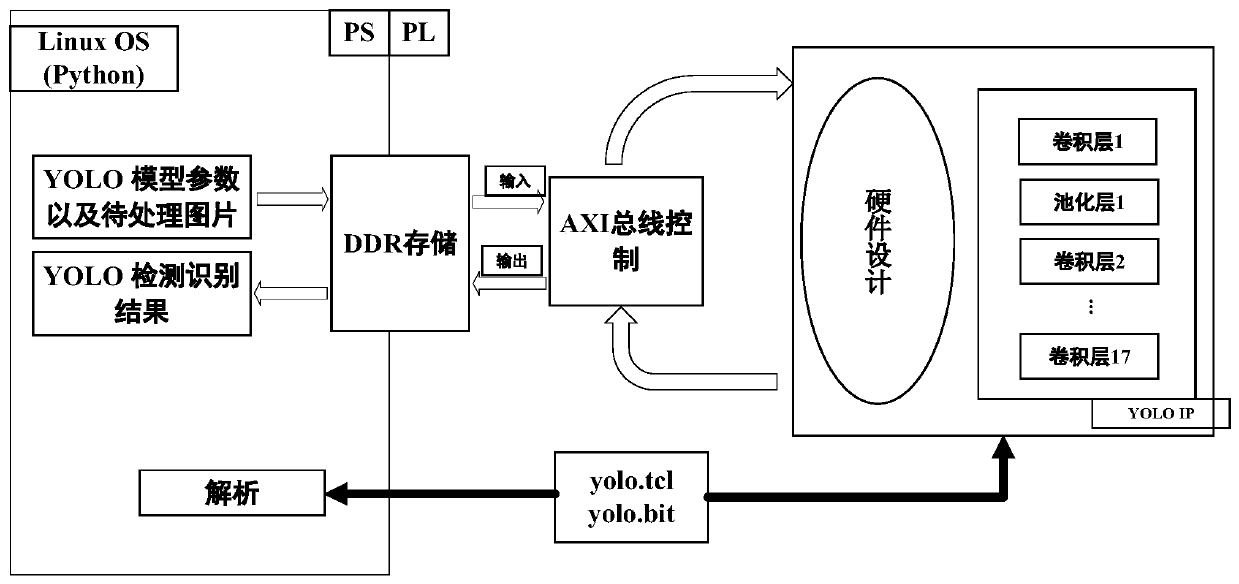

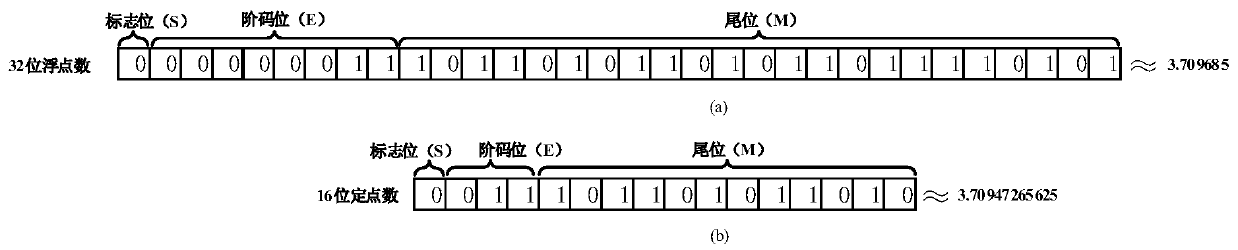

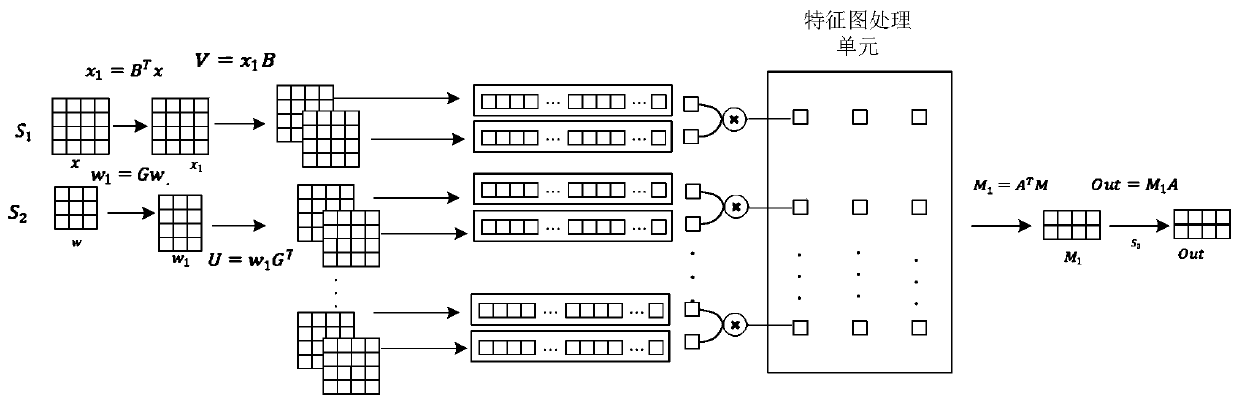

Winograd YOLOv2 target detection model method based on FPGA acceleration

ActiveCN111459877ASave resourcesReduce usageNeural architecturesArchitecture with single central processing unitComputation complexityData path

The invention discloses a Winograd YOLOv2 target detection model method based on FPGA acceleration. The method comprises the steps: employing a PYNQ board card, and enabling a main control chip of thePYNQ board card to comprise a processing system end PS and a programmable logic end PL; wherein the PS end caches a YOLO model and feature map data of a to-be-detected image; the PL end caches the parameters of the YOLO model and the to-be-detected image into an on-chip RAM, deploys a YOLO accelerator with a Winograd algorithm, completes acceleration operation on the model, forms a data path of ahardware accelerator, and realizes target detection of the to-be-detected image; and an operation result of the acceleration circuit can be read out, and image preprocessing and display are carried out. By adopting the technical scheme of the invention, the calculation complexity of the YOLO algorithm can be reduced, the FPGA accelerator storage optimization algorithm reduces the calculation timeof the FPGA when accelerating the YOLO algorithm, accelerates the target detection, and effectively improves the performance of the target detection.

Owner:BEIJING TECHNOLOGY AND BUSINESS UNIVERSITY +1

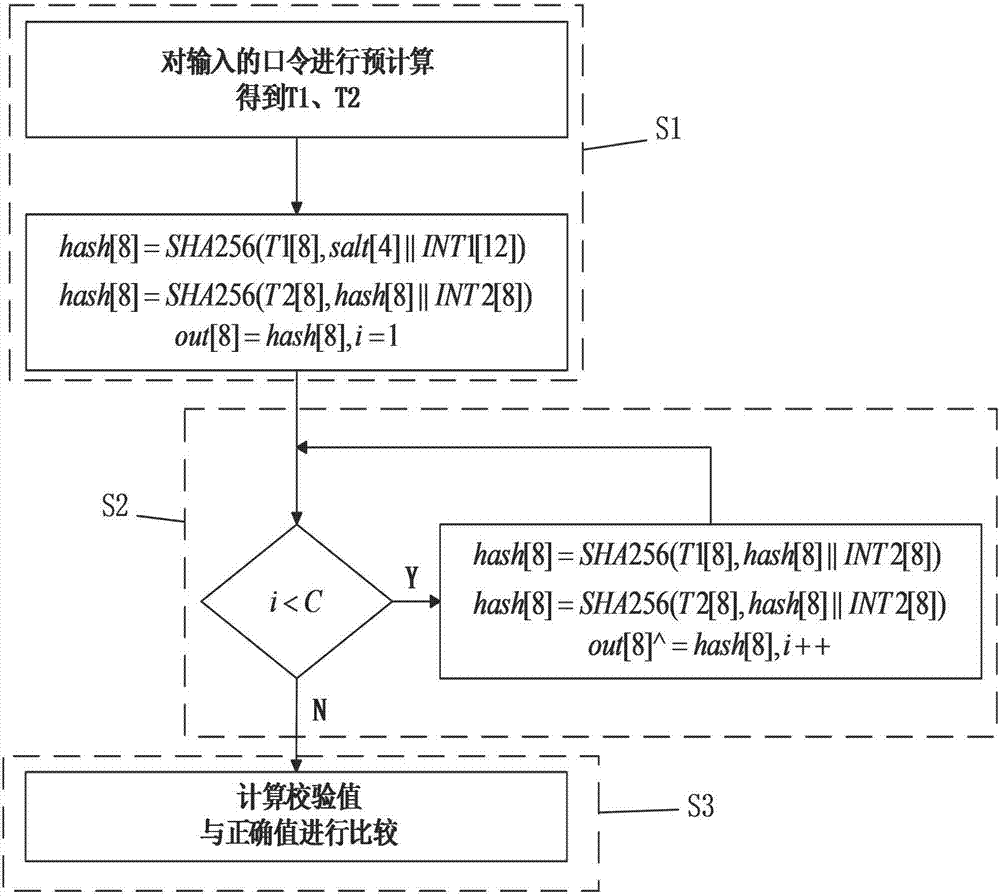

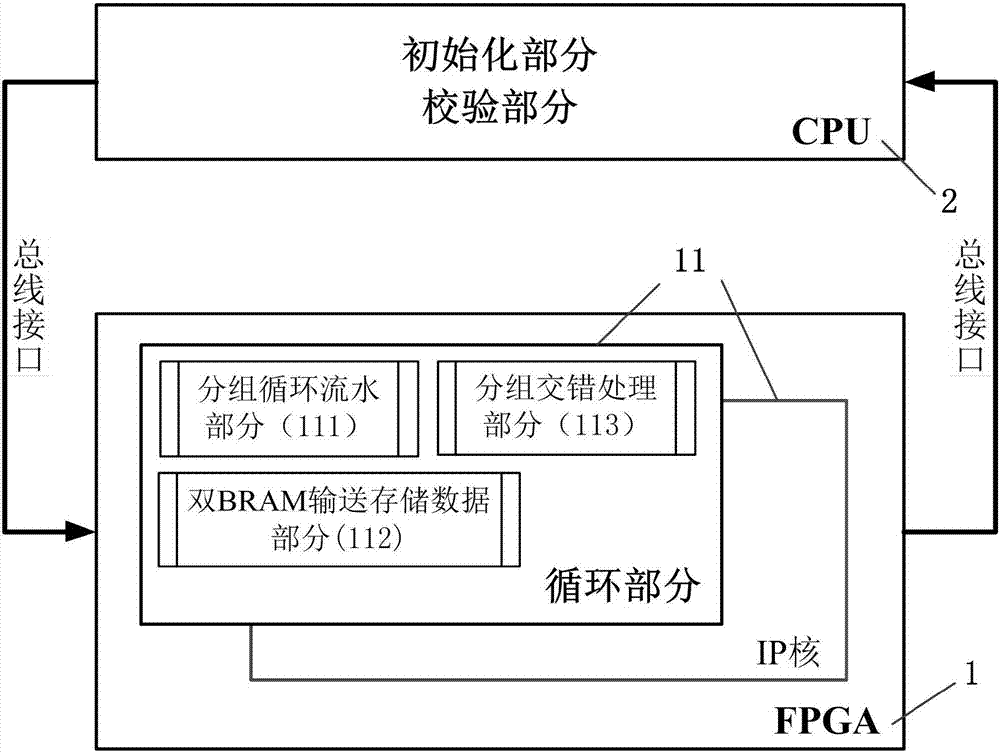

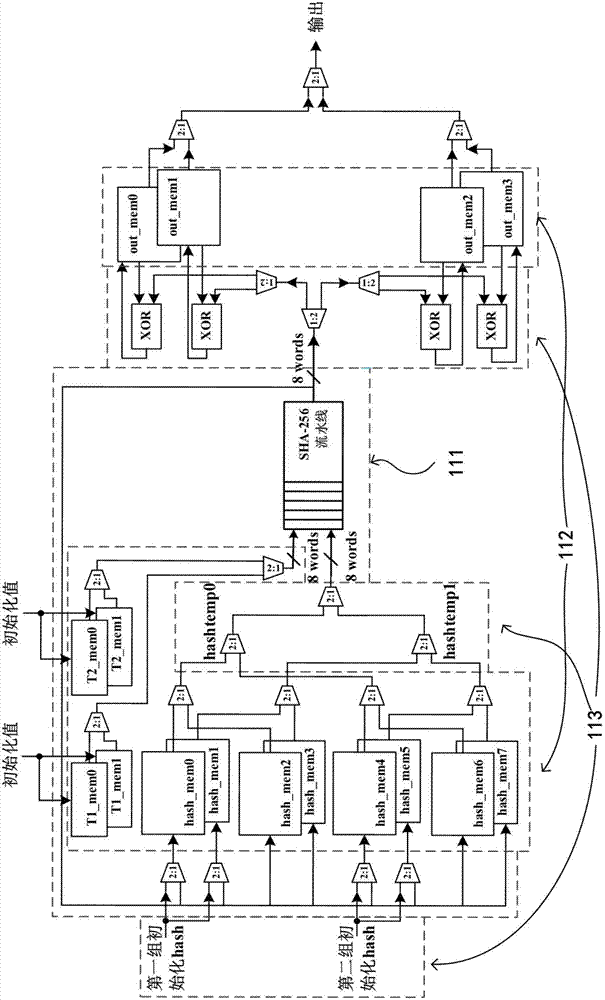

PBKDF2 cryptographic algorithm accelerating method and used device

ActiveCN107135078AImprove abstract abilityImprove reusabilityKey distribution for secure communicationUser identity/authority verificationResource utilizationBus interface

The invention discloses a PBKDF2 cryptographic algorithm accelerating device. The device comprises a CPU+FPGA (Field-Programmable Gate Array) heterogeneous system composed of an FPGA and a universal CPU. The invention further provides a PBKDF2 cryptographic algorithm accelerating method. The method comprises the following steps: 1) initial: computing a pre-computing part and a part before a loop body of a PBKDF2 algorithm is executed in a CPU, and transmitting a computed result to the FPGA via a bus interface; 2) loop: placing a computing-intensive loop body part in the PBKDF2 algorithm onto the FPGA, improving an acceleration effect and a resource utilization efficiency on the FPGA using an optimization means, and transmitting the computed result to the CPU via the bus interface; and 3) check: reading result data obtained after FPGA accelerated computing, and performing computed result summarization as well as check value computation and judgment.

Owner:北京骏戎嘉速科技有限公司

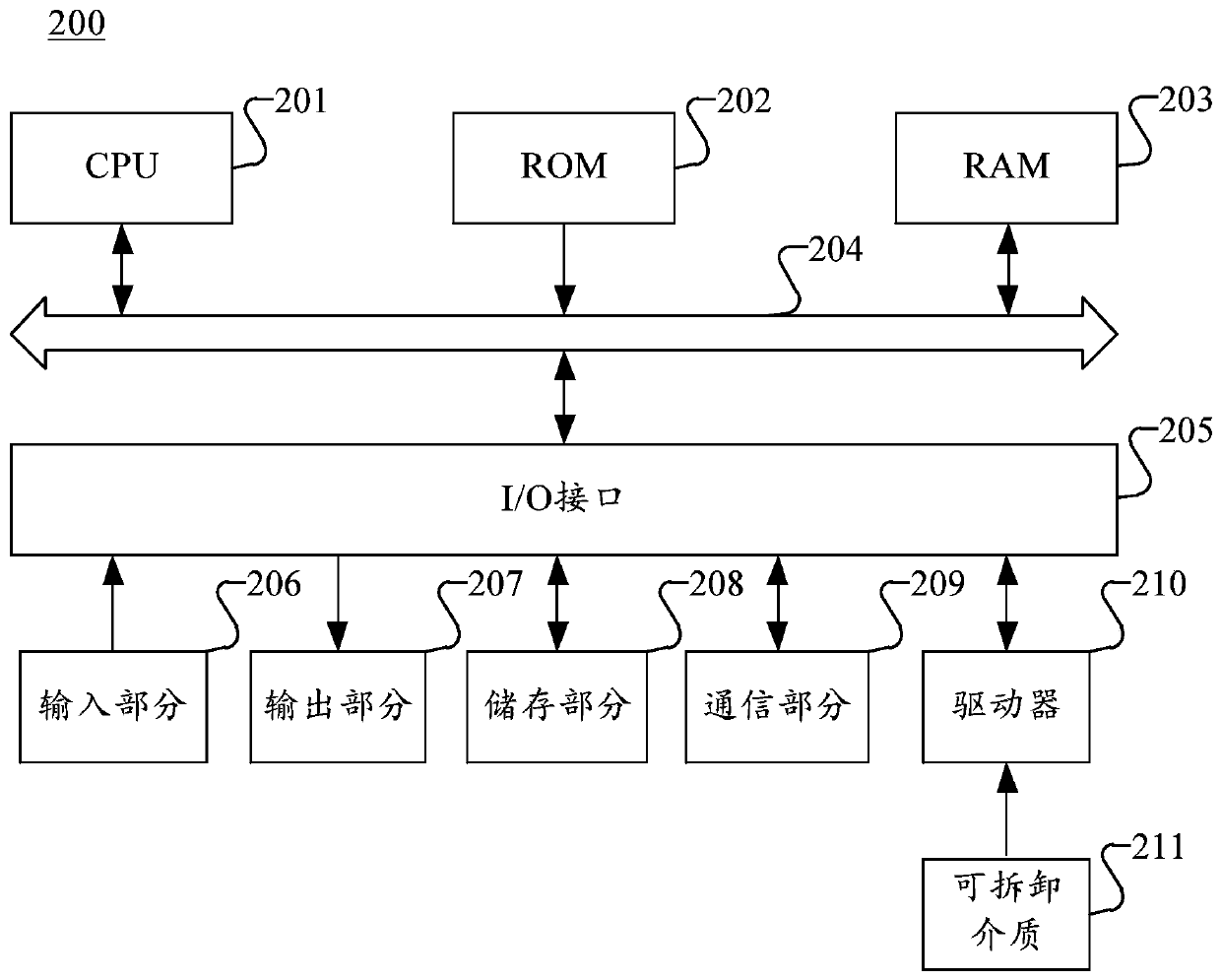

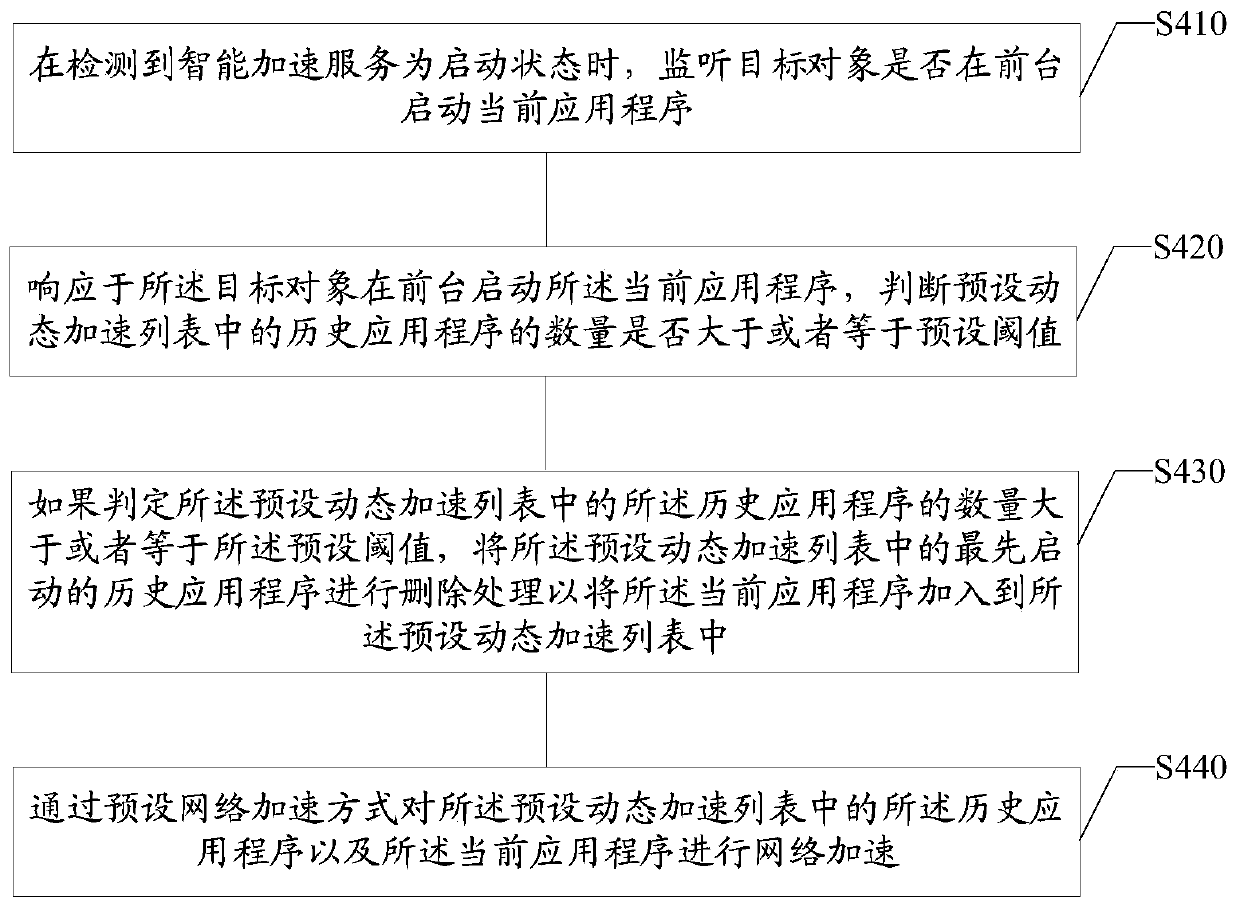

Application program acceleration method and device, storage medium and electronic equipment

ActiveCN110688169ADoes not affect accelerationAvoid wastingProgram initiation/switchingProgram loading/initiatingSimulationSoftware engineering

The invention provides an application program acceleration method and device, electronic equipment and a storage medium, relates to the technical field of computers. The application program acceleration method comprises the steps of when it is detected that an intelligent acceleration service is in a starting state, monitoring whether a target object starts a current application program at a foreground or not; in response to the fact that the target object starts the current application program at the foreground, judging whether the number of historical application programs in a preset dynamicacceleration list is greater than or equal to a preset threshold value or not; if it is judged that the number of the historical application programs in the preset dynamic acceleration list is largerthan or equal to a preset threshold value, deleting the historical application program started firstly in the preset dynamic acceleration list so as to add the current application program into the preset dynamic acceleration list; and performing network acceleration on the historical application programs and the current application programs in the preset dynamic acceleration list in a preset network acceleration mode. According to the invention, the network speed of the application programs in the acceleration list can be ensured, and the user experience is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

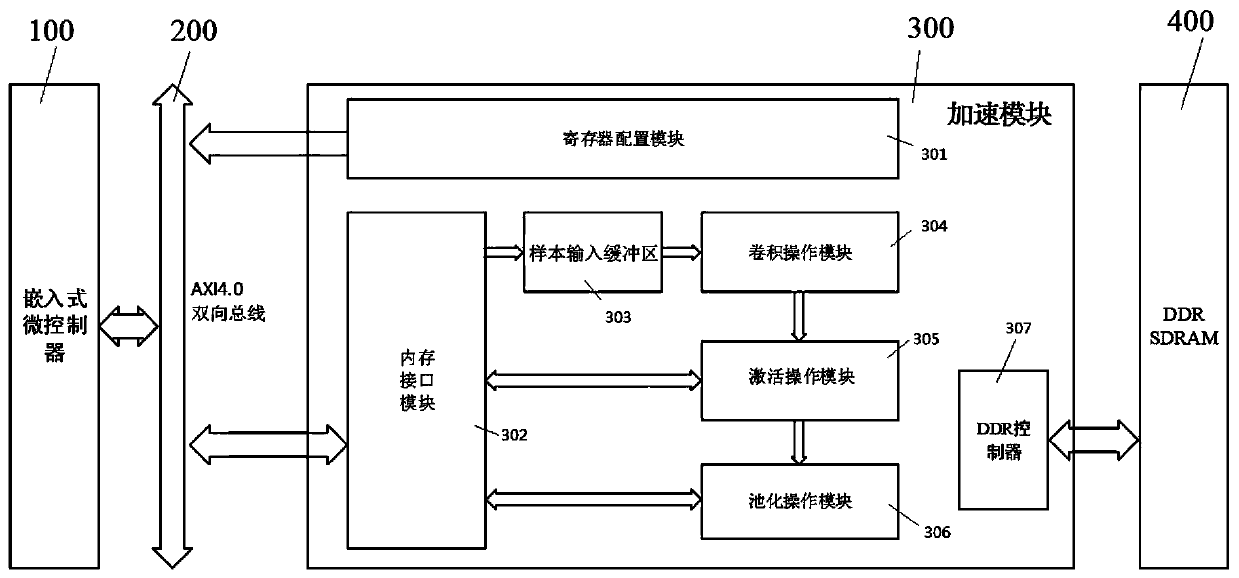

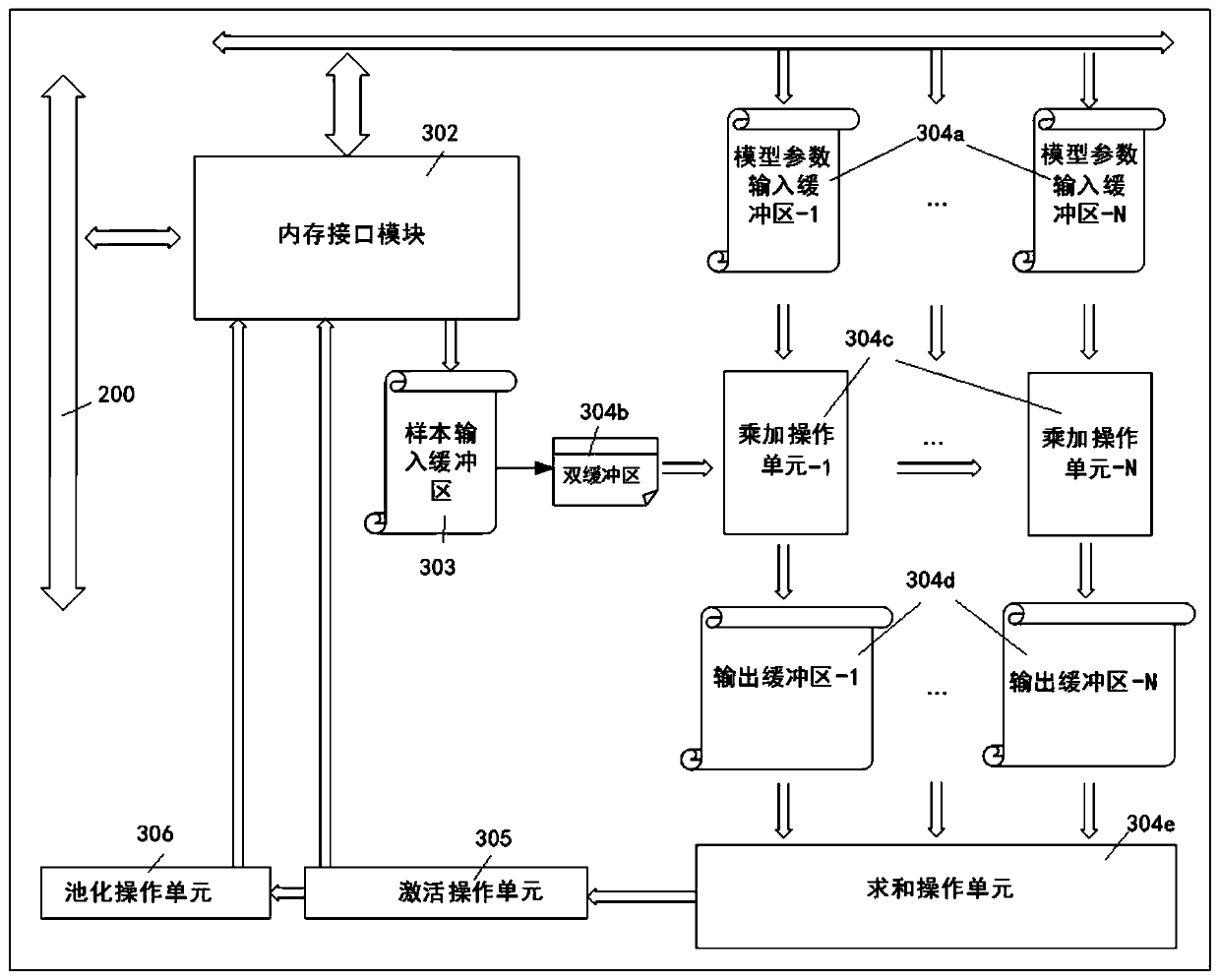

Intelligent acceleration chip suitable for power system edge calculation

InactiveCN109947573ASimple structureReduce power consumptionResource allocationPhysical realisationMicrocontrollerNerve network

The invention discloses an intelligent acceleration chip suitable for edge computing of a power system. The intelligent acceleration chip comprises an AXI4.0 bidirectional bus, a DDR SDRAM acceleration module, an embedded microcontroller and an AXI4.0 bidirectional bus, and the DDR SDRAM is used for storing the lightweight neural network model, and the acceleration module is connected with the AXI4.0 bidirectional bus and the DDR SDRAM and is used for executing convolution, nonlinearity and pooling operation according to the lightweight neural network model, wherein the embedded microcontroller is connected with the AXI4.0 bidirectional bus, and the embedded microcontroller carries out command interaction with the acceleration module through the AXI4.0 bidirectional bus so as to control the operation of the acceleration module. The intelligent acceleration chip suitable for edge calculation of the power system realizes chip-level acceleration of convolution operation, nonlinear operation and pooling operation, and is simple in structure, low in power consumption and high in operation speed.

Owner:BEIJING SMARTCHIP MICROELECTRONICS TECH COMPANY +1

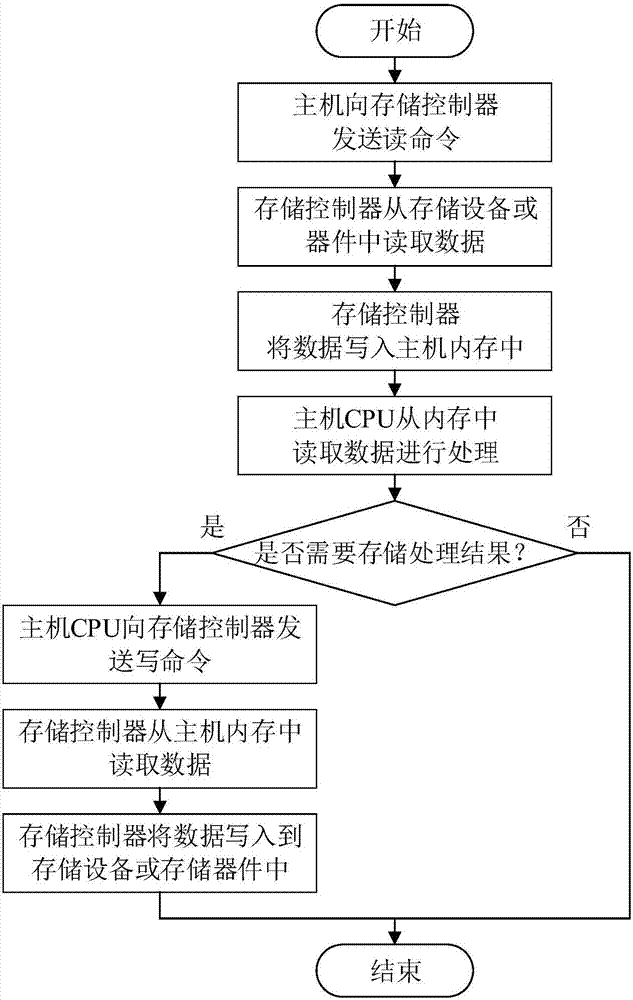

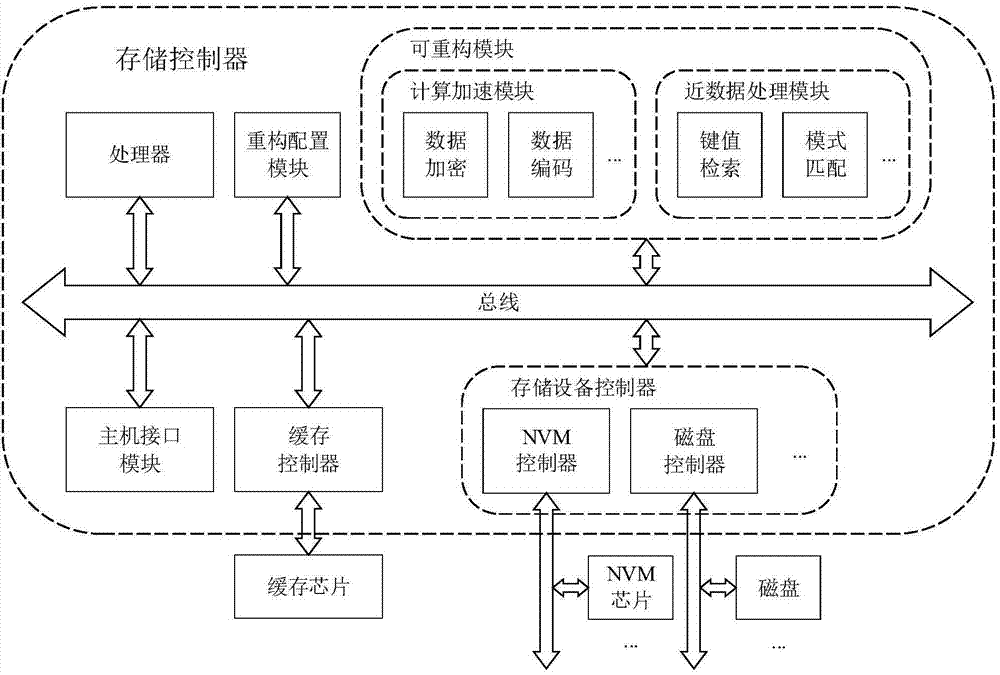

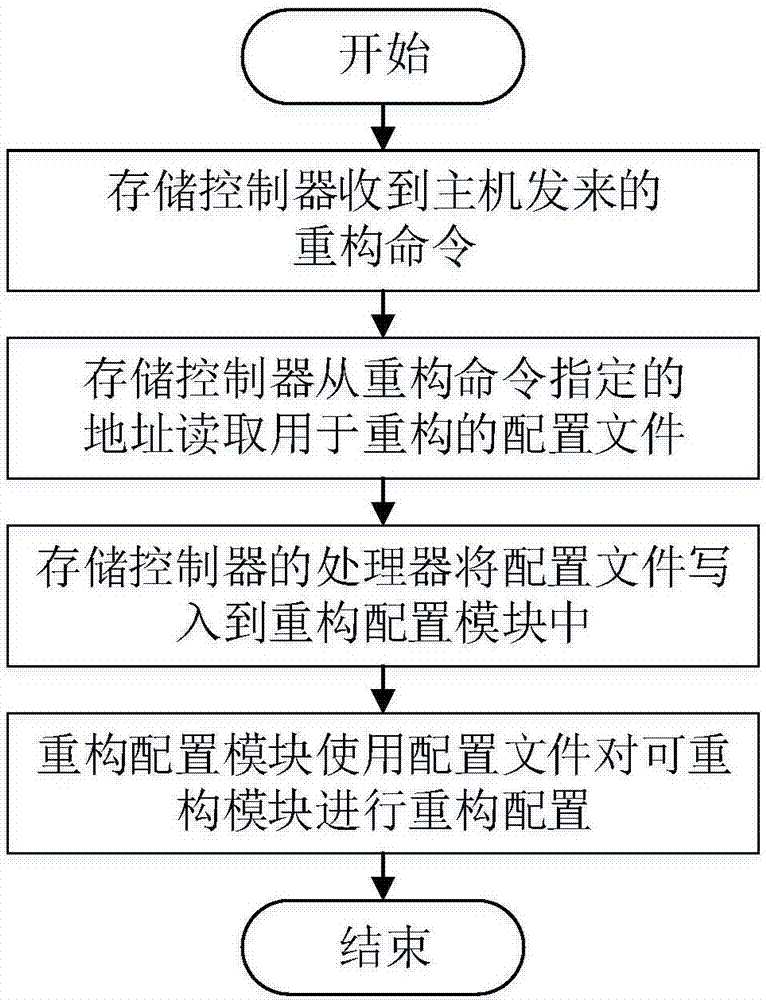

Storage controller

ActiveCN106933510AFlexible configurationImprove performanceInput/output to record carriersControl storeComputerized system

The invention discloses a storage controller, comprising a host interface module, a reconfiguration module, a cache controller, a storage equipment controller, a processor and a reconfigurable module, wherein the host interface module is used for transmitting a command and data between the storage controller and a host; the reconfiguration module is used for reconfiguring the reconfigurable module according to a configuration file after the host interface module receives a reconfiguration command; the cache controller is used for controlling read-write of a cache of an equipment terminal; the storage equipment controller is used for controlling the read-write of various storage equipment or storage devices; the processor is used for executing a control program related to the command received by the host interface module; and the reconfigurable module is used for reconfiguration through a reconfiguration mode according to needs. By use of the storage controller, the computer system performance can be improved.

Owner:HUAZHONG UNIV OF SCI & TECH

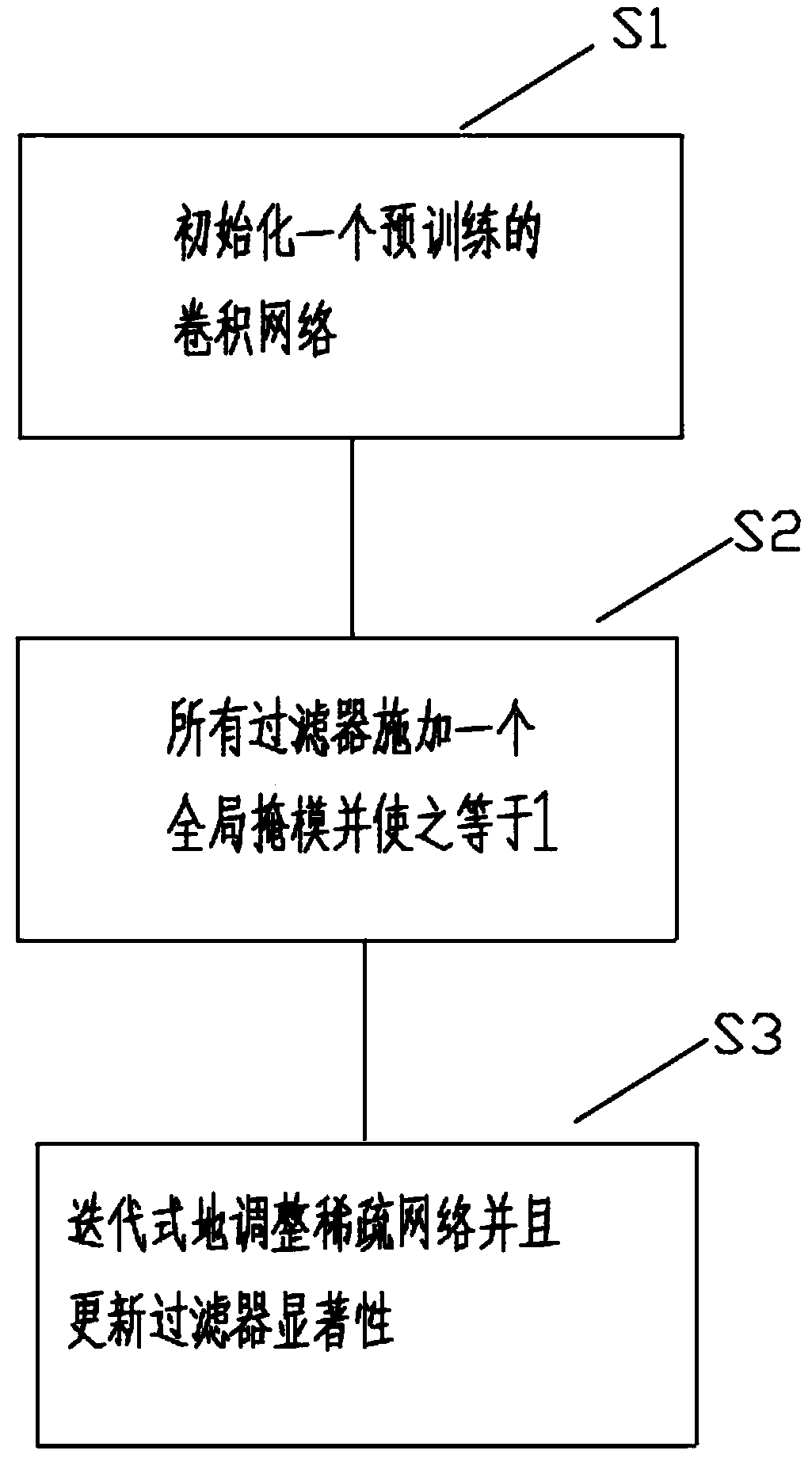

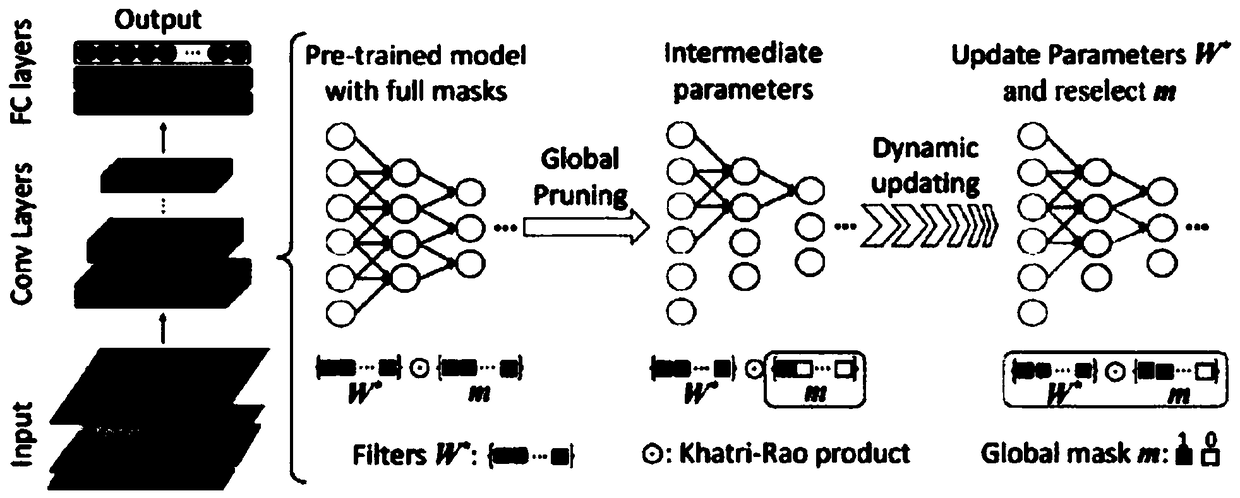

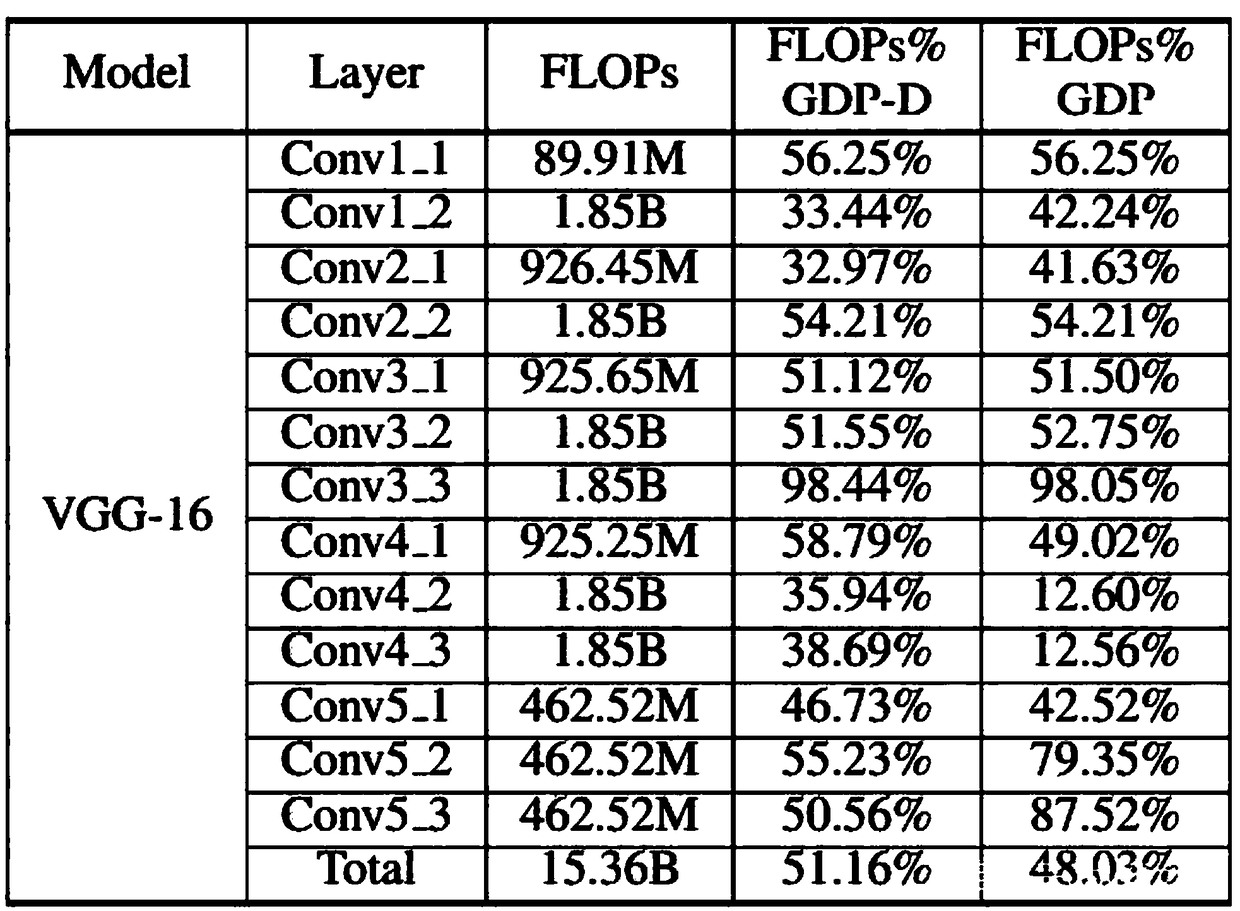

Compression and acceleration method based on a deep neural network model

InactiveCN109492754AImprove accuracyAccelerated implementationNeural architecturesNeural learning methodsNetwork modelMachine learning

The invention discloses a compression and acceleration method based on a deep neural network model. The compression and acceleration method comprises the following steps: 1) initializing a pre-trainedconvolutional network; 2) applying a global mask to all the filters, wherein the global mask is equal to 1; and 3) iteratively adjusting the sparse network and updating the filter significance. According to the compression and acceleration method based on the deep neural network model, the accuracy loss of the neural network is reduced through the pruned neural network, and the calculated amountand the scale of the neural network model can be compressed by multiple times on the premise that the algorithm precision of the neural network is not lost basically.

Owner:深圳市友杰智新科技有限公司

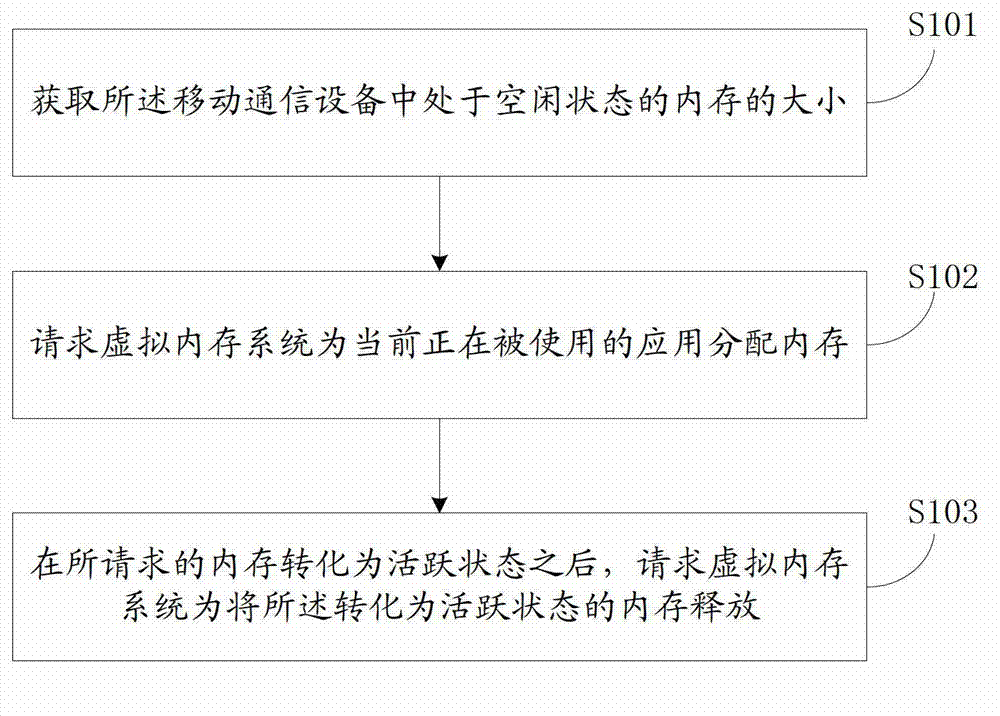

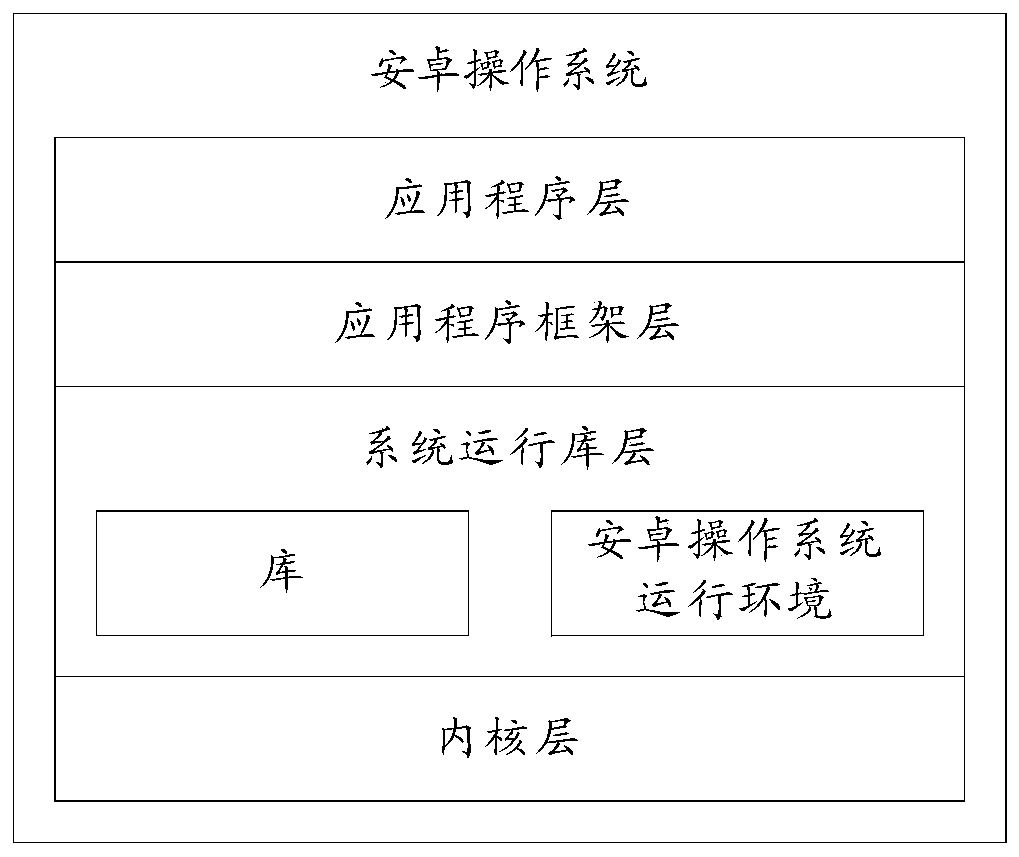

Method and device of accelerating to mobile communication device

ActiveCN103092769AAccelerated implementationMemory adressing/allocation/relocationVirtual memoryDistributed memory

The invention discloses a method and a device of accelerating to a mobile communication device. Operating systems which do not open user authority are operated in the mobile communication device. The method of accelerating to the mobile communication device comprises the following steps: acquiring a size of a memory which is in an idle condition in the mobile communication device, requesting a virtual memory system to distribute memories for application which is used currently, wherein a size of a requested memory is larger than the size of the memory which is in the idle condition, transforming the memory which is in the idle condition into an active memory and transforming a part memory or a total memory which is in a non-active condition into an active condition, requesting the virtual memory system to free the memory which is transformed into the active condition, transforming the memory which is transformed into the active condition into the idle condition, transforming the memory which is in the idle condition into the idle condition again, and transforming the memory which is in the non-active condition into the idle condition. The method and the device of accelerating to the mobile communication device can clean system memory and achieve the acceleration of the mobile communication device.

Owner:BEIJING QIHOO TECH CO LTD

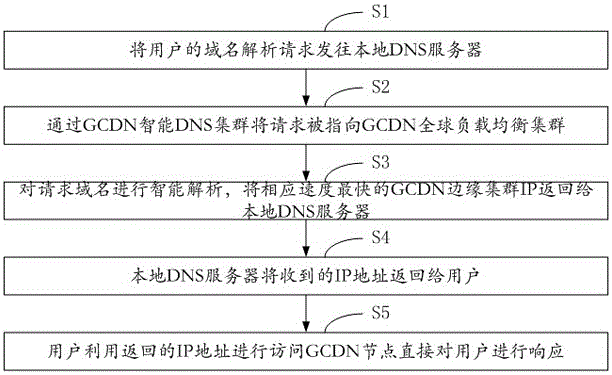

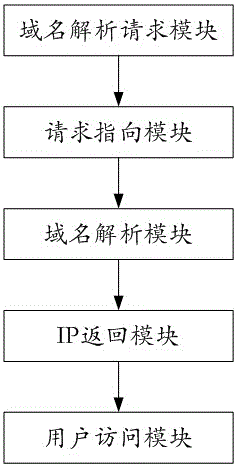

Global content distribution method and system

InactiveCN106131144AAccelerated implementationLoad balancingTransmissionDomain nameContent distribution

The invention relates to a global content distribution method. The method comprises a source station server, a global load balancing cluster in communication connection with the source station server, and a plurality of GCDN (Global Content Delivery Network) node servers; an access method comprises the following steps: step A, sending a domain name resolution request of a user to a local DNS (Domain Name Server); step B, making the request be directed to a GCDN global load balancing cluster through a GCDN intelligent DNS cluster; step C, performing intelligent resolution on a requested domain name, and returning a GCDN edge cluster IP (Internet Protocol) with the corresponding fastest speed to the local DNS; step D, returning a received IP address to the user by the local DNS; and step E, accessing a GCDN node by the user by using the returned IP address and directly responding to the user. A local Cache is used for accelerating a GCDN global network mirror and an acceleration engine, and through a high-speed compression channel and a cluster anti-attack technology, load balancing and intelligent multi-thread of the network are achieved and a fastest path can be automatically obtained.

Owner:深圳互联先锋科技有限公司

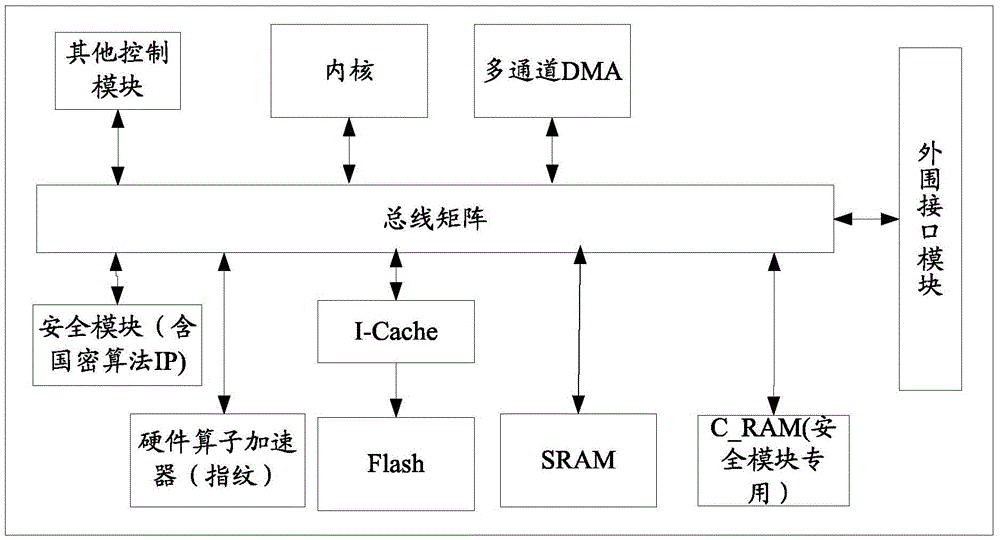

Fingerprint safety chip

InactiveCN105528559AAccelerated implementationImprove securityInternal/peripheral component protectionDigital data authenticationParallel computingFingerprint

The invention discloses a fingerprint safety chip, which comprises a safety module, a fingerprint hardware operator accelerator, an instruction high-speed cache memory I-Cache and a busbar, wherein the safety module is used for supporting a GMB algorithm; the safety module, the fingerprint hardware operator accelerator and the instruction high-speed cache memory I-Cache are connected by the busbar. The fingerprint safety chip has the advantages that the safety of the data processing of the fingerprint identification is improved, and the chip property is improved.

Owner:DATANG MICROELECTRONICS TECH CO LTD +1

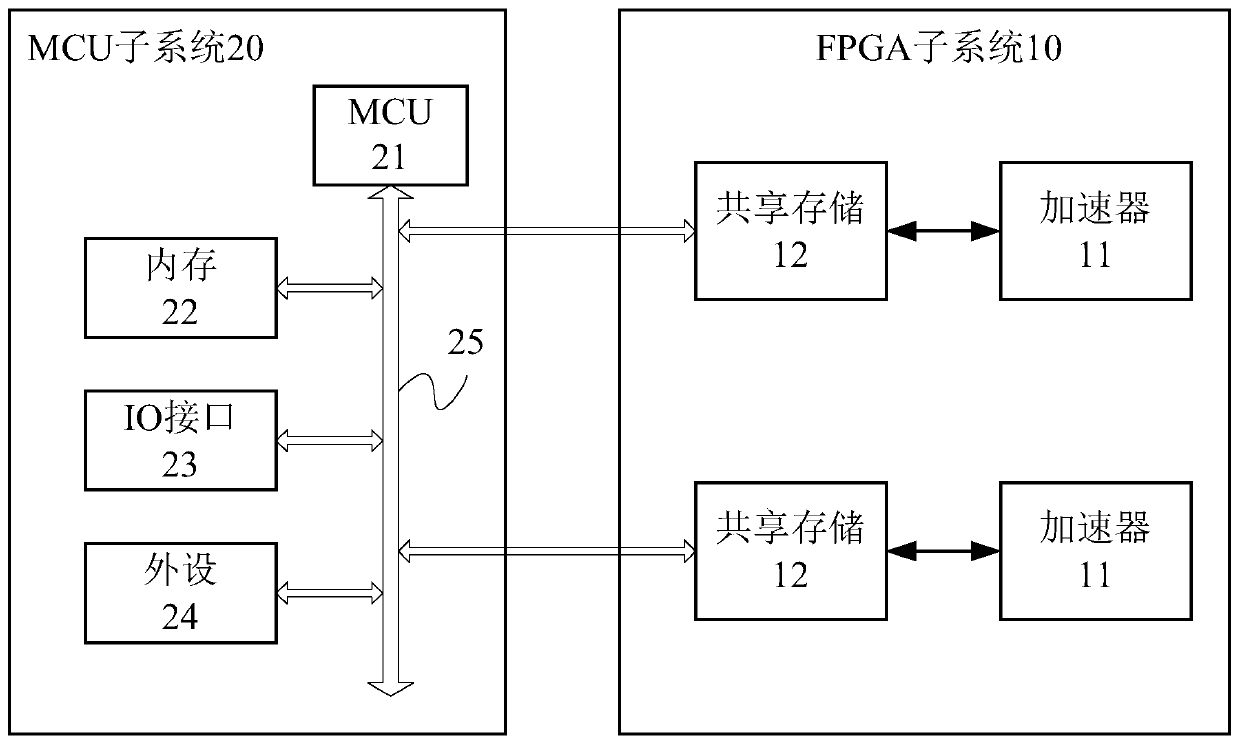

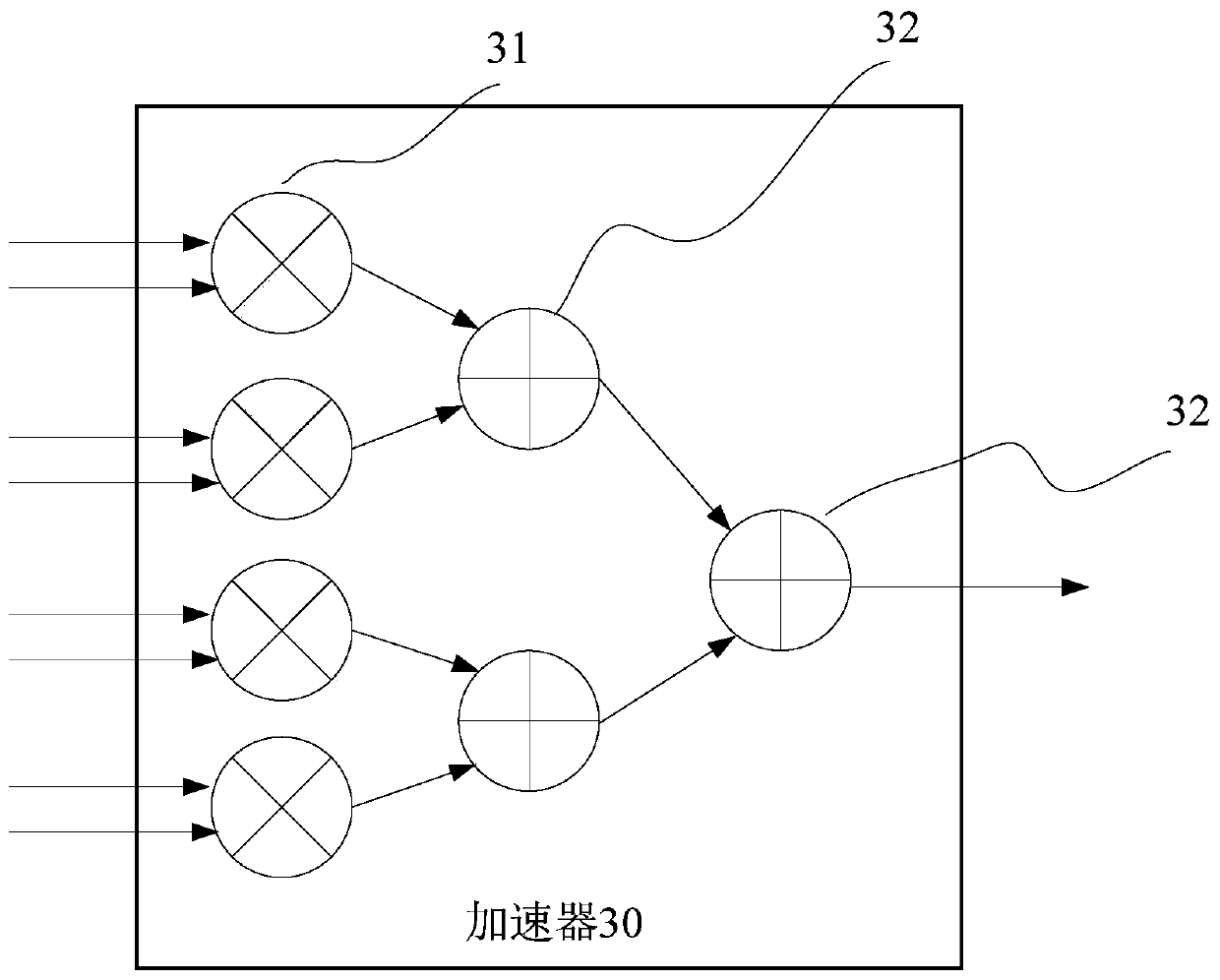

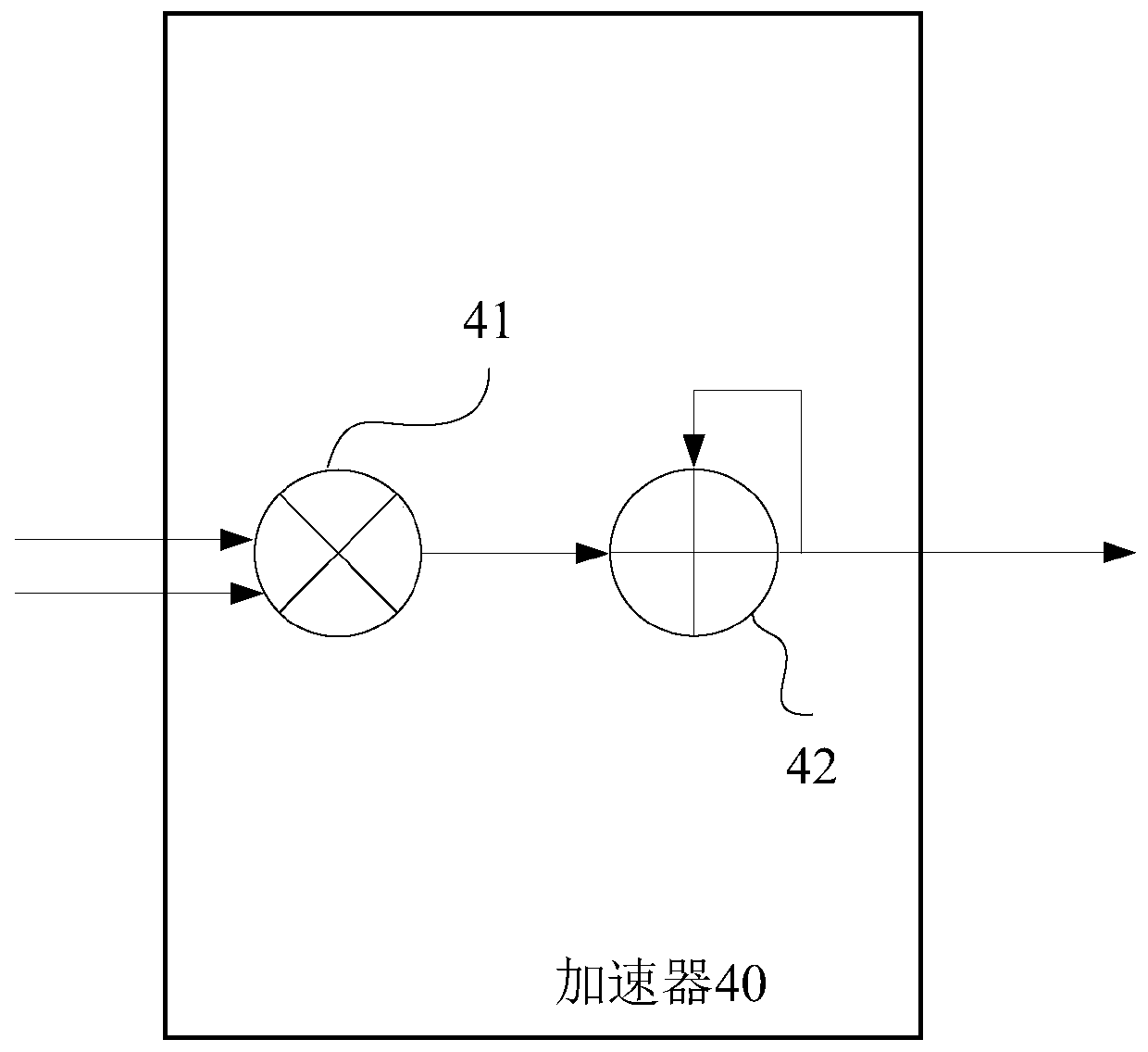

Edge artificial intelligence computing system framework based on SoC FPGA

PendingCN110727633AAccelerated implementationReduce power consumptionGeneral purpose stored program computerPhysical realisationAlgorithmEngineering

An edge artificial intelligence computing system framework based on an SoC FPGA comprises an MCU subsystem and an FPGA subsystem, and the FPGA subsystem comprises an accelerator used for carrying outacceleration operation on an artificial intelligence algorithm; a shared memory used as an interface of the accelerator and the MCU subsystem; wherein the MCU subsystem uploads data to be calculated to the shared memory, and retrieves an operation result; and the accelerator independently reads data from the shared memory for operation and writes back an operation result. The system architecture has the advantages of small hardware area, low power consumption, high operational performance and high usability, and the design process is simple and flexible.

Owner:GOWIN SEMICON CORP LTD

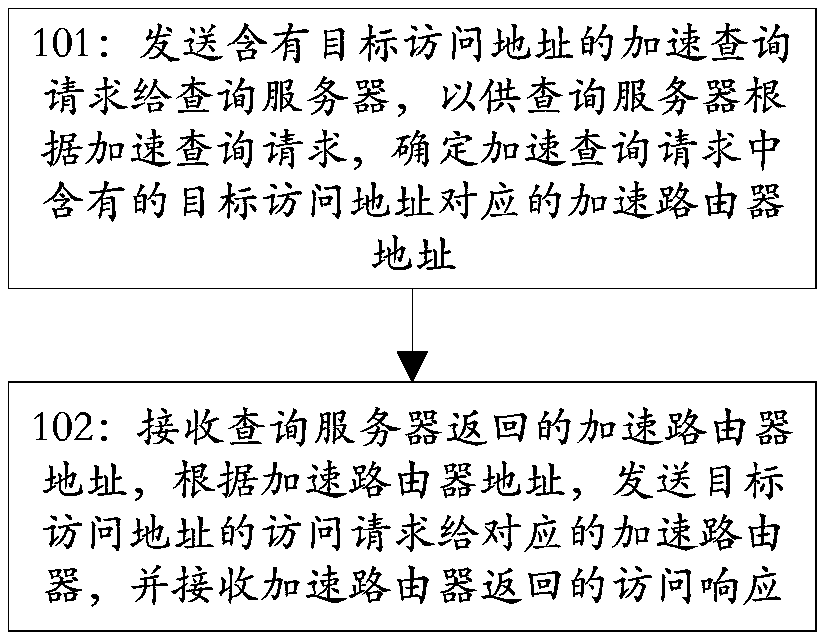

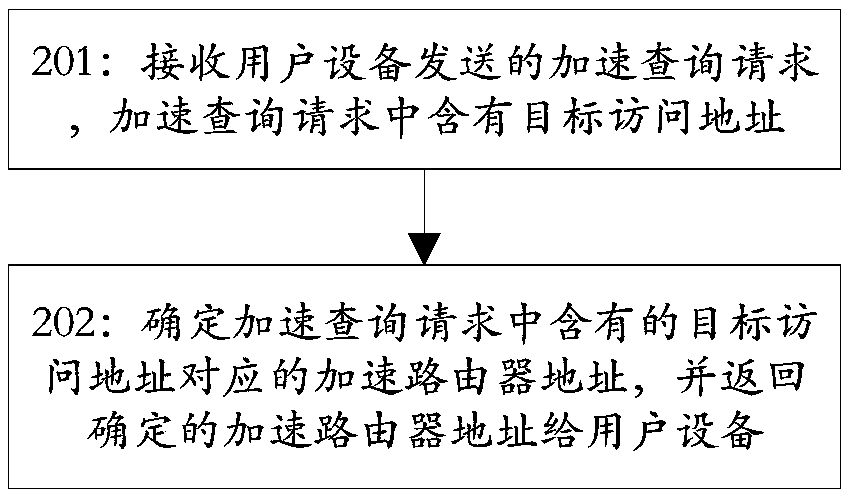

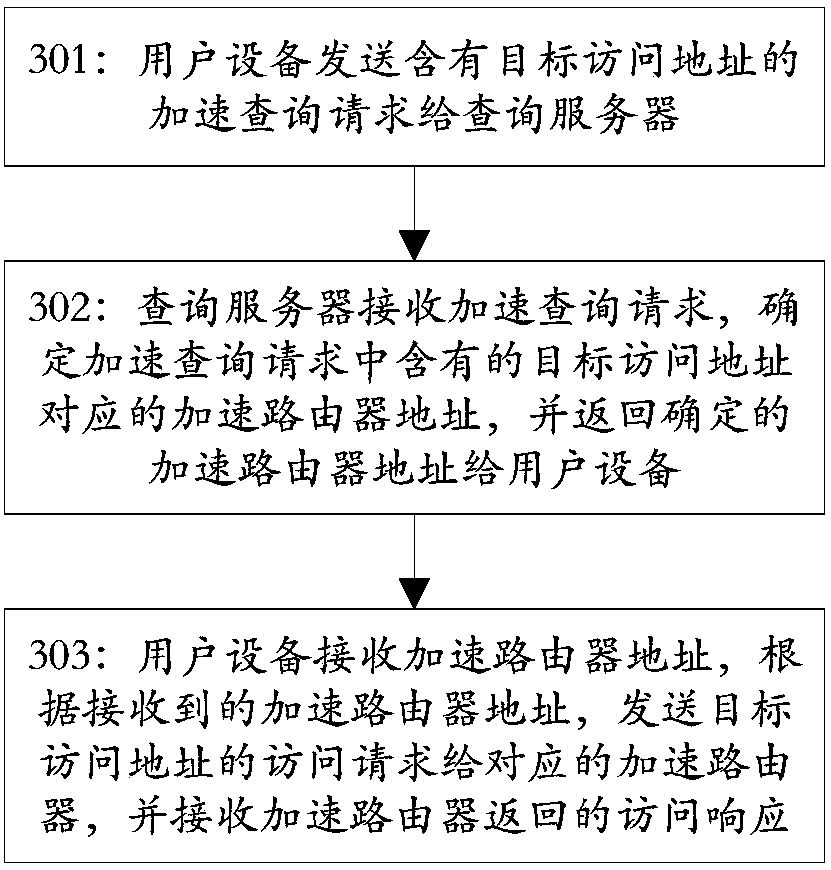

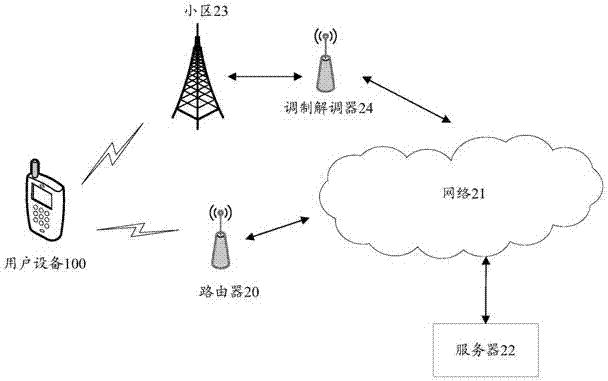

Network acceleration method and system

InactiveCN108449273AImprove experienceAccelerated implementationData switching networksNetwork deploymentComputer network

The invention discloses a network acceleration method and system, belonging to the technical field of networks. The method includes the following steps that: user equipment sends a query accelerationrequest including a target access address to a query server; the query server receives the query acceleration request, determines an acceleration router address corresponding to the target access address included in the query acceleration request, and returns the acceleration router address to the user equipment; and the user equipment receives the acceleration router address, sends an access request of the target access address to the corresponding acceleration router according to the acceleration router address, and receives an access response returned by the acceleration router. According to the scheme of the invention, the network acceleration is realized by querying the query server for the acceleration router address and accessing a corresponding service server through the acceleration router corresponding to the query server, the operation of adding an acceleration server in each area corresponding to each service server is not required, and thus the network structure can be simplified, the cost of network deployment can be reduced, and the user experience can be further improved.

Owner:SHANGHAI LIANSHANG NETWORK TECHNOLOGY CO LTD

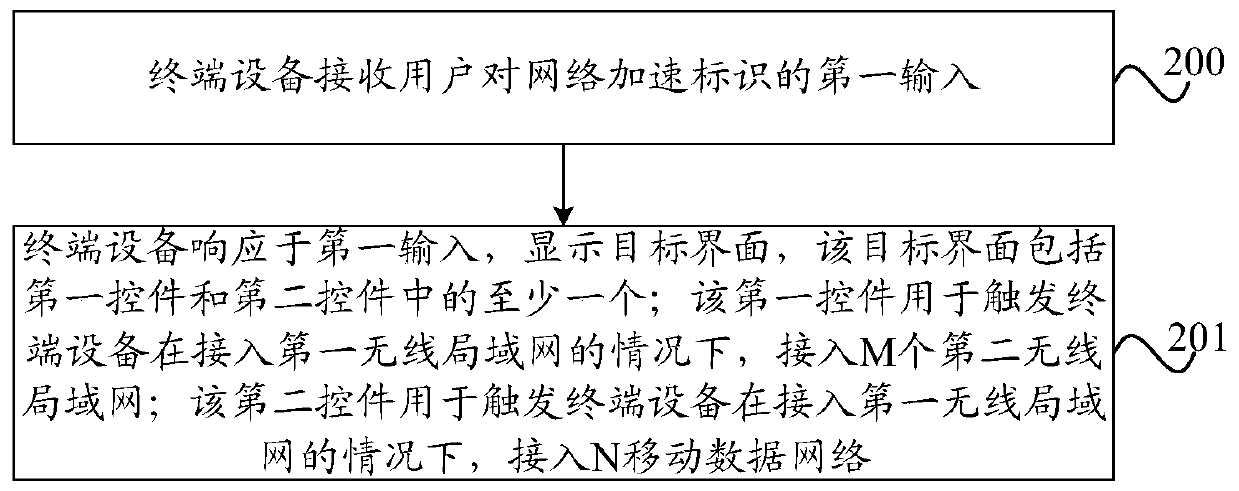

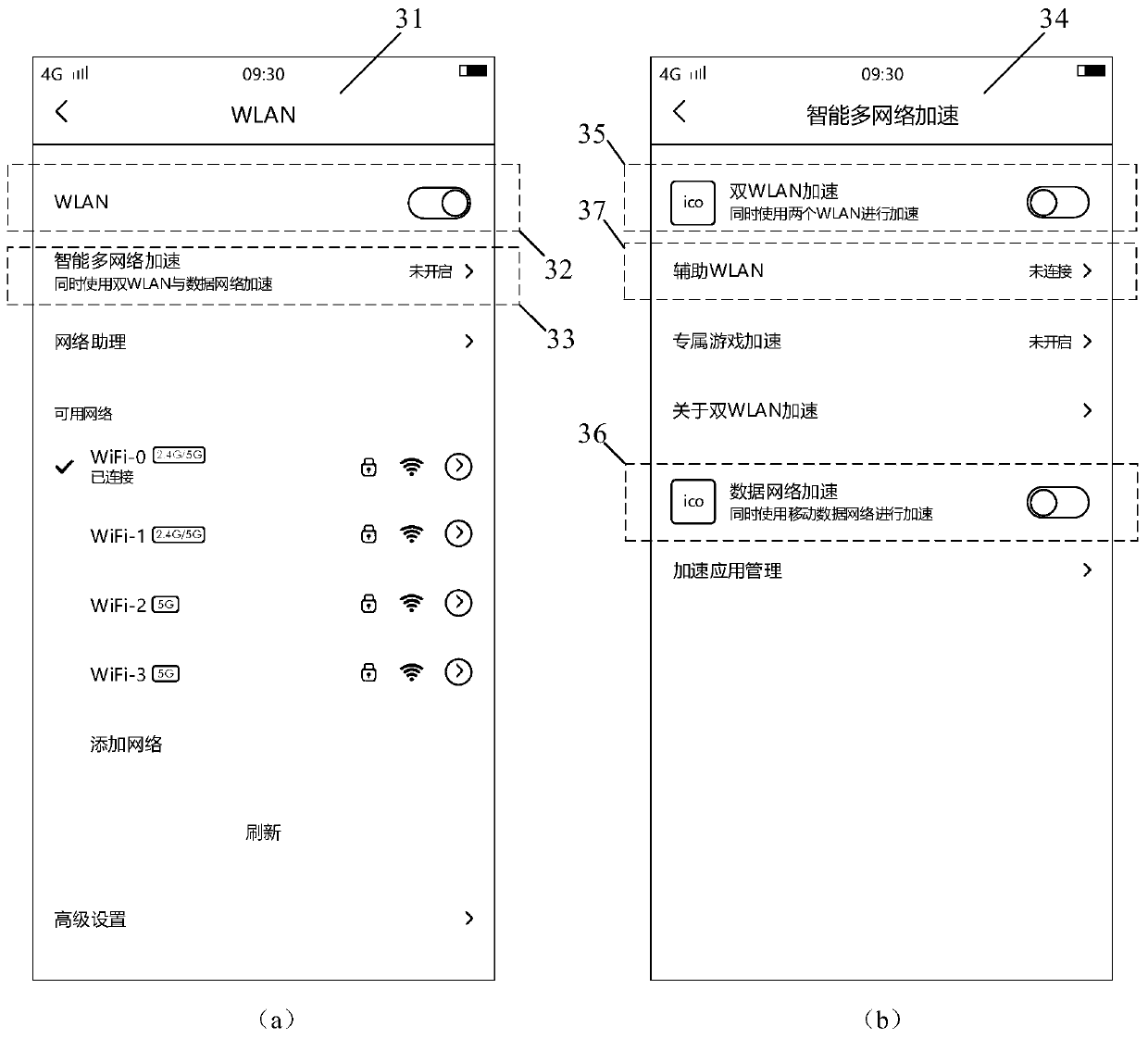

Multi-network access method and terminal equipment

PendingCN110769524AFast data transferAccelerated implementationNetwork topologiesDevices with wireless LAN interfaceAccess networkTerminal equipment

The embodiment of the invention provides a multi-network access method and terminal equipment, relates to the technical field of communication, and aims to solve the problem that the data transmissionspeed of interaction between the existing terminal equipment and a network cannot meet the use requirements of users. The method comprises the following steps: receiving a first input of a user to anetwork acceleration identifier, wherein the network acceleration identifier is an entrance for triggering terminal equipment to access a network; in response to the first input, displaying a target interface, wherein the target interface comprises at least one of a first control and a second control, the first control is used for triggering the terminal device to access M second wireless local area networks under the condition of accessing the first wireless local area network, the second control is used for triggering the terminal equipment to access N mobile data networks under the condition of accessing the first wireless local area network, and the speed of transmitting the data based on the plurality of accessed networks is greater than the speed of transmitting the data based on thefirst wireless local area network. The method can be applied to a network acceleration scene of the terminal equipment.

Owner:VIVO MOBILE COMM CO LTD

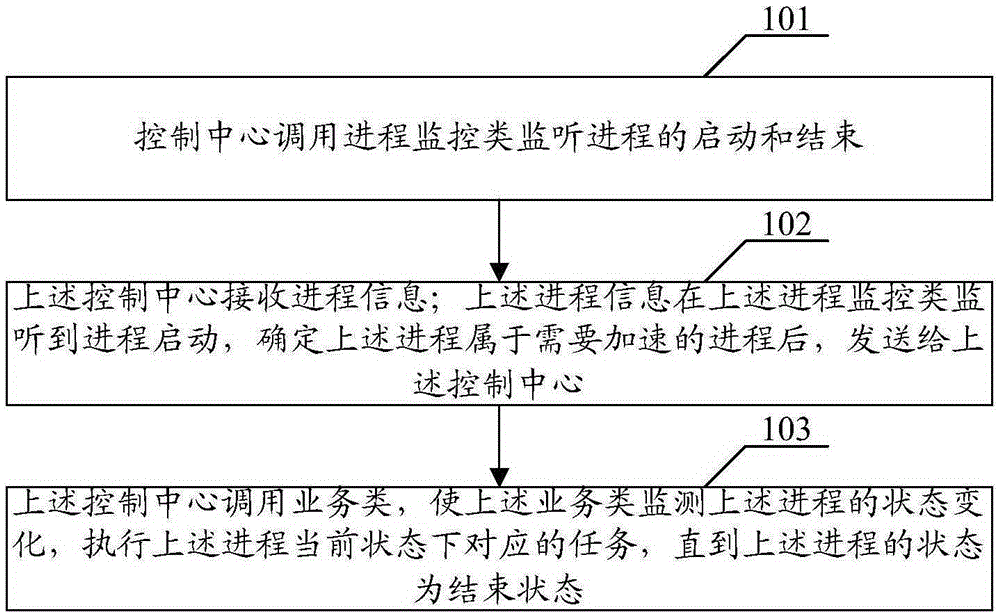

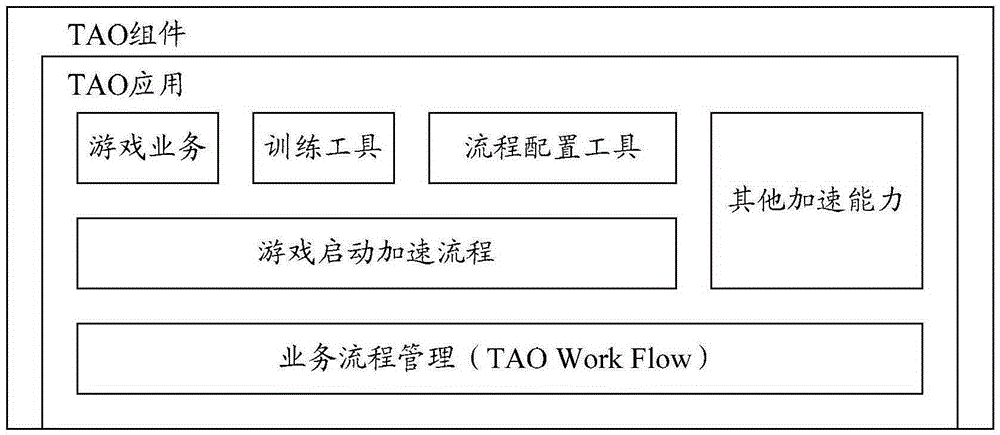

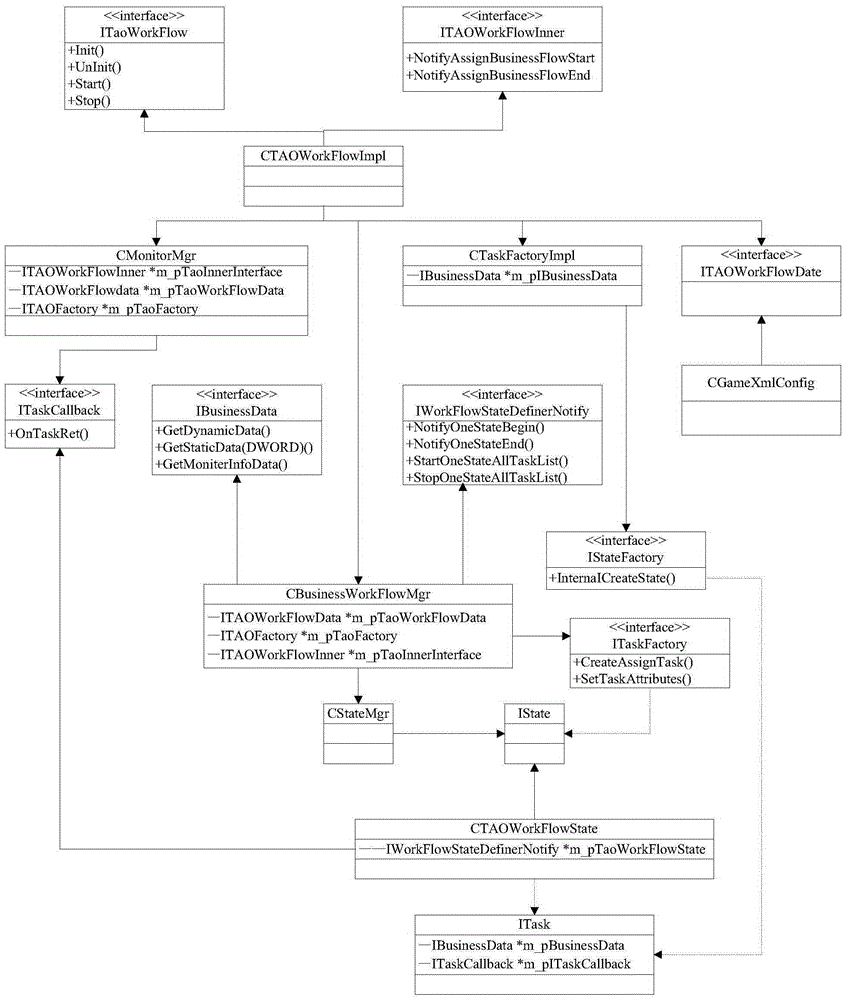

Application acceleration method and apparatus

ActiveCN106528188AAccelerated implementationImprove operational efficiencyInterprogram communicationDigital computer detailsBusiness classProcess information

Embodiments of the invention disclose an application acceleration method and apparatus. The method is implemented by comprising the steps that a control center calls a process monitoring class to monitor start and stop of a process; the control center receives process information; the process information is sent to the control center after the process monitoring class monitors that a process is started and the process is a process to be accelerated; and the control center calls a business class, enables the business class to monitor state change of the process, and executes a corresponding task in a current state of the process until the states of all processes are stop states. In the whole acceleration process, an application can be accelerated only when configuration data in the business class can support process acceleration, and tasks in a process execution process can be multiplexed / shared by different processes without code modification, so that the operation and maintenance efficiency can be improved by the acceleration scheme adopted by the method and the apparatus.

Owner:TENCENT TECH (SHENZHEN) CO LTD +1

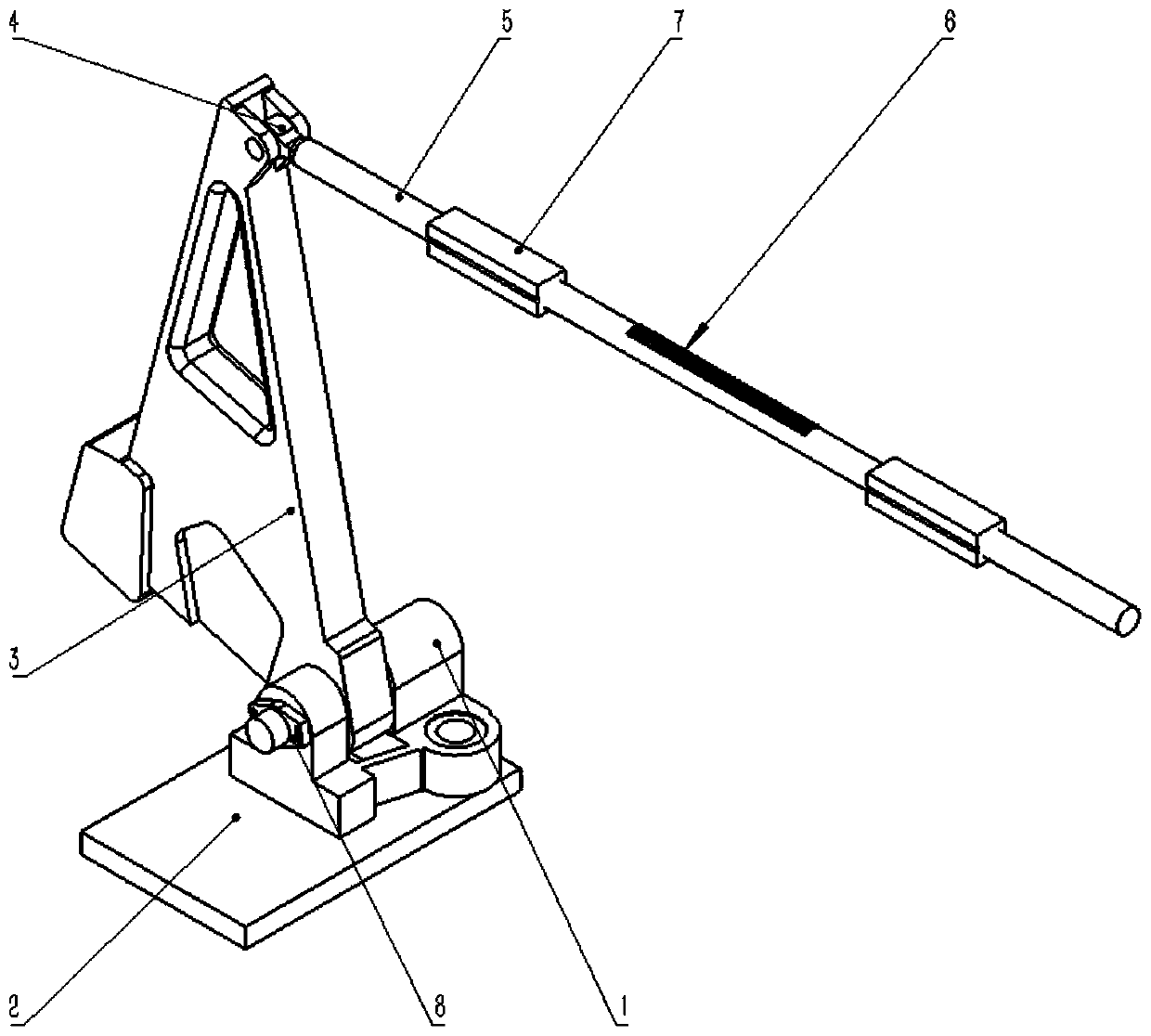

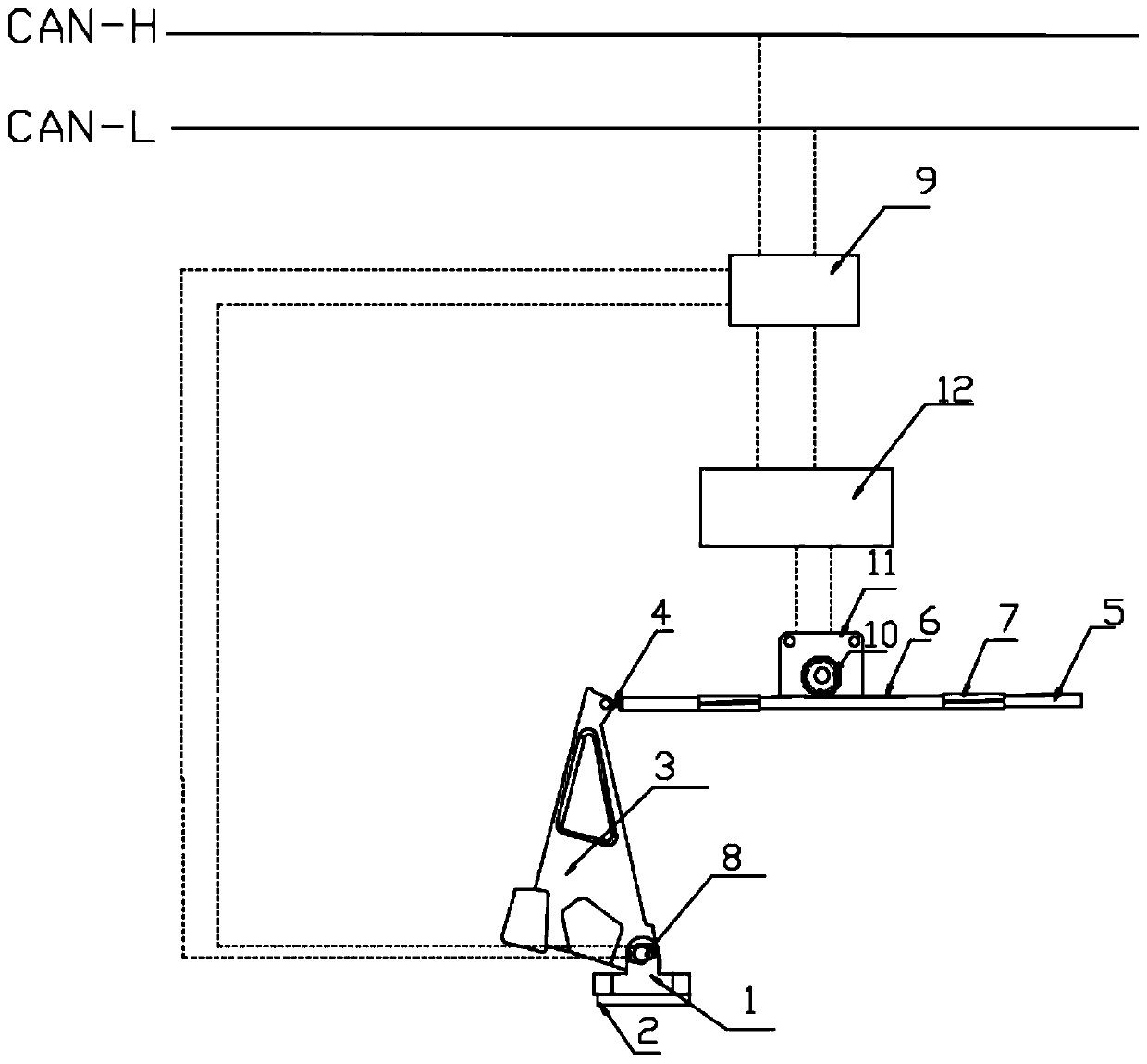

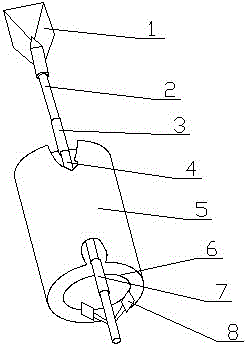

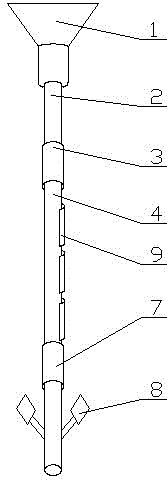

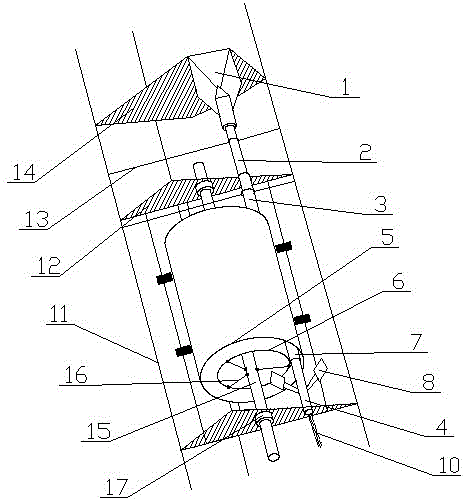

Driverless racing car accelerator pedal device

PendingCN110450628AEasy to assemble and disassembleEasy to controlPropulsion unit arrangementsMotor driveControl signal

The invention discloses an unmanned racing car accelerator pedal device. The unmanned racing car accelerator pedal device comprises a control part and a driving part, wherein the control part comprises an accelerator pedal angle sensor and a signal processor; the accelerator pedal angle sensor is installed at a rotating shaft of the accelerator pedal and used for acquiring a position signal of theaccelerator pedal in real time and transmitting the signal to the signal processor; the signal processor is connected with a CAN bus of a racing car and used for receiving a desired acceleration signal from the CAN bus, converting the desired acceleration signal into a position signal of the accelerator pedal, and comparing the position signal of the accelerator pedal with a real-time position signal of the accelerator pedal obtained by the accelerator pedal angle sensor, a control signal is output according to the comparison result, a motor controller is used for controlling a servo motor torotate forward or reverse at the corresponding angle, and the servo motor drives the accelerator pedal to change angel positions through the driving part to control the movement of the accelerator pedal of a racing car. The acceleration mechanism is convenient to disassemble and assemble, is easy to control, is convenient to modify, and can realize acceleration and deceleration control over the racing car.

Owner:GUANGDONG UNIV OF TECH

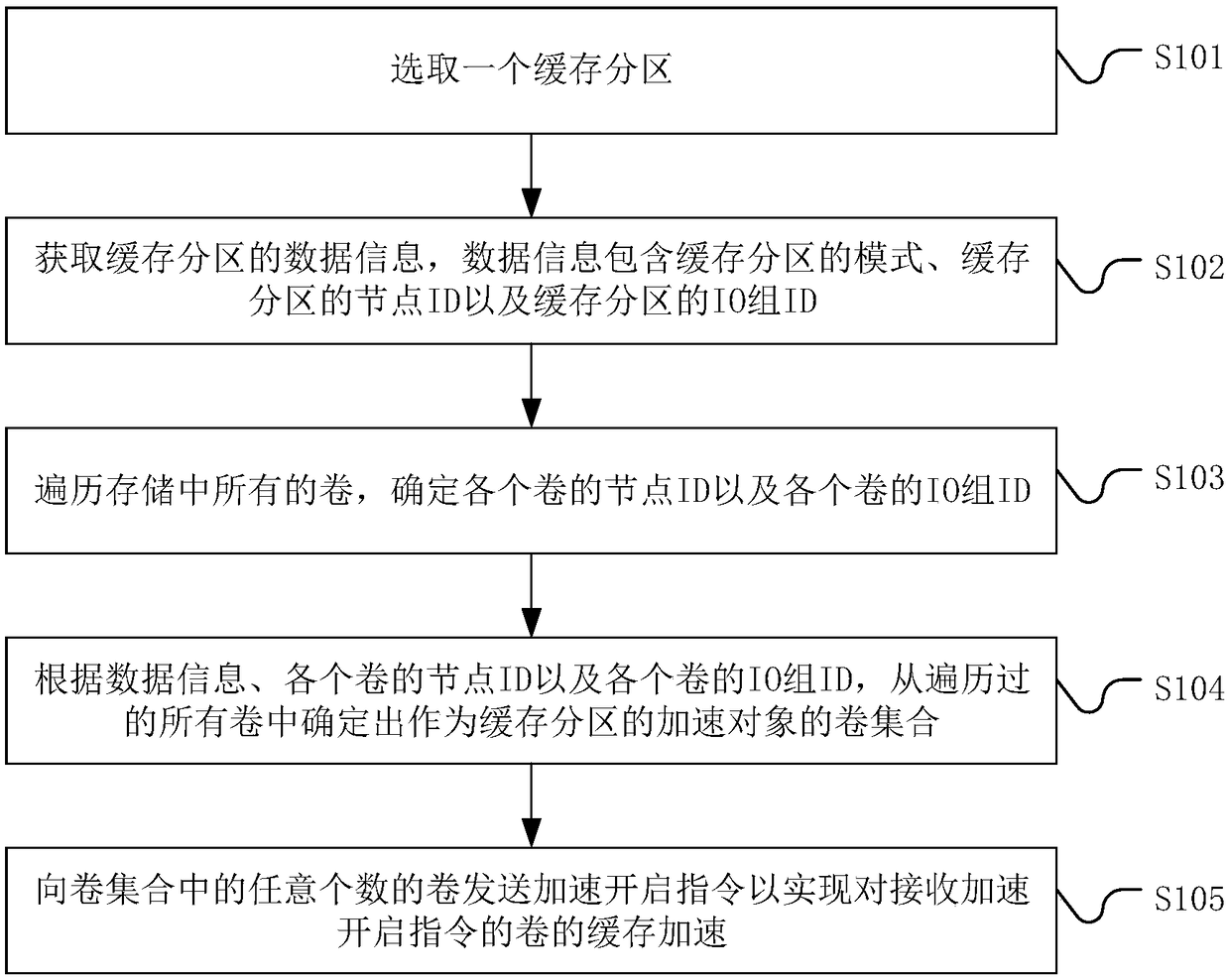

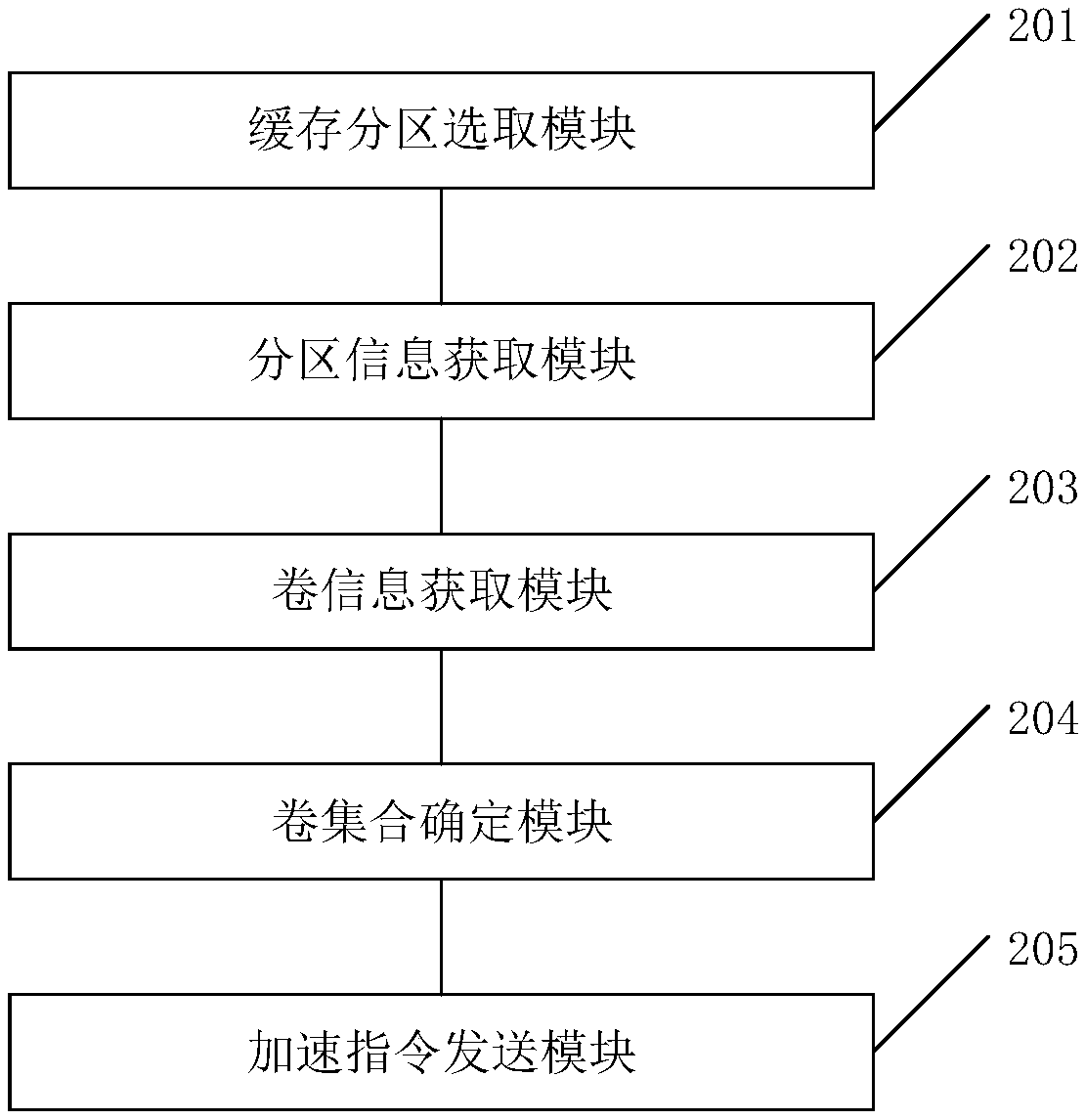

Cache acceleration management method, system and device for volumes in storage, and storage medium

ActiveCN108845767AAccelerated implementationImprove management efficiencyInput/output to record carriersData informationParallel computing

The invention discloses a cache acceleration management method for volumes in a storage. The method comprises the steps of selecting a cache partition; acquiring data information of the cache partition, wherein the data information comprises a mode of the cache partition, a node ID of the cache partition and an IO group ID of the cache partition; traversing all the volumes in the storage, and determining a node ID of each volume and an IO group ID of each volume; according to the data information, the node ID of each volume and the IO group ID of each volume, determining a volume set serving as an acceleration object of the cache partition from all the traversed volumes; and sending acceleration starting instructions to any number of the volumes in the volume set so as to achieve cache acceleration of the volumes receiving the acceleration starting instructions. By applying the method, all the volumes, capable of being subjected to cache acceleration management, of the cache partitionare determined, so that the management efficiency of batch cache acceleration of the volumes is improved. The invention further discloses a cache acceleration management system and device for the volumes in the storage, and a storage medium, which have the corresponding technical effects.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

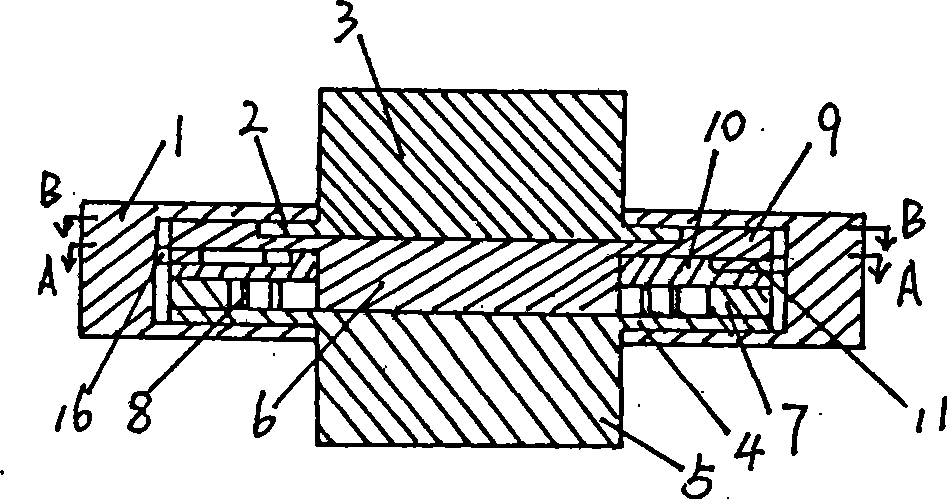

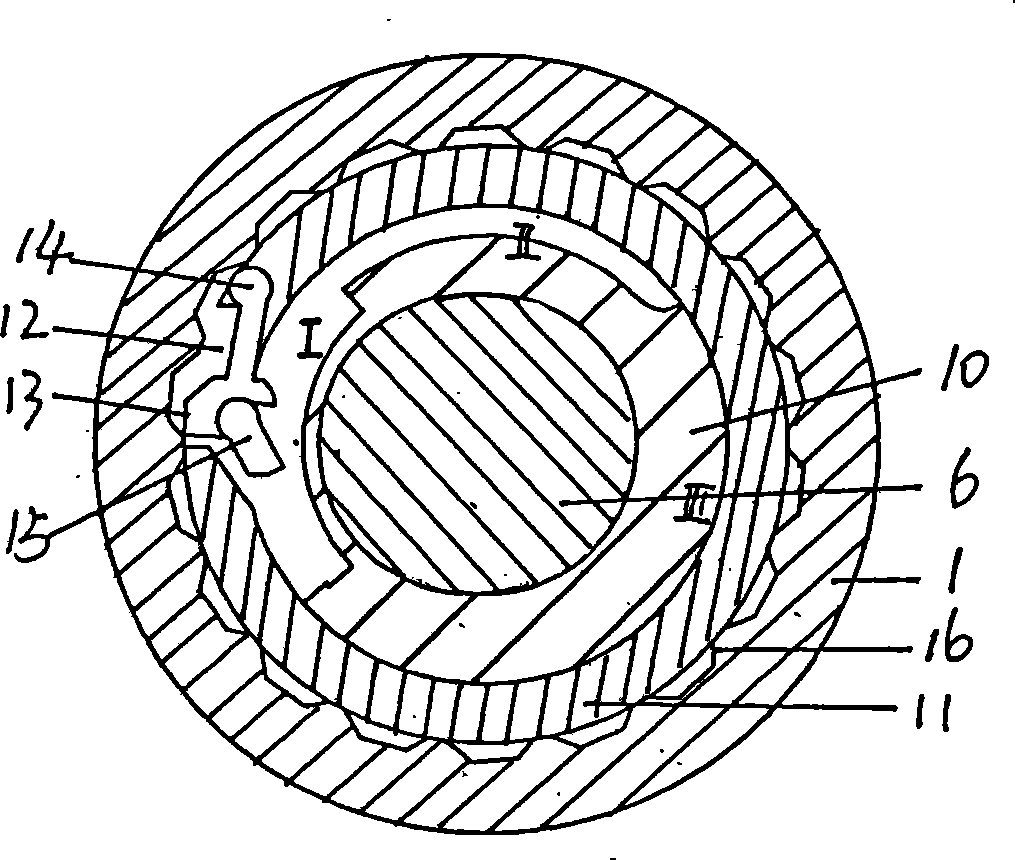

Mechanical stepless automatic speed variator

InactiveCN101377232AAccelerated implementationAccelerated impactGearingAutomatic transmissionTorque regulation

The present invention relates to a transmission, in particular to a mechanical stepless automatic transmission, which solves the problem that the prior mechanical transmission can not satisfy the actual requirement for variable speed transmission in the mechanical transmission. The mechanical stepless automatic transmission comprises a casing body, an output shaft of a transmission disc fixed at the power input end, an input shaft of a rolling disc fixed at the power output end, and an intermediate shaft; wherein, the transmission disc, the intermediate shaft and the rolling disc are arranged in the casing body; an annular fixed body is positioned on the rolling disc; an annular torsion spring is fixed between one end of the intermediate shaft and the annular fixed body; an output initiative disc is fixed at the other end of the intermediate shaft; a torque regulating disc is sleeved on the intermediate shaft; the outer wall of the torque regulating disc is divided into three parts with different radiuses; an annular supporting body is arranged on the output initiative disc, and is provided with a gap; an opening-closing locking pin with one end hinged with the annular supporting body is arranged at the gap; and an annular gear is positioned on the casing body. The present invention has the advantages of reasonable structure and good effects, can realize the stepping mechanical stepless automatic transmission, and is suitable for automobiles and other machinery.

Owner:王焰

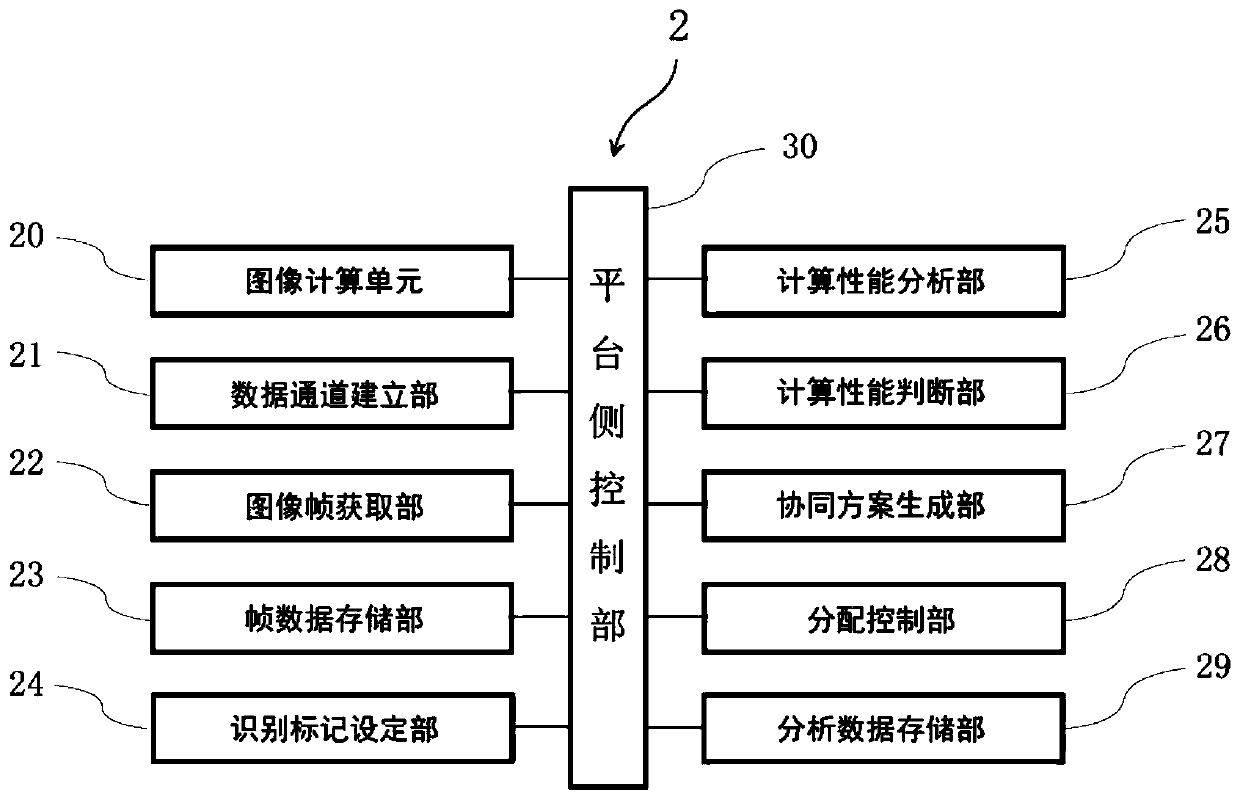

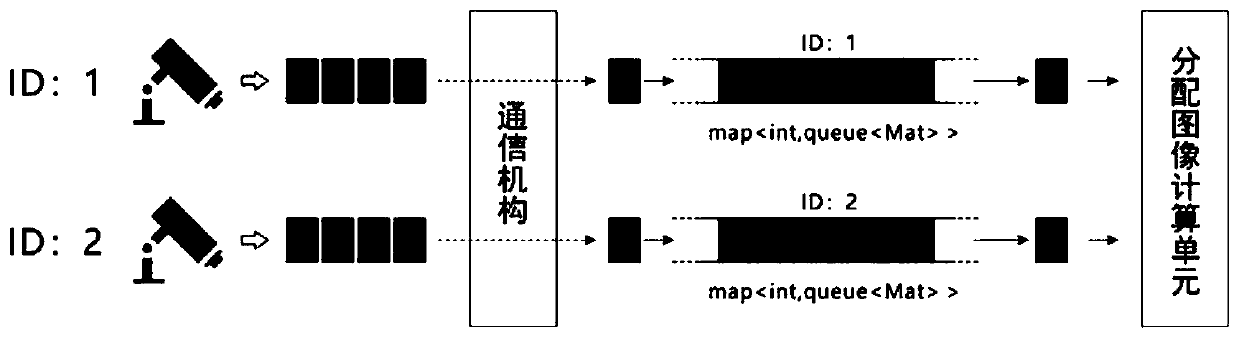

An ultrahigh-definition video image analysis acceleration method and system

ActiveCN109727276AAccelerated implementationGuaranteed real-timeImage analysisUltrahigh resolutionImaging analysis

The invention provides an ultrahigh-definition video image analysis acceleration method and an ultrahigh-definition video image analysis acceleration system based on the ultrahigh-definition video image analysis acceleration method. The method is used for carrying out real-time processing and analysis on ultrahigh-resolution video images by adopting an analysis platform comprising a plurality of image calculation units, and is characterized by comprising the following steps: S1, establishing a data transmission channel for acquiring the video images, continuously acquiring image frames of thevideo images, and directly storing the image frames; S2, sequentially setting sequence marks for the acquired image frames according to the acquisition sequence; S3, analyzing the calculation performance of the image calculation units, further determining the processing sequence of each image calculation unit, and generating a corresponding processing scheme; S4, controlling a corresponding imagecalculation unit to carry out image analysis calculation on the image frame according to the processing scheme so as to obtain an analysis result; And S5, sequentially storing the corresponding analysis results according to the sequence marks.

Owner:FUDAN UNIV

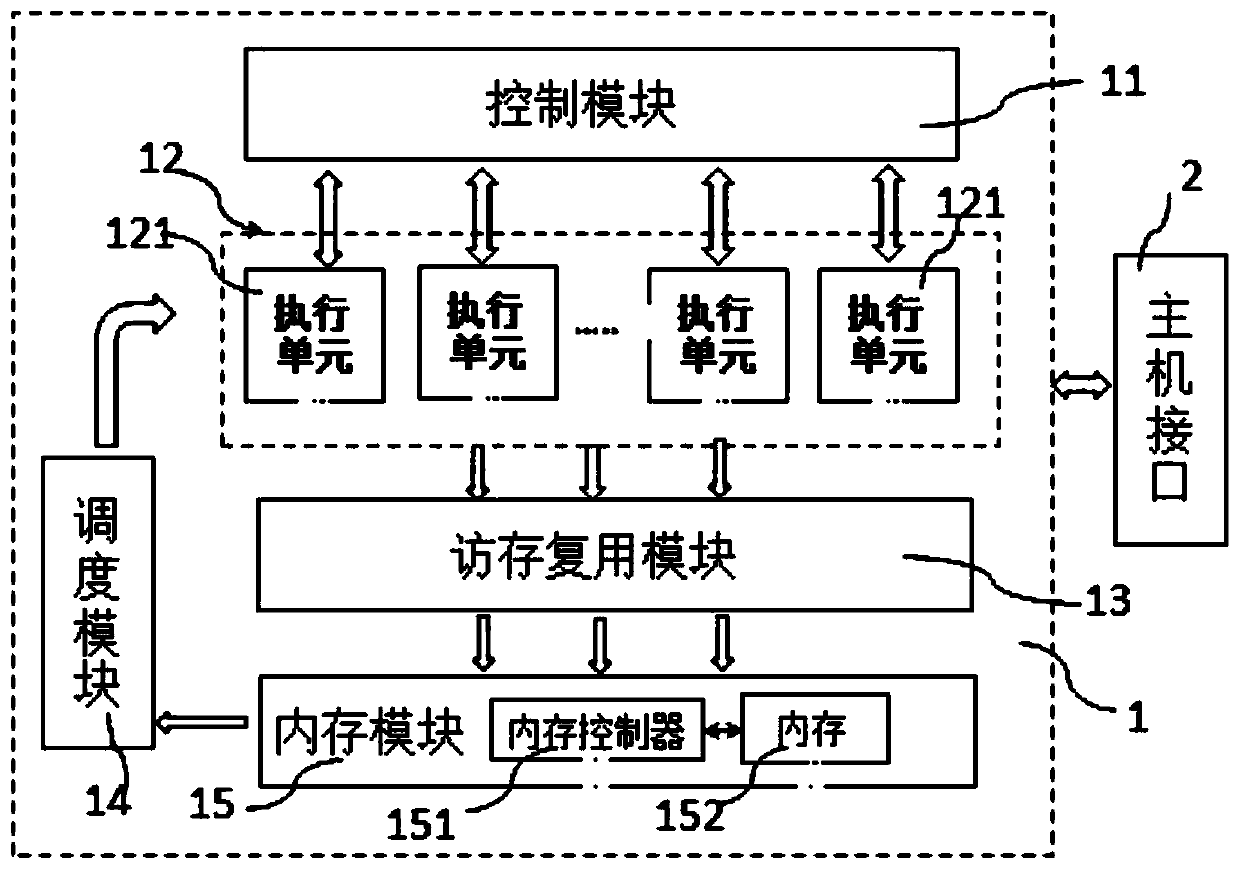

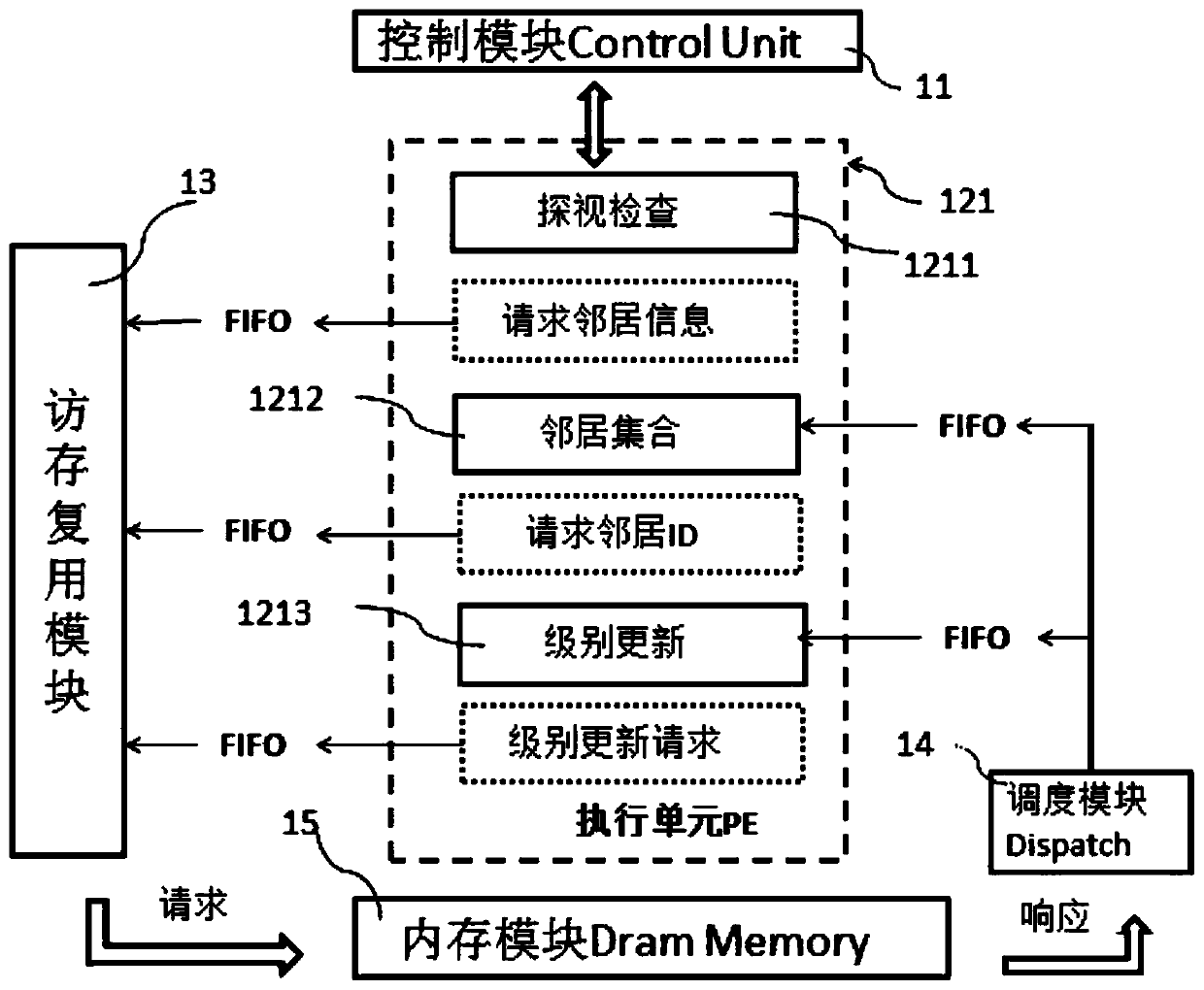

Width-first search algorithm-oriented acceleration device and method and storage medium

ActiveCN109992413AAccelerated implementationImprove bandwidth utilizationResource allocationStill image data queryingComputer moduleAssembly line

The invention relates to a width-first search algorithm-oriented acceleration device and method and a storage medium. The device comprises a memory module which is used for storing graph data and a search result, a execution unit module which is used for constructing a multi-stage assembly line according to the internal characteristics of the width-first-oriented search algorithm so as to executea traversal search task, a memory access multiplexing module which is used for processing a memory access request of the assembly line according to a set priority, a scheduling module which is used for distributing the response data of the memory module to an idle execution unit; and a control module which is used for controlling and managing each module. The method and the device can improve thecomputational efficiency of graph data processing.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

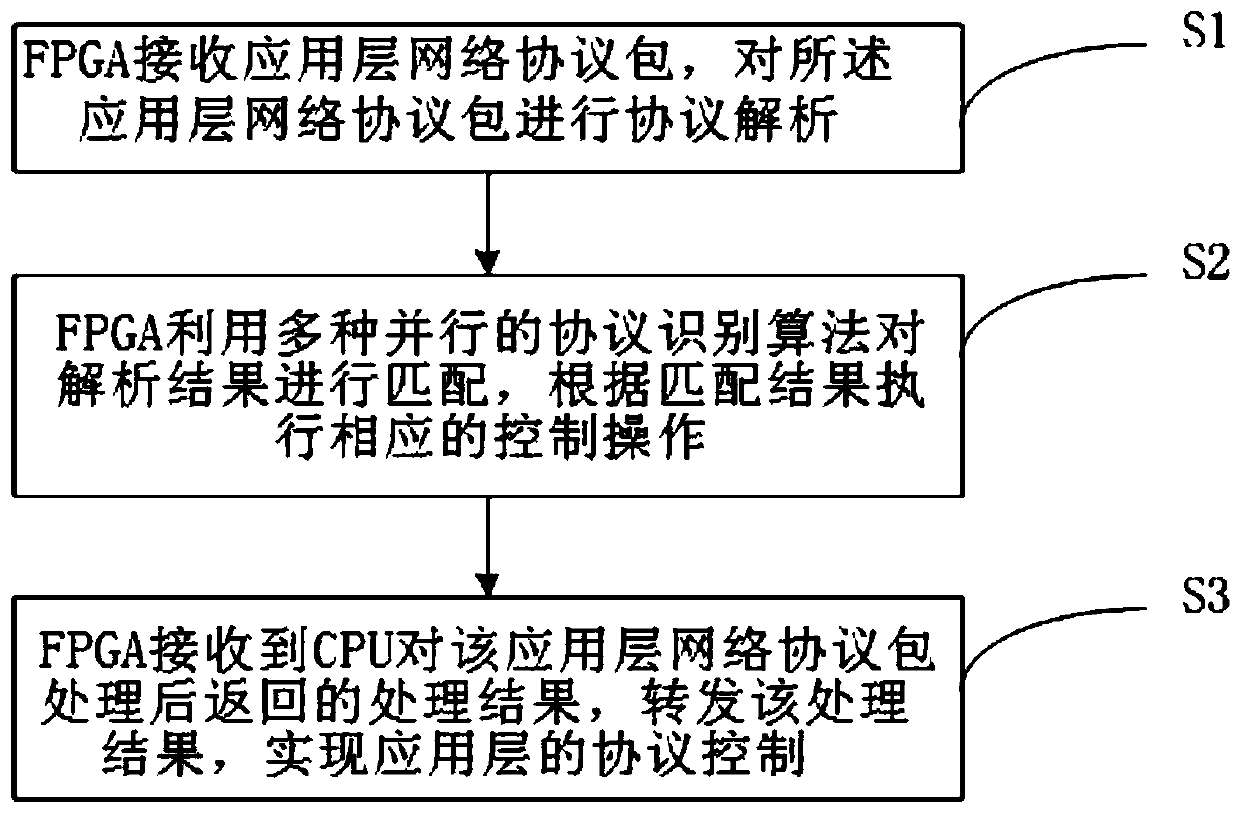

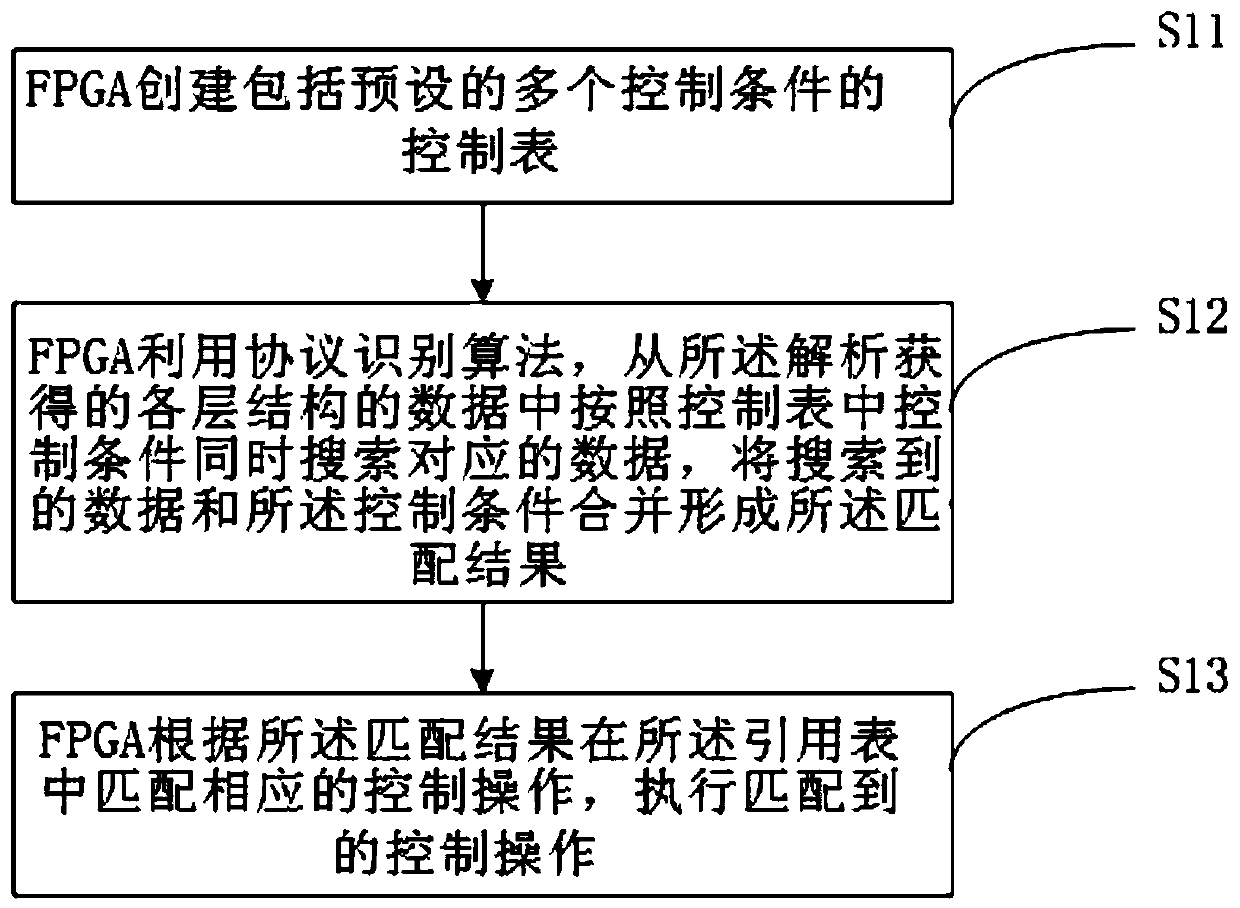

Ethernet application layer protocol control system and method based on hardware acceleration

ActiveCN111245866AReduce the load on the CPUImprove efficiencyTransmissionEmbedded systemHardware acceleration

The invention provides an Ethernet application layer protocol control system based on hardware acceleration. An FPGA performs protocol analysis on application layer network protocol packets, matches the analysis result by utilizing a plurality of parallel protocol identification algorithms, executes a corresponding control operation according to the matching result, discards or forwards the application layer network protocol packets which do not need to be subjected to deep processing, and transmitting the application layer network protocol packets which need to be subjected to deep processingto a CPU for processing; and the FPGA receives and forwards a processing result returned by the CPU to realize protocol control of the application layer. According to the system, a software and hardware combination mode is adopted, the communication connection between the FPGA and the CPU is added, a process of analyzing and processing application layer network protocol packets in a CPU in the prior art is transferred to an FPGA to be realized, the application layer network protocol packets are processed in parallel through the FPGA, and the application layer network protocol packets needingto be processed by the CPU are captured and intercepted and are transmitted back to the CPU for processing, so that the burden of the CPU is greatly reduced, the Ethernet application layer protocol control efficiency is improved, and CPU acceleration is realized.

Owner:深圳市龙信信息技术有限公司

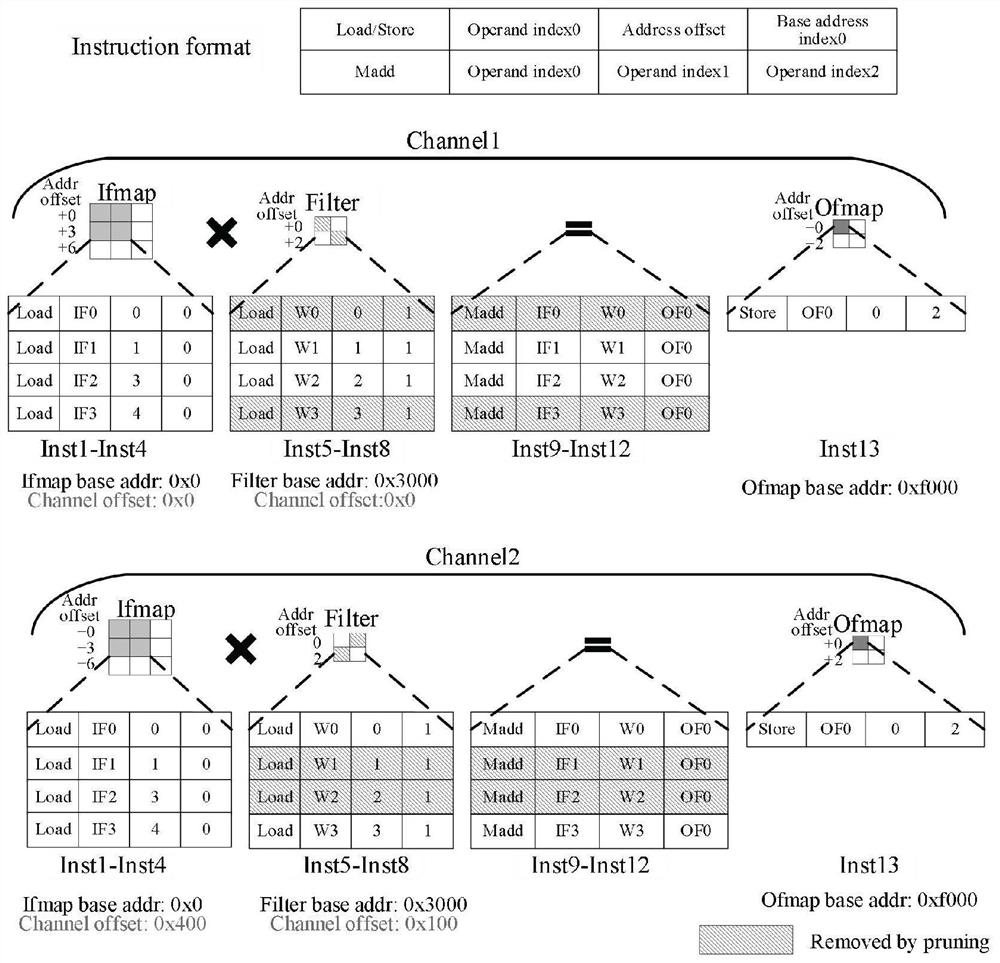

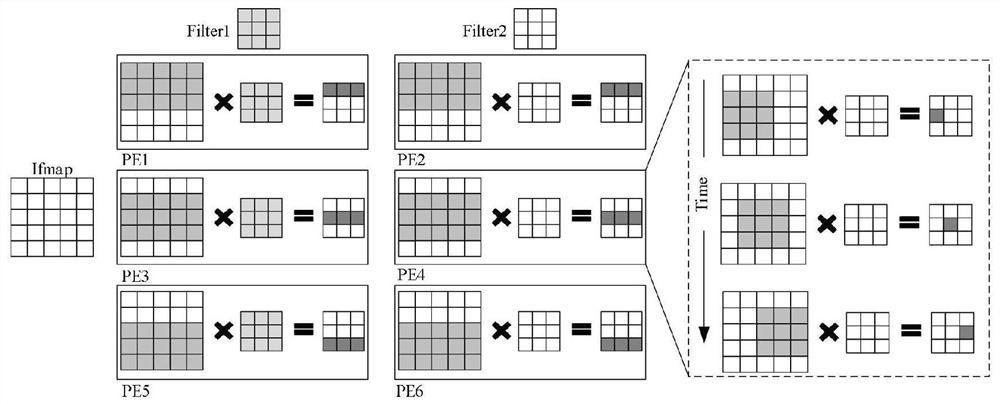

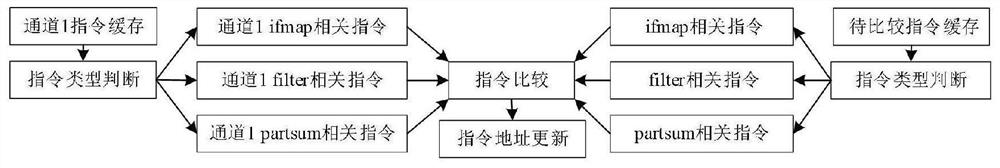

Sparse convolutional neural network acceleration method and system based on data flow architecture

ActiveCN112015473AAccelerated implementationReduce constant visitsInstruction analysisNext instruction address formationAlgorithmTheoretical computer science

The invention provides a sparse convolutional neural network acceleration method and system based on a data flow architecture. For sparse convolution application, a set of instruction sharing detection device and a sparse convolution acceleration method are designed in a software mode. The instructions generated by the compiler are detected and compared, the instructions with the completely same instruction content in all the instructions are marked, the addresses of the instructions are set to be the same addresses, instruction sharing in sparse convolution is achieved, therefore, access of instruction loading to a memory is reduced, and the sparse convolution running time is prolonged.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

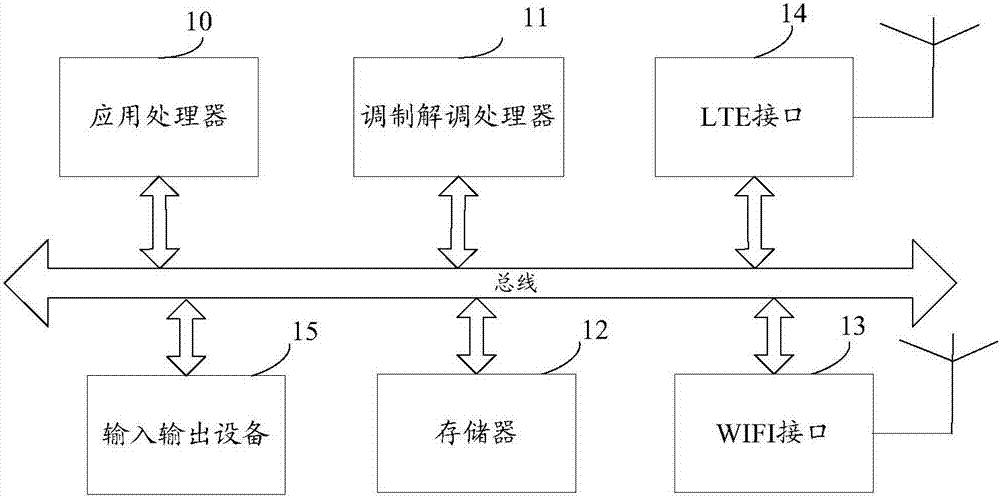

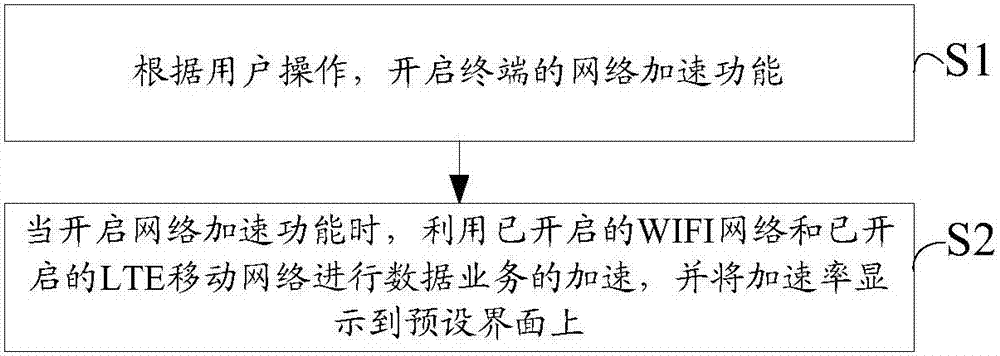

Terminal and network acceleration control method thereof thereof

InactiveCN107295574AAccelerated implementationImprove intelligenceNetwork traffic/resource managementNetwork topologiesWifi networkAcceleration rate

The invention discloses a terminal and a network acceleration control method thereof. The terminal comprises a WIFI interface and an LTE interface. The method comprises the following steps of according to the operation of a user, turning on the network acceleration function of the terminal; when the network acceleration function is turned on, accelerating the data service by utilizing an opened WIFI network and an opened LTE mobile network, and displaying the acceleration rate on a preset interface. According to the invention, the real network acceleration is realized by using the WIFI and the LTE. The acceleration can be carried out according to an acceleration mode selected by the user. Meanwhile, the detailed information of the acceleration can be displayed, such as the increased efficiency of the speed, the consumption of mobile network data and the like. Therefore, the intelligence and the flexibility of network acceleration are improved. The user experience is improved.

Owner:NUBIA TECHNOLOGY CO LTD

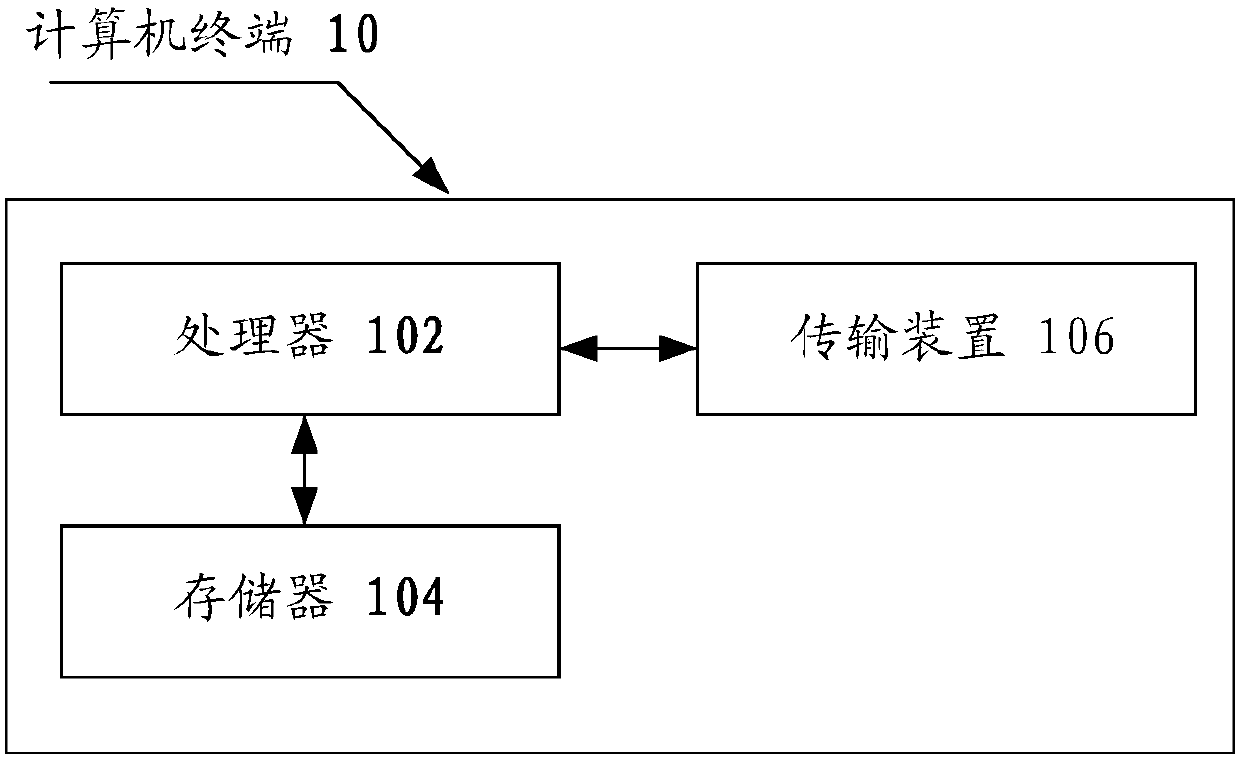

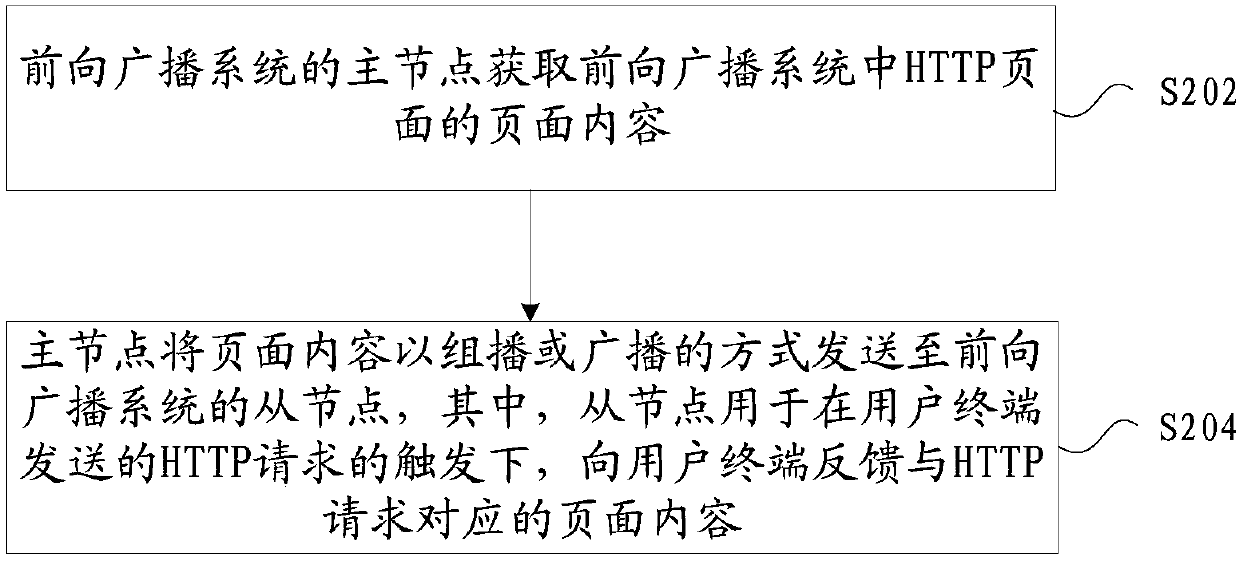

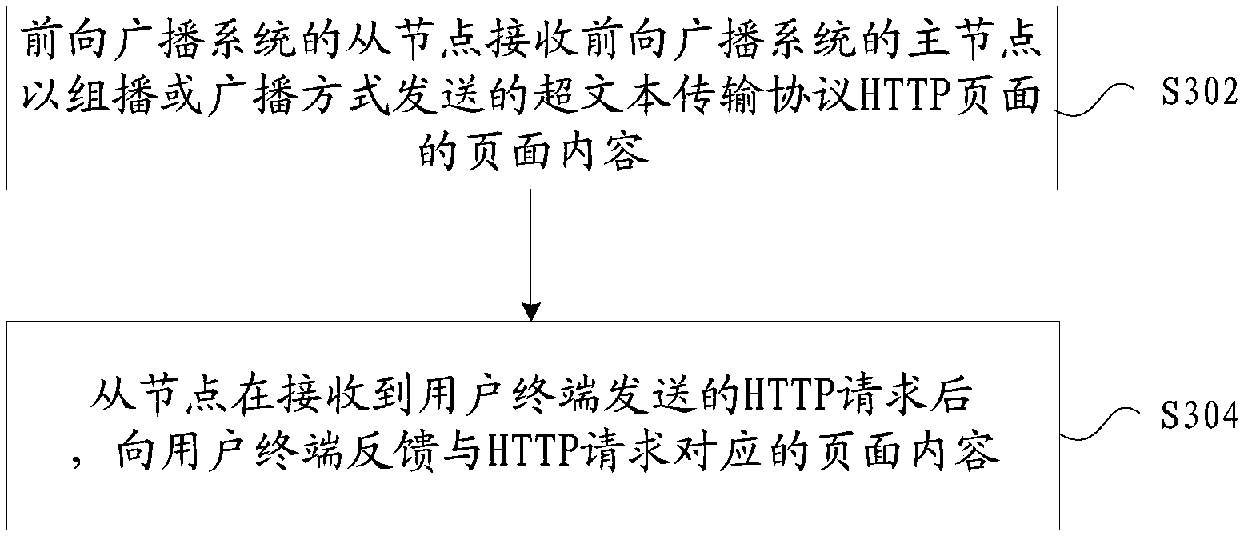

Processing method and processing device for page content, main node and auxiliary node

ActiveCN107800666ASolve the problem of not being able to effectively adapt to bandwidth-limited systemsEasy accessTransmissionTraffic capacityComputer terminal

The invention provides a processing method and a processing device for a page content, a main node and an auxiliary node, wherein the processing method comprises the steps of acquiring the page content of a hyper text transfer protocol (HTTP) page in a forward broadcast system by a main node of the forward broadcast system; and transmitting the page content to an auxiliary node of the forward broadcast system by the main node in a multicast or broadcast manner, wherein the auxiliary node is used for performing feedback of the page content which corresponds with the HTTP request to a user terminal through triggering of the HTTP request which is transmitted from the user terminal. The processing method, the processing device, the main node and the auxiliary node has advantages of settling aproblem of incapability of effectively adapting a limited-bandwidth system by HTTP page accelerating technology in related technology, furthermore saving bandwidth flow, and realizing user HTTP accessing acceleration on the condition that the occupied bandwidth is reduced.

Owner:ZTE CORP

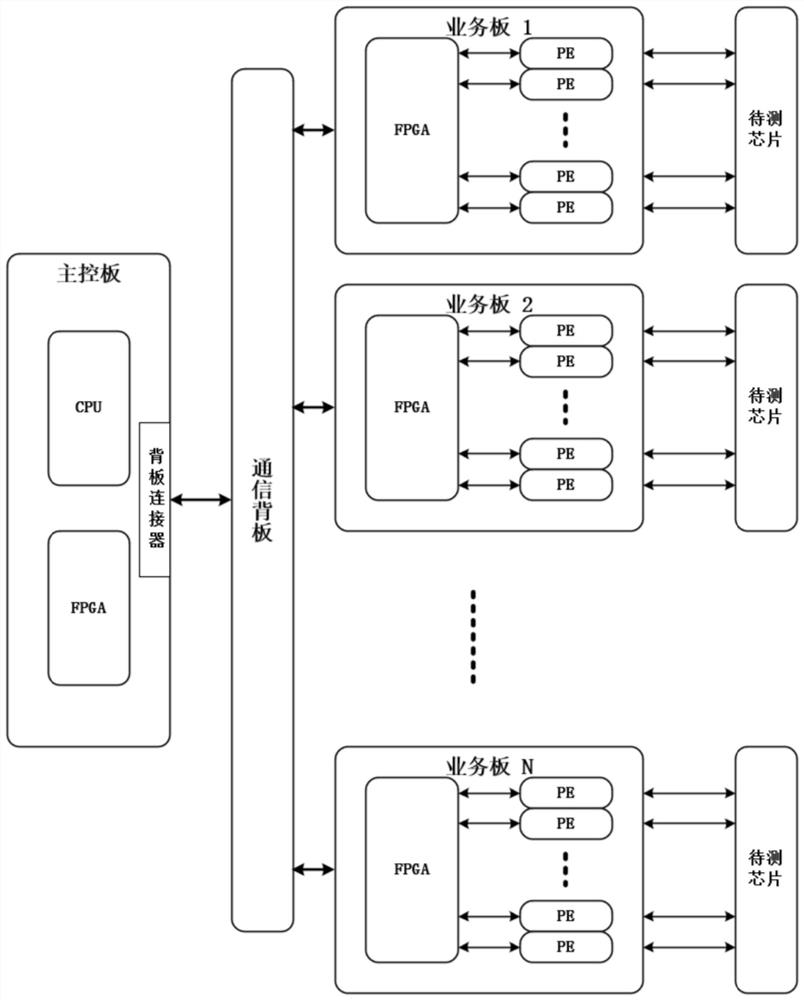

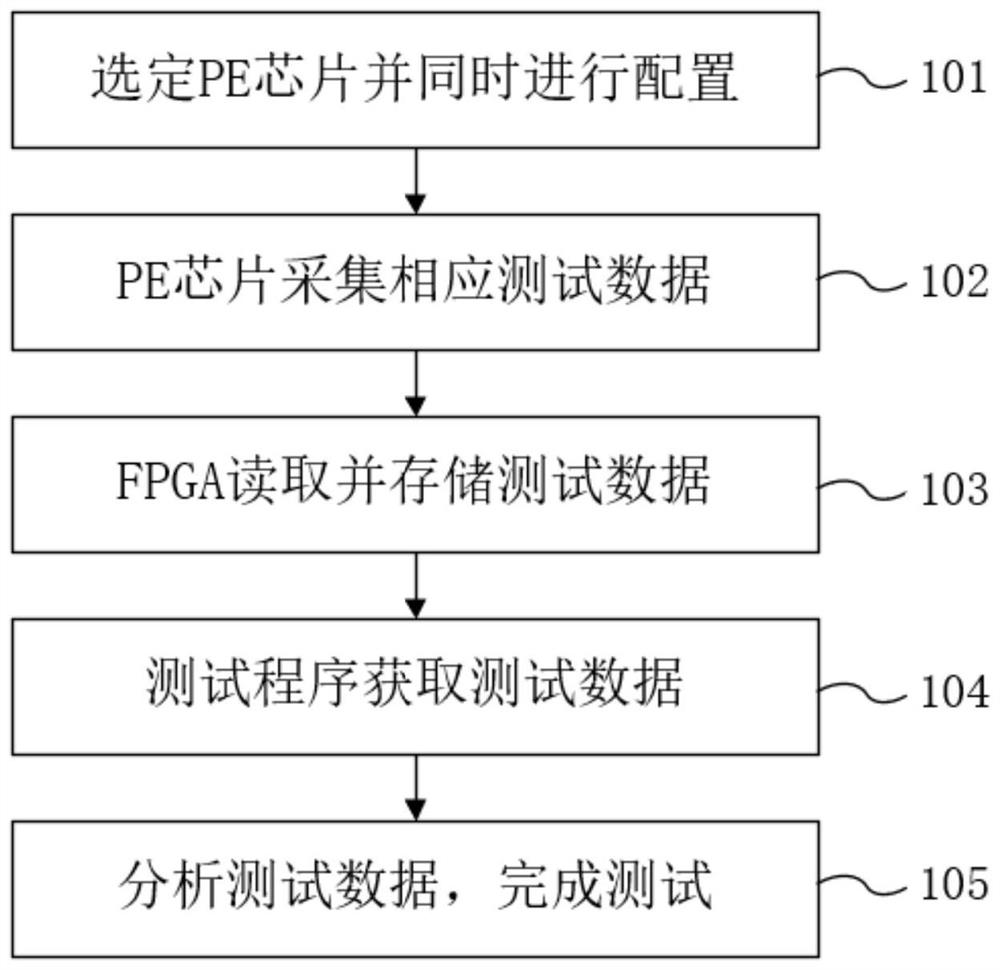

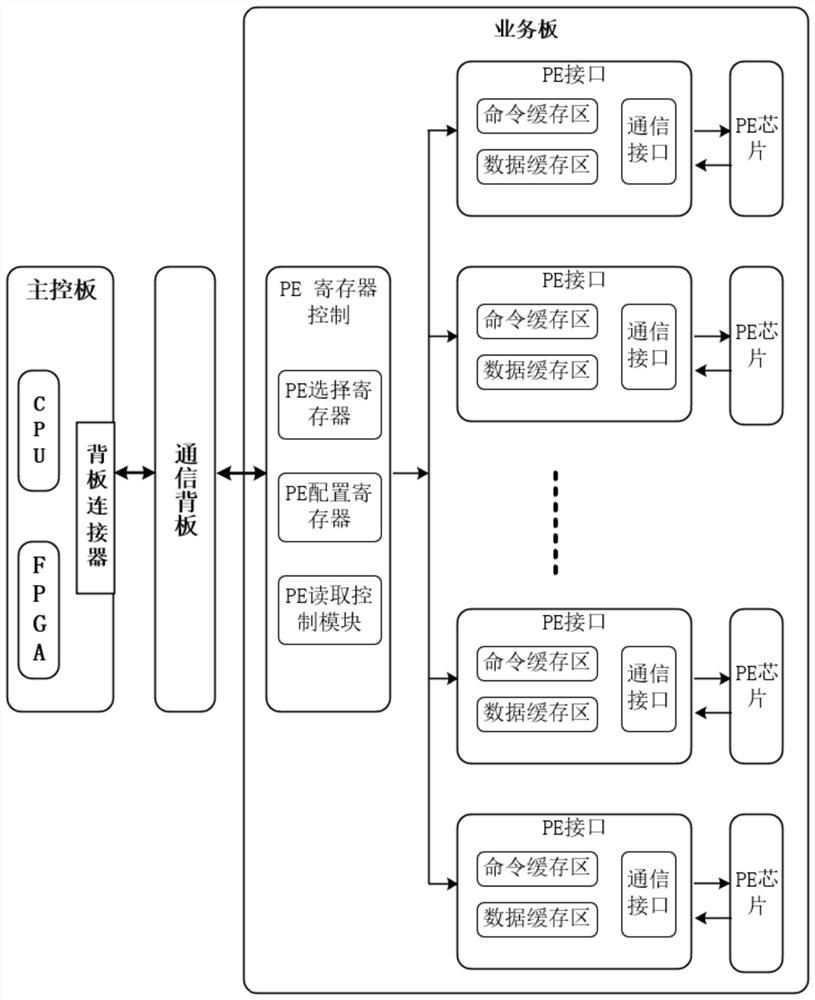

Acceleration method and device based on ATE equipment chip test and test machine system

ActiveCN114356820AReduce configuration timeShorten read timeElectronic circuit testingEnergy efficient computingTest efficiencyAccess time

The invention provides an acceleration method and device based on ATE equipment chip testing and a testing machine system. The acceleration method comprises the following steps: selecting and configuring a pin circuit chip; the pin circuit chip collects test data fed back by the chip to be tested; at a preset time interval, the FPGA on each service board reads the test data in all the pin circuit chips on the service board in parallel, and stores the read test data in the FPGA; the test program obtains test data of all pin circuit chips on the service board by reading data stored in the FPGA on each service board; and the test program analyzes the test data to complete the test of the to-be-tested chip. According to the scheme provided by the invention, by reducing the access times of the test program to the pin circuit chip in the chip test process of the ATE equipment, the configuration time and reading time of the chip are reduced, the chip test time is shortened, the chip test efficiency is improved, hardware adjustment is not needed, and only the FPGA on the service board needs to be designed and upgraded.

Owner:杭州加速科技有限公司

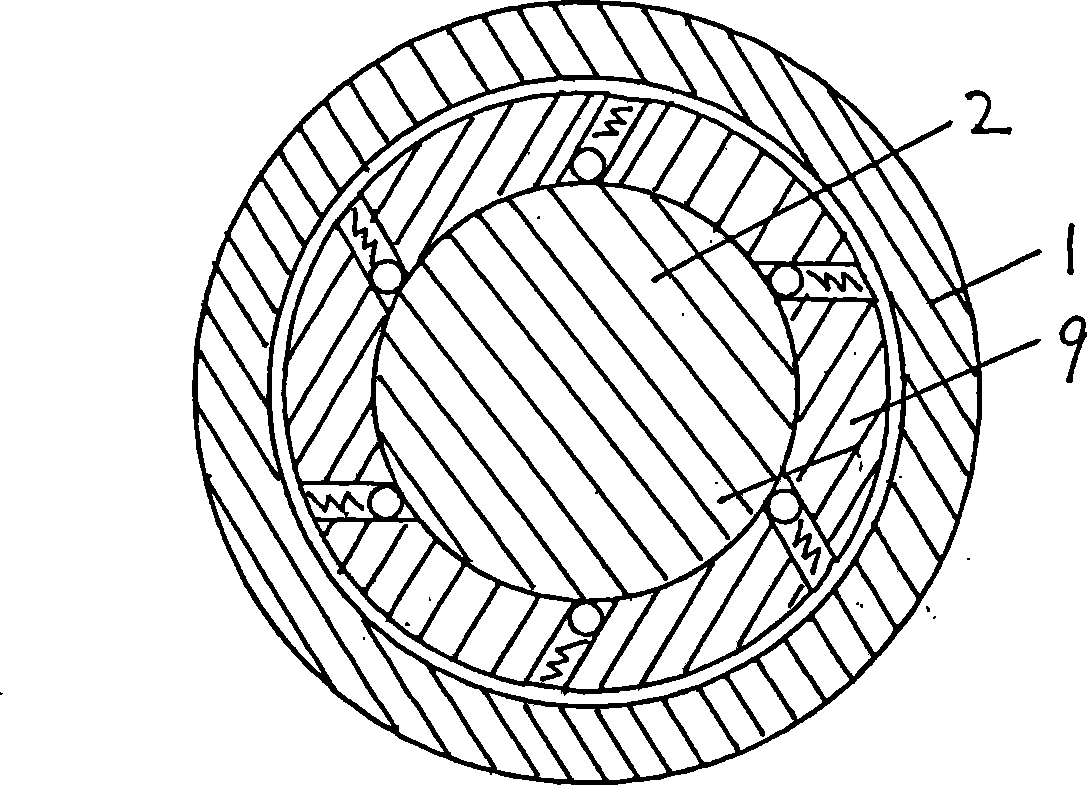

Electromagnetic power thruster

InactiveCN104454416AAccelerated implementationImpede accelerationCosmonautic vehiclesCosmonautic propulsion system apparatusEngineeringMagnet

The invention discloses an electromagnetic power thruster which comprises an ionization section, an accelerating section and a neutralization jet section. The thruster is characterized in that the ionization section is composed of a graphite electrode pipeline (2) which is connected with a tail gas jet port end of a micro rocket engine (1); the accelerating section comprises a weak electrode pipeline (4) and an enhancement electrode plate (9) on the outer periphery of the weak electrode pipeline (4), and the weak electrode pipeline (4) penetrates through an annular channel formed by an outer cylindrical magnet (5) and an inner cylindrical magnet (6); the neutralization jet section comprises a cathode ray pipe (8) installed on the outer side of the weak electrode pipeline (4) , a front magnetism-isolating sleeve (3) is arranged between the ionization section and the accelerating section, and a rear magnetism-isolating sleeve (7) is arranged between the accelerating section and the neutralization jet section. The electromagnetic power thruster is simple in structure and low in manufacturing cost, energy is saved, the specific impulse and the thrust-to-power ratio can be adjusted at will according to requirements, the single equipment can bear high power, and large thrust force can also be obtained.

Owner:周纪兵

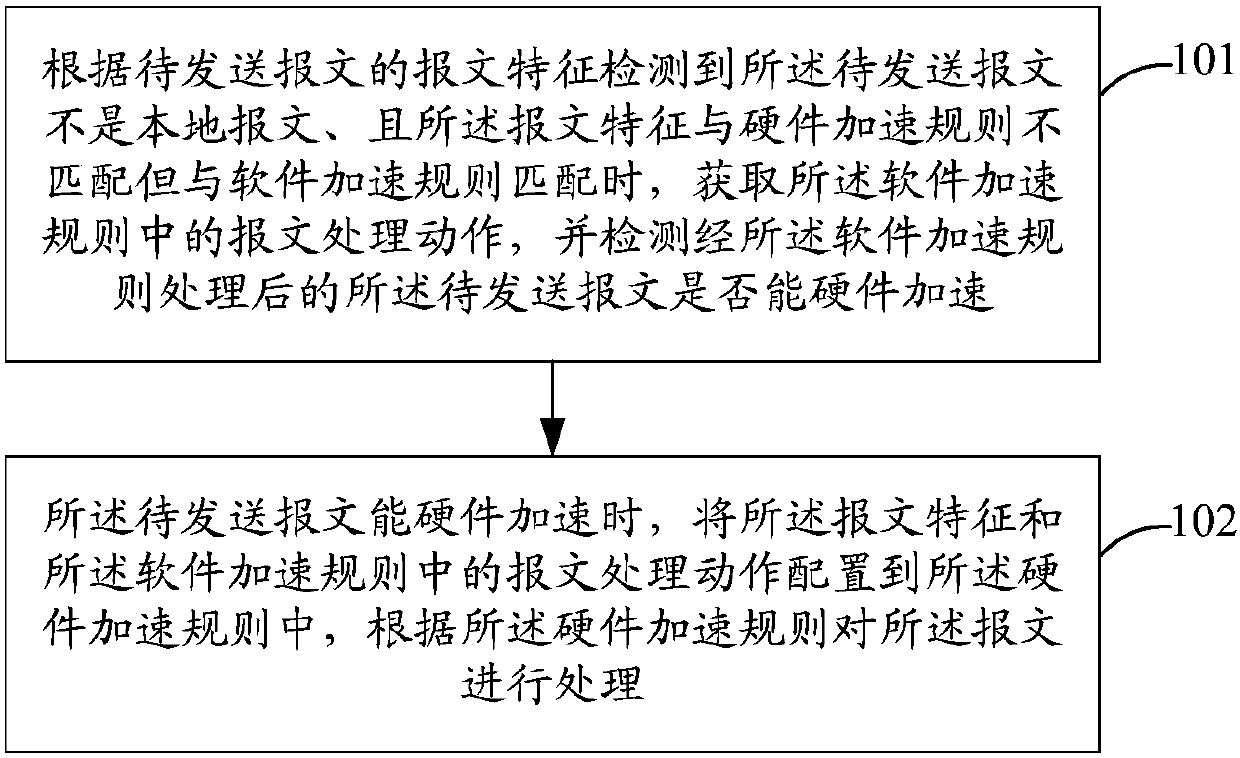

Message accelerating method and device

InactiveCN107592287AAccelerated implementationEasy to handleSecuring communicationComputer hardwareMessage processing

The invention discloses a message accelerating method, and the method comprises the steps: detecting whether a to-be-transmitted message is a local message or not according to the features of the to-be-transmitted message; obtaining a message processing operation in a software accelerating rule when the message features is not matched with a hardware accelerating rule but is matched with the software accelerating rule, and detecting whether the hardware accelerating of the to-be-transmitted message processed through the software accelerating rule can be carried out or not; configuring the message features and the message processing operation in the software accelerating rule in the hardware accelerating rule if the hardware accelerating of the to-be-transmitted message can be carried out,and carrying out the processing of the to-be-transmitted message according to the hardware accelerating rule. The invention also discloses a message accelerating device.

Owner:SANECHIPS TECH CO LTD

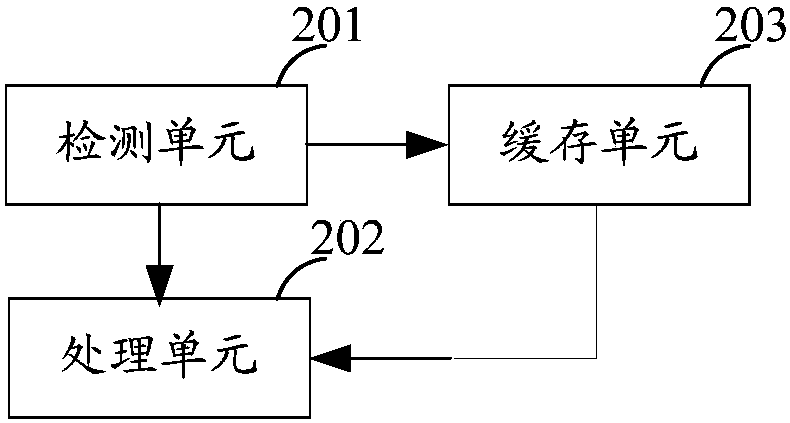

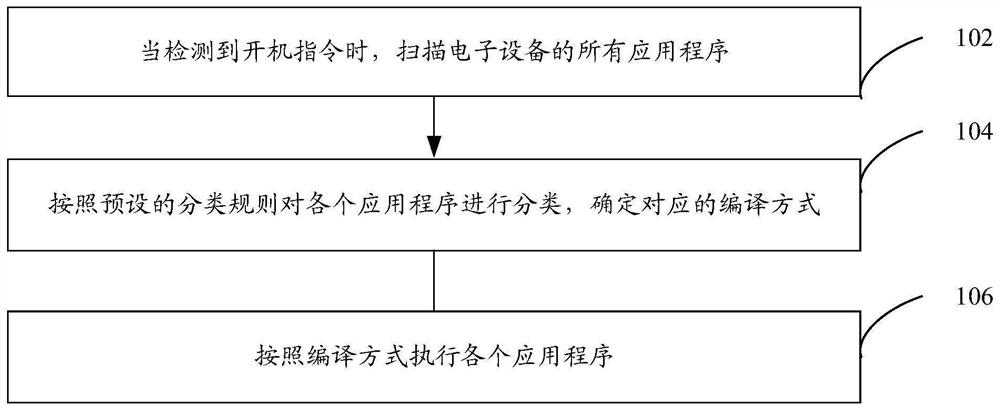

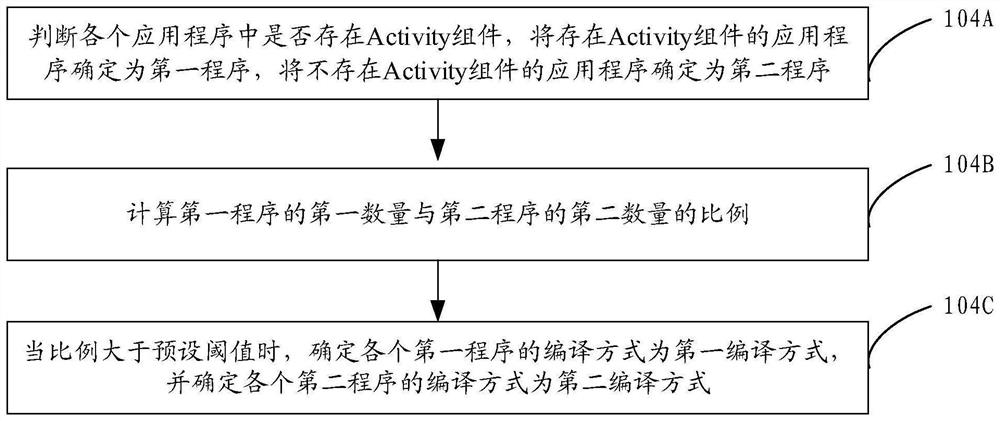

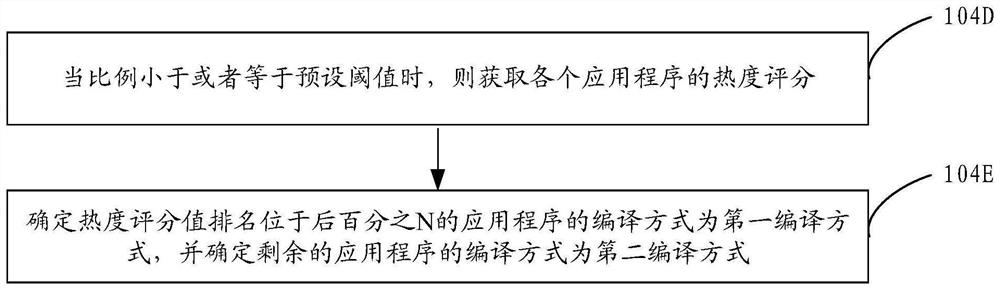

Startup acceleration method and device, electronic equipment and storage medium

PendingCN114489672AAccelerated implementationRealize bootingCharacter and pattern recognitionProgram loading/initiatingSoftware engineeringClassification rule

The embodiment of the invention provides a startup acceleration method and device, electronic equipment and a storage medium, and the method comprises the steps: when a startup instruction is detected, scanning all application programs of the electronic equipment, classifying each application program according to a preset classification rule, determining a corresponding compiling mode, and executing each application program according to the compiling mode. Compared with the traditional method for performing dex2oat compiling on all the application programs, the method has the advantages that the compiling mode of the application programs is determined after classification according to the related information of the application programs, so that the compiling mode of each application program is the optimal compiling mode, the loading and compiling speed of the application programs is greatly increased, and the loading and compiling efficiency of the electronic equipment is improved. Acceleration of startup of the electronic equipment is achieved, and then user experience is improved.

Owner:SHENZHEN TCL NEW-TECH CO LTD