PBKDF2 cryptographic algorithm accelerating method and used device

A cryptographic algorithm and acceleration device technology, applied to secure communication devices, user identity/authority verification, and key distribution, can solve problems such as limited performance, limited operating speed, and replacement of CPUs or GPUs, and achieve improved throughput and high pipeline Working frequency, the effect of ensuring correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

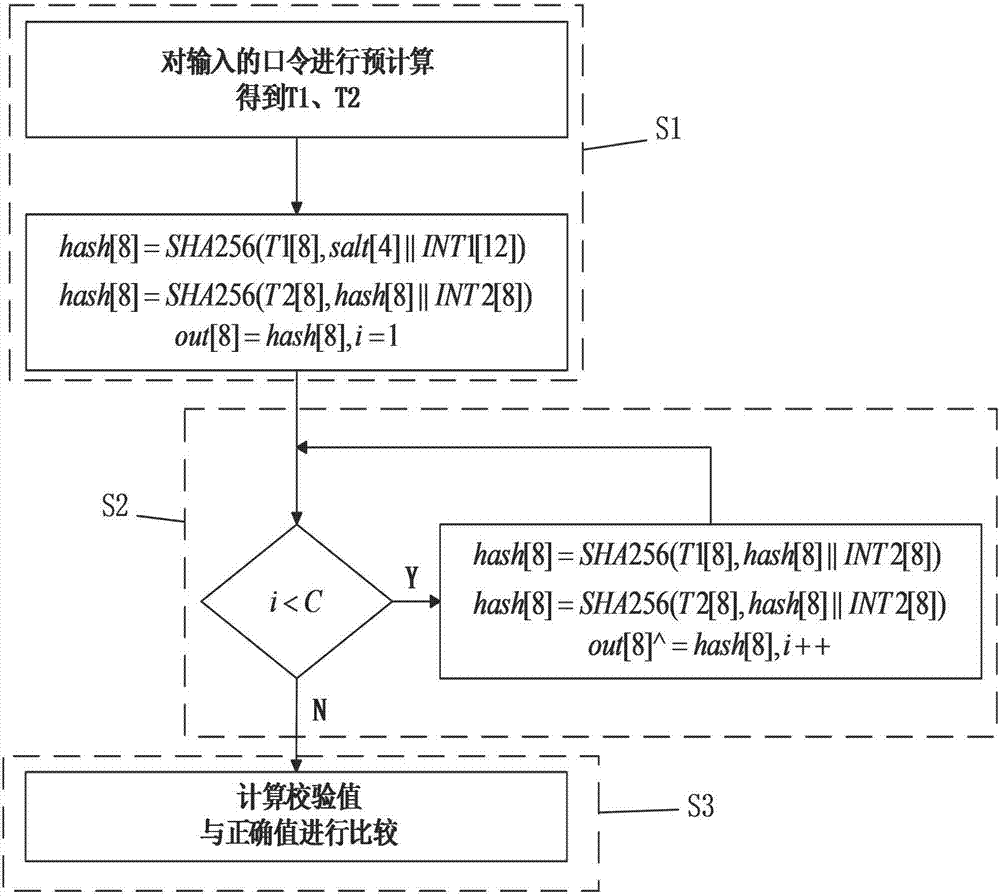

Method used

Image

Examples

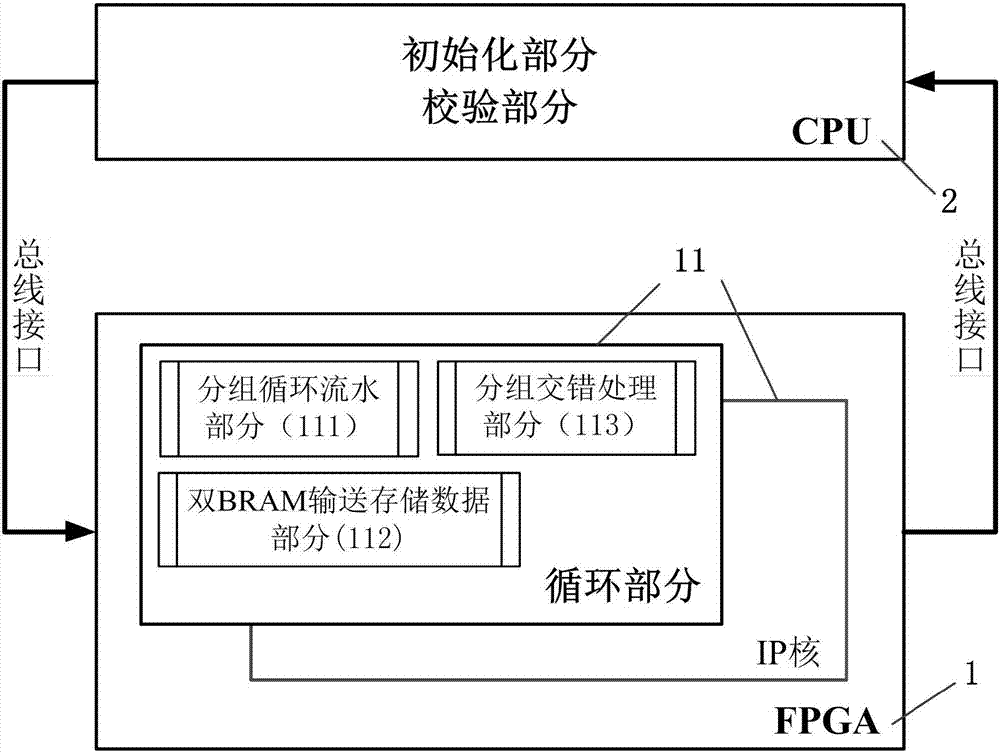

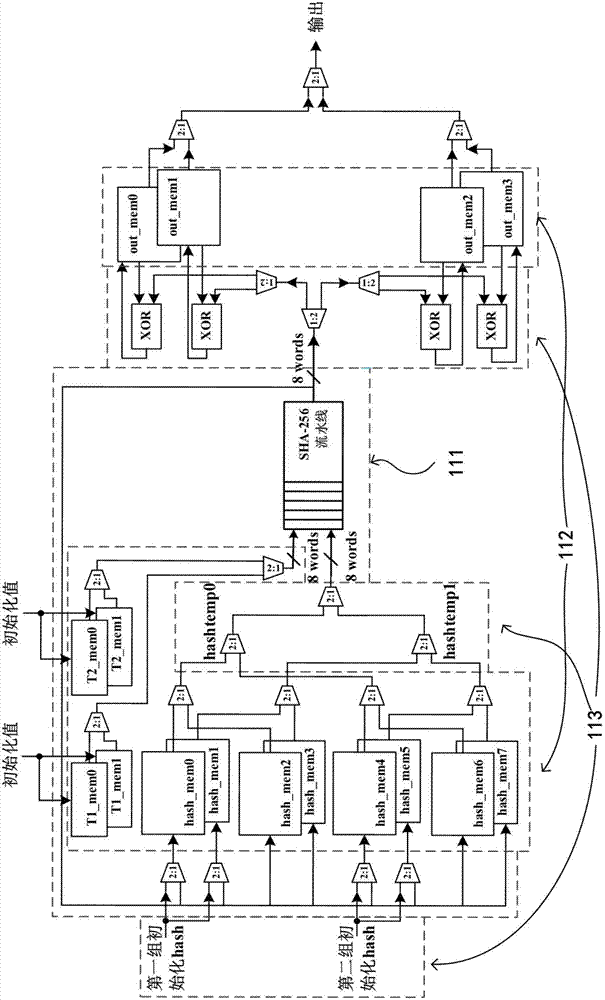

Embodiment 1

[0052] Embodiment 1, the PBKDF2 cryptographic algorithm acceleration device includes a CPU+FPGA heterogeneous system composed of FPGA1 and general-purpose CPU2. CPU2 and FPGA1 are connected to each other through the bus interface; FPGA1 not only has the programmability and flexibility of software, but also has the characteristics of high throughput and low delay of ASIC; the internal resources of FPGA1 can be reconfigured, which is convenient for design Data parallelism and pipeline parallelism, easy to balance data parallelism and pipeline parallelism. The present invention utilizes the characteristics of FPGA1 to accelerate the implementation of the PBKDF2 algorithm, so that when using the dictionary method, the key recovery of various applications with the PBKDF2 cryptographic algorithm as its main encryption algorithm can be completed at high speed on the general-purpose CPU+FPGA device, that is, Heterogeneous computing is used to improve the performance of the key recover...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More