Intelligent acceleration chip suitable for power system edge calculation

An edge computing and accelerating chip technology, applied in energy-saving computing, resource allocation, biological neural network model, etc., can solve the problems of increased terminal cost, disadvantageous edge computing battery-powered terminal deployment, and high battery-powered power consumption requirements. The effect of low power consumption, fast operation speed and simple chip structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, but it should be understood that the protection scope of the present invention is not limited by the specific embodiments.

[0021] Unless expressly stated otherwise, throughout the specification and claims, the term "comprise" or variations thereof such as "includes" or "includes" and the like will be understood to include the stated elements or constituents, and not Other elements or other components are not excluded.

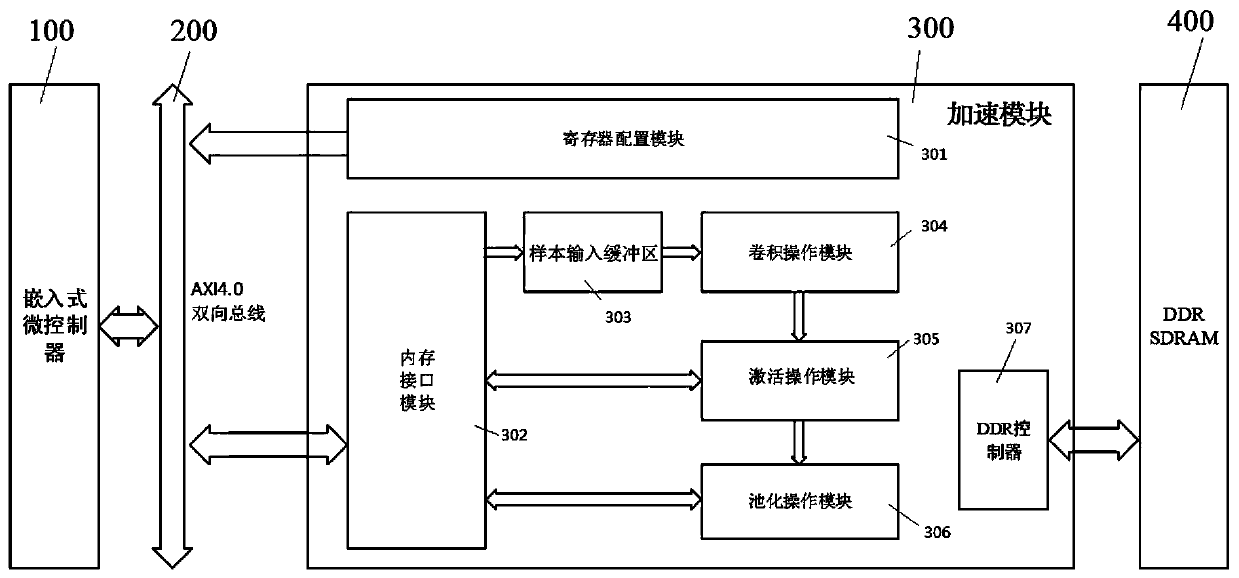

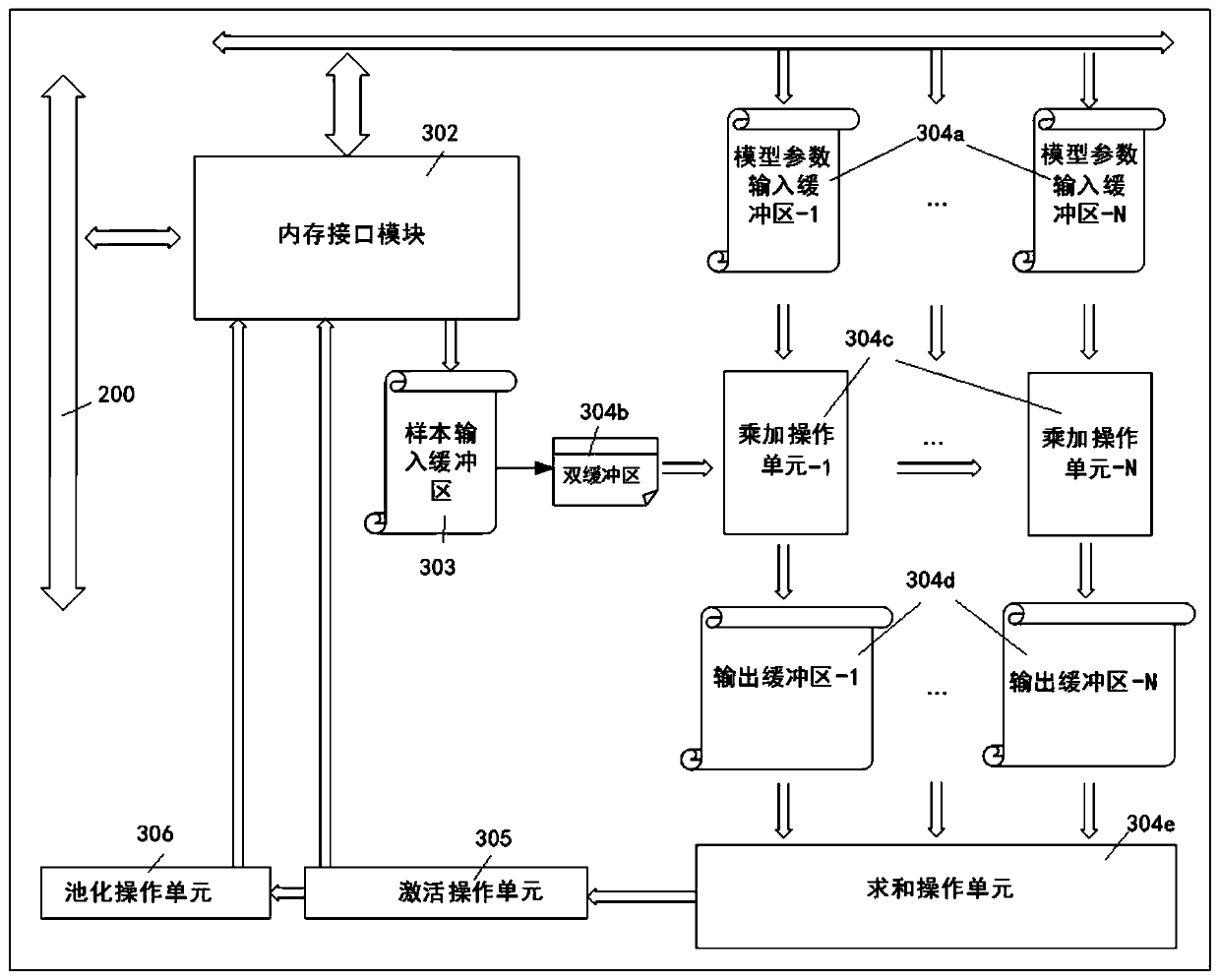

[0022] In order to pursue the balance between power consumption and calculation speed, the present invention proposes an intelligent acceleration chip suitable for edge computing in power systems. The main design idea is: design an intelligent acceleration chip for a lightweight deep neural network The task of intelligent inference at the edge of the Internet of Things mainly completes the inference work of deep learning, m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More