Winograd YOLOv2 target detection model method based on FPGA acceleration

A target detection and model technology, applied in the field of computer vision and edge computing, can solve problems such as high power consumption and unreasonable on-chip resource allocation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0088] Below in conjunction with accompanying drawing, further describe the present invention through embodiment, but do not limit the scope of the present invention in any way.

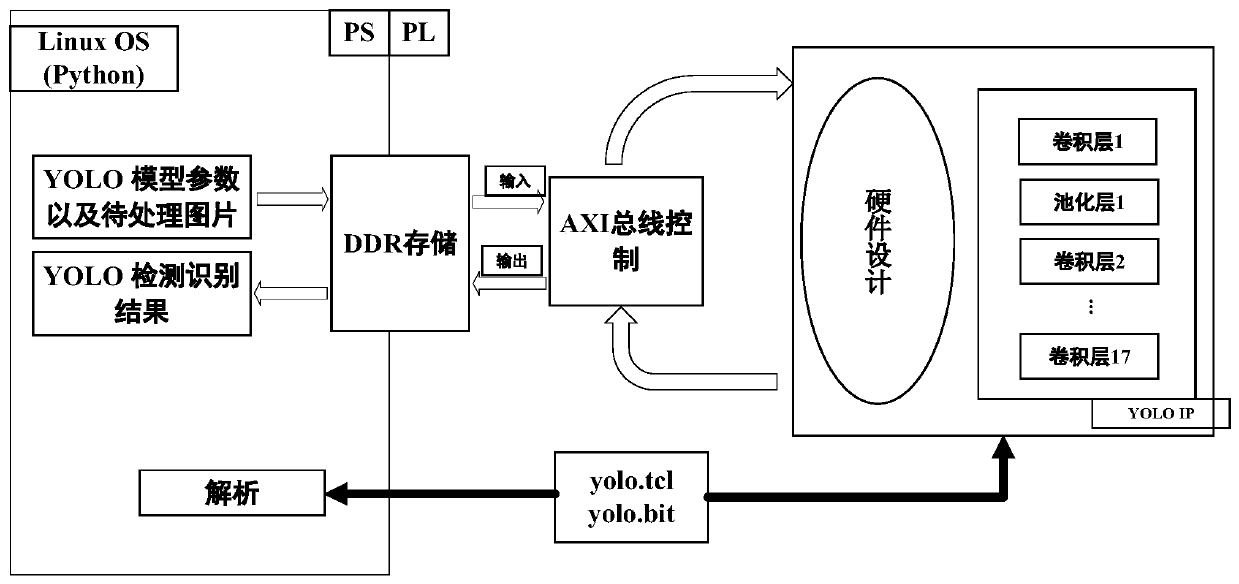

[0089] The overall hardware architecture of the accelerator designed by the present invention is as follows: figure 1 As shown, first complete the training of the YOLOv2 model on the host computer, use the VOC data set (VOC2007+2012), randomly select 16551 pictures as the training set, and 16492 pictures as the test set. Then carry out the fixed-point task of the model, and complete the edge algorithm on the embedded side. The PS side integrates the ARM core and is equipped with a Linux operating system. When transplanting the operating system, the Python language environment is reserved. The CPU can control all interfaces between the PS and PL, and the accelerator Through CPU scheduling, the feature map of the YOLO model is input into the DDR cache, and the bus interacts with the peripheral circuit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More