Non-Volatile Memory Devices Enabling Persistent In-Memory Computing Systems

SEP 2, 20259 MIN READ

Generate Your Research Report Instantly with AI Agent

PatSnap Eureka helps you evaluate technical feasibility & market potential.

NVM Technology Evolution and Objectives

Non-volatile memory (NVM) technologies have undergone significant evolution over the past decades, transforming from simple storage solutions to sophisticated components enabling persistent in-memory computing systems. The journey began with magnetic core memory in the 1950s, followed by the development of semiconductor-based memory technologies such as EPROM and EEPROM in the 1970s and 1980s. Flash memory emerged in the late 1980s, revolutionizing portable storage and eventually becoming ubiquitous in consumer electronics.

The early 2000s witnessed the emergence of next-generation NVM technologies including Phase-Change Memory (PCM), Resistive RAM (ReRAM), and Magnetoresistive RAM (MRAM). These technologies promised better performance characteristics than flash memory, including faster write speeds, higher endurance, and lower power consumption. The mid-2010s marked a significant milestone with Intel and Micron's introduction of 3D XPoint technology, commercially known as Optane, which bridged the performance gap between DRAM and NAND flash.

Current technological trends are focused on enhancing NVM performance metrics while reducing manufacturing costs. Density improvements continue through 3D stacking and multi-level cell architectures. Latency reduction remains a critical focus area, with emerging NVMs targeting sub-microsecond access times to compete with volatile memory technologies. Power efficiency improvements are being pursued through novel materials and circuit designs that minimize energy consumption during read/write operations.

The primary objective of NVM technology development for persistent in-memory computing is to create memory devices that combine the speed of DRAM with the persistence of storage. This convergence aims to eliminate the traditional memory hierarchy, reducing data movement between volatile and non-volatile domains. Such systems would maintain computational state across power cycles, enabling instant-on capabilities and resilience against power failures.

Additional technical objectives include achieving write endurance comparable to DRAM (>10^16 cycles), reducing write latency to nanosecond range, and ensuring data retention periods of 10+ years at operating temperatures. Scalability to sub-10nm process nodes while maintaining performance characteristics represents another critical goal for mass adoption in computing systems.

The industry is also pursuing architectural innovations that leverage NVM's unique characteristics. This includes developing memory-centric computing architectures where processing occurs closer to data, reducing energy consumption and latency associated with data movement. Standardization efforts are underway to create unified programming models and interfaces that abstract the complexities of persistent memory systems, making them more accessible to software developers.

The early 2000s witnessed the emergence of next-generation NVM technologies including Phase-Change Memory (PCM), Resistive RAM (ReRAM), and Magnetoresistive RAM (MRAM). These technologies promised better performance characteristics than flash memory, including faster write speeds, higher endurance, and lower power consumption. The mid-2010s marked a significant milestone with Intel and Micron's introduction of 3D XPoint technology, commercially known as Optane, which bridged the performance gap between DRAM and NAND flash.

Current technological trends are focused on enhancing NVM performance metrics while reducing manufacturing costs. Density improvements continue through 3D stacking and multi-level cell architectures. Latency reduction remains a critical focus area, with emerging NVMs targeting sub-microsecond access times to compete with volatile memory technologies. Power efficiency improvements are being pursued through novel materials and circuit designs that minimize energy consumption during read/write operations.

The primary objective of NVM technology development for persistent in-memory computing is to create memory devices that combine the speed of DRAM with the persistence of storage. This convergence aims to eliminate the traditional memory hierarchy, reducing data movement between volatile and non-volatile domains. Such systems would maintain computational state across power cycles, enabling instant-on capabilities and resilience against power failures.

Additional technical objectives include achieving write endurance comparable to DRAM (>10^16 cycles), reducing write latency to nanosecond range, and ensuring data retention periods of 10+ years at operating temperatures. Scalability to sub-10nm process nodes while maintaining performance characteristics represents another critical goal for mass adoption in computing systems.

The industry is also pursuing architectural innovations that leverage NVM's unique characteristics. This includes developing memory-centric computing architectures where processing occurs closer to data, reducing energy consumption and latency associated with data movement. Standardization efforts are underway to create unified programming models and interfaces that abstract the complexities of persistent memory systems, making them more accessible to software developers.

Market Analysis for Persistent Memory Solutions

The persistent memory solutions market is experiencing robust growth, driven by the increasing demand for high-performance computing systems that can process and store vast amounts of data efficiently. Current market valuations place the global persistent memory market at approximately 8 billion USD in 2023, with projections indicating a compound annual growth rate (CAGR) of 29% through 2030, potentially reaching 45 billion USD by the end of the decade.

Several key sectors are fueling this market expansion. Data centers represent the largest segment, accounting for roughly 40% of the current market share. The need for faster data access, reduced latency, and improved system resilience in cloud computing environments has positioned persistent memory as a critical technology for next-generation data center architectures.

Enterprise computing constitutes another significant market segment at 25%, where organizations are increasingly adopting persistent memory solutions to enhance database performance, accelerate analytics, and support real-time decision-making processes. Financial services firms, in particular, have been early adopters, leveraging persistent memory to minimize transaction processing times and maintain data integrity during system failures.

The edge computing sector is emerging as the fastest-growing segment with a 35% year-over-year growth rate. As IoT deployments expand and 5G networks proliferate, the demand for local data processing with persistence capabilities is surging. Autonomous vehicles, industrial automation, and smart city applications are driving this trend, requiring computing systems that can maintain state even during power interruptions.

From a geographical perspective, North America currently leads the market with a 42% share, followed by Asia-Pacific at 31% and Europe at 22%. However, the Asia-Pacific region is expected to witness the highest growth rate over the next five years, primarily due to increasing investments in digital infrastructure across China, Japan, South Korea, and India.

Customer requirements are evolving rapidly, with system architects prioritizing four key attributes: performance (particularly reduced latency), data persistence guarantees, power efficiency, and total cost of ownership. The performance-to-cost ratio remains a critical factor influencing adoption decisions, with many organizations conducting extensive proof-of-concept deployments before committing to large-scale implementations.

Market challenges include the relatively high cost of persistent memory compared to conventional storage solutions, compatibility issues with existing software stacks, and concerns about long-term reliability. These factors have somewhat constrained adoption rates, particularly among small and medium-sized enterprises with limited IT budgets.

Several key sectors are fueling this market expansion. Data centers represent the largest segment, accounting for roughly 40% of the current market share. The need for faster data access, reduced latency, and improved system resilience in cloud computing environments has positioned persistent memory as a critical technology for next-generation data center architectures.

Enterprise computing constitutes another significant market segment at 25%, where organizations are increasingly adopting persistent memory solutions to enhance database performance, accelerate analytics, and support real-time decision-making processes. Financial services firms, in particular, have been early adopters, leveraging persistent memory to minimize transaction processing times and maintain data integrity during system failures.

The edge computing sector is emerging as the fastest-growing segment with a 35% year-over-year growth rate. As IoT deployments expand and 5G networks proliferate, the demand for local data processing with persistence capabilities is surging. Autonomous vehicles, industrial automation, and smart city applications are driving this trend, requiring computing systems that can maintain state even during power interruptions.

From a geographical perspective, North America currently leads the market with a 42% share, followed by Asia-Pacific at 31% and Europe at 22%. However, the Asia-Pacific region is expected to witness the highest growth rate over the next five years, primarily due to increasing investments in digital infrastructure across China, Japan, South Korea, and India.

Customer requirements are evolving rapidly, with system architects prioritizing four key attributes: performance (particularly reduced latency), data persistence guarantees, power efficiency, and total cost of ownership. The performance-to-cost ratio remains a critical factor influencing adoption decisions, with many organizations conducting extensive proof-of-concept deployments before committing to large-scale implementations.

Market challenges include the relatively high cost of persistent memory compared to conventional storage solutions, compatibility issues with existing software stacks, and concerns about long-term reliability. These factors have somewhat constrained adoption rates, particularly among small and medium-sized enterprises with limited IT budgets.

Current NVM Landscape and Technical Barriers

The non-volatile memory (NVM) landscape has evolved significantly over the past decade, with several technologies emerging as potential enablers for persistent in-memory computing systems. Currently, the market is dominated by NAND Flash memory, which has reached maturity in terms of commercial deployment but faces scaling limitations. More advanced NVM technologies include Phase-Change Memory (PCM), Resistive RAM (ReRAM), Magnetoresistive RAM (MRAM), and Ferroelectric RAM (FeRAM), each offering unique advantages for persistent memory applications.

PCM, based on chalcogenide materials that switch between amorphous and crystalline states, offers high endurance (10^6-10^8 cycles) and reasonable write speeds. Intel and Micron's 3D XPoint technology, marketed as Optane, represents the most commercially successful PCM implementation to date, positioned between DRAM and NAND Flash in the memory hierarchy.

ReRAM, which operates by forming and dissolving conductive filaments in metal-oxide materials, provides excellent scalability and low power consumption. Companies like Western Digital and Crossbar have made significant investments in this technology, though widespread commercial deployment remains limited.

MRAM, particularly Spin-Transfer Torque MRAM (STT-MRAM), leverages magnetic tunnel junctions to store data and offers nearly unlimited write endurance with SRAM-like performance. Everspin Technologies has pioneered commercial MRAM products, with major foundries including TSMC and Samsung incorporating MRAM into their technology roadmaps.

Despite these advancements, several technical barriers impede the widespread adoption of NVM in persistent in-memory computing systems. The most significant challenge is the performance gap between NVM technologies and DRAM, with write latencies typically 3-10x slower and read latencies 2-4x slower than conventional volatile memory. This performance disparity creates bottlenecks in systems designed for high-throughput computing.

Endurance limitations present another critical barrier, particularly for PCM and ReRAM, which can withstand significantly fewer write cycles than DRAM. This necessitates sophisticated wear-leveling algorithms and redundancy schemes that add complexity to memory controllers and system architecture.

Power consumption during write operations remains substantially higher for most NVM technologies compared to DRAM, creating thermal management challenges in dense computing environments. Additionally, the cell-to-cell variability in resistance states introduces reliability concerns that must be addressed through error correction mechanisms.

The integration of NVM into existing computing architectures presents significant challenges, requiring modifications to memory controllers, cache coherence protocols, and operating systems. The lack of standardized interfaces and programming models further complicates adoption, as software developers must navigate different persistence semantics across various NVM implementations.

PCM, based on chalcogenide materials that switch between amorphous and crystalline states, offers high endurance (10^6-10^8 cycles) and reasonable write speeds. Intel and Micron's 3D XPoint technology, marketed as Optane, represents the most commercially successful PCM implementation to date, positioned between DRAM and NAND Flash in the memory hierarchy.

ReRAM, which operates by forming and dissolving conductive filaments in metal-oxide materials, provides excellent scalability and low power consumption. Companies like Western Digital and Crossbar have made significant investments in this technology, though widespread commercial deployment remains limited.

MRAM, particularly Spin-Transfer Torque MRAM (STT-MRAM), leverages magnetic tunnel junctions to store data and offers nearly unlimited write endurance with SRAM-like performance. Everspin Technologies has pioneered commercial MRAM products, with major foundries including TSMC and Samsung incorporating MRAM into their technology roadmaps.

Despite these advancements, several technical barriers impede the widespread adoption of NVM in persistent in-memory computing systems. The most significant challenge is the performance gap between NVM technologies and DRAM, with write latencies typically 3-10x slower and read latencies 2-4x slower than conventional volatile memory. This performance disparity creates bottlenecks in systems designed for high-throughput computing.

Endurance limitations present another critical barrier, particularly for PCM and ReRAM, which can withstand significantly fewer write cycles than DRAM. This necessitates sophisticated wear-leveling algorithms and redundancy schemes that add complexity to memory controllers and system architecture.

Power consumption during write operations remains substantially higher for most NVM technologies compared to DRAM, creating thermal management challenges in dense computing environments. Additionally, the cell-to-cell variability in resistance states introduces reliability concerns that must be addressed through error correction mechanisms.

The integration of NVM into existing computing architectures presents significant challenges, requiring modifications to memory controllers, cache coherence protocols, and operating systems. The lack of standardized interfaces and programming models further complicates adoption, as software developers must navigate different persistence semantics across various NVM implementations.

Existing NVM Architectures for In-Memory Computing

01 Non-volatile memory architecture and design

Non-volatile memory devices are designed with specific architectures to maintain data persistence even when power is removed. These designs include various cell structures, memory arrays, and control circuitry that enable reliable data retention. The architecture may incorporate features like floating gate transistors, charge trapping layers, or resistive elements that can maintain their state without continuous power application, ensuring long-term data persistence.- Non-volatile memory architecture and data persistence: Non-volatile memory devices are designed with specific architectures to ensure data persistence even when power is removed. These architectures include various cell structures, memory arrays, and control circuits that maintain stored information indefinitely. The persistence characteristic makes these memories suitable for long-term data storage in various applications, including embedded systems and data centers.

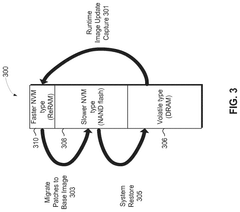

- Memory management techniques for persistent storage: Various memory management techniques are employed to optimize the persistence capabilities of non-volatile memory devices. These include wear-leveling algorithms, garbage collection, and specific addressing schemes that enhance the reliability and longevity of persistent storage. These techniques help manage the inherent limitations of non-volatile memory while maximizing data integrity and retention over time.

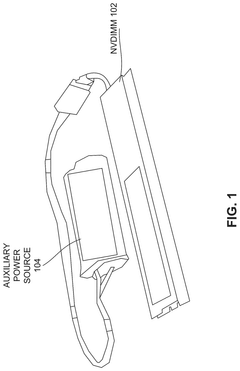

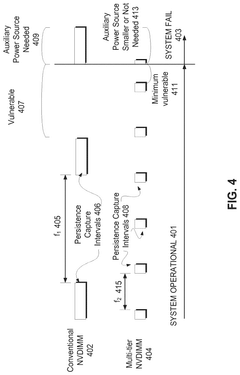

- Power-loss protection mechanisms: Non-volatile memory devices incorporate specific mechanisms to protect data during unexpected power loss events. These mechanisms include power-fail detection circuits, capacitive backup power supplies, and atomic write operations that ensure data consistency. By implementing these protection features, non-volatile memory systems can maintain data persistence even during system failures or power interruptions.

- Interface protocols for persistent memory access: Specialized interface protocols are developed to efficiently access and utilize the persistence features of non-volatile memory. These protocols include specific command sets, timing parameters, and data transfer mechanisms optimized for persistent storage operations. The interfaces enable seamless integration of non-volatile memory into computing systems while maintaining data persistence guarantees across system boundaries.

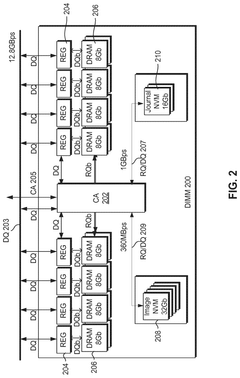

- Performance optimization for persistent memory: Various techniques are employed to optimize the performance of non-volatile memory while maintaining persistence guarantees. These include caching mechanisms, parallel access methods, and specialized controller designs that reduce latency and increase throughput. By balancing performance with persistence requirements, these optimizations enable non-volatile memory to serve in applications requiring both high-speed operation and reliable data retention.

02 Memory persistence management techniques

Various techniques are employed to manage persistence in non-volatile memory systems, including wear-leveling algorithms, error correction codes, and refresh operations. These management techniques help extend the lifespan of memory cells while ensuring data integrity over time. Advanced controllers implement sophisticated algorithms to distribute write operations evenly across the memory array, detect and correct errors, and maintain data persistence even under adverse conditions.Expand Specific Solutions03 Power failure data protection mechanisms

Non-volatile memory devices incorporate specific mechanisms to protect data during unexpected power failures. These include power-loss protection circuits, capacitive backup power sources, and atomic write operations that ensure data consistency. When power is suddenly removed, these mechanisms ensure that in-progress operations are either completed or safely aborted, preventing data corruption and maintaining the persistence characteristics of the memory.Expand Specific Solutions04 Performance optimization for persistent memory

Various techniques are implemented to optimize the performance of persistent memory while maintaining data integrity. These include caching strategies, parallel access methods, and specialized memory controllers that balance speed with persistence requirements. Advanced memory architectures employ multi-level cell designs, interleaved access patterns, and optimized read/write algorithms to achieve higher throughput while ensuring data remains persistent.Expand Specific Solutions05 Emerging non-volatile memory technologies

New technologies are being developed to enhance the persistence capabilities of non-volatile memory devices. These include phase-change memory, magnetoresistive RAM, resistive RAM, and other emerging technologies that offer improved data retention, endurance, and power efficiency. These technologies utilize different physical phenomena to store information persistently, such as changes in material phase, magnetic orientation, or resistance states, providing alternatives to traditional flash memory with potentially superior persistence characteristics.Expand Specific Solutions

Leading Companies in NVM and In-Memory Computing

The non-volatile memory devices enabling persistent in-memory computing systems market is in a growth phase, with increasing demand driven by data-intensive applications. The market is projected to expand significantly as organizations seek more efficient computing architectures. Technologically, the field shows varying maturity levels across players. Industry leaders like Micron Technology, Intel, and Samsung Electronics have established strong positions with advanced product offerings, while emerging players such as SunRise Memory and Unity Semiconductor are developing innovative solutions. Academic institutions including Tsinghua University and Beihang University are contributing significant research. Chinese companies like Alibaba and Huawei (through xFusion) are increasingly investing in this space, indicating the global strategic importance of persistent memory technologies.

Micron Technology, Inc.

Technical Solution: Micron has developed 3D XPoint technology (jointly with Intel) and is now independently advancing its own non-volatile memory solutions for persistent memory computing. Their current focus is on their QuantX 3D NAND and 3D XPoint-based products that enable byte-addressable persistent memory access. Micron's architecture integrates these NVM devices directly into the memory hierarchy, allowing data to persist even during power loss while maintaining DRAM-like access speeds. Their implementation includes specialized controllers that manage wear-leveling, error correction, and address translation to optimize performance and endurance. Micron has also developed software development kits that help programmers leverage persistent memory features through standardized APIs, making it easier to develop applications that can benefit from data persistence without sacrificing performance.

Strengths: Industry-leading manufacturing capabilities for memory technologies; strong vertical integration from design to production; extensive patent portfolio in NVM technologies. Weaknesses: Dependency on ecosystem adoption of persistent memory programming models; higher cost compared to traditional storage solutions; thermal management challenges in high-density implementations.

Intel Corp.

Technical Solution: Intel has pioneered Optane DC Persistent Memory, based on 3D XPoint technology, which bridges the gap between DRAM and storage. This technology creates a new memory tier that offers near-DRAM performance with storage-like persistence and capacity. Intel's implementation places non-volatile memory modules in standard DIMM slots, allowing direct access through the memory bus rather than slower I/O channels. Their architecture supports two operational modes: Memory Mode (where persistent memory acts as large capacity volatile memory with DRAM as cache) and App Direct Mode (where applications directly address persistent memory). Intel has also developed the Persistent Memory Development Kit (PMDK), a collection of libraries and tools that enable developers to integrate persistent memory capabilities into applications. The technology achieves latencies in the hundreds of nanoseconds range, significantly faster than NAND-based SSDs while maintaining data during power cycles.

Strengths: Complete ecosystem from hardware to software development tools; integration with existing server platforms; established partnerships with major software vendors for application support. Weaknesses: Higher cost per GB compared to NAND storage; performance still lags behind DRAM in some workloads; requires specific CPU support (primarily Intel Xeon platforms).

Key Patents and Innovations in Persistent Memory

High performance persistent memory

PatentPendingUS20250021450A1

Innovation

- A multi-tiered memory system that combines DRAM and NAND FLASH technologies, using a centralized buffer to manage write streams and employ journaling for incremental state capture, reducing the need for auxiliary power sources and minimizing downtime by spreading write activity across multiple memory types.

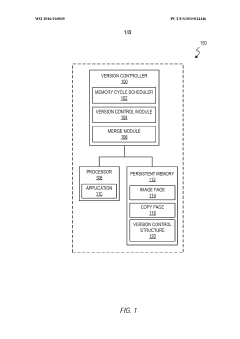

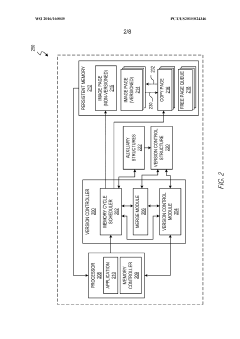

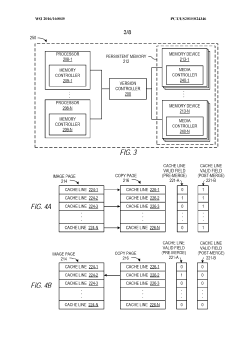

Persistent memory versioning and merging

PatentWO2016160035A1

Innovation

- A version controller is introduced to manage data versioning and merging by allocating a copy page in persistent memory, tracking cache line validity, and performing either forward or backward merges based on a merge direction policy, offloading processor-intensive tasks and minimizing data movement.

Energy Efficiency Considerations in NVM Systems

Energy efficiency has emerged as a critical consideration in the development and deployment of Non-Volatile Memory (NVM) systems for persistent in-memory computing. The inherent power characteristics of NVM technologies present both challenges and opportunities for energy-efficient computing paradigms. Traditional DRAM-based systems consume significant power for data retention through constant refresh operations, whereas NVM technologies eliminate this requirement due to their persistence properties.

When evaluating energy efficiency in NVM systems, several key metrics must be considered: read/write energy consumption, leakage power, and system-level energy implications. Different NVM technologies exhibit varying energy profiles - for instance, STT-MRAM demonstrates relatively low read energy but higher write energy compared to conventional memories, while ReRAM offers excellent standby power characteristics but faces challenges with write endurance and energy.

The asymmetric energy costs between read and write operations in most NVM technologies necessitate specialized memory management policies. Write operations typically consume 5-10 times more energy than read operations in technologies like PCM and ReRAM. This asymmetry has prompted the development of write-aware caching algorithms and data placement strategies that minimize energy-intensive write operations while maintaining system performance.

Hybrid memory architectures combining NVM with traditional volatile memories present promising approaches for optimizing energy efficiency. These architectures strategically leverage the complementary characteristics of different memory technologies - using DRAM for write-intensive workloads and NVM for persistence and low standby power. Research indicates that such hybrid systems can achieve up to 40% energy reduction compared to pure DRAM systems while maintaining comparable performance levels.

Circuit-level innovations have also contributed significantly to improving NVM energy efficiency. These include low-swing write drivers, sense amplifier optimizations, and adaptive voltage scaling techniques that dynamically adjust operating parameters based on workload characteristics. Additionally, emerging 3D integration approaches for NVM technologies offer potential for reduced interconnect energy through shorter data paths and improved thermal management.

At the system architecture level, energy-proportional computing designs that incorporate NVM are gaining traction. These designs enable fine-grained power management where memory subsystems can be partially powered down during periods of low utilization while maintaining data persistence. The non-volatility characteristic enables innovative power management schemes that were previously impossible with volatile memories, potentially reducing system-wide energy consumption by 15-30% in data center environments.

When evaluating energy efficiency in NVM systems, several key metrics must be considered: read/write energy consumption, leakage power, and system-level energy implications. Different NVM technologies exhibit varying energy profiles - for instance, STT-MRAM demonstrates relatively low read energy but higher write energy compared to conventional memories, while ReRAM offers excellent standby power characteristics but faces challenges with write endurance and energy.

The asymmetric energy costs between read and write operations in most NVM technologies necessitate specialized memory management policies. Write operations typically consume 5-10 times more energy than read operations in technologies like PCM and ReRAM. This asymmetry has prompted the development of write-aware caching algorithms and data placement strategies that minimize energy-intensive write operations while maintaining system performance.

Hybrid memory architectures combining NVM with traditional volatile memories present promising approaches for optimizing energy efficiency. These architectures strategically leverage the complementary characteristics of different memory technologies - using DRAM for write-intensive workloads and NVM for persistence and low standby power. Research indicates that such hybrid systems can achieve up to 40% energy reduction compared to pure DRAM systems while maintaining comparable performance levels.

Circuit-level innovations have also contributed significantly to improving NVM energy efficiency. These include low-swing write drivers, sense amplifier optimizations, and adaptive voltage scaling techniques that dynamically adjust operating parameters based on workload characteristics. Additionally, emerging 3D integration approaches for NVM technologies offer potential for reduced interconnect energy through shorter data paths and improved thermal management.

At the system architecture level, energy-proportional computing designs that incorporate NVM are gaining traction. These designs enable fine-grained power management where memory subsystems can be partially powered down during periods of low utilization while maintaining data persistence. The non-volatility characteristic enables innovative power management schemes that were previously impossible with volatile memories, potentially reducing system-wide energy consumption by 15-30% in data center environments.

Reliability and Endurance Challenges

Non-volatile memory (NVM) technologies face significant reliability and endurance challenges that must be addressed for their successful integration into persistent in-memory computing systems. The write endurance of NVM devices remains a critical limitation, with technologies like Phase Change Memory (PCM) typically supporting 10^6-10^8 write cycles, Resistive RAM (ReRAM) offering 10^6-10^9 cycles, and Spin-Transfer Torque Magnetic RAM (STT-MRAM) providing 10^12-10^15 cycles. While these figures represent improvements over traditional flash memory, they fall short of DRAM's virtually unlimited endurance (>10^16 cycles).

Wear leveling mechanisms have emerged as essential techniques to distribute write operations evenly across memory cells, thereby extending overall device lifetime. Advanced wear leveling algorithms can significantly improve endurance by tracking cell usage patterns and dynamically redirecting writes to less-utilized cells. However, these mechanisms introduce computational overhead and latency that must be carefully balanced against reliability benefits.

Data retention represents another significant challenge, particularly in elevated operating temperatures common in computing environments. Most NVM technologies exhibit degradation in retention capabilities as temperature increases, with some PCM implementations losing data integrity after only a few hours at temperatures exceeding 85°C. This necessitates the implementation of error correction codes (ECC) and periodic refresh operations, which partially compromise the persistence advantage of NVM.

Read disturbance effects present additional reliability concerns, where repeated read operations to a specific memory location can inadvertently alter the stored data in adjacent cells. This phenomenon is particularly pronounced in certain ReRAM and STT-MRAM architectures, requiring sophisticated error detection and correction mechanisms to maintain data integrity during intensive read operations.

The variability in switching behavior between write cycles introduces further reliability challenges. Cell-to-cell variations and cycle-to-cycle inconsistencies can lead to unpredictable performance and potential data corruption. Statistical models have been developed to characterize this variability, enabling adaptive programming schemes that adjust write parameters based on individual cell characteristics.

Environmental factors, including temperature fluctuations, electromagnetic interference, and radiation exposure, can significantly impact NVM reliability. Research indicates that some NVM technologies exhibit increased error rates when subjected to thermal cycling or electromagnetic disturbances, necessitating robust shielding and environmental control systems in mission-critical applications.

Addressing these reliability and endurance challenges requires a multi-faceted approach combining materials science innovations, circuit-level techniques, and system architecture adaptations. Recent advancements in material engineering have yielded more robust storage elements with improved endurance characteristics, while intelligent memory controllers with advanced error management capabilities help mitigate reliability concerns at the system level.

Wear leveling mechanisms have emerged as essential techniques to distribute write operations evenly across memory cells, thereby extending overall device lifetime. Advanced wear leveling algorithms can significantly improve endurance by tracking cell usage patterns and dynamically redirecting writes to less-utilized cells. However, these mechanisms introduce computational overhead and latency that must be carefully balanced against reliability benefits.

Data retention represents another significant challenge, particularly in elevated operating temperatures common in computing environments. Most NVM technologies exhibit degradation in retention capabilities as temperature increases, with some PCM implementations losing data integrity after only a few hours at temperatures exceeding 85°C. This necessitates the implementation of error correction codes (ECC) and periodic refresh operations, which partially compromise the persistence advantage of NVM.

Read disturbance effects present additional reliability concerns, where repeated read operations to a specific memory location can inadvertently alter the stored data in adjacent cells. This phenomenon is particularly pronounced in certain ReRAM and STT-MRAM architectures, requiring sophisticated error detection and correction mechanisms to maintain data integrity during intensive read operations.

The variability in switching behavior between write cycles introduces further reliability challenges. Cell-to-cell variations and cycle-to-cycle inconsistencies can lead to unpredictable performance and potential data corruption. Statistical models have been developed to characterize this variability, enabling adaptive programming schemes that adjust write parameters based on individual cell characteristics.

Environmental factors, including temperature fluctuations, electromagnetic interference, and radiation exposure, can significantly impact NVM reliability. Research indicates that some NVM technologies exhibit increased error rates when subjected to thermal cycling or electromagnetic disturbances, necessitating robust shielding and environmental control systems in mission-critical applications.

Addressing these reliability and endurance challenges requires a multi-faceted approach combining materials science innovations, circuit-level techniques, and system architecture adaptations. Recent advancements in material engineering have yielded more robust storage elements with improved endurance characteristics, while intelligent memory controllers with advanced error management capabilities help mitigate reliability concerns at the system level.

Unlock deeper insights with PatSnap Eureka Quick Research — get a full tech report to explore trends and direct your research. Try now!

Generate Your Research Report Instantly with AI Agent

Supercharge your innovation with PatSnap Eureka AI Agent Platform!